www.ijetmas.com September 2017, Volume 5, Issue 9, ISSN 2349-4476

# 1-Bit Full Adder Cell Implemented Using Nanostructures Field-Effect Transistors (nano-FETs)

## **Bander Saman**

Electrical Engineering Department, Taif University, KSA

#### ABSTRACT

This paper aims at designing a 1-bit full adder circuits using high-mobility nanostructures n-channel spatial wavefunction switching (SWS) FETs which provide a significant reduction of cell area (52% smaller in size) and power dissipation. Unlike conventional FETs, SWS-FETs are comprised of two or more vertically stacked coupled quantum dot or quantum well channels, and the spatial location of carriers within these channels is used to encode the logic states (00), (01), (10) and (11). The device is models based on integration of the Berkeley Short-channel IGFET Model (BSIM4.6) and the Analog Behavioral Model (ABM), the model are used to design and develop SWS-FET logic gates (NOT, NAND, NOR and XOR) using 20 nm FETs model. The SWS-FET gates are adjusted for a 1 bit fulladder circuits. The one-bit full addercan be implemented with two XOR and three NANDcomplementary metal-oxide-semiconductor (CMOS) logic gates, the proposed SWS 1-bit full adder circuit successfully designed and simulatedwith less number of transistors (61% less than CMOS1-bit full adder circuit counterpart).In addition, simulation of the proposed SWS1-bit full adder is presented including the operation speed (delay). The accuracy of the circuit is verified in Cadence OrCAD simulator.

#### Keywords

SWS-FETS; FULL ADDER MULTI-CHANNEL FETS; VLSI.

#### INTRODUCTION

The semiconductor industry follows Moore's Law, which predicts the size of Metal-Oxide-Semiconductor (MOS) devices to shrink by 50% every 18-24 months [1, 2]. When the devices sizes have started to approach sub-20 nm regime, several issues have begun to make further miniaturization difficult [3]. The MOS scaling will be not satisfying the requirements of the full adder circuit which is one of the major components in a VLSI. In order toreduce the transistors count of and increase the performance of VLSI circuits, the nanostructures n-FETs to be introduced to implement the full adder circuit.

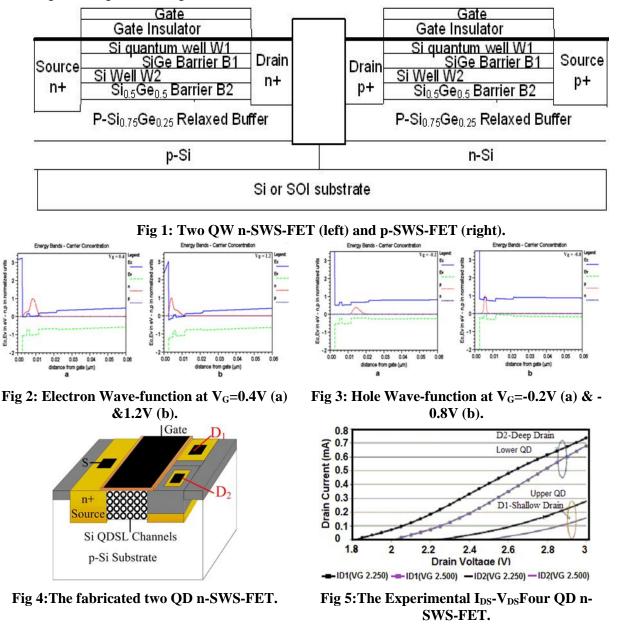

One of the nanostructures n-FETs device is quantum well channels spatial wave-function switched field effect transistor (SWS-FET) as shown in Fig. 1, the SWS-FET device consists of multiple Quantum Well/Dot channels that allow the electron wave-function s switching from one channel to the other as a function of gate voltage. The spatial location of carriers in multiple channels is used to enable the switch between the channels and encode the logic states (00), (01), (10) and (11) [1]. Since each channel is connected to different sources and drains, the current in a SWS-FET is routed between multiple channel drains according to the voltage on a single gate transistor. SWS-FETs can be fabricated in same way as CMOS-FETs with few modifications process, the fabrication process of SWS-FET is explained in detail by Jain et al. [4].

Fig. 1 shows Structures of n- and p- SWS-FET with two Si Quantum Well (2-QW) channel, the device has upper Si well (W1) and lower Si well (W2) sandwiched between SiGe barriers.Fig. 2 presents quantum simulations showing the transfer of electron Wave-function from the lower well (W2) to the upper well (W1) as the gate voltage is changed from 0.4V to 1.2V forthen-SWS-FET device. While, Fig. 3 shows transfer of holes in a similar manner for the gate voltage changed -0.2V to -0.8V forthep-SWS-FET device.Fig. 4 shows the fabricated SiOx- cladded Si quantum dot n-SWS-FET structure [5]. This device has four QD layers with

www.ijetmas.com September 2017, Volume 5, Issue 9, ISSN 2349-4476

single source and two drains (D1 and D2). However, Fig.5 presents the drain-to- source characteristics ( $I_{DS}$  vs  $V_{DS}$ ) for gate voltage in the range of 1.8-2.0V [5].

In terms of circuits design, the device provides opportunity to process 2-bits simultaneously. We have reported circuits of logic gates , analog to digital convertor (ADC), D-latches and static random access memory (SRAM) cells using SWS-FETs with an area saving as shown in Table 1 [6, 7, 8]. In these circuit, the SWS-FETs have utilized multiple source/drain configurations of n-channel SWS-FETs.

| Circuit         | Reeducation % | CMOS   |        | SWS-FET |        |        |       |

|-----------------|---------------|--------|--------|---------|--------|--------|-------|

| Circuit         |               | n-type | p-type | Total   | n-type | p-type | Total |

| 3-bit ADC       | 1-32/74=56%   | 37     | 37     | 74      | 30     | 2      | 32    |

| D-latches       | 1-12/16=25%   | 8      | 8      | 16      | 12     | 0      | 12    |

| 1-bit SRAM (6T) | 1-2/6=66.7%   | 3      | 3      | 6       | 2      | 0      | 2     |

Table 1. The number of transistors between CMOS and SWSFET technology

www.ijetmas.com September 2017, Volume 5, Issue 9, ISSN 2349-4476

#### SWSFET CIRCUIT MODEL

The two QW-SWS-FET has more number of states in its transfer characteristic based on the switching of charge carriers from one channel to other channel of the device [6], the follow of current in each channel/well is related to the gate voltage (V<sub>G</sub>) and two threshold voltages (V<sub>TH2</sub> for the lower well W2 and V<sub>TH1</sub> for the upper well W1). Once V<sub>G</sub>> V<sub>TH2</sub>, the electrons appear in W2 and current flows in W2. If V<sub>G</sub> is increased moreas  $>V_{TH1}$ , the carrier (or their wave-function) start transferring to W1 and the current flows in both wells. Finally, V<sub>G</sub> is further increased (V<sub>G</sub>>>V<sub>TH2</sub>), carrier completely transfer from W2 to W1 and the current flows only in W1.

The self-consistent solution to Poisson and Schrödinger equations give 2D charge density and distribution in two QW[4]. The solution also helps to compute the drains current in each wells  $I_{DS-W1}$  and  $I_{DS-W2}$ . In a simpler model,  $I_{DS-W2}$  and  $I_{DS-W2}$  can be expressed by adapting the classical MOS-FET equations. Equations (1) and (2) represent  $I_{DS-W1}$  and  $I_{DS-W2}$ , respectively. Equation (3) expresses the developed threshold voltage for the lower well ( $V_{th-W2}$ ) [9].

$$I_{DS-W1} = \frac{W_1}{L} C_{OX} \sim_n ((V_{GS1} - V_{th1}) V_{DS1} - \frac{V_{DS1}^2}{2})$$

(1)

$$I_{DS-W2} = \frac{W_2}{L} C_{OX} \sim_n ((V_{GS2} - V_{th-W2}) V_{DS2} - \frac{V_{DS2}^2}{2})$$

(2)

$$V_{th-W2} = \begin{cases} V_{th2} & V_{GS2} < V_{UL} \\ V_{th2} + \frac{(V_{GS2} - V_{UL})^2}{V_{vth1} - V_{UL}} & V_{GS2} \ge V_{UL} \end{cases}$$

(3)

Where

| L                  | the channel length of the device.                                               |

|--------------------|---------------------------------------------------------------------------------|

| $W_{1}, W_{2}$     | the width of the upper well and the lower well, respectively.                   |

| Cox                | the gate capacitance per unit area.                                             |

| μn                 | the channel mobility.                                                           |

| $V_{GS1,}V_{GS2}$  | the gate to source voltage of the upper well and the lower well, respectively.  |

| $V_{DS1}, V_{DS2}$ | the drain to source voltage of the upper well and the lower well, respectively. |

| $V_{th1,}V_{th2}$  | the threshold voltage of the upper well and the lower well, respectively.       |

| $V_{\text{UL}}$    | the transition voltage                                                          |

| V <sub>th-W2</sub> | thedeveloped threshold voltage of well 2                                        |

|                    |                                                                                 |

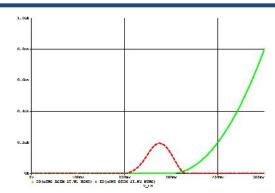

A circuit model for a SWS-FET has already been introducedbased on the equation above[9]. The circuit model is an integration between the Berkeley Short-channel IGFET Model (BSIM4.6) and the Analog Behavioral Model (ABM). This model is set in hierarchical block and it ready to be used in Cadence-OrCAD CIS. Fig. 6shows asimulation  $I_{DS}$ -V<sub>GS</sub> characteristic of 2 QW n-SWS-FET with twin-drain and single-source. The twindrain n-SWS-FET model have 230-parameters obtained using modeled BSIM4.6.0 level 7 Third Generation Model. The major parameters are ( $V_{DD}$ =1V, L=20nm, W1=40nm, W2=100nm,  $V_{TH1}$ =0.3V, 5V,  $V_{TH2}$ =0.2 V, and  $V_{UL}$ =0.2V). The simulation result show excellent performance on switching and output currents.

www.ijetmas.com September 2017, Volume 5, Issue 9, ISSN 2349-4476

Fig6:The simulation of twin-drain 20nm n-SWS-FET modeled I<sub>DS-W2</sub>(- -)&I<sub>DS-W1</sub>( ).

# LOGIC GATES CIRCUITS USING N-SWS-FET

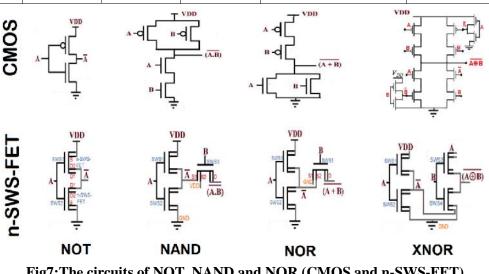

The complementary MOS (CMOS) uses PMOS and NMOS transistors to implement any Boolean functions [14]. This section shows the design possibilities of logic gates using only n-SWS-FETs. The truth table for the various logic gates is presented in Table 2.Fig. 7 shows the circuit designs of logic gates (NOT/Inverter, NAND, NOR and XNOR) gates using SWS-FETs, where the circuits of SWS-FET gate are established by Jain et al. [1, 9].

| Table 2. The truth table for the imperimented logic gates. |     |         |        |        |                                              |                                |

|------------------------------------------------------------|-----|---------|--------|--------|----------------------------------------------|--------------------------------|

| A                                                          | В   | NOT (A) | NAND   | NOR    | XOR                                          | XNOR                           |

|                                                            |     | Ā       | A      | A + B  | $A \oplus B = \overline{A}B + A\overline{B}$ | $A \odot B = \overline{A} + A$ |

| 0                                                          | 0   | 1       | 1      | 1      | 0                                            | 1                              |

| 0                                                          | 1   | 1       | 1      | 0      | 1                                            | 0                              |

| 1                                                          | 0   | 0       | 1      | 0      | 1                                            | 0                              |

| 1                                                          | 1   | 0       | 0      | 0      | 0                                            | 1                              |

| # CMO                                                      | S   | 1-PMOS  | 2-PMOS | 2-PMOS | 16 (by 4-NAND)                               | 16 (by 4-NOR)                  |

| transistors                                                |     | 1-NMOS  | 2-NMOS | 2-NMOS | 8(by Transmission Gate [10,11])              |                                |

| # n-SWS-FET                                                |     | 2       | 3      | 3      | 4                                            | 4                              |

| transisto                                                  | ors |         |        |        |                                              |                                |

Table 2. The truth table for the implemented logic gates.

Fig7:The circuits of NOT, NAND and NOR (CMOS and n-SWS-FET)

www.ijetmas.com September 2017, Volume 5, Issue 9, ISSN 2349-4476

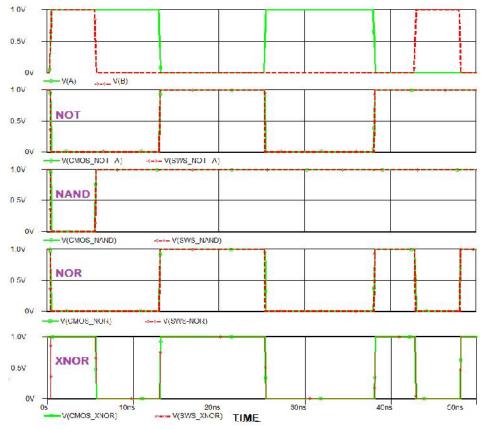

The accuracy of the CMOS and SWS gates are verified as shown in Fig 8.The outputs of SWS-FET and CMOS are identical and responding in the same time.

Fig8:The simulation of CMOS and n-SWS logic gates

# ONE-BIT FULL ADDER CIRCUITS USING N-SWS-FET

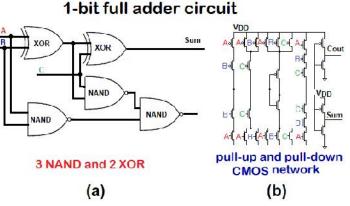

The 1-bit full adder can be performed by 3 NAND and 2 XOR gates as circuit shown in Fig. 9 (a), Table 3 shows Truth Table of the 1-bit full adder [12]. The 1-bit full adder adds three one-bit numbers A, B, and C. where, A and B are the operands and C is a bit carried in from the previous stage. The circuit has a two-bit output carry ( $C_{out}$ ) and Sum.

The conventional CMOS 1-bit full adder circuit has 44 transistors (12 FETs NANDs and 32 FETs for XORs)asshown in Fig. 9. However, this high number of transistors may results in large power consumption and introduces more delay. If the XOR is designed by using CMOS transmission gate, the number of transistors is reduce to 28 transistors (12 FETs for NANDs+16 FETs for XORs).Based on pull-up and pull-down CMOS network, the 1-bit full adder can be also done by 28 CMOS transistors as shown in Fig. 9 (b)[13]. Also, many 1-bit full adder circuits are designed with the transistor counts varies from 28 to 6[13]. In this paper, 17 n-SWS-FETs are used to build the 1-bit full adder circuit (9 SWS-FETs for SWS-NANDs and 8SWS-FETs for SWS-XORs).

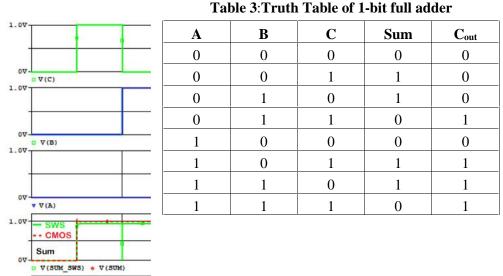

Fig 10 shows the simulation of conventional CMOS44 transistors(--) and the SWS-FET ( )1-bit full adder circuit. The simulations have been done at 20nm channel length transistors, the major simulations parameters are ( $V_{DD}=1V$ , L=20nm, W1=40nm, W2=100nm,  $V_{TH1}=0.3V$ , 5V,  $V_{TH2}=0.2$  V, and  $V_{UL}=0.2V$ ). The binary inputs are V(A), V(B), and V(C). A sum of the binary input data is denoted by V(SUM) and a carry bit is indicated as V(Cout). In the simulation, the sum is the XOR of the three inputs (A, B, C). The simulation

www.ijetmas.com September 2017, Volume 5, Issue 9, ISSN 2349-4476

results show excellent performance for CMOS and SWS-FETand their outputs are typically as of the 1-bit full adder Truth Table.

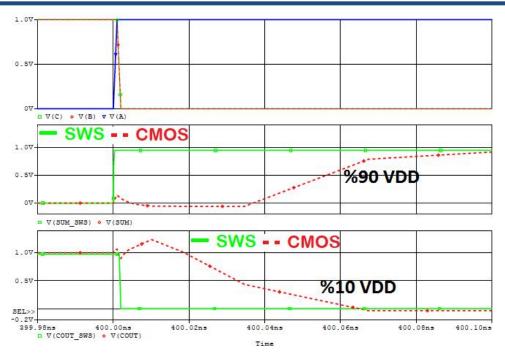

The simulation analysis is carried out with three inputs (A, B, C) and two outputs (Sum and Cout) of full Adder. The simulation waveform of delay is shown in Fig.11and Table 4, the comparison shows that the SWS-FETs adder circuit has lass number of transistors and less delay compare with the conventional CMOS adder circuit.As a result, the SWS-FET 1-bit full adder circuit takes lesser area and consumes lesser power, while maintaining the fast speed of operation.

Fig9: The 1-bit full Adder Circuit.

Table 3: Truth Table of 1-bit full adder

Fig10:The simulation of CMOS & SWS-FET Full Adder. Table 4: The delay Simulation Result 1-bit full adder circuits

| Circuit | # Transistors | Delay Sum     | Delay Cout    |

|---------|---------------|---------------|---------------|

| CMOS    | 44            | 60picosecond  | 40picosecond  |

| SWSFET  | 21            | <10picosecond | <10picosecond |

SWS - CMOS Cout OV

U.COUT\_SWS) V(COUT)

www.ijetmas.com September 2017, Volume 5, Issue 9, ISSN 2349-4476

Fig11:The delaysimulation of the conventional CMOS& SWS-FET 1-bit Full Adder.

## CONCLUSION

This paper presents the modeling of logic circuits based on spatial wave-function-switched field-effect transistors (SWS-FETs). The circuits of SWS-FET logic gates, 1-bit Full Adder circuits are been designed in a Cadence Or CAD using 20nm technology, with a voltage supply of 1V.

In summary, we have successfully demonstrated conventional CMOS and SWS-FET 1-bit full adder circuits. The simulation of the two circuits are presented, the comparison and results aretabulated. The number of the FETs is reduced from 44 in conventional CMOS architecture to 17 using n channel SWS-FETs. This reduces cell area and power dissipation, then the delay is reduced from 60 psconventional CMOS to <10 ps using SWS-FETs. This is making SWS-FET a promising technology for analog applications.

#### REFERENCES

- P. Gogna, M. Lingalugari, J. Chandy, E. Heller, E-S. Hasaneen and F. Jain. 2012. Quaternary Logic and Applications Using Multiple Quantum Well Based SWSFETs, Int. Journal of VLSI design & Communication Systems, Vol.3, No.5.

- [2] Moore, G. 2006. Cramming more components onto integrated circuits, Reprinted from Electronics, volume 38, number 8, April 19, 1965, pp.114 ff. Solid-State Circuits Newsletter, IEEE, 20(3), 33-35.

- [3] Kim, Austin, Baauw, Mudge, Flautner, Hu, Irwin, Kandemir, and Narayanan. 2003. Leakage current: Moore's law meets static power. Computer, 36(12), 68-75.

- [4] Jain, F. C., J. Chandy, B. Miller, E-S. Hasaneen, and E. Heller. 2011. Spatial Wavefunction-Switched (SWS)-FET: A Novel Device To Process Multiple Bits Simultaneously With Sub-Picosecond Delays. International Journal of High Speed Electronics and Systems, 20(03), pp.641–652.

- [5] Jain, Miller, Suarez, Chan, Karmakar, Al-Amoody, Gogna, Chandy, and Heller. 2011. Spatial Wavefunction-Switched (SWS) InGaAs FETs with II–VI Gate Insulators. Journal of Electronic Materials, 40(8), pp.1717–1726.

- [6] Bander Saman, P. Gogna, El-Sayed Hasaneen, J. Chandy, E. Heller, and F. C. Jain. 2017. Spatial Wavefunction Switched (SWS) FET SRAM Circuits and Simulation. International Journal of High Speed Electronics and Systems, Vol. 26, No. 3 (2017) 1740009

www.ijetmas.com September 2017, Volume 5, Issue 9, ISSN 2349-4476

- [7] B. Saman, P. Gogna, E-S. Hasaneen, J. Chandy, and E. Heller, and F. Jain1. 2016. Complementary Spatial Wavefunction-Switched (SWS) FETs and Circuits. International Semiconductor Device Research Symposium (ISDR) 2016.

- [8] B. Saman, P. Gogna, E. Heller, F.C Jain. 2016. D Latch Flip Flop Using Spatial Wave-function Switched Field-Effect Transistors. In Proceedings of the IASTEM International Conference, Miami, USA, December 2016.

- [9] Saman, B., P. Mirdha, M. Lingalugari, F. Gogna, E. Jain, Hasaneen, and Heller. 2015. Logic Gates Design and Simulation Using Spatial Wavefunction Switched (SWS) FETs. International Journal of High Speed Electronics and Systems, vol. 24, no. 3-4, 2015, pp.

- [10] Swati Sharma, Rajesh Mehra. 2014. Area & Power Efficient Design of XNOR-XOR Logic Using 65nm Technology. National Conference on Synergetic Trends in engineering and Technology (STET-2014)

- [11] Maruf M Ali,S. M. Mainullslam,Md. MehediFarhad,Md. RubaiyatIalam,andNazmun.Islam. 2013. Analysis of CMOS Multiplexer Circuits of Different Area and Logic Style. IOSR Journal of VLSI and Signal Processing (IOSR-JVSP) Volume 3, Issue 6, PP 17-27

- [12] Singh, N.K. & Sharma, P.K., 2014. 2T 2:1 MUX based 1 bit full adder design. Communications and Signal Processing (ICCSP), 2014 International Conference on, pp.1491–1493.

- [13] Manjunath, K., P. Abdul Lateef Haroon, A. Pagi, and J. Ulaganathan. 2016. Analysis of various full-adder circuits in cadence. 2015 International Conference on Emerging Research in Electronics, Computer Science and Technology, ICERECT 2015, pp.90–97.