# Design and Simulation of Dynamic Voltage Restorer (DVR) Using Sinusoidal Pulse Width Modulation (SPWM)

Saripalli Rajesh<sup>\*</sup>, Mahesh K. Mishra, *Senior Member IEEE* and Sridhar K.

Abstract— This paper gives a systematic procedure of the design and simulation of Dynamic Voltage Restorer (DVR) using Sinusoidal Pulse Width Modulation (SPWM). Though power quality related problems like voltage sags/swells occur both on the transmission side as well as the distribution side, the terminology used for the compensation devices is different. DVR is a series connected device used for compensating voltage sags and swells on the distribution side. In this work, a step by step procedure is given to figure out the components that are required for the design and simulation of DVR. The detection of sags/swells is carried out with the help of dgo theory, whereas the control of the voltage source inverter is done with the help of SPWM. The VSI has been implemented with the help of both Bipolar SPWM as well as Unipolar SPWM and the results were compared. The simulation was carried out with the help of SIMULINK & MATLAB and the results were found to be in accordance with theory.

Index terms – Dynamic Voltage Restorer (DVR), Sinusoidal Pulse Width Modulation (SPWM), dqo theory, Voltage sag/swell.

## I. INTRODUCTION

The term Power Quality is something that tells about the quality of power. While "power quality" is a convenient term for many, it is the quality of the voltage rather than power or current that is actually described by the term in [1]. Ideally any electric utility is supposed to supply a pure sinusoidal voltage of required magnitude and frequency for all the time without any deviation. But in reality it is not possible to meet the ideal requirements. Thus, practically there are deviations in the voltages which can have adverse effects on the load. Of all the power quality problems, 92% of the interruptions in industrial installations are due to voltage sags [2]-[4]. According to IEEE Std. 1159-1995, sag is defined as a decrease in rms voltage or current between 0.1pu and 0.9 pu at the power frequency for durations from 0.5 cycles to 1 min. Sags and swells are characterized by their magnitude as well as time duration. These voltage problems can be solved using a series connected custom power device called dynamic voltage restorer (DVR). In this paper, the implementation of DVR and its simulation are discussed in detail. The emphasis has been given for switching control strategy i.e. pulse width modulation scheme and their detailed results are presented.

## II. PRINCIPLE OF DVR

The principle of DVR is simple i.e. whenever the source voltage is unbalanced or distorted the DVR restores the loadside voltage to the desired amplitude by injecting a voltage of required magnitude [5]. In other words we can say that the main function of the DVR is to regulate the load voltage waveform constantly and if any sag or swell occurs, the required voltage will be injected to the load point. In short, the principle of DVR can be explained with the help of the following equation which has to be satisfied for all the time.

Source voltage + DVR voltage = Load voltage (1)

The DVR has to work only when there is a sag/swell in the source voltage. Depending on that there are actually three modes of operation for a DVR. They are

- i. Protection Mode

- ii. Standby Mode

- iii. Injection Mode

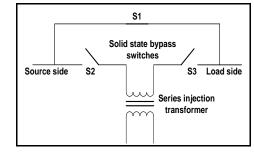

Whenever there is a fault on the line, very high fault currents will be flowing through the line. Since the DVR is series connected, the fault currents will be flowing through the DVR also which is not desired. The DVR should be protected from these over currents or large inrush currents [6]. The bypass switches remove the DVR from system by supplying another path through switch  $S_1$  for current as shown in Fig. 1.

Fig. 1 Configuration of switches in protection mode

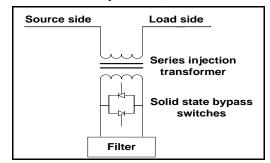

In standby mode (normal steady state conditions), the DVR may either go into short circuit operation or inject small voltage to compensate the voltage drop for transformer reactance or losses as shown in Fig. 2. Short circuit operation of DVR is the general preferred solution in steady state [6]. (Because the small voltage drops due to transformer reactance do not disturb the load requirements).

Fig. 2 Configuration of switches in standby mode

The DVR goes into injection mode as soon as the sag is detected. Three single-phase ac voltages are injected in series with required magnitude, phase and wave shape for compensation. The types of voltage sags, load conditions and power rating of DVR will determine the possibility of compensating voltage sag [6].

#### III. IMPLEMENTATION OF DVR

In the previous section the principle and the operating modes of DVR have been discussed. Now the important thing is to figure out the components that are required for the implementation of DVR. The following steps are used to implement the DVR in injection mode.

*Step 1:* To find out whether there is any sag/swell in the source voltage. It is done by comparing the terminal source voltages with reference load voltages. The difference between the source voltages and reference load voltages is the required amount of voltage that has to be injected by the DVR.

*Step 2:* To generate switching commands to the VSI in order to track the reference voltages (generated in step 1) using a suitable switching scheme such as PWM.

*Step 3:* To filter out the harmonics that are present in the output of the voltage source inverter.

*Step 4*: To inject the filtered output through the three single phase series isolation transformers present between the source and the load.

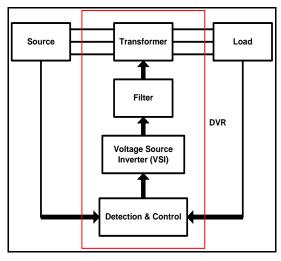

Following above mentioned steps, the DVR should work only if there is any difference between the terminal source voltage and the load voltage. To implement above steps, the following building blocks are required to realize the DVR.

- i. Detection and control block

- ii. Voltage source inverter

- iii. Filter components

- iv. Isolation transformers

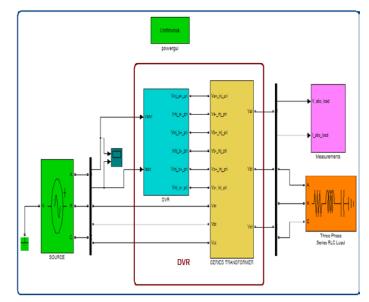

Fig. 3 shows the block diagram of DVR. It can be seen that the DVR is connected in series between the source and the load.

Fig. 3 Block diagram of DVR

# A. Detection and Control Block

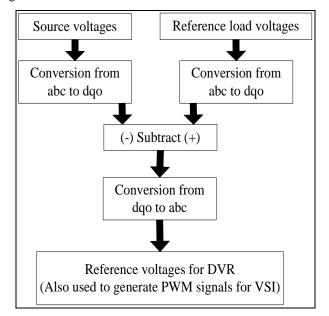

The first component of the DVR is the detection and control block. All it needs to do is to monitor the terminal source voltage and the reference load voltages in the dq reference frame. Whenever, there is any sag/swell in the source voltage there will be deviation in the dq components of the source voltage from those of the reference load voltages [7]. Based on the difference between the dq components of the source and reference load voltages, the detection block will generate a reference voltage ' $v_{DVR}$ ' that needs to be injected by the DVR. The same reference voltage  $v_{DVR}$  is used to generate the PWM signals for the VSI block.

The shape of the reference voltage,  $v_{DVR}$ , depends on two factors i.e. whether the sag/swell voltages are balanced or not and contain harmonics or not.

On the basis of above factors, the shape of the reference voltage  $v_{DVR}$  can be one of the following four cases, as shown in Table 1.

TABLE 1 SHAPES OF REFERENCE DVR VOLTAGES IN DIFFERENT CASES

|      | Type of sag/swell |              | Harmonics    |              | Shape of the   |  |

|------|-------------------|--------------|--------------|--------------|----------------|--|

| Case | Balanced          | Unbalanced   | Present      | Absent       | Reference      |  |

| 1    | $\checkmark$      |              | $\checkmark$ |              | Non Sinusoidal |  |

| 2    | $\checkmark$      |              |              | $\checkmark$ | Sinusoidal     |  |

| 3    |                   | $\checkmark$ | $\checkmark$ |              | Non Sinusoidal |  |

| 4    |                   | $\checkmark$ |              | $\checkmark$ | Sinusoidal     |  |

The shape of the reference DVR voltages  $v_{DVR}$  is sinusoidal only in two cases i.e. in case 2 and case 4. The flow chart of implementing the detection and control block is as shown in Fig. 4.

Fig. 4 Flow chart showing the implementation of detection and control block

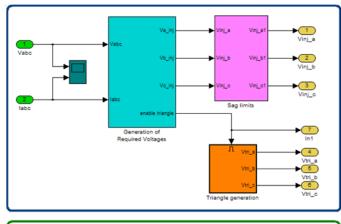

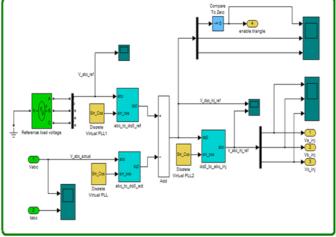

The above algorithm for the detection and generation of reference voltage is implemented using Simulink model as shown in Fig. 5.

Fig. 5 Simulink diagram of the Detection & Control Block

The next step is to implement the VSI with the help of the reference voltages generated by the detection and control block.

#### B. Voltage Source Inverter

The voltage source inverter should be controlled in such a way as to generate the voltages which are same as the reference voltages generated by the detection and control block. Here in this work, sinusoidal pulse width modulation (SPWM) is used as the switching strategy for the inverter. Actually any PWM technique can be used as the switching strategy for the VSI. However, due to the merits mentioned in [8], SPWM has been chosen to control the VSI. The following reasons will justify the selection of SPWM as the control strategy for the VSI.

- i. The output of the inverter should be same as the reference voltages generated by the detection and control block.

- ii. From the theory of SPWM [9], we know that the fundamental of the output of the inverter will be same as the modulating waveform used to compare the triangular carrier.

Combining (i) and (ii) it can be concluded that if the reference voltages generated by the detection and control block are

given as the modulating waveforms for the inverter then the fundamental component of the output of the inverter will be same as the reference voltages generated by the detection and control block. This inherent advantage of SPWM (which makes our design much simpler) justifies the selection of SPWM as the switching strategy for the inverter. Along with this, SPWM also have following advantages.

- iii. Inverter implemented using SPWM will have a constant switching frequency.

- iv. By choosing the modulation frequency (which is nothing but the ratio of carrier frequency to the modulating waveform frequency) very high, the switching harmonics can be pushed to high frequency side which in turn will make the filter requirement less [8].

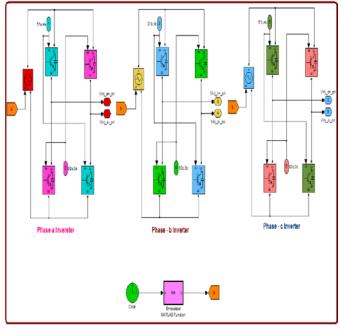

In the simulation the voltage source inverter has been implemented as shown in Fig. 6.

Fig. 6 Simulink diagram showing three single phase H- bridge inverters

The modulation index  $M_a$  is equal to

$$M_a = \frac{\text{Amplitude of the modulating waveform}}{\text{Amplitude of the carrier waveform}}$$

(2)

The modulating waveforms are nothing but the reference voltages generated by the detection and control block. Therefore the amplitude of modulating waveform is nothing but the magnitude of sag whereas the amplitude of carrier waveform is set as 1 pu. Therefore

$M_a =$  Magnitude of sag

The modulation frequency  $M_f$  is defined as

$$M_f = \frac{\text{Frequency of the carrier waveform}}{\text{Frequency of the modulating waveform}}$$

(3)

In the simulation, frequency of the modulating waveform is 50Hz and  $M_f$  is chosen as 57. Therefore,

Frequency of carrier waveform = 57\*50= 2850Hz

There is nothing special in choosing  $M_f$  as 57, the only constraint is that  $M_f$  should be as high as possible. But again there is an upper limit on  $M_f$  because as we keep on increasing  $M_f$  the switching losses also increase. Thus, there is always a tradeoff between switching losses and  $M_f$ .

The next step is to find out the value of DC source voltage of the inverter. In the linear region of modulation ( $0 < M_a < 1$ ), the amplitude of the fundamental component of the inverter output is equal to the product of the modulation index and the DC source voltage. Therefore

$$V_{inv out,1} = M_a * V_{dc} \tag{4}$$

where

$V_{inv out,1}$  is the amplitude of the fundamental component of the inverter output and  $V_{dc}$  is the voltage of the DC source. The constraint for successful compensation is that the amplitude of the fundamental component of the inverter output should be equal to the magnitude of sag. Therefore,  $V_{inv out,1}$  should be equal to the magnitude of sag.

Substituting the value of  $M_a$  in (4), we get the value of DC source voltage as

Magnitude of sag = (Magnitude of sag \*  $V_{dc}$ ). It implies that

$$V_{dc} = 1$$

pu

Now having figured out all the values that are required for the inverter the next step is to filter out the harmonics that are present in the inverter output.

#### C. Filter Components

The non-linear characteristics of semiconductor devices present in the inverter result in distorted waveforms associated with harmonics at the inverter output. To overcome this problem and provide high quality energy supply, filter unit is used [10]. Since SPWM technique with high modulation frequency is used to implement the inverter, all the harmonics are pushed to the high frequency side which in turn are easier to filter out. All the harmonics are centered around the multiples of carrier frequency. So, higher the carrier frequency easier will be the filtering. But as mentioned earlier, always there will be a tradeoff between switching losses and filtering. The values of the filter components used in the simulation are the following

$$R=2\Omega; C=50\mu F; L=5mH$$

#### D. Isolation Transformer

The filtered inverter output is injected to the line with the help of an isolation transformer [11]. The isolation transformer has the following advantages

- They isolate the inverter from the line and thus prevent the DC source of the inverter being shorted through the switches.

- The ratings of the inverter can be reduced by using a step up transformer.

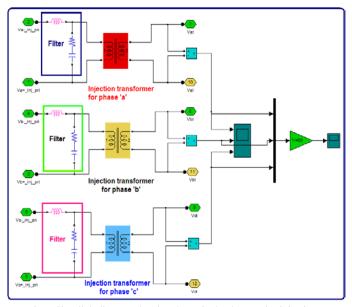

Fig. 7 shows the Simulink implementation of the filter unit and the transformer block.

Fig. 7 Simulink diagram showing three single phase series injection transformers and filters

Now assembling all the four building blocks we get the final device DVR as shown in Fig. 8.

Fig. 8 Block diagram showing the simulation of DVR

#### IV. RESULTS & DISCUSSIONS

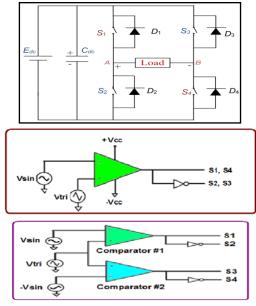

The designed DVR is used to compensate sags/swells of magnitude in the range (0.1pu -0.9 pu). But in reality a DVR can compensate a maximum of 0.5pu. For the purpose of demonstration sag of magnitude 0.6 pu and a swell of magnitude 0.4 pu are considered. The VSI is implemented using both Bipolar SPWM as well as Unipolar SPWM and the results were compared. The pulses for Bipolar and Unipolar SPWM are generated with the help of circuits as shown in Fig. 9. The output of the comparator will be high when  $v_{sin} > v_{tri}$  and it will be low when  $v_{sin} < v_{tri}$ .

Fig. 9 Generation of pulses in bipolar and unipolar SPWM

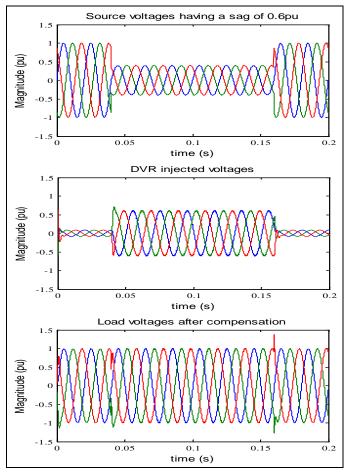

#### Case 1: Compensation of balanced sag using DVR

A balanced sag of magnitude 0.6 pu occurs from t=0.04s to t=0.16s. Fig. 9 shows the waveforms of source voltage, DVR injected voltage and load voltage respectively. It is clear from Fig. 9 that the DVR is working well in case of sags.

Fig. 10 Waveforms showing the compensation of sag

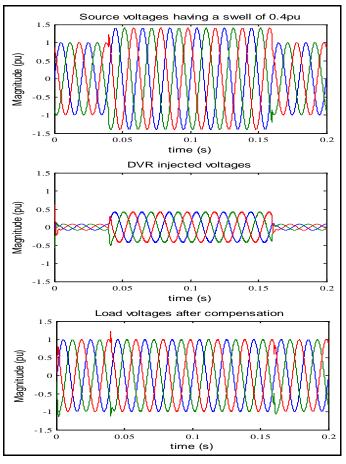

#### Case 2: Compensation of balanced swell using DVR

A balanced swell of magnitude 0.4 pu occurs from t=0.04s to t=0.16s. Fig. 10 shows the waveforms of source voltage, DVR injected voltage and load voltage respectively. It is clear from Fig. 10 that the DVR is working well in case of swells.

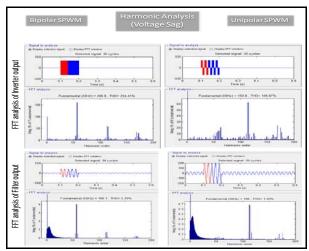

The FFT analysis was done for case 1 and case 2 to check out the quality of waveforms at various points. Fig. 11 shows the comparison of FFT analysis of the inverter output and the filtered inverter output respectively in both bipolar SPWM as well as unipolar SPWM (For case 1).

Fig. 12 Waveforms showing the FFT analysis of Inverter & Filter outputs

From the FFT analysis it is clear that all the harmonics are pushed to high frequency side and also the THD content is very low in case of Unipolar SPWM when compared to Bipolar SPWM. FFT analysis was done for both sags and swells and the results have been shown in Table 2.

Table 2 Comparision of THD values in Bipolar & Unipolar SPWM for both Sag & Swell

| S.NO | Waveform        | THD in Bipolar<br>SPWM (%) |        | THD in Unipolar<br>SPWM (%) |       |

|------|-----------------|----------------------------|--------|-----------------------------|-------|

|      |                 | Sag                        | Swell  | Sag                         | Swell |

| 1    | Inverter Output | 204.41                     | 269.93 | 106.67                      | 175.2 |

| 2    | Filter Output   | 5.39                       | 6.61   | 1.5                         | 1.52  |

| 3    | Source voltage  | 0.02                       | 0.00   | 0.02                        | 0.00  |

| 4    | Load voltage    | 2.32                       | 2.82   | 0.7                         | 0.66  |

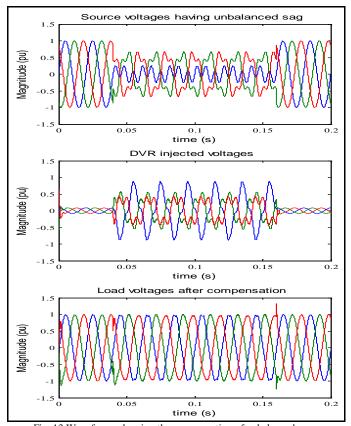

# Case 3: Compensation of unbalanced sag having harmonics using DVR

An unbalanced sag having harmonics occurs from t=0.04s to t=0.16s. The reference DVR voltages in this case are not sinusoidal. Fig. 12 shows the waveforms of source voltage, DVR injected voltage and load voltage respectively. It is clear from the figures that the DVR is working well in case of unbalanced sags having harmonics. The results of FFT analysis for the unbalanced sags are shown in Table 3.

Fig. 13 Waveforms showing the compensation of unbalanced sags

Table 3 Comparision of THD values in Bipolar & Unipolar SPWM for unbalanced sags

| S.NO | Waveform        | THD in Bipolar<br>SPWM (%) | THD in Unipolar<br>SPWM (%) |

|------|-----------------|----------------------------|-----------------------------|

| 1    | Inverter Output | 142.17                     | 63.11                       |

| 2    | Filter Output   | 25.05                      | 24.72                       |

| 3    | Source voltage  | 200                        | 200                         |

| 4    | Load voltage    | 4.61                       | 4.41                        |

#### V. CONCLUSIONS

The designed system for compensating sags/swells is working well and has been verified using Simulink. The voltage source inverter was implemented with the help of both Bipolar SPWM & Unipolar SPWM. The results were in accordance with theory (SPWM). The designed DVR can compensate any sag of magnitude between 0.1-0.9 pu (in simulation). But in reality a DVR can compensate maximum sag of 0.5 pu. The simulation was made keeping in mind the constraints on hardware i.e. the simulated version will be very close to the hardware implementation. So the hardware implementation is made relatively easier by the design of the DVR simulation closer to reality.

#### REFERENCES

- Roger C. Dugan, Mark F. McGranaghan, Surya Santoso, H. Wayne Beaty, "*Electrical Power Systems Quality*", Chapter 1 & 2 pp. 1-30, Second Edition, Tata McGraw-Hill, 2004.

- [2] M. H. J Bollen, Understanding Power Quality Problems, Voltage Sags and Interruption, Piscataway, NJ: IEEE Press, 1999.

- [3] S. W. Middlekauff, and E. R. Collins, "System and customer impact: consideration of series custom power devices," *IEEE Trans. on Power Delivery*, vol. 13, no.1, pp.278-282, Jan. 1998.

- [4] S.S. Choi, J. D. Li and D.M. Vilathgamuwa, "A generalized voltage compensation strategy for mitigating the impacts of voltage sags/swells," *IEEE Trans. on Power Delivery*, vol. 20, no.3, pp.2289-2297, July 2005.

- [5] Ghosh A., Ledwich G., "Structures and control of a dynamic voltage regulator (DVR)," *Power Engineering Society Winter Meeting*, 2001. IEEE, vol.3, pp. 1027-1032 vol.3, 2001.

- [6] V. K. Ramachandaramurthy, A. Arulampalam, C. Fitzer, C. Zhan, M. Barnes and N. Jenkins "Supervisory control of dynamic voltage restorers" IEE Proc. Gener. Transm. Distrib. vol. 151, no. 4, pp. 509-516, July 2004.

- [7] Omar R., Rahim N.A., "Modeling and simulation for voltage sags/swells mitigation using dynamic voltage restorer (DVR)," *Power Engineering Conference*, 2008. AUPEC '08. Australasian Universities, pp.1-5, 14-17 Dec. 2008.

- [8] Dr. Zainal Salam, "Power *electronics and Drives*", Chapter-4, version 3, 2003.

- [9] Hussin H., Saparon A., Muhamad M., Risin M. D., "Sinusoidal Pulse Width Modulation (SPWM) Design and Implementation by Focusing on Reducing Harmonic Content, *Mathematical Modeling* and Computer Simulation (AMS), 2010 Fourth Asia International Conference, pp.620-623, 26-28 May 2010.

- [10] Sasitharan S, Mishra Mahesh K., "Design of passive filter components for switching band controlled DVR," *TENCON-2008*, *IEEE Region 10 Conference*, pp.1-6, 19-21 Nov. 2008

- [11] S. Sasitharan., Mishra Mahesh. K., Kumar B. K., Jayashankar V., "Rating and design issues of DVR injection transformer," *Applied Power Electronics Conference and Exposition*, 2008. APEC 2008. Twenty-Third Annual IEEE, pp. 449-455, 24-28 Feb. 2008.