International Journal of Innovative Research in Science, Engineering and Technology

Volume 3, Special Issue 3, March 2014

2014 International Conference on Innovations in Engineering and Technology (ICIET'14)

21<sup>st</sup> & 22<sup>nd</sup> March Organized by

K.L.N. College of Engineering, Madurai, Tamil Nadu, India

# **A Survey on Multi Gate MOSFETS**

**B.Buvaneswari**

Department Of CSE, K.L.N College of engineering, Madurai, , India

**ABSTRACT**— This paper presents the various device structure of MOSFETs like SOI-MOSFET, Double gate Mosfet, Trigate mosfet, Multigate mosfet ,Nanowire Mosfets,High-K Mosfets& their deserves. To grasp during a easy means, mathematical ideas of device physics skipped.

**INDEX TERMS-**DG-MOSFET, GAA, MuG MOSFETS.

#### **I.INTRODUCTION**

Over the past decades, the Metal oxide Semiconductor (MOSFET) has repeatedly been scaled down in size[1]; classic MOSFET channel lengths were once many micrometers, however fashionable integrated circuits square measure incorporating MOSFETs with channel lengths of tens of nanometers. Henry Martyn Robert Dennard's work on scaling theory was polar in recognizing that this in progress reduction was potential. Intel began production of a method that includes a thirty two nm feature size (with the channel being even shorter) in late 2009. The semiconductor trade maintains a "roadmap", the ITRS,[2] that sets the pace for MOSFET development. Historically, the difficulties with decreasing the scale of the MOSFET are related to the semiconductor fabrication method, the necessity to use terribly low voltages, and with poorer electrical performance necessitating circuit plan and innovation

(small MOSFETs demonstrate higher outflow currents, and lower output resistance). A multigate device or multiple gate junction transistor (MuGFET) refers to a MOSFET (metal-oxide-semiconductor field-effect transistor) which includes quite one gate into a sole device. The multiple gates could also be controlled by one gate.conductor, whereby the multiple gate surfaces act electrically as one gate, or by freelance gate electrodes. A multigate device using freelance gate electrodes is usually referred to as a Multiple Insulated Gate Field impact electronic transistor (MIGFET). Multigate transistors square measure one in every of quite an few ways being developed by CMOS semiconductor makers to form ever-smaller microprocessors and memory cells, conversationally spoken as extending Moore's Law.[1]Development efforts into multigate transistors are reported by AMD, Hitachi, IBM, Infineon Technologies, Intel Corporation, TSMC, Free scale Semiconductor, University of American state, Berkeley et al. and also the ITRS predicts that such devices are going to be the cornerstone of sub-32 nm technologies[2]. The prime roadblock to widespread implementation is manufacturability, as each coplanar and non-planar styles gift noteworthy challenges, especially with relation to lithography and patterning. Alternative complementary ways for device scaling embody channel strain engineering, silicon-oninsulator-based technologies, and high-k/metal gate materials. Because the rein in of CMOS technology approaches physical limitations, the necessity arises approaches physical limitations, the necessity arises for

**Copyright to IJIRSET**

www.ijirset.com

783

different device structures. For different device structures, several novel structures are planned for varied novel structures are planned for the nanoscale regime. One such structure is that the Double-Gate electronic transistor, planned within the Eighties.Transistor, projected within the Eighties.Other potential solutions embody SOI devices, strained-silicon FETs, carbon carbon nanotube FETs.

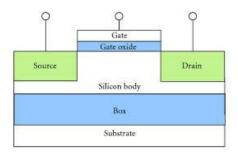

#### II. Silicon ON Insulator

In physics, associate SOI MOSFET semiconductor conductor layer, e.g. silicon, atomic number 32 or variety, fashioned is made is created on top of associate dielectric layer which can be a buried oxide (BOX) layer formed during a semiconductor substrate[3]. SOI MOSFET devices square measure custom-made to be used by the pc trade. The buried oxide layer will be utilized in SRAM memory designs[4]. There square measure 2 kind of SOI devices: PDSOI (partially depleted SOI) and FDSOI (fully depleted SOI) MOSFETs. For a n-type PDSOI MOSFET the sandwiched p-type film between the gate oxide (GOX) and buried oxide (BOX) is massive, therefore the depletion region cannot cowl the total p region. Thus to some extent PDSOI behaves like bulk MOSFET. Noticeably there square measure some benefits over the majority MOSFETs. The film is incredibly skinny in FDSOI devices so the depletion region covers the total film. In FDSOI the front gate (GOX) supports less depletion charges than the majority thus a rise in inversion charges happens leading to higher switch speeds. Alternative drawbacks in bulk MOSFETs, like threshold voltage spiel off, higher sub-threshold slop body impact, etc. square measure reduced in FDSOI since the supply and drain electrical fields cannot interfere owing to the BOX. The most drawback in PDSOI is that the "floating body impact (FBE)" since the film isn't connected to any of the provides.

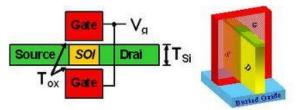

## **II. Double Gate MOSFET**

As CMOS scaling is forthcoming its restrictions, double gate MOSFET (Figure 2) is generating marvelous attention as a potential choice to the conservative bulk MOSFET[5]. Associate analytic model for metric weight unit MOSFET can facilitate the circuit style cluster of individuals to assess metric weight unit MOSFET and build use of it in numerous applications [5]. Currently,

**Copyright to IJIRSET**

#### www.ijirset.com

M.R. Thansekhar and N. Balaji (Eds.): ICIET'14

Figure 1: SOI MOSFET Structure

May possibly be a semiconductor on dielectric (SOI) MOSFET structure during which a semi all the models address solely common gate (both gates tied together) operation of a Symmetric undoped device. There's a powerful ought to develop a model for a doped Symmetric common device.

A perturbation approach is employed to resolve the Poisson's equation of a finite-doped Symmetric metric weight unit electronic transistor. To progress the speed of model analysis, analytical estimate is employed to guage the surface potential. The consequence on surface potential owing to poly-depletion impact and quantum confinement is completely shapely.

Figure 2: Symmetric common DG-MOSFET Structure

DGT is comprised of a conducting channel (usually undoped), enclosed by gate electrodes on either facet. This ensures that no a part of the channel is way off from a gate conductor. The voltage applied on the gate terminals controls the electrical field, determinative the quantity of current flow through the channel. The foremost common mode of operation is to modify each gate at the same time. Another mode is to modify only 1 gate and apply a bias to the second gate (this is termed

devices.

"ground plane" (GP) or "back-gate"(BG)) . The advantage of DG-MOSFET is as follows:

1) Reduction of short channel effects (SCE) 2) Maintaining smart electrical characteristics High  $I_{ON}/I_{OFF}$ magnitude relation a. 3) Keeping fabrication method easy

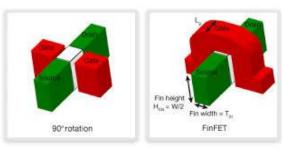

#### **III. FINFET**

Figure 3: structure of FINFET

The term FinFET was coined by University of American state, Berkeley researchers (Profs. Chenming Hu, Tsu-Jae King-Liu and Jeffrey Bokor) to explain a nonplanar, double-gate electronic transistor engineered on associate SOI substrate, supported the previous DELTA (singlegate) electronic transistor style. The distinctive feature of the FinFET is that the conducting channel is wrapped by a skinny semiconductor "fin" that forms the body of the device. The thickness of the fin (measured within the direction from supply to drain) determines the effective channel length of the device. In current usage the term FinFET features a less actual definition. Among silicon chip makers, AMD, IBM, and Motorola describe their double-gate development efforts as FinFET extension whereas Intel avoids mistreatment the term to explain their closely connected tri-gate design.[7] within the scientific journalism. FinFET is employed somewhat unremarkably to explain any fin-based, multigate electronic transistor design despite of variety of gates[6].

A 25-nm electronic transistor operative on simply zero.7 V was confirmed in Dec 2002 by Taiwan Semiconductor producing Company. The "Omega FinFET" style is called when the similarity between the Greek letter omega ( $\Omega$ ) and also the type during which the gate wraps round the source/drain structure. it's a gate

delay of simply zero.39 time unit (ps) for the N-type electronic transistor and zero.88 annotation for the Ptype.FinFET may have 2 electrically freelance gates, which provides circuit designers a lot of suppleness to style with economical, low-power gates.[8]In 2012, Intel started mistreatment FinFETs for its forthcoming business devices. Hot leaks suggest that Intel's FinFET form features an uncommon form of a triangle instead of parallelogram and it's speculated that this can be either as a result of a triangle features a higher structural strength and may be a lot of faithfully factory-made or as a result of a prism has a higher space to volume magnitude relation than an oblong prism therefore increasing switch performance.[9] Sept 2012, international Foundries declared plans to supply a 14-nanometer method technology that includes FinFET three-dimensional transistors in 2014. ensuing month, the contestant company TSMC, declared begin early or "risk" fabrication of sixteen nm FinFETS in Gregorian calendar month 2013. The fin structure MOSFET could be a device during which the short channel effects square measure suppressed to boost properties like current drivability and threshold voltage stability by incorporating a threedimensional structure to the channel. it's a bonus of being come-at-able by standard planing machine process technology in contrast to alternative three-dimensional

There square measure 2 minor variants of the FinFET, namely, the omega-gate FinFET and also the pigate FinFET, that square measure named following the form of the overlapping gate over the fin. within the case of the omega-gate FinFET, the gate undercuts and partly covers very cheap surface of the fin yet, whereas within the case of the pi-gate FinFET, the gate extends to a depth below very cheap of the semiconductor fin. The target of those structures is to realize an extra gate management over the channel and stop fringing fields from penetrating into the semiconductor body.

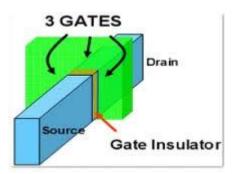

#### **IV.TRI-GATE MOSFET**

Tri-gate or 'Transistor (not to be confused with 3D microchips) production is employed by Intel Corporation for the nonplanar electronic transistor design utilized in English ivy Bridge and Haswell processors. These transistors take up one gate stacked on high of 2 vertical gates leaving essentially 3 times the area for electrons to

## **Copyright to IJIRSET**

www.ijirset.com

785

travel. Intel reports that their tri-gate transistors decrease leak and consume way less power than current transistors [7]. This enables up to thirty seventh higher speed, or power consumption at underneath five hundredth of the previous kind of transistors utilized by Intel. Intel explains, "The further management permits the maximum amount current flowing as potential once the transistor is within the 'on' state (for performance), and as shut to zero as potential once it's within the 'off' state (to minimize power), and permits the electronic transistor to modify terribly quickly between the 2 states (again, for performance)." Intel has explicit that each one product when Sandy Bridge are going to be primarily based upon this style. Intel was the primary company to announce this technology. In Sept 2002, Intel declared their creation of 'Triple-Gate Transistors' to use 'transistor switch performance and reduces power-wasting leakage'. A year later in Sept 2003, AMD declared it absolutely was engaged on similar technology at the International Conference on Solid State Devices and Materials. Any announcements of this technology were created till Intel's announcement in might 2011 albeit it absolutely was explicit at IDF 2011, that they established a operating SRAM chip supported this technology at IDF 2009. On April twenty three, 2012 Intel free a replacement line of CPUs, termed English ivy Bridge, that feature tri-gate transistors. Intel has been engaged on its tri-gate design since 2002; however it took till 2011 to figure out production problems. The new variety of electronic transistor was represented on might four, 2011, in city. Intel factories square measure expected to form upgrades over 2011 and 2012 to be able to manufacture the English Bridge CPUs. ivy As well as being employed in Intel's English ivy Bridge chips for desktop PCs, the new transistors will be utilized in Intel's Atom chips for low powered devices. The term tri-gate is usually used generically to denote any multigate electronic transistor with 3 effective gates or channels.

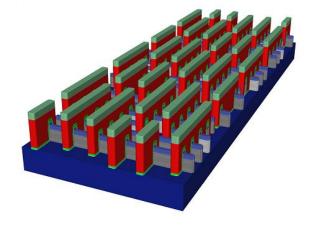

Figure4 : Trigate Structure

Figure 5: Multigate structure

#### V. GATE-ALL-AROUND (GAA) MOSFET

Gate-all-around FETs square measure comparable in model to FinFETs excluding that the gate material surrounds the channel region on all sides[8]. Looking on style, gate-all-around FETs will have 2 or four effective gates. Gate-all-around FETs are with success engineered around a semiconductor nanowire. and engraved InGaAs nanowires.

**Copyright to IJIRSET**

www.ijirset.com

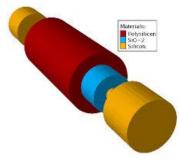

Figure 6: GAA MOSFET Structure

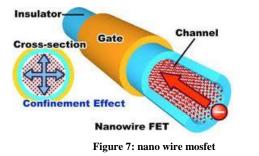

#### VI. NANOWIRE MOSFET

Nanowire MOSFETs with whole close gate square measure presently well thought-out united of the promising solutions for commutation bulk (single-gate) devices and continued MOSFET scaling within the nm scale [9][11]. The most good thing about this design is to supply a unbreakable electricity coupling between the physical phenomenon channel and also the gate conductor, that considerably reduces short-channel effects (SCE) compared to standard bulk devices. Then, the constraints on channel doping levels will be snug and nanowire MOSFET devices will be deliberate with intrinsic (pure Si) channels. This offers hefty benefits, particularly in terms of quality and removal of doping fluctuations. The intrinsic channel may be valuable with observe to source-to-drain transport owing to the high probability of flight transport.

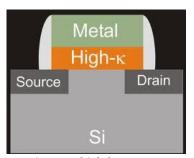

#### VII. HIGH-K DIELECTRICS

At the moment, the target is to scale down the MOSFET since we tend to square measure toward the within during a new era of even smaller devices. Ideally we tend to might scale down all parameter and also the applied voltages with constant scaling issue k associated increase the doping profile by k; this may result in an unchanged threshold swing. but this can't be done owing to physical and technological limitations. However, there square measure some physical and technical limitations, such us:Cannot scale down the inbuilt junction voltage and also the surface potential;Forthcoming the nanoscale for the oxide thickness implies a rise within the defects; Reduction on the drain and supply ends up in a rise within the drain and supply resistance; Taking in issues the contact breakdown we tend to can't increase indefinitely the doping profile.

Owing to all limitations alternative scaling models are proposed: constant-voltage scaling, quasi-constantvoltage scaling, generalized scaling and versatile scaling issue. Within the last one, we will modification specific parameters severally as long because the general behavior remains the same [10]. additionally the advance of some technologies have given a facilitate, such the employment of high-k dielectrics for gate dielectrics which might relax the physical thickness up the defect density and reducing the sector for tunneling[12]; MOSFET engineered on a awfully skinny body 3D structure can decrease considerably the physical phenomenon path for punch-through.

As a part of device scaling in semiconductor, the oxide thickness should be reduced to a couple of nm. Scaling the oxide thickness ends up in a big quantity of leak current owing to tunneling. For that reason, new high k insulator materials rather than SiO2 square measure needed. However, the narrower band gap of high-k materials cancels the good thing about the high insulator constant. Therefore, an acceptable trade-off between the insulator constant and also the physical phenomenon band offset is that the 1st criterion for high-k insulator candidates would like.

# **Copyright to IJIRSET**

## www.ijirset.com

787

#### A SURVEY ON MULTI GATE MOSFETs...

Figure 8 :high-k MOSFET

## VII. CONCLUSION

This paper summarizes the most recent trends within the style of MOSFET so as to mitigate the short channel effects & quantum effects. The multigate structures like metric weight unit, Trigate, and GAA mosfets have mentioned. The trend towards the necessity of other insulator materials additionally mentioned.

#### REFERENCES

G. E. Moore, "Cramming more components onto integrated circuits", *Proceedings of the IEEE*, vol. 86, no. 1, pp. 82-85, 1998.

"International Technology Roadmap for Semiconductors (ITRS)",

[3] S. Cristoloveanu, "Future trends in SOI technologies," *Journal of*

[3] S. Cristoloveanu, "Future trends in SOI technologies," *Journal of the Korean Physical Society*, vol. 39, pp. S52-S55, Dec 2001.

[4] A. Breed and K.P. Roenker, "Dual-gate (FinFET) and TriGate MOSFETs: Simulation and design," *Proceedings of the International Semiconductor Device Research Symposium (ISDRS-2003)*, pp. 150-151, December 2003.

[5] J-T. Park and J-P Colinge, "Multiple-Gate SOI MOSFETs: Device Design Guidelines," *IEEE Transactions on Electron Devices*, pp. 2222-2228, vol. 49, no. 12, Dec. 2002.

[6] Aniket Breed and Kenneth P. Roenker, "A Small-signal, RF Simulation Study of Multiple-gate MOSFET Devices," *IEEE Topical Meeting on Silicon Monolithic ICs in RF Systems*, Atlanta, GA, Sept. 2004.

[7] A. Breed and K.P. Roenker, "Dual-gate (FinFET) and TriGate MOSFETs: Simulation and design," *Proceedings of the International Semiconductor Device Research Symposium (ISDRS-2003)*, pp. 150-151, December 2003.

[8] J-T. Park and J-P Colinge, "Multiple-Gate SOI MOSFETs: Device Design Guidelines," *IEEE Transactions on Electron Devices*, pp. 2222-2228, vol. 49, no. 12, Dec. 2002.

[9] Aniket Breed and Kenneth P. Roenker, "A Small-signal, RF Simulation Study of Multiple-gate MOSFET Devices," *IEEE Topical Meeting on Silicon Monolithic ICs in RF Systems*, Atlanta, GA, Sept. 2004.

[10] Biswajit Ray, Santanu Mahapatra "A New Threshold Voltage Model for Omega Gate Cylindrical Nanowire Transistor", 21st International Conference on VLSI Design, 1063-9667/08, DOI 10.1109/VLSI.2008.52, page 447-452.

## **Copyright to IJIRSET**

#### www.ijirset.com

788

# M.R. Thansekhar and N. Balaji (Eds.): ICIET'14

[11] Cong Li, Yiqi Zhuang, Ru Han "Cylindrical surrounding-gate MOSFETs with electrically induced source/drain extension", Microelectronics Journal

[12] F. M. Bufler et al., "Comparison of Semiclassical Transport Formulations Including Quantum Corrections for Advanced Devices with High-K Gate stacks", Proceeding of 14th IWCE 2010, Pisa, Italy, pp. 319-322 (2010).