DIGITAL ELECTRONICS

By:ÁÖ¦ ÉÓ @eà ÁOEÁP ÉOŠËP ã# Electrical Engineering Department

### V@ Counters

#### Upon completion of the chapter, students should be able to:

- F.1 Understand the basic concepts of asynchronous counter and synchronous counters, and the difference between them.

- F.1.1 Draw circuit and Timing Diagram of Asynchronous Counters

- F.1.2 Interpret the Operation and Application of an asynchronous counter

- F.1.3 Draw circuit and timing diagram of synchronous counters

- F.1.4 Interpret the operation and application of synchronous up/down counters.

- F.1.5 Describe how the counters in F.1.1 and F.1.3 can be connected in cascade to produce higher mod

- F.1.6 Explain the application of counters in Digital Clock

# Introduction – ÁCOUNTERS

- A *counter* is a register that goes through a <u>predetermined</u> <u>sequence of states upon the application of clock pulses.</u>

- Asynchronous counters

- Synchronous counters

- Asynchronous Counters (or *Ripple counters*)

- the clock signal (CLK) is only used to clock the first FF.

- Each FF (except the first FF) is clocked by the preceding FF.

- Synchronous Counters,

- the clock signal (CLK) is applied to all FF, which means that all FF shares the same clock signal,

- thus the output will change at the same time.

DIGITAL ELECTRONICS

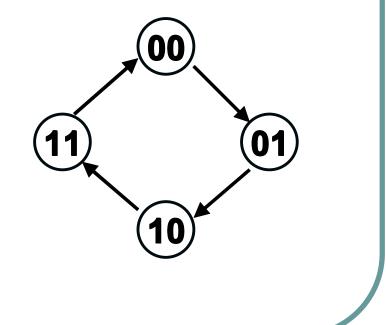

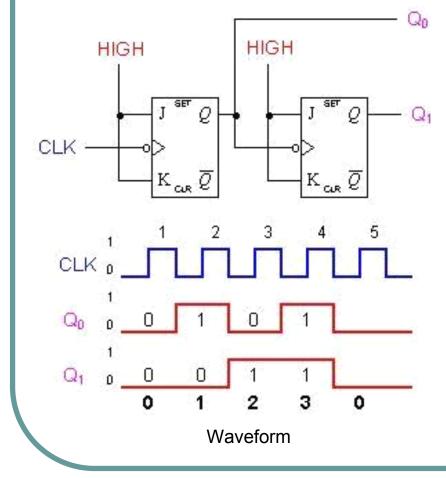

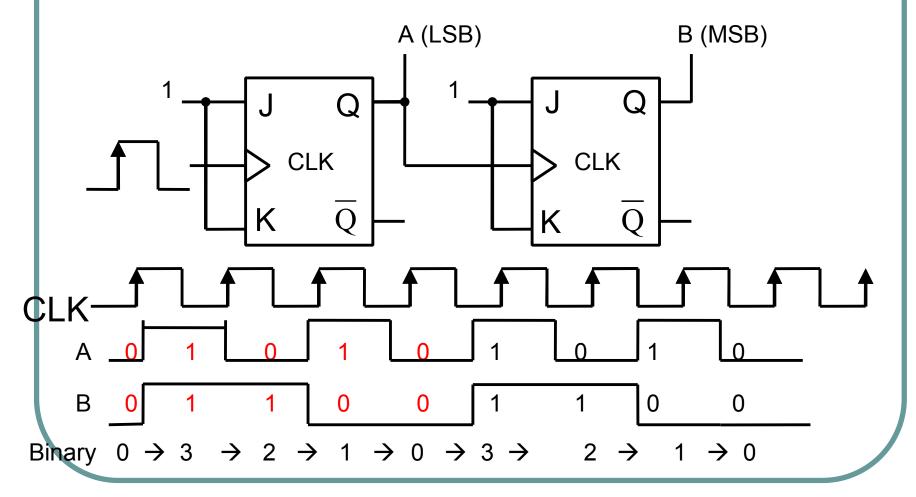

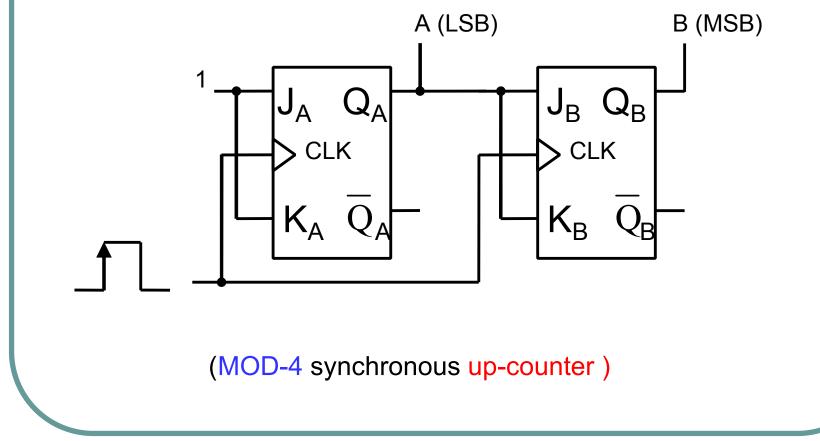

The Asynchronous Counter that counts 4 number starts from 00→01→10→11 and back to 00 is called MOD-4 Ripple (Asynchronous) Up-Counter.

#### • Next state table and state diagram

| Present State | Next State |

|---------------|------------|

| $Q_1Q_0$      | $Q_1Q_0$   |

| 00            | 01         |

| 01            | 10         |

| 10            | 11         |

| 11            | 00         |

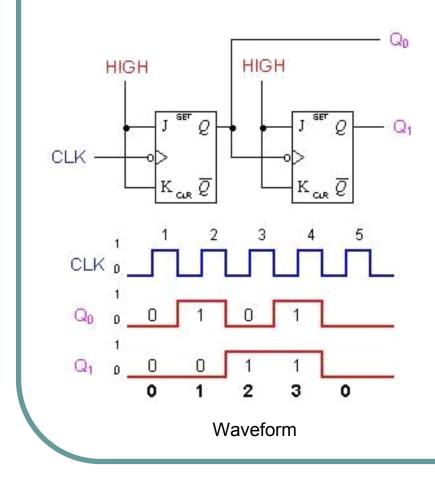

Figure F.1 : MOD 4 Asynchronous Up Counter

- A two-bit asynchronous counter is shown on the left. The external clock is connected to the clock input of the first flip-flop (FF0) only. So, FF0 changes state at the falling edge of each clock pulse, but FF1 changes only when triggered by the falling edge of the Q output of FF0.

- Note that for simplicity, the transitions of Q0, Q1 and CLK in the timing diagram above are shown as simultaneous even though this is an asynchronous counter. Actually, there is some small delay between the CLK, Q0 and Q1 transitions.

- Because of the inherent propagation delay through a flip-flop, the transition of the input clock pulse and a transition of the Q output of FF0 can never occur at exactly the same time. Therefore, the flip-flops cannot be triggered simultaneously, producing an asynchronous operation.

- The 2-bit ripple counter circuit shown has four different states, each one corresponding to a count value.

Similarly, a counter with *n* flip-flops can have 2 to the power n states. (2<sup>n</sup>) The number of states in a counter is known as its mod (modulo) number.

Thus a 2-bit counter is a mod-4 counter.

Figure F.1 : MOD 4 Asynchronous Up Counter

- Usually, all the CLEAR inputs are connected together, so that a single pulse can clear all the flip-flops before counting starts. The clock pulse fed into FF0 is rippled through the other counters after propagation delays, like a ripple on water, hence the name Ripple Counter

- A mod-n counter may also described as a divide-by-*n* counter. This is because the most significant flip-flop (the furthest flip-flop from the original clock pulse) produces one pulse for every *n* pulses at the clock input of the least significant flip-flop (the one triggers by the clock pulse).

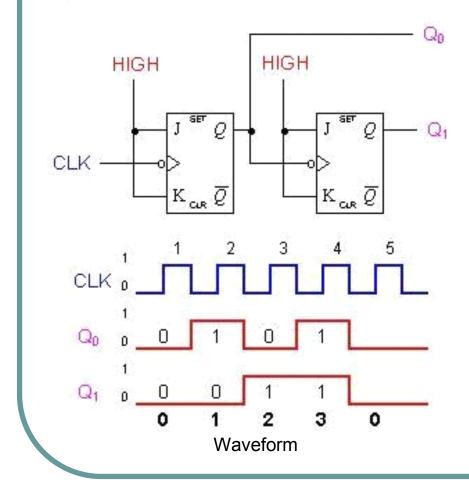

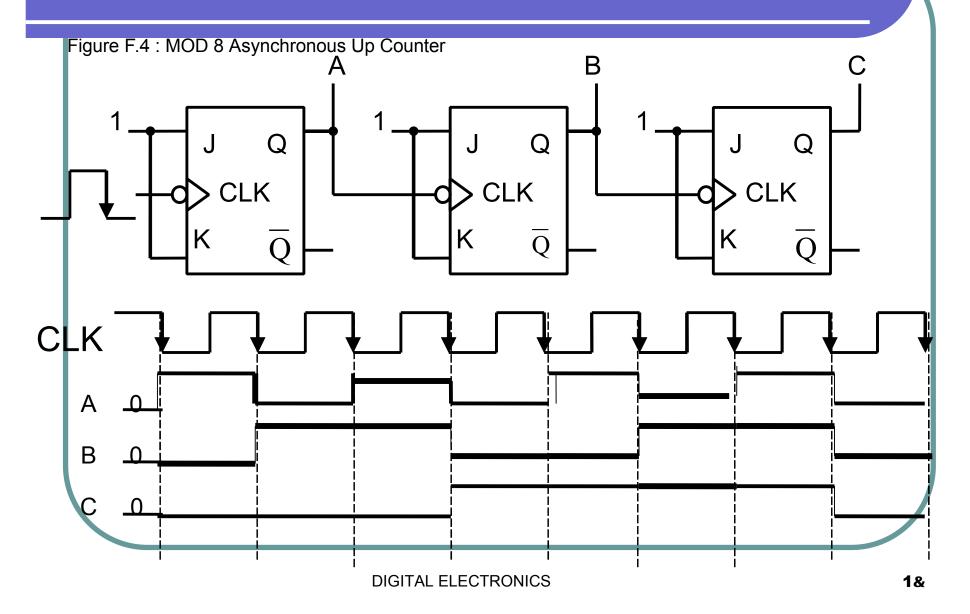

# MOD 8 Asynchronous Up Counter

- The following is a three-bit asynchronous binary counter and its timing diagram for one cycle.

- It works exactly the same way as a twobit asynchronous binary counter mentioned above, except it has eight

states due to the third flip-flop.

## MOD 8 Asynchronous Up Counter

Figure F.3a Next State Table

| Present State | Next State |

|---------------|------------|

| СВА           | СВА        |

| 000           | 001        |

| 001           | 010        |

| 010           | 011        |

| 011           | 100        |

| 100           | 101        |

| 101           | 110        |

| 110           | 111        |

| 111           | 000        |

# Exercise :

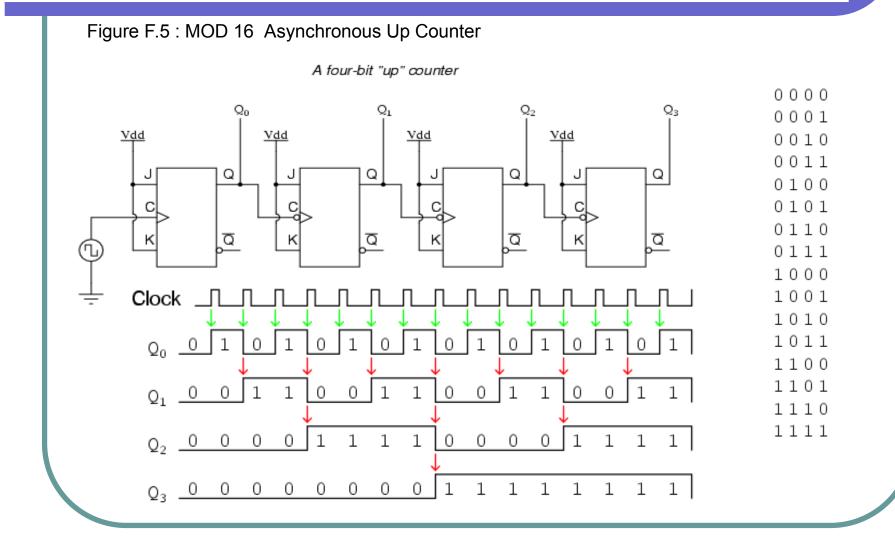

#### MOD 16 Asynchronous Up counter – (Negative Triggered)

DIGITAL ELECTRONICS

#### MOD 16 Asynchronous Up counter (Positive Triggered)

Figure F.6 : MOD 16 Asynchronous Up Counter

A different way of making a four-bit "up" counter

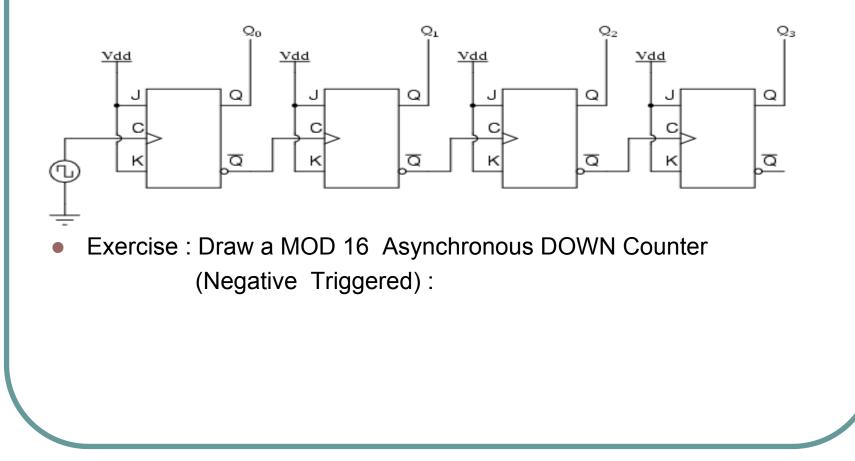

# Asynchronous DOWN Counter

Figure F.7 : MOD 4 or 2-bit Asynchronous down counter

### • Exercise:

- Design a MOD-4 ripple down-counter

- Design a MOD-8 ripple down counter using negative triggered.

- Design a MOD-16 ripple down counter using positive triggered.

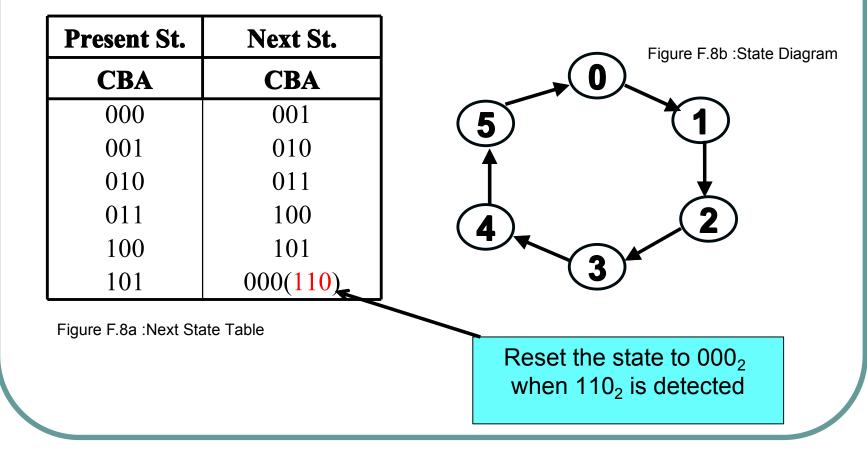

### Asynchronous Counters (MOD $\neq 2^{N}$ )

- So far, we have design the counters with MOD number equal to 2<sup>N</sup>, where N is the number of bit (N = 1,2,3,4....) (also correspond to number of FF)

- Thus, the counters are limited on for counting MOD-2, MOD4, MOD-8, MOD-16 etc..

- The question is how to design a MOD-5, MOD-6, MOD-7, MOD-9 which is not a MOD-2<sup>N</sup> (MOD ≠ 2<sup>N</sup>)?

- MOD-6 counters will count from 0<sub>10</sub> (000<sub>2</sub>) to 5<sub>10</sub>(101<sub>2</sub>) and after that will recount back to 0<sub>10</sub> (000<sub>2</sub>) continuously.

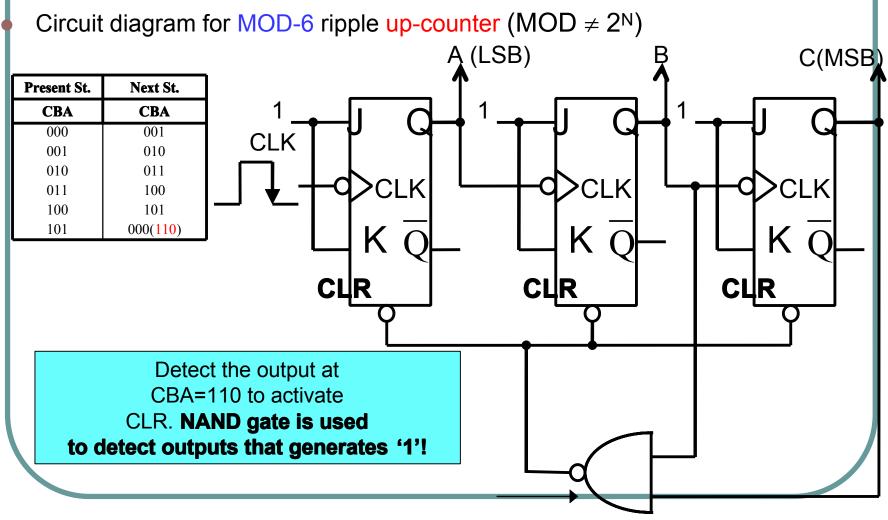

### Asynchronous Counters (MOD $\neq 2^{N}$ )

#### MOD-6 ripple up-counter (MOD $\neq 2^{N}$ )

### Asynchronous Counters (MOD $\neq 2^{N}$ )

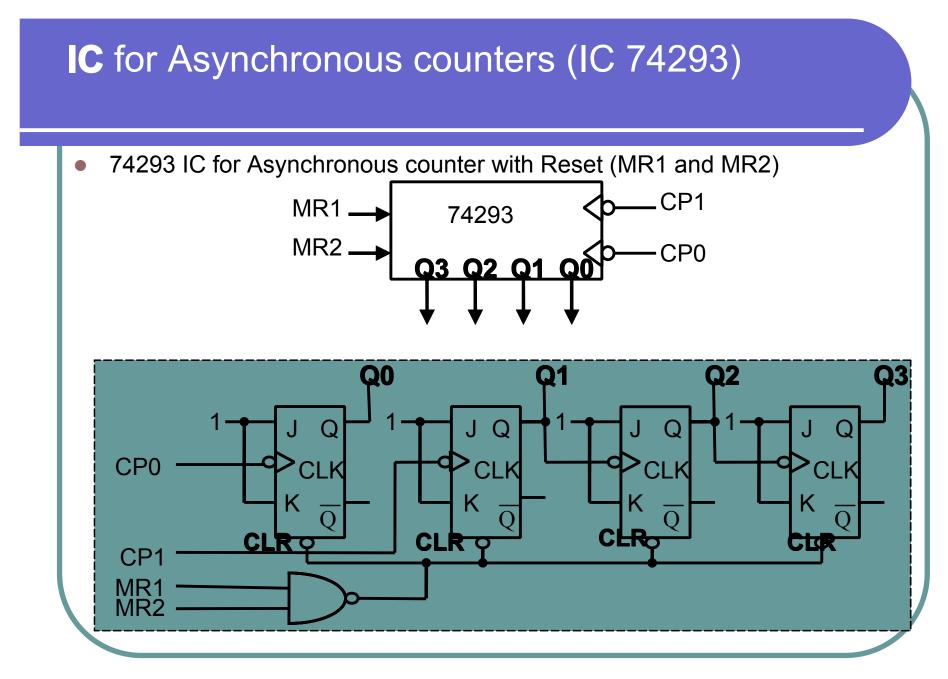

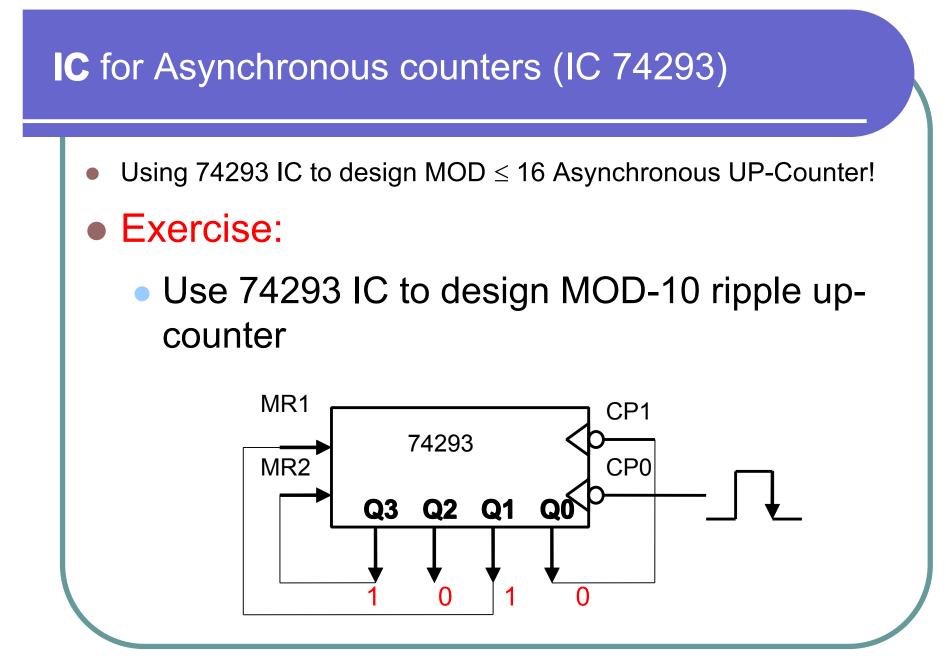

#### IC for Asynchronous counters (IC 74293)

#### Exercise:

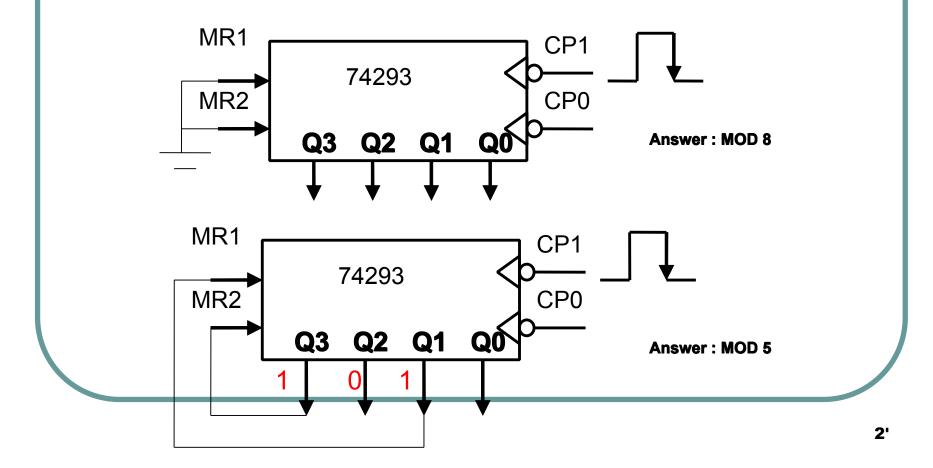

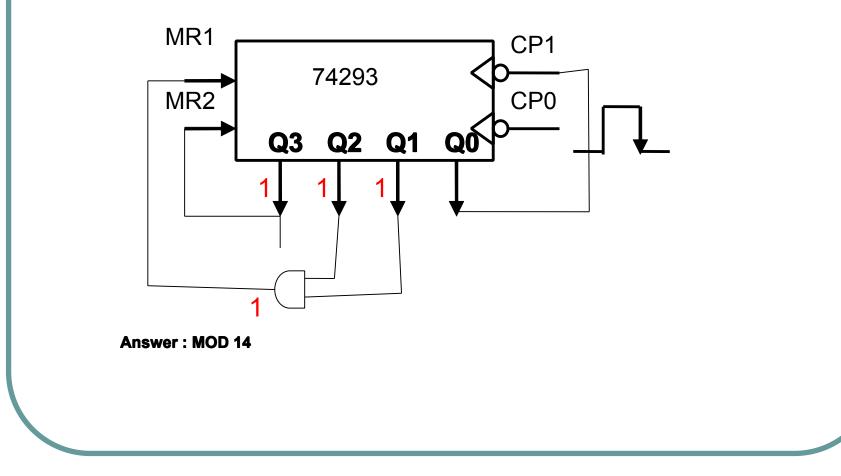

• Determine the MOD for each configuration shown below?

#### IC for Asynchronous counters (IC 74293)

Determine the MOD for configuration shown below?

### IC for Asynchronous counters (IC 74293)

#### **CASCADE** connection to produce Higher Mod

Exercise : Design Asynchronous counters MOD-60 using IC 74293.

Solution : Discuss with your Lecturer in class.

Exercise : i. Design Asynchronous counters MOD-55 using IC 74293.

ii. Design Asynchronous counters MOD-

1000 using IC 74293.

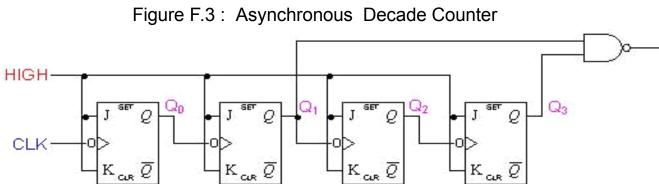

## **Asynchronous Decade Counters**

- The binary counters previously introduced have two to the power *n* states. But counters with states less than this number are also possible. They are designed to have the number of states in their sequences, which are called truncated sequences. These sequences are achieved by forcing the counter to recycle before going through all of its normal states.

- A common modulus for counters with truncated sequences is ten. A counter with ten states in its sequence is called a *decade counter*. The circuit below is an implementation of a decade counter.

## **Asynchronous Decade Counters**

• The sequence of the decade counter is shown in the table below:

| Clock Pulse | Q3 | 02  | Q1 | Q0-  |

|-------------|----|-----|----|------|

| 0           | 0  | 0   | 0  | 0    |

|             | 0  | -0  | 0  | mh-1 |

| 2           | 0  | 0-  | -1 | -0   |

| 3           | 0  | 0   |    |      |

| 4           | 0  | 1   | -0 | 0    |

| 5           | 0  | 1   | 0  |      |

| 6           | 0  | 1   | -1 | 0    |

|             | 0  | 1   | -1 | ···· |

| 8           |    | - 0 | 0  | 0    |

| 9           | 1  | 0   | 0  | 1 -  |

Figure F.4 : True Table Asynchronous Decade Counter

Once the counter counts to ten (1010), all the flip-flops are being cleared. Notice that only Q1 and Q3 are used to decode the count of ten. This is called partial decoding, as none of the other states (zero to nine) have both Q1 and Q3 HIGH at the same time.

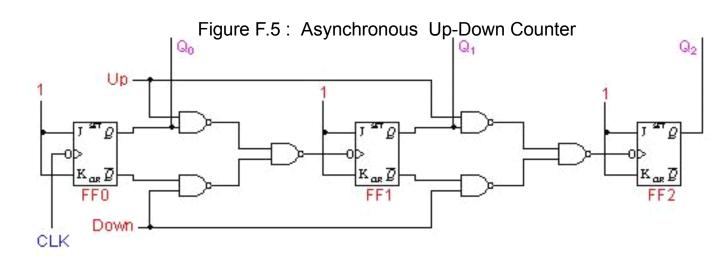

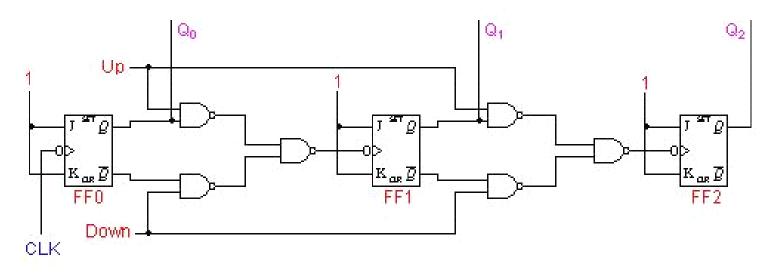

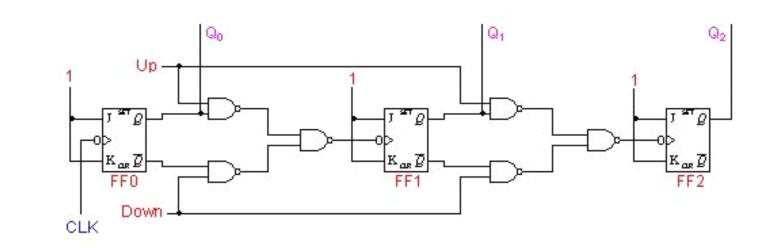

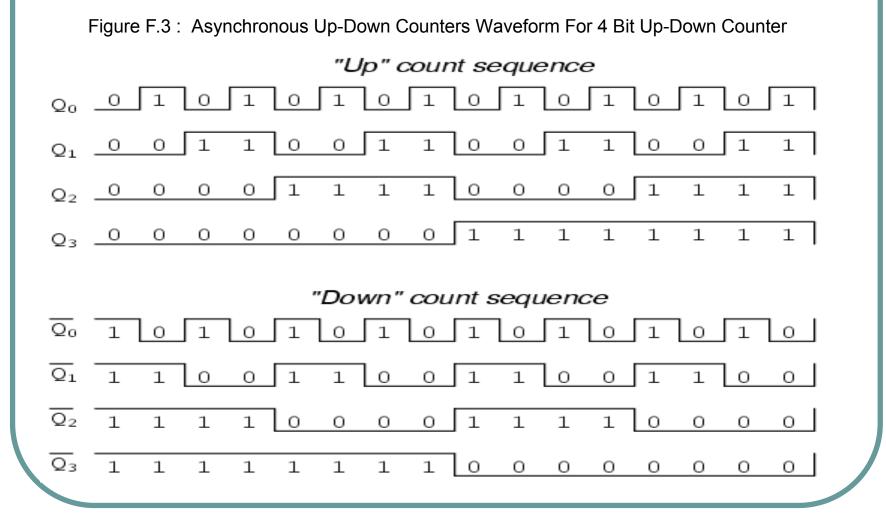

In certain applications a counter must be able to count both up and down. The circuit below is a 3-bit up-down counter. It counts up or down depending on the status of the control signals UP and DOWN. When the UP input is at 1 and the DOWN input is at 0, the NAND network between FF0 and FF1 will gate the non-inverted output (Q) of FF0 into the clock input of FF1. Similarly, Q of FF1 will be gated through the other NAND network into the clock input of FF2. Thus the counter will count up.

• When the control input UP is at 0 and DOWN is at 1, the inverted outputs of FF0 and FF1 are gated into the clock inputs of FF1 and FF2 respectively. If the flip-flops are initially reset to 0's, then the counter will go through the following sequence as input pulses are applied.

Notice that an asynchronous up-down counter is slower than an up counter or a down counter because of the additional propagation delay introduced by the NAND networks.

- Disadvantages of Asynchronous Counters:-

- Propagation delay is severe for larger MOD of counters, especially at the MSB.

- Existence of 'glitch' is inevitable for MOD  $\neq 2^{N}$  counters.

- Cannot design random counters (i.e:- to design circuit that counts numbers in these sequence

5→6→7→2→3→1→5→6→7→2→3→1→5→6....)

Solution, use *SYNCHRONOUS COUNTERS*.

DIGITAL ELECTRONICS

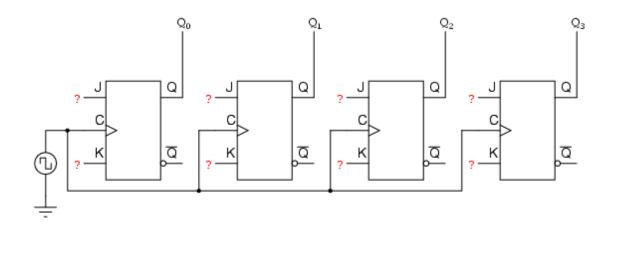

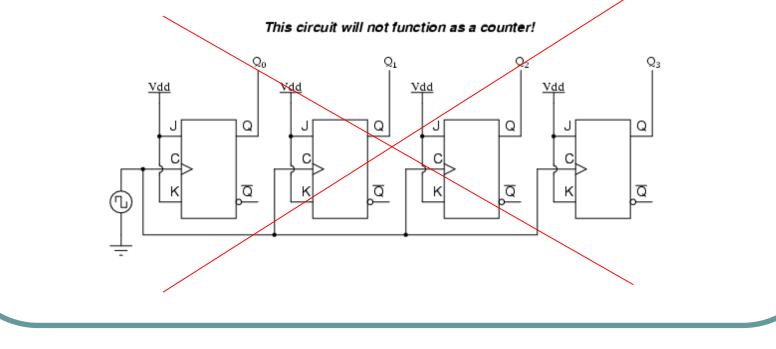

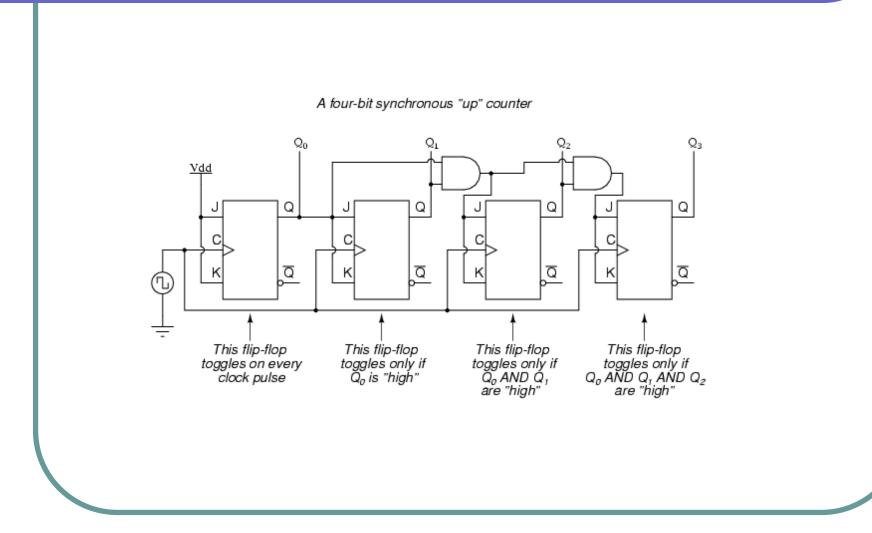

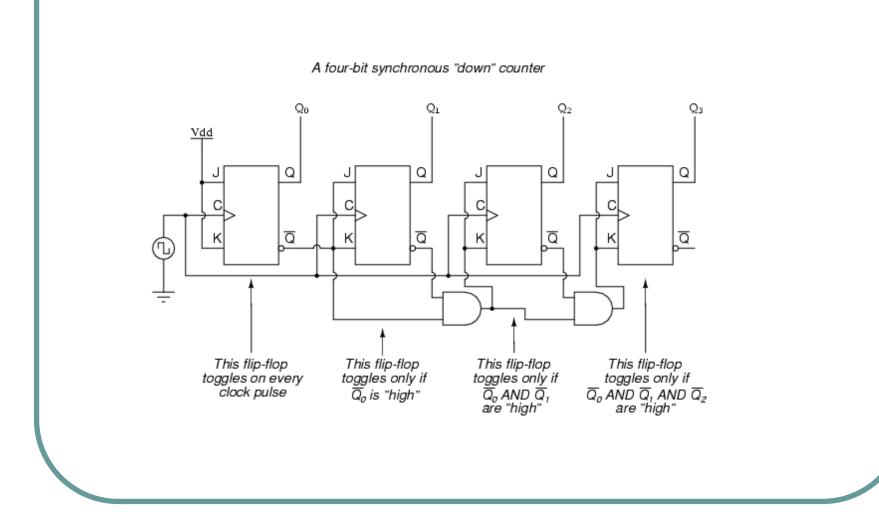

A synchronous counter, in contrast to an asynchronous counter, is one whose output bits change state simultaneously, with no ripple. The only way we can build such a counter circuit from J-K flip-flops is to connect all the clock inputs together, so that each and every flip-flop receives the exact same clock pulse at the exact same time:

Now, the question is, what do we do with the J and K inputs? We know that we still have to maintain the same divide-by-two frequency pattern in order to count in a binary sequence, and that this pattern is best achieved utilizing the "toggle" mode of the flip-flop, so the fact that the J and K inputs must both be (at times) "high" is clear. However, if we simply connect all the J and K inputs to the positive rail of the power supply as we did in the asynchronous circuit, this would clearly not work because all the flip-flops would toggle at the same time: with each and every clock pulse!

# Synchronous Counters

- For synchronous counters, all the flip-flops are using the same CLOCK signal. Thus, the output would change synchronously.

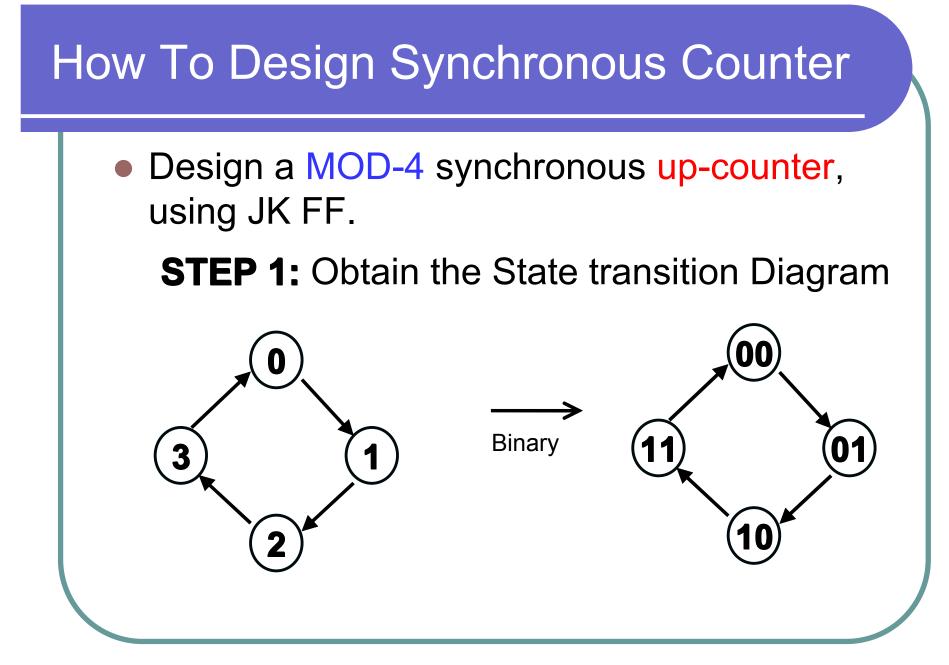

- Procedure to design synchronous counter are as follows:-

**STEP 1**: Obtain the State Diagram.

- **STEP 2**: Obtain the Excitation Table using state transition table for any particular FF (JK or D). Determine number of FF used.

- **STEP 3:** Obtain and simplify the function of each FF input using K-Map.

**STEP 4:** Draw the circuit.

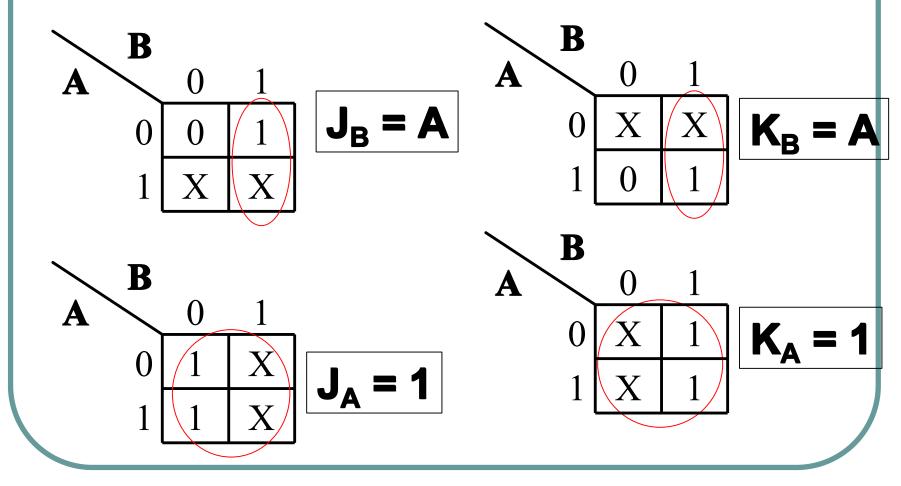

**STEP 2:** Obtain the Excitation table. Two JK FF are used.

| <b>OUTPUT TRANSITION</b>                              | FF INPUT |

|-------------------------------------------------------|----------|

| $\mathbf{Q}_{\mathbf{N}}$ $\mathbf{Q}_{\mathbf{N+1}}$ | J K      |

| $0 \rightarrow 0$                                     | 0 X      |

| $0 \rightarrow 1$                                     | 1 X      |

| $1 \rightarrow 0$                                     | X 1      |

| $1 \rightarrow 1$                                     | X 0      |

Excitation table

| Pr | esent State | Next State | Inpu                          | ut, J K                       |

|----|-------------|------------|-------------------------------|-------------------------------|

|    | BA          | BA         | J <sub>B</sub> K <sub>B</sub> | J <sub>A</sub> K <sub>A</sub> |

|    | 0 0         | 0 1        | 0 X                           | 1 X                           |

|    | 0 1         | 1 0        | 1 X                           | X 1                           |

|    | 1 0         | 1 1        | X 0                           | 1 X                           |

|    | 1 1         | 0 0        | X 1                           | X 1                           |

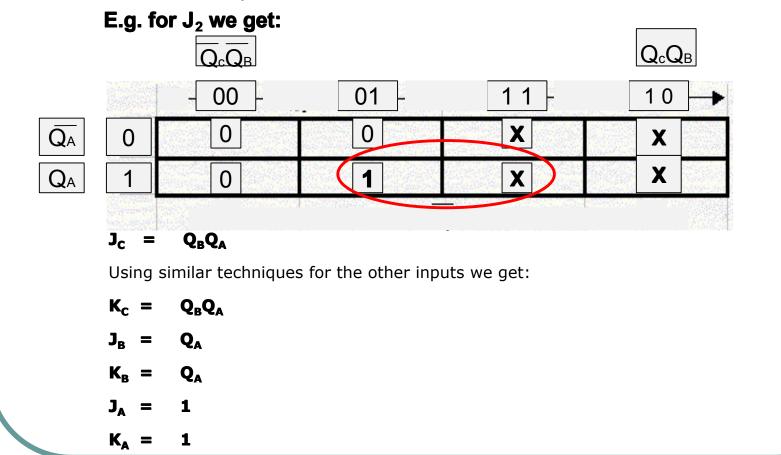

**STEP 3:** Obtain the simplified function using K-Map

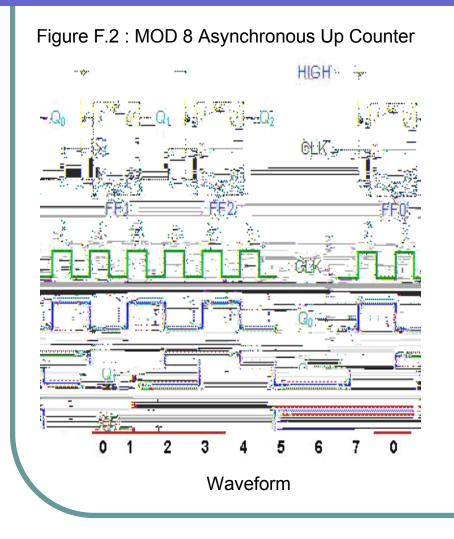

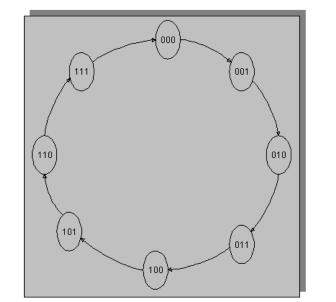

- Let us employ these techniques to design a MOD-8 counter to count in the following sequence: 0, 1, 2, 3, 4, 5, 6, 7.

- Step1: Determined Flip Flop Used and Creating state transition diagram. (Rajah Keadaan)

$$N = 2^{n}$$

$$8 = 2^{n}$$

$$n = \log 8 / \log 2$$

$$= 3 \operatorname{Flip} \operatorname{Flop} (3 \operatorname{Bit})$$

$$M = 2^{n} - 1$$

NI

$$= 2^3 - 1 = 8 - 1 = 7$$

N = Modulo/MODn = Flip Flop Used M = Maximum Number To Be Count

• **Step 2:** Creating present state-next state table

| P                     | resent S   | state      | Next State            |            |    |  |  |

|-----------------------|------------|------------|-----------------------|------------|----|--|--|

| <b>Q</b> <sub>2</sub> | <b>Q</b> 1 | <b>Q</b> o | <b>Q</b> <sub>2</sub> | <b>Q</b> 1 | Qo |  |  |

| 0                     | 0          | 0          | 0                     | 0          | 1  |  |  |

| 0                     | 0          | 1          | 0                     | 1          | 0  |  |  |

| 0                     | 1          | 0          | 0                     | 1          | 1  |  |  |

| 0                     | 1          | 1          | 1                     | 0          | 0  |  |  |

| 1                     | 0          | 0          | 1                     | 0          | 1  |  |  |

| 1                     | 0          | 1          | 1                     | 1          | 0  |  |  |

| 1                     | 1          | 0          | 1                     | 1          | 1  |  |  |

| 1                     | 1          | 1          | 0                     | 0          | 0  |  |  |

$$Q_0 = Q_A$$

$$Q_1 = Q_B$$

$$Q_2 = Q_c$$

• Step 3: Expand the present state-next state table to form the transition table.

| Excitation Table<br>( <i>Jadual Ujaan Flip Flop<br/>JK</i> ) |   |   |   |  |  |  |  |  |  |

|--------------------------------------------------------------|---|---|---|--|--|--|--|--|--|

| Q                                                            | Q | J | K |  |  |  |  |  |  |

| 0                                                            | 0 | 0 | Х |  |  |  |  |  |  |

| 0                                                            | 1 | 1 | Х |  |  |  |  |  |  |

| 1                                                            | 0 | Х | 1 |  |  |  |  |  |  |

| 1                                                            | 1 | Х | 0 |  |  |  |  |  |  |

'X' indicates a "don't care" condition.

|   |                       |                |                       |                       |                |                       | _                             |                               |                               |  |

|---|-----------------------|----------------|-----------------------|-----------------------|----------------|-----------------------|-------------------------------|-------------------------------|-------------------------------|--|

|   |                       | resei<br>State | -                     | Next State            |                |                       | Present inputs                |                               |                               |  |

|   | <b>Q</b> <sub>C</sub> | Q <sub>B</sub> | <b>Q</b> <sub>A</sub> | <b>Q</b> <sub>C</sub> | Q <sub>B</sub> | <b>Q</b> <sub>A</sub> | J <sub>c</sub> K <sub>c</sub> | J <sub>B</sub> K <sub>B</sub> | J <sub>A</sub> K <sub>A</sub> |  |

|   | 0                     | 0              | 0                     | 0                     | 0              | 1                     | 0X                            | 0X                            | 1X                            |  |

|   | 0                     | 0              | 1                     | 0                     | 1              | 0                     | 0X                            | 1X                            | X1                            |  |

|   | 0                     | 1              | 0                     | 0                     | 1              | 1                     | 0X                            | X0                            | 1X                            |  |

|   | 0                     | 1              | 1                     | 1                     | 0              | 0                     | 1X                            | X1                            | X1                            |  |

|   | 1                     | 0              | 0                     | 1                     | 0              | 1                     | X0                            | 0X                            | 1X                            |  |

| _ | 1                     | 0              | 1                     | 1                     | 1              | 0                     | X0                            | 1X                            | X1                            |  |

|   | 1                     | 1              | 0                     | 1                     | 1              | 1                     | X0                            | X0                            | 1X                            |  |

|   | 1                     | 1              | 1                     | 0                     | 0              | 0                     | X1                            | X1                            | X1                            |  |

|   |                       |                |                       |                       |                |                       |                               |                               |                               |  |

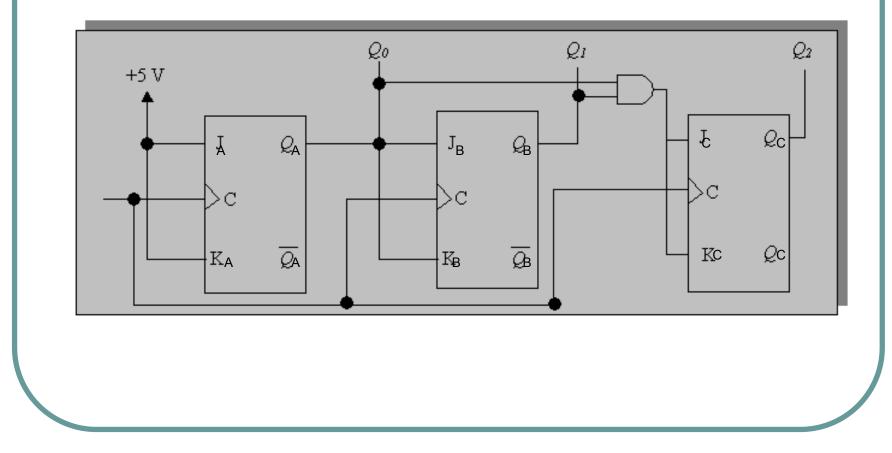

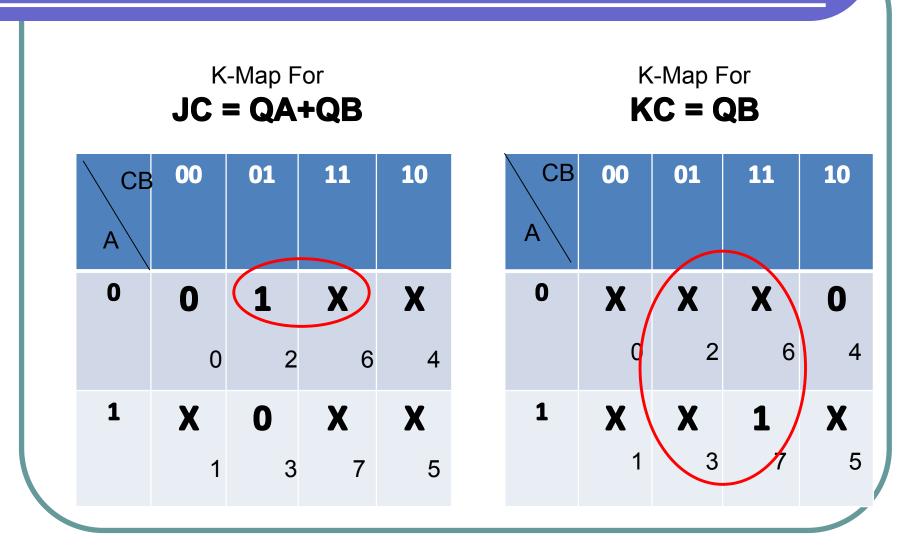

• **Step 4:** Use Karnaugh maps to identify the present state logic functions for each of the inputs.

• **Step 5:** Constructing Circuit

# How To Design Synchronous Counter that count Random number

#### Example :

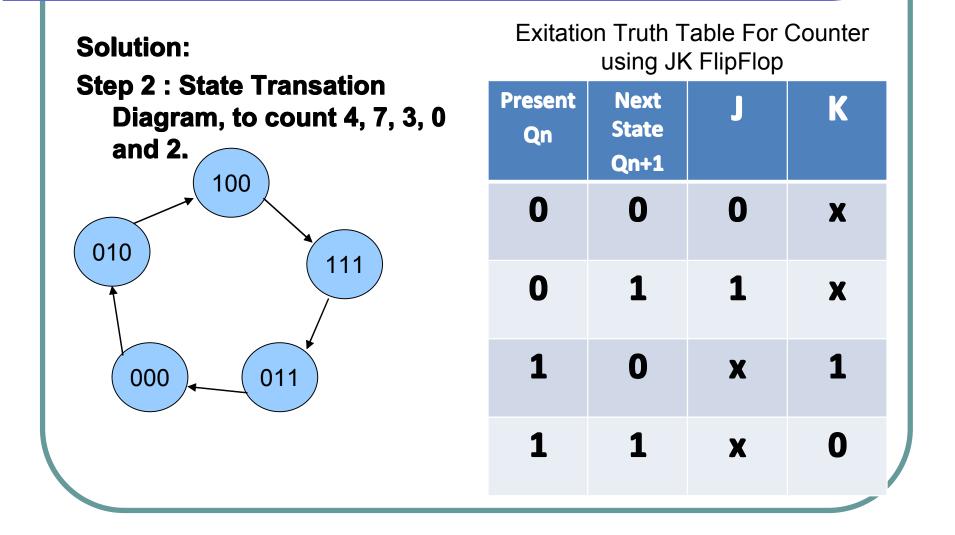

Design a Synchronous Counter to Count 4,7,3,0 and 2 respectively using JKFlip Flop negative trigered by showing:

- i. Flip Flop Used

- ii. State Transition Diagram

- iii. Exitation Table / Present state, next State

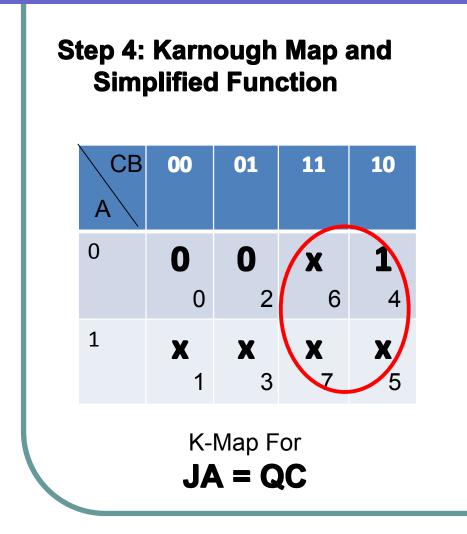

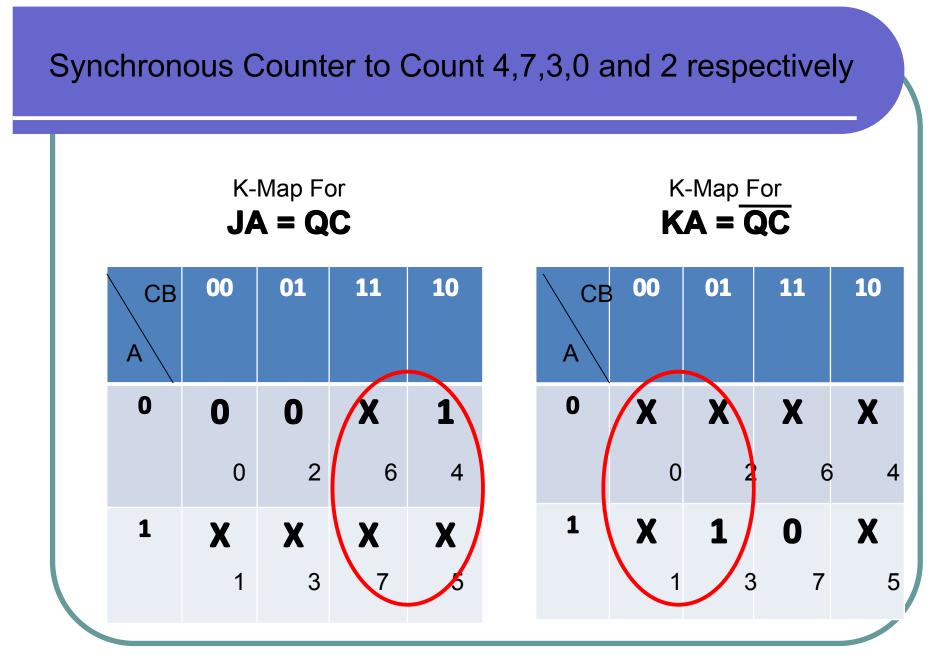

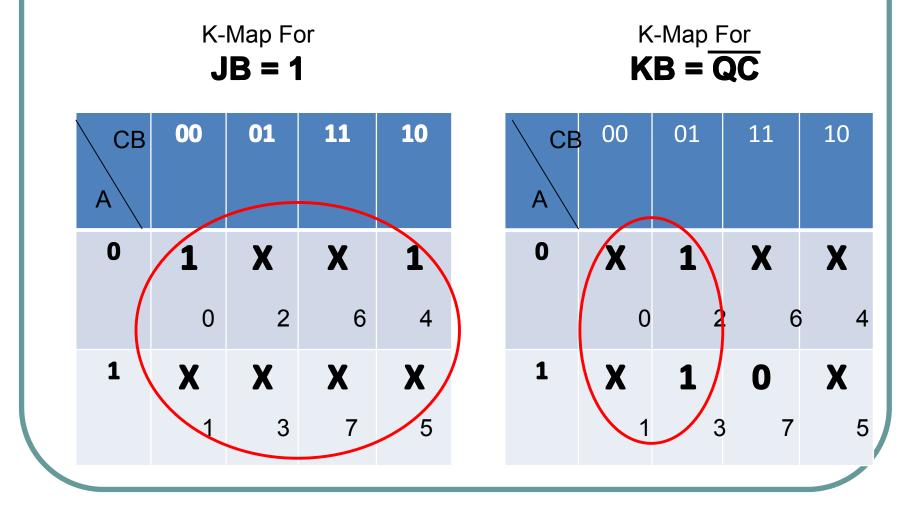

- iv. Karnough Map & perform Simplified Function

- v. The Synchronous Counter

**Solution:** Step 1 : Flip Flop Used Find Modulo, N= 2<sup>n</sup> M = 7,  $M = 2^{n} - 1 = 7$  $2^{n} = N$ , so, N = 7+1 = 8, **MOD 8**  $2^{n} = 8$ , n = log 8 / log 2 n = 3 bit = 3 Flip Flop.

| Step        | 3 : Ex           | <b>litatic</b> | on Tal | ble /p | reser  | nt Sta | ite, N | ext S | tate |    |    |    |

|-------------|------------------|----------------|--------|--------|--------|--------|--------|-------|------|----|----|----|

| Deci<br>mal | Present<br>State |                |        | Ne     | xt Sta | ate    | JC     | KC    | JB   | KB | JA | KA |

|             | QC               | QB             | QA     | QC     | QB     | QA     |        |       |      |    |    |    |

| 4           | 1                | 0              | 0      | 1      | 1      | 1      | Х      | 0     | 1    | Х  | 1  | х  |

| 7           | 1                | 1              | 1      | 0      | 1      | 1      | x      | 1     | X    | 0  | X  | 0  |

| 3           | 0                | 1              | 1      | 0      | 0      | 0      | 0      | Х     | Х    | 1  | Х  | 1  |

| 0           | 0                | 0              | 0      | 0      | 1      | 0      | 0      | Х     | 1    | Х  | 0  | Х  |

| 2           | 0                | 1              | 0      | 1      | 0      | 0      | 1      | Х     | Х    | 1  | 0  | Х  |

**61** - --m Table Imma and Otata Nard Otata

## **Step 5 : Perform Counter Circuit** By using simplified function from K-Map, **JA = QC**, KA = QC,JB = 1, KB = QC, JC = QA + QB, KC = QB**'1' / Vdd** JA JB QB $Q_{A'}$ Jc Qc Kc Qc KB QB **CP, CLOCK PULSE**

Exercises:

Design a counter to count in the following sequence: 6, 4. 2, 3, 1.

Design a counter to count in the following sequence: 15,9,11,5,2,13,1.

Do more exercises in Past Years Exam Paper.

End Of This Topic.....