# 9. Synopsys PrimeTime Support

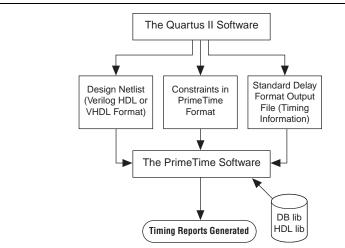

PrimeTime is the Synopsys stand-alone full chip, gate-level static timing analyzer. The Quartus<sup>®</sup> II software makes it easy for designers to analyze their Quartus II projects using the PrimeTime software. The Quartus II software exports a netlist, design constraints (in the PrimeTime format), and libraries to the PrimeTime software environment. Figure 9–1 shows the PrimeTime flow diagram.

#### Figure 9–1. PrimeTime Software Flow Diagram

This chapter contains the following sections:

- "Quartus II Settings for Generating the PrimeTime Software Files"

- "Files Generated for the PrimeTime Software Environment" on page 9–2

- "Running the PrimeTime Software" on page 9–6

- "PrimeTime Timing Reports" on page 9–7

- "Static Timing Analyzer Differences" on page 9–18

# **Quartus II Settings for Generating the PrimeTime Software Files**

To set up the Quartus II software to generate files for the PrimeTime software, perform the following steps:

- 1. In the Quartus II software, on the Assignments menu, click **Settings**, and then click **EDA Tool Settings**.

- 2. In the Category list, under EDA Tool Settings, select Timing Analysis.

- 3. In the **Tool name** list, select **PrimeTime**, and in the **Format for output netlist** list, select either **Verilog** HDL or **VHDL**.

<sup>© 2010</sup> Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX are Reg. U.S. Pat. & Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries. All other trademarks and service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

When you compile your project after making these settings, the Quartus II software runs the EDA Netlist Writer to create three files for the PrimeTime software. These files are saved in the *<revision\_name>/timing/primetime* directory by default, where *<revision\_name>* is the name of your Quartus II software revision. If it is not, you have used the wrong variable name.

# Files Generated for the PrimeTime Software Environment

The Quartus II software generates a flattened netlist, a Standard Delay Output File (.sdo), and a Tcl script that prepares the PrimeTime software for timing analysis of the Quartus II project. These files are saved in the *<project directory*/timing/primetime directory.

The Quartus II software uses the EDA Netlist Writer to generate PrimeTime files based on either the Classic Timing Analyzer or the TimeQuest Timing Analyzer static timing analysis results. When you run the EDA Netlist Writer, the PrimeTime **.sdo** files are based on delays generated by the currently selected timing analysis tool in the Quartus II software.

To specify the timing analyzer, on the Assignments menu, click **Settings**. The **Settings** dialog box appears. Under **Category**, click **Timing Analysis Settings**. Select the timing analyzer of your choice.

For more information about specifying the Quartus II timing analyzers, refer to either the *Quartus II Classic Timing Analyzer* or the *Quartus II TimeQuest Timing Analyzer* chapter in volume 3 of the *Quartus II Handbook*. Also, refer to the *Switching to the Quartus II TimeQuest Timing Analyzer* chapter in volume 3 of the *Quartus II Handbook* to help you decide which timing analyzer is most appropriate for your design.

# **The Netlist**

Depending on whether **Verilog HDL** or **VHDL** is selected as the **Format for output netlist** option, in the **Tool name** list on the **Timing Analysis** page of the **Settings** dialog box, the netlist is written and saved as either *<project name>.vo* or *<project name>.vho*, respectively. This file contains the flattened netlist representing the entire design.

IP

When you select the TimeQuest analyzer, only a Verilog HDL PrimeTime netlist can be generated.

## The .sdo File

The Quartus II software saves the **.sdo** file as either *<revision\_name>\_v.sdo* or *<revision\_name>\_v.sdo*, depending on whether you select **Verilog HDL** or **VHDL** in the **Tool name** list on the **Timing Analysis** page of the **Settings** dialog box.

This file contains the timing information for each timing path between any two nodes in the design.

When you enable the Classic Timing Analyzer, the slow-corner (worst-case) timing models are used by default when generating the **.sdo** file. To generate the **.sdo** file using the fast-corner (best-case) timing models, perform the following steps:

- 1. In the Quartus II software, on the Processing menu, point to **Start** and click **Start Classic Timing Analyzer (Fast Timing Model)**.

- After the fast-corner timing analysis is complete, on the Processing menu, point to Start and click Start EDA Netlist Writer to create a <revision\_name>\_v\_fast.sdo or <revision\_name>\_vhd\_fast.sdo file, which contains the best-case delay values for each timing path.

If you are running a best-case timing analysis, the Quartus II software generates a Tcl script similar to the following: <*revision\_name*>\_**pt\_v\_fast.tcl**.

When the TimeQuest analyzer is run with the fast-corner netlist, or when the **Optimize fast-corner timing** check box is selected in the **Fitter Settings** dialog box, the fast-corner Synopsys Design Constraints File (**.sdc**) file is generated.

After the EDA Netlist Writer has finished, two **.sdc** files are created: <*revision\_name>\_v\_sdo* (slow corner) and *<revision\_name>\_v\_fast.sdo* (fast corner).

## Generating Multiple Operating Conditions with the TimeQuest Analyzer

You can specify different operating conditions to the EDA Netlist Writer for PrimeTime analysis. The different operating conditions are reflected in the .**sdo** file generated by the EDA Netlist Writer.

From the TimeQuest analyzer console pane, use the command get\_available\_operating\_conditions to obtain a list of available operating conditions for the target device.

The following steps show how to generate the .**sdo** files for the three different operating conditions for a Stratix III design. Enter each command at the command prompt.

- The --tq2pt option for quartus\_sta is required only if the project does not specify that the PrimeTime tool is be used as the timing analysis tool.

- 1. Generate the first slow-corner model at the operating conditions: slow, 1100 mV, and  $85^{\circ}$  C.

quartus\_sta --model=slow --voltage=1100 --temperature=85 <project name>

2. Generate the fast-corner model at the operating conditions: fast, 1100 mV, and 0° C.

quartus\_sta --model=fast --voltage=1100 --temperature=0

--tq2pt <project name>

3. Generate the PrimeTime output files for the corners specified above. The output files are generated in the **primetime\_two\_corner\_files** directory.

```

quartus_eda --timing_analysis --tool=primetime

--format=verilog

--output_directory=primetime_two_corner_files

--write settings files=off <project name>

```

4. Generate the second slow-corner model at the operating conditions: slow, 1100 mV, and 0° C.

```

quartus_sta --model=slow --voltage=1100 --temperature=0

--tq2pt <project name>

```

5. Generate the PrimeTime output files for the second slow corner. The output files are generated in the **primetime\_one\_slow\_corner\_files** directory.

```

quartus_eda --timing_analysis --tool=primetime

--format=verilog

--output_directory=primetime_one_slow_corner_files

--write_settings_files=off $revision

```

To summarize, the previous steps generate the following files for the three operating conditions:

- First slow corner (slow, 1100 mV, 85° C):

.vo file—primetime\_two\_corner\_files/<project name>.vo

.sdo file—primetime\_two\_corner\_files/<project name>\_v.sdo

- Fast corner (fast, 1100 mV, 0° C):

.vo file—primetime\_two\_corner\_files/<project name>.vo

.sdo file—primetime\_two\_corner\_files/<project name>\_v\_fast.sdo

- Second slow corner (slow, 1100 mV, 0° C):

.vo file—primetime\_one\_slow\_corner\_files/<project name>.vo

.sdo file—primetime\_one\_slow\_corner\_files/<project name>\_v.sdo

- The **primetime\_one\_slow\_corner\_files** directory may also have files for fast corner. These files can be ignored because they were already generated in the **primetime\_two\_corner\_files** directory.

# **The Tcl Script**

The Tcl script generated by the Quartus II software contains information required by the PrimeTime software to analyze the timing and set up your post-fit design. This script specifies the search path and the names of the PrimeTime database library files provided with the Quartus II software. The search\_path and link\_path variables are defined at the beginning of the Tcl file. The link\_path variable is a space-delimited list that contains the names of all database files used by the PrimeTime software.

Depending on whether you select **Verilog** HDL or **VHDL** in the **Format for output netlist** list on the **Timing Analysis** page of the **Settings** dialog box, when the Classic Timing Analyzer is enabled, the EDA Netlist Writer generates and saves the script as either <*revision\_name>\_pt\_v.tcl* or <*revision\_name>\_pt\_vhd.tcl*.

To access the EDA Settings dialog box, perform the following:

- 1. On the Assignments menu, click Settings, and then click EDA Tool Settings

- 2. Expand EDA Tool Settings under the Category list.

In the dialog box, you can specify VHDL or Verilog HDL for the format of the output netlist.

The script also directs the PrimeTime software to use the *<device family>\_all\_pt.v* or *<device family>\_all\_pt.vhd* file, which contains the Verilog HDL or VHDL description of library cells for the targeted device family.

Example 9–1 shows the search\_path and link\_path variables defined in the Tcl script:

#### Example 9–1. Sample PrimeTime Setup Script

```

set quartus_root "altera/quartus/"

set search_path [list . [format "%s%s" $quartus_root "eda/synopsys/primetime/lib"] ]

set link_path [list * stratixii_lcell_comb_lib.db stratixii_lcell_ff_lib.db

stratixii_asynch_io_lib.db stratixii_io_register_lib.db stratixii_termination_lib.db

bb2_lib.db stratixii_ram_internal_lib.db stratixii_memory_register_lib.db

stratixii_memory_addr_register_lib.db stratixii_mac_out_internal_lib.db

stratixii_lvds_receiver_lib.db stratixii_lvds_transmitter_lib.db

stratixii_rublock_lib.db stratixii_pll_lib.db stratixii_dll_lib.db alt_vtl.db]

read_vhdl _-vhdl_compiler stratixii_all_pt.vhd

```

The EDA Netlist Writer converts any Classic Timing Analyzer timing assignments to the PrimeTime software constraints and exceptions when it generates the PrimeTime files. The converted constraints are saved to the Tcl script. The Tcl script also includes a PrimeTime software command that reads the **.sdo** file generated by the Quartus II software. You can place additional commands in the Tcl script to analyze or report on timing paths.

Table 9–1 shows some examples of timing assignments converted by the Quartus II software for the PrimeTime software. For example, the set\_input\_delay -max command sets the input delay on an input pin.

Table 9–1. Equivalent Quartus II and PrimeTime Software Constraints

| Quartus II Equivalent                                                | PrimeTime Constraint                                                                        |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Clock defined on input pin, clock of 10 ns period and 50% duty cycle | create_clock -period 10.000 -waveform {0 5.000} \<br>[get_ports clk] -name clk              |

| Input maximum delay of 1 ns on input pin, din                        | set_input_delay -max -add_delay 1.000 -clock \<br>[get_clocks clk] [get_ports din]          |

| Input minimum delay of 1 ns on input pin, din                        | set_input_delay -min -add_delay 1.000 -clock \<br>[get_clocks clk] [get_ports din]          |

| Output maximum delay of 3 ns on output pin, out                      | <pre>set_output_delay -max -add_delay 3.000 -clock \ [get_clocks clk] [get_ports out]</pre> |

When the TimeQuest analyzer is turned on, the EDA Netlist Writer generates and saves the script as *<revision\_name>.pt.tcl*.

The EDA Netlist Writer converts all TimeQuest analyzer **.sdc** constraints and exceptions into compatible PrimeTime software constraints and exceptions when it generates the PrimeTime files. The constraints and exceptions are saved to the <*revision\_name*>.constraints.sdc file.

## **Generated File Summary**

The files that are generated by the EDA Netlist Writer for the PrimeTime software depend on the Quartus II timing analysis tool you select.

Table 9–2 shows the files that are generated for the PrimeTime software when the Classic Timing Analyzer is selected.

| File                                                                                       | Description                                                                                                                                                                                                                  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| <revision_name>.<b>vho</b>  <br/><revision_name>.<b>vo</b></revision_name></revision_name> | The PrimeTime software output netlist. Either a VHDL Output File ( <b>.vho</b> ) or a Verilog Output File ( <b>.vo</b> ) is generated, depending on the output netlist language set.                                         |  |  |  |  |  |  |

| <revision_name>_vhd.sdo  <br/><revision_name>_v.sdo</revision_name></revision_name>        | The PrimeTime software standard delay file. Either a VHDL Standard Delay Output File ( <b>vhd.sdo</b> ) or a Verilog Standard Delay Output File ( <b>v.sdo</b> ) is generated, depending on the output netlist language set. |  |  |  |  |  |  |

| <revision_name>_pt_vhd.tcl  <br/><revision_name>_pt_v.tcl</revision_name></revision_name>  | PrimeTime setup and constraint script. Either a VHDL Tcl Script File ( <b>vhd.tcl</b> ) or a Verilog Tcl Script File ( <b>v.tcl</b> ) is generated, depending on the output netlist language set.                            |  |  |  |  |  |  |

Table 9–3 shows the files that are generated for the PrimeTime software when the TimeQuest analyzer is selected. The EDA Netlist Writer supports the output netlist format only when the TimeQuest analyzer is enabled.

Table 9–3. TimeQuest Timing Analyzer-Generated PrimeTime Files

| File                                                                                   | Description                                                                                                                    |

|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| <revision_name>.vo</revision_name>                                                     | The PrimeTime software output netlist. When the TimeQuest analyzer is enabled, only PrimeTime (Verilog HDL) is supported.      |

| <revision_name>_v.sdo  <br/><revision_name>_v_fast.sdo</revision_name></revision_name> | The PrimeTime software standard delay file. When the TimeQuest analyzer is enabled, only PrimeTime (Verilog HDL) is supported. |

| <revision_name>.pt.tcl</revision_name>                                                 | PrimeTime setup and constraint script. When the TimeQuest analyzer is enabled, only PrimeTime (Verilog HDL) is supported.      |

| <revision_name>.collections.sdc</revision_name>                                        | Contains the mapping from the TimeQuest analyzer netlist to the PrimeTime netlist.                                             |

| <revision_name>.constraints.sdc</revision_name>                                        | Contains the converted TimeQuest analyzer constraints for the PrimeTime software.                                              |

# **Running the PrimeTime Software**

The PrimeTime software runs only on UNIX operating systems. If the Quartus II output files for the PrimeTime software were generated by running the Quartus II software on a PC/Windows-based system, follow these steps to run the PrimeTime software using Quartus II output files:

1. Install the PrimeTime libraries on a UNIX system by installing the Quartus II software on UNIX.

The PrimeTime libraries are located in the *<Quartus II installation directory>***/eda/synopsys/primetime/lib** directory.

2. Copy the Quartus II output files to the appropriate UNIX directory. You may need to run a PC to UNIX program, such as dos2unix, to remove any control characters.

3. Modify the Quartus II path in Tcl scripts to point to the PrimeTime libraries using the first line of Example 9–1:

```

set quartus_root "altera/quartus/" set search_path [list . [format

"%s%s" $quartus_root "eda/synopsys/primetime/lib"] ]

```

# **Analyzing Quartus II Projects**

The PrimeTime software is controlled with Tcl scripts and can be run through pt\_shell. You can run the <*revision\_name>\_pt\_v.tcl* script file. For example, type the following at a UNIX system command prompt:

```

pt_shell -f <revision_name>_pt_v.tcl ←

```

When the TimeQuest analyzer is selected, type the following at a UNIX system command prompt:

pt\_shell -f <revision\_name>.pt.tcl ←

After all Tcl commands in the script are interpreted, the PrimeTime software returns control to the pt\_shell prompt, which allows you to use other commands.

# **Other pt\_shell Commands**

You can run additional pt\_shell commands at the pt\_shell prompt, including the man program. For example, to read documentation about the report\_timing command, type the following at the pt\_shell prompt:

```

man report_timing 🕶

```

You can list all commands available in pt\_shell by typing the following at the pt\_shell prompt:

help 🖊

Type quit ← at the pt\_shell prompt to close pt\_shell.

You can also run pt\_shell without a script file by typing pt\_shell at the UNIX command line prompt.

# **PrimeTime Timing Reports**

This section describes PrimeTime timing reports.

# Sample PrimeTime Software Timing Report

After running the script, the PrimeTime software generates a timing report. If the timing constraints are not met, Violated is displayed at the end of the timing report. The timing report also gives the negative slack.

The PrimeTime software timing report is similar to the sample shown in Example 9–2. The starting point in this report is a register clocked by clock signal, clock, and the endpoint is another register, inst3-I.lereg.

Example 9–2. Hold Path Report in PrimeTime

| <pre>Startpoint: inst2~I.lereg<br/>(rising edge-triggered flip-flop clocked by<br/>Endpoint: inst3~I.lereg<br/>(rising edge-triggered flip-flop clocked by<br/>Path Group: clock<br/>Path Type: min</pre>                                                                                                                                                                                                                                                                              |                  |                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------|

| Point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Incr             | Path                                                                               |

| <pre>clock clock (rise edge)<br/>clock network delay (propagated)<br/>inst2~I.lereg.clk (stratix_lcell_register)<br/>inst2~I.lereg.regout (stratix_lcell_register) &lt;<br/>inst2~I.regout (stratix_lcell)<br/>inst3~I.datac (stratix_lcell)<br/>inst3~I.lereg.datac (stratix_lcell_register)<br/>data arrival time<br/>clock clock (rise edge)<br/>clock network delay (propagated)<br/>inst3~I.lereg.clk (stratix_lcell_register)<br/>library hold time<br/>data required time</pre> | 0.000*<br>0.000* | 3.166<br>3.166r<br>3.342r<br>3.342r<br>6.755r<br>6.755<br>0.000<br>3.002<br>3.002r |

| data required time<br>data arrival time                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  | 3.102<br>-6.755                                                                    |

| slack (MET)                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  | 3.653                                                                              |

# Comparing Timing Reports from the Classic Timing Analyzer and the PrimeTime Software

Both the Classic Timing Analyzer and the TimeQuest analyzer generate a static timing analysis report for every successful design compilation. The timing report lists all of the timing paths in your design that were analyzed, and indicates whether these paths have met or violated their timing requirements. Violations are reported only if timing constraints were specified.

The TimeQuest analyzer and PrimeTime use an equivalent set of equations when reporting the static timing analysis results for a design. However, the Classic Timing Analyzer uses slightly different reporting equations when reporting the static timing analysis results for a design. This section describes the differences between the Classic Timing Analyzer and the PrimeTime software.

The timing report generated by the Classic Timing Analyzer differs from the report generated by the PrimeTime software. Both tools provide the same data, but the data is presented in different formats. The following sections show how the PrimeTime software reports the following slack values differently from the Classic Timing Analyzer report:

- "Clock Setup Relationship and Slack" on page 9–9

- "Clock Hold Relationship and Slack" on page 9–12

- "Input Delay and Output Delay Relationships and Slack" on page 9–16

## **Clock Setup Relationship and Slack**

The Classic Timing Analyzer performs a setup check that ensures that the data launched by source registers is latched correctly at the destination registers. The Classic Timing Analyzer does this by determining the data arrival time and clock arrival time at the destination registers, and compares this data with the setup time delay of the destination register. Equation 9–1 expresses the inequality that is used for a setup check. The data arrival time includes the longest path from the clock to the source register, the clock-to-out micro delay of the source register, and the longest path from the source register to the destination register. The clock arrival time is the shortest delay from the clock to the destination register.

#### Equation 9-1.

Clock Arrival – Data Arrival  $\geq$  t<sub>su</sub>

Slack is the margin by which a timing requirement is met or not met. Positive slack indicates the margin by which a requirement is met. Negative slack indicates the margin by which a requirement is not met. The Classic Timing Analyzer determines the clock setup slack, as shown in Equation 9–2:

#### Equation 9-2.

Clock Setup Slack = Largest Register-to-Register Requirement – Longest Register-to-Register Delay

The longest register-to-register delay in the previous equation is equal to the register-to-register data delay.

#### Equation 9-3.

Largest Register-to-Register Requirement = Setup Relationship between Source and Destination + Largest Clock Skew – Micro  $t_{co}$  of Destination Register – Micro  $t_{su}$  of Destination Register

Setup Relationship between Source and Destination = Latch Edge – Launch Edge

Clock Skew = Shortest Clock Path to Destination - Longest Clock Path to Source

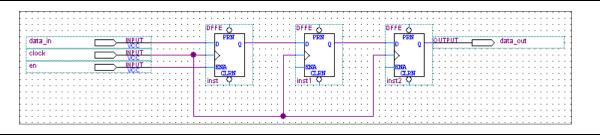

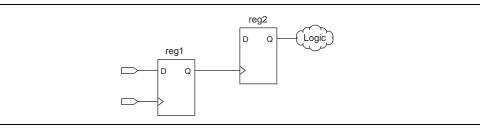

Figure 9–2 shows a simple three-register design.

Figure 9–2. Simple Three-Register Design

The Classic Timing Analyzer generates a report for the design, as shown in Figure 9–3.

#### Figure 9–3. Timing Analyzer Report from Figure 9–2

| Compilation Report - Clock | k S | iet | up: 'clo | c <b>k'</b>             |                     |       |       |               |             |          |                              |                            |

|----------------------------|-----|-----|----------|-------------------------|---------------------|-------|-------|---------------|-------------|----------|------------------------------|----------------------------|

| 🞒 🔄 Compilation Report 🛛 🧧 | ^   | Cl  | ock Seti | p: 'clock'              |                     |       |       |               |             |          |                              |                            |

|                            |     |     | Slack    | Actual fmax<br>(period) |                     | From  | To    | From<br>Clock | To<br>Clock |          | Required Longest<br>P2P Time | Actual Longest<br>P2P Time |

| - 🗃 🎹 Flow Settings        |     | 1   | 4.237 n  | s 265.75 MHz (          | period = 3.763 ns ) | inst2 | inst3 | clock         | clock       | 8.000 ns | 7.650 ns                     | 3.413 ns                   |

| 🗃 🔠 Flow Elapsed Time      |     | 2   | 4.741 n  | 306.84 MHz (            | period = 3.259 ns ) | inst  | inst2 | clock         | clock       | 8.000 ns | 7.980 ns                     | 3.239 ns                   |

| 🗃 🖹 Flow Log               |     | F   |          |                         |                     |       |       |               |             |          |                              |                            |

| 🗄 🎒 🛄 Analysis & Synthesis |     |     |          |                         |                     |       |       |               |             |          |                              |                            |

| 🗄 🎒 🧰 Fitter               |     |     |          |                         |                     |       |       |               |             |          |                              |                            |

| 🗄 🕘 📄 Assembler            |     |     |          |                         |                     |       |       |               |             |          |                              |                            |

| 🖻 🞒 Timing Analyzer        |     |     |          |                         |                     |       |       |               |             |          |                              |                            |

| 🚽 🚑 🔣 Summary              |     |     |          |                         |                     |       |       |               |             |          |                              |                            |

| 🚽 🚰 🎹 Settings             |     |     |          |                         |                     |       |       |               |             |          |                              |                            |

| Clock Settings Summ        |     |     |          |                         |                     |       |       |               |             |          |                              |                            |

| Clock Setup: 'clock'       |     |     |          |                         |                     |       |       |               |             |          |                              |                            |

| 🚽 🚑 🔣 Clock Setup (I/O pat |     |     |          |                         |                     |       |       |               |             |          |                              |                            |

| - 🚑 🔣 Clock Hold: 'clock'  |     |     |          |                         |                     |       |       |               |             |          |                              |                            |

| - 🚑 🖽 Clock Hold (I/O path |     |     |          |                         |                     |       |       |               |             |          |                              |                            |

| 🚽 🤩 🔣 tsu                  |     |     |          |                         |                     |       |       |               |             |          |                              |                            |

| A tco                      | ~   |     |          |                         |                     |       |       |               |             |          |                              |                            |

|                            |     |     |          |                         |                     |       |       |               |             |          |                              |                            |

Equation 9–1, Equation 9–2, and Equation 9–3 are similar to those found in other static timing analysis tools, such as the PrimeTime software. Equation 9–4 through Equation 9–7, used by the PrimeTime software, are essentially the same as those used by the Classic Timing Analyzer, but they are rearranged.

#### Equation 9-4.

Slack = Data Required – Data Arrival

#### Equation 9-5.

Clock Arrival = Latch Edge + Shortest Clock Path to Destination

#### Equation 9-6.

Data Required = Clock Arrival – Micro  $t_{su}$

#### Equation 9–7.

Data Arrival = Launch Edge + Longest Clock Path to Source + Micro  $t_{co}$  + Longest Data Delay

Figure 9–4 shows a clock setup check in the Quartus II software.

#### Figure 9-4. Clock Setup Check Reporting with the Classic Timing Analyzer

| 🗉 🚯 Info: Slack time is 4.237 ns for clock "clock" between source register "inst2" and destination register "inst3" |

|---------------------------------------------------------------------------------------------------------------------|

| - 🚯 Info: Fmax is 265.75 MHz (period= 3.763 ns)                                                                     |

| 🛱 🌗 Info: + Largest register to register requirement is 7.650 ns                                                    |

| 🗘 🕀 Info: + Setup relationship between source and destination is 8.000 ns                                           |

| □ 申 🕀 Info: + Latch edge is 8.000 ns                                                                                |

| 🕸 🤀 Info: - Launch edge is 0.000 ns                                                                                 |

| □ Info: - Clock setup uncertainty between source and destination is 0.000 ns                                        |

| 🛱 🌮 Info: + Largest clock skew is -0.164 ns                                                                         |

| 🕸 🕀 Info: + Shortest clock path from clock "clock" to destination register is 3.002 ns                              |

| $\pm \mathfrak{D}$ Info: - Longest clock path from clock "clock" to source register is 3.166 ns                     |

|                                                                                                                     |

| 🛄 Info: - Micro setup delay of destination is 0.010 ns                                                              |

| 🗄 🏵 Info: - Longest register to register delay is 3.413 ns                                                          |

The results in Equation 9–8 are obtained by extracting the numbers from the Classic Timing Analyzer report and applying them to the clock setup slack equations from the Classic Timing Analyzer:

#### Equation 9-8.

Setup Relationship between Source and Destination = Latch Edge – Launch Edge – Clock Setup Uncertainty

8.0 - 0.0 - 0.0 = 8.0 ns

$Clock \ Skew \ = \ Shortest \ Clock \ Path \ to \ Destination - Longest \ Clock \ Path \ to \ Source$

3.002 - 3.166 = -0.164 ns

Largest Register-to-Register Requirement = Setup Relationship between Source & Destination + Largest Clock Skew -Micro  $t_{co}$  of Source Register - Micro  $t_{su}$  of Destination Register

8 + (-0.164) - 0.176 - 0.010 = 7.650 ns

Clock Setup Slack = Largest Register-to-Register Requirement – Longest Register-to-Register Delay

7.650 - 3.413 = 4.237 ns

For the same register-to-register path, the PrimeTime software generates a clock setup report as shown in Example 9–3:

#### Example 9–3. Setup Path Report in PrimeTime

| <pre>Startpoint: inst2~I.lereg<br/>(rising edge-triggered flip-flop clocked by<br/>Endpoint: inst3~I.lereg<br/>(rising edge-triggered flip-flop clocked by<br/>Path Group: clock<br/>Path Type: max</pre>                                                                                                                                                                                                                                                                                          |                                                          |                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------|

| Point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Incr                                                     | Path                                                              |

| <pre>clock clock (rise edge)<br/>clock network delay (propagated)<br/>inst2~I.lereg.clk (stratix_lcell_register)<br/>inst2~I.lereg.regout (stratix_lcell_register) &lt;<br/>inst2~I.regout (stratix_lcell) &lt;-<br/>inst3~I.datac (stratix_lcell) &lt;-<br/>inst3~I.lereg.datac (stratix_lcell_register)<br/>data arrival time<br/>clock clock (rise edge)<br/>clock network delay (propagated)<br/>inst3~I.lereg.clk (stratix_lcell_register<br/>library setup time<br/>data required time</pre> | 3.166<br>0.000<br>- 0.176*<br>0.000*<br>0.000*<br>3.413* | 3.342r<br>3.342r<br>6.755r<br>6.755<br>8.000<br>11.002<br>11.002r |

| data required time<br>data arrival time                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          | 10.992<br>-6.755                                                  |

| slack (MET)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          | 4.237                                                             |

## **Clock Hold Relationship and Slack**

The Classic Timing Analyzer performs a hold time check along every register-to-register path in the design to ensure that no hold time violations have occurred. The hold time check verifies that data from the source register does not reach the destination until after the hold time of the destination register. The condition used for a hold check is shown in Equation 9–9:

#### Equation 9–9.

Data Arrival – Clock Arrival  $\geq$  t<sub>H</sub>

The Classic Timing Analyzer determines the clock hold slack with Equation 9–10, Equation 9–11, Equation 9–12, and Equation 9–13:

#### Equation 9-10.

Clock Hold Slack = Shortest Register-to-Register Delay – Smallest Register-to-Register Requirement

#### Equation 9–11.

Smallest Register-to-Register Requirement = Hold Relationship between Source & Destination + Smallest Clock Skew – Micro  $t_{su}$  of Source + Micro  $t_{H}$  of Destination

#### Equation 9–12.

Hold Relationship between Source & Destination = Latch Edge – Launch Edge

#### Equation 9-13.

Smallest Clock Skew = Longest Clock Path from Clock to Destination Register – Shortest Clock Path from Clock to Source Register

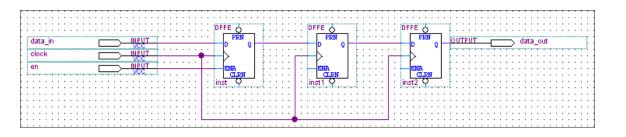

Figure 9–5 shows a simple three-register design.

#### Figure 9–5. Simple Three-Register Design

The Classic Timing Analyzer generates a report as shown in Figure 9-6.

Figure 9–6. Timing Analyzer Report Generated from the Three-Register Design

| 🗃 🔄 Compilation Report                   | ^ | Cl  | ock Hold: '      | clock' |       |               |             |                               |                               |                             |

|------------------------------------------|---|-----|------------------|--------|-------|---------------|-------------|-------------------------------|-------------------------------|-----------------------------|

| - 🚑 🖹 Legal Notice<br>- 🎒 📑 Flow Summary |   |     | Minimum<br>Slack | From   | To    | From<br>Clock | To<br>Clock | Required Hold<br>Relationship | Required Shortest<br>P2P Time | Actual Shortest<br>P2P Time |

| - 🗃 🎹 Flow Settings                      |   | 1   | 3.149 ns         | inst   | inst2 | clock         | clock       | 0.000 ns                      | 0.090 ns                      | 3.239 ns                    |

| - 🎒 🎹 Flow Elapsed Time                  |   | 2   | 3.653 ns         | inst2  | inst3 | clock         | clock       | 0.000 ns                      | -0.240 ns                     | 3.413 ns                    |

| 🗃 🖹 Flow Log                             |   | Г   |                  |        |       |               |             |                               |                               | 1                           |

| 🗄 🚭 🧰 Analysis & Synthesis               |   |     |                  |        |       |               |             |                               |                               |                             |

| 🗄 🎒 🚞 Fitter                             |   |     |                  |        |       |               |             |                               |                               |                             |

| 🗄 🎒 🚞 Assembler                          |   |     |                  |        |       |               |             |                               |                               |                             |

| 🖻 🚭 🔁 Timing Analyzer                    |   |     |                  |        |       |               |             |                               |                               |                             |

| - 🞒 🔣 Summary                            |   |     |                  |        |       |               |             |                               |                               |                             |

| - 🗃 🎛 Settings                           |   |     |                  |        |       |               |             |                               |                               |                             |

| - 🗃 🎛 Clock Settings Summ                |   |     |                  |        |       |               |             |                               |                               |                             |

| - 🗃 🐻 Clock Setup: 'clock'               |   |     |                  |        |       |               |             |                               |                               |                             |

|                                          |   |     |                  |        |       |               |             |                               |                               |                             |

| - 🚑 🔣 Clock Hold: 'clock'                |   |     |                  |        |       |               |             |                               |                               |                             |

|                                          |   | L . |                  |        |       |               |             |                               |                               |                             |

| - 🚑 🔣 Clock Hold (I/O path               |   |     |                  |        |       |               |             |                               |                               |                             |

The previous equations are similar to those found in the Quartus II software. Equation 9–14 through Equation 9–17 are the same equations that are used by the PrimeTime software, but they are rearranged.

#### Equation 9–14.

Slack = Data Required – Data Arrival

#### Equation 9–15.

Clock Arrival = Latch Edge + Longest Clock Path to Destination

#### Equation 9–16.

Data Required = Clock Arrival – Micro  $t_{H}$

#### Equation 9–17.

```

Data Arrival = Launch Edge + Longest Clock Path to Source + Micro t_{co} + Shortest Data Delay

```

The shortest register-to-register delay in the previous equation is equal to register-to-register data delay.

Figure 9–7 shows a clock setup check with the Classic Timing Analyzer.

#### Figure 9–7. Clock Hold Check Reporting with the Classic Timing Analyzer

| 🗉 🥹 Info: Minimum slack time is 3.653 ns for clock "clock" between source register "inst2" and destination register "inst3" |

|-----------------------------------------------------------------------------------------------------------------------------|

| 🛱 🦃 Info: + Shortest register to register delay is 3.413 ns                                                                 |

| $\dot{f e}$ - $m{\langle}$ Info: - Smallest register to register requirement is -0.240 ns                                   |

| $\dot{\oplus} \dot{\Rightarrow}$ Info: + Hold relationship between source and destination is 0.000 ns                       |

| 🔁 🤹 Info: + Latch edge is 0.000 ns                                                                                          |

| 🕸 🏟 Info: - Launch edge is 0.000 ns                                                                                         |

| └──— Info: - Clock hold uncertainty between source and destination is 0.000 ns                                              |

| 🛱 🌮 Info: + Smallest clock skew is -0.164 ns                                                                                |

| 🖶 🏵 Info: + Longest clock path from clock "clock" to destination register is 3.002 ns                                       |

| 🐵 🏵 Info: - Shortest clock path from clock "clock" to source register is 3.166 ns                                           |

| ————————————————————————————————————                                                                                        |

| L 💭 Info: + Micro hold delay of destination is 0.100 ns                                                                     |

|                                                                                                                             |

The results in Equation 9–18 are obtained by extracting the numbers from the Timing Analysis report and applying the clock setup slack equations from the Classic Timing Analyzer.

#### Equation 9–18.

Clock Hold Slack = Shortest Register-to-Register Delay – Smallest Register-to-Register Requirement 3.413 - (-0.240) = 3.653 ns

Smallest Register-to-Register Requirement = Hold Relationship between Source & Destination + Smallest Clock Skew – Micro  $t_{co}$  of Source + Micro  $t_{H}$  of Destination

0 + (-0.164) - 0.176 + 0.100 = -0.240 ns

Hold Relationship between Source & Destination = Latch – Launch 0.0 - 0.0 ns

Smallest Clock Skew = Longest Clock Path from Clock to Destination Register – Shortest Clock Path from Clock to Source Register

3.002 - 3.166 = -0.164 ns

For the same register-to-register path, the PrimeTime software generates the report shown in Example 9–4:

Example 9-4. Hold Path Report in PrimeTime

| <pre>Startpoint: inst2~I.lereg<br/>(rising edge-triggered flip-flop clocked by c<br/>Endpoint: inst3~I.lereg<br/>(rising edge-triggered flip-flop clocked by c<br/>Path Group: clock<br/>Path Type: min</pre>                                                                                                             |                                                                 |                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------|

| Point                                                                                                                                                                                                                                                                                                                     | Incr                                                            | Path                                                    |

| <pre>clock clock (rise edge)<br/>clock network delay (propagated)<br/>inst2~I.lereg.clk (stratix_lcell_register)<br/>inst2~I.lereg.regout (stratix_lcell_register)&lt;-<br/>inst2~I.regout (stratix_lcell)<br/>inst3~I.datac (stratix_lcell)<br/>inst3~I.lereg.datac (stratix_lcell_register)<br/>data arrival time</pre> | 0.000<br>3.166<br>0.000<br>0.176*<br>0.000*<br>0.000*<br>3.413* | 3.166<br>3.166r<br>3.342r<br>3.342r<br>3.342r<br>3.342r |

| <pre>clock clock (rise edge)<br/>clock network delay (propagated)<br/>inst3~I.lereg.clk (stratix_lcell_register)<br/>library hold time<br/>data required time<br/></pre>                                                                                                                                                  | 0.000<br>3.002<br>0.100*                                        | 3.002<br>3.002r                                         |

| slack (MET)                                                                                                                                                                                                                                                                                                               |                                                                 | 3.653                                                   |

Both sets of hold slack equations can be used to determine the hold slack value of any path.

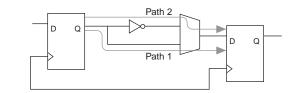

## **Input Delay and Output Delay Relationships and Slack**

Input delay and output delay reports generated by the Classic Timing Analyzer are similar to the clock setup and clock hold relationship reports. Figure 9–8 shows the input delay and output delay report for the design shown in Figure 9–5 on page 9–13.

Figure 9–8. Input and Output Delay Reporting with the Classic Timing Analyzer

| 🞒 🖹 Legal Notice                       | ∧ C | lock Setup | ) (I/O paths)           | : 'clock'           |       |          |       |       | -        |                              |                          |

|----------------------------------------|-----|------------|-------------------------|---------------------|-------|----------|-------|-------|----------|------------------------------|--------------------------|

| Flow Summary                           |     | Slack      | Actual fmax<br>(period) |                     | From  | To       |       |       |          | Required Longest<br>P2P Time | Actual Longe<br>P2P Time |

| Flow Elapsed Time                      | 1   | 0.175 ns   | ····                    | period = 7.825 ns ) | inst3 | data out |       |       | 8.000 ns | 3.572 ns                     | 3.397 ns                 |

| 🗿 🖹 Flow Log                           | 2   |            |                         | period = 2.620 ns ) |       | inst     | clock | clock | 8.000 ns | 8.490 ns                     | 3.110 ns                 |

| 🗃 🧰 Analysis & Synthesis               |     |            |                         | · · · ·             |       |          |       |       |          |                              |                          |

| 🗐 🧰 Fitter                             |     |            |                         |                     |       |          |       |       |          |                              |                          |

| 🗃 🦲 Assembler                          |     |            |                         |                     |       |          |       |       |          |                              |                          |

| 🗃 🔄 Timing Analyzer                    |     |            |                         |                     |       |          |       |       |          |                              |                          |

| - 🛃 🔜 Summary                          |     |            |                         |                     |       |          |       |       |          |                              |                          |

| - 🗃 🎹 Settings                         |     |            |                         |                     |       |          |       |       |          |                              |                          |

| - 🗃 🎹 Clock Settings Summary           |     |            |                         |                     |       |          |       |       |          |                              |                          |

| - 🗃 🔣 Clock Setup: 'clock'             | -1  |            |                         |                     |       |          |       |       |          |                              |                          |

| - 🚑 🔣 Clock Setup (I/O paths): 'clock' |     |            |                         |                     |       |          |       |       |          |                              |                          |

| 🗃 🔄 Clock Hold: 'clock'                |     |            |                         |                     |       |          |       |       |          |                              |                          |

| - 🚑 🔣 Clock Hold (I/O paths): 'clock'  |     |            |                         |                     |       |          |       |       |          |                              |                          |

| Gock Hold (I/O paths): 'clock'         | -   |            |                         |                     |       |          |       |       |          |                              |                          |

Figure 9–9 shows the fully expanded view for the output delay path.

| Figure 9–9. ( | Output Delay | y Path Reportin | g with the Classic | Timing Analyzer |

|---------------|--------------|-----------------|--------------------|-----------------|

|               |              |                 |                    |                 |

| 🗉 🏵 Info: Slack time is 175 ps for clock "clock" between source register "inst3" and destination pin "data_out" |

|-----------------------------------------------------------------------------------------------------------------|

|                                                                                                                 |

|                                                                                                                 |

| 🗣 🐶 Info: + Largest register to pin requirement is 3.572 ns                                                     |

| $\oplus \oplus$ Info: + Setup relationship between source and destination is 8.000 ns                           |

| ⊕-(\$) Info: + Latch edge is 8.000 ns                                                                           |

| ⊕-(\$) Info: - Launch edge is 0.000 ns                                                                          |

| └──— Info: - Clock setup uncertainty between source and destination is 0.000 ns                                 |

| $\oplus \mathfrak{P}$ Info: - Longest clock path from clock "clock" to source register is 3.002 ns              |

| - 🕀 Info: - Micro clock to output delay of source is 0.176 ns                                                   |

| 🖳 💭 Info: - Max Output delay of pin is 1.25 ns                                                                  |

| $\oplus \mathbb{Q}$ Info: - Longest register to pin delay is 3.397 ns                                           |

For the same output delay path, the PrimeTime software generates a report similar to Example 9–5:

#### Example 9–5. Setup Path Report in PrimeTime

| Startpoint: inst3~I.lereg<br>(rising edge-triggered flip-flop clocked by cl<br>Endpoint: data_out<br>(output port clocked by clock)<br>Path Group: clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ock)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Path Type: max<br>Point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Incr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <pre>clock clock (rise edge)<br/>clock network delay (propagated)<br/>inst3~I.lereg.clk (stratix_lcell_register)<br/>inst3~I.lereg.regout (stratix_lcell_register)&lt;-<br/>inst3~I.regout (stratix_lcell)&lt;-<br/>data_out~I.datain (stratix_io)&lt;-<br/>data_out~I.datain (stratix_io)&lt;-<br/>data_out~I.out_mux3.A (mux21)&lt;-<br/>data_out~I.out_mux3.MO (mux21)&lt;-<br/>data_out~I.and2_22.IN1 (AND2)&lt;-<br/>data_out~I.and2_22.Y (AND2)&lt;-<br/>data_out~I.out_mux1.A (mux21)&lt;-<br/>data_out~I.out_mux1.MO (mux21)&lt;-<br/>data_out~I.inst1.datain (stratix_asynch_io)&lt;-<br/>data_out~I.inst1.padio (stratix_asynch_io)&lt;-<br/>data_out~I.padio (stratix_io)&lt;-<br/>data_out~I.padio (stratix_io)&lt;-<br/>data_out (out)<br/>data arrival time<br/>clock clock (rise edge)<br/>clock network delay (propagated)<br/>output external delay<br/>data required time</pre> | 0.000<br>3.002<br>0.000<br>0.176*<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.000<br>0.0000<br>0.0000<br>0.0000<br>0.0000<br>0.0000<br>0.0000<br>0.0000<br>0.0000<br>0.0000<br>0.0000<br>0.0000<br>0.0000<br>0.0000<br>0.0000<br>0.0000<br>0.0000<br>0.0000<br>0.0000<br>0.0000<br>0.0000<br>0.0000<br>0.0000<br>0.0000<br>0.0000<br>0.0000<br>0.00000<br>0.00000<br>0.00000<br>0.00000<br>0.00000<br>0.00000<br>0.00000<br>0.00000<br>0.00000000 | 3.002<br>3.002r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178r<br>3.178 |