# A Digitally Controlled Grid Connected Modular Cascaded H-bridge Multilevel Inverter

| 著者       | RAVIKANT PANDEY                      |

|----------|--------------------------------------|

| その他のタイトル | 電力系統に接続されたモジュラー・カスケードHブ              |

|          | リッジ多段インバータのディジタル制御                   |

| 学位授与年度   | 平成29年度                               |

| 学位授与番号   | 17104甲生工第310号                        |

| URL      | http://hdl.handle.net/10228/00006820 |

# A Digitally Controlled Grid Connected Modular Cascaded H-bridge Multilevel Inverter

#### A DISSERTATION

submitted in partial fulfilment of the requirements for the degree

of

# **DOCTOR OF PHILOSOPHY**

By

## **Ravikant Pandey**

## (Student Number: 15899018)

under the supervision of

# Prof. Tsuyoshi Hanamoto

Graduate School of Life Science and Systems Engineering (LSSE) Green Electronics Division Kyushu Institute of Technology Hibikino, Wakamatsu-ku, Kitakyushu-shi Fukuoka-ken, Japan March, 2018

# Acknowledgement

First and foremost, I would like to express special gratitude to my supervisor Prof. Tsuyoshi Hanamoto, for granting me the freedom to pursue the research ideas that have been led to completion of this dissertation. Hanamoto sensei has inspired me with his polite and brilliant suggestions for research and life. I would like to thank Hanamoto sensei most sincerely for giving me the opportunity to work under his supervision. He has been supportive and contributed immensely for successful completion of this thesis.

I sincerely thank to professors of committee, Prof. Yasunori Mitani, Prof. Ichiro Omura and Prof. Shyam S. Pandey for reading my thesis and giving me the enormous suggestions to make it more effective and concrete. I am thankful for their contribution and vast ideas to make my thesis more elaborative.

I shall extend my special thanks to my friends Ravi, Yoshino and Maehata for their support during my study in japan. These guys with in the same lab made my three years of study very enjoyable and fruitful. I also like to thank all the member of Hanamoto laboratory for planning different parties, trips, game and supporting me during my stay and research in last three years.

I also like to thank Natsumo Yoshitake for discussing and working with me as a team for the different task and to achieve different milestone in the ongoing research. His suggestion and doubts always drives me for more hard work for the relevant solutions. I shall thank Yoshitake san for helping in development of hardware prototype.

I would like to thank my all Indian friends living in Kitakyusu Japan specially Gaurav, Gyanendra, Mallikarjun, Nishanth, Nayan, Kaushal, Nishit, Atul and Vijay for their wonderful company in here. I always felt like Kitakyushu is second home because of these guys.

I would like to express my gratitude to Kyutech teaching and non-teaching staff, JSPS, KDDI foundation, FAIS for supporting my study and stay in Japan. I would like to specially thank Japanese language teachers for their experienced teaching and effort to teach Japanese language.

I also like to thank and express my gratitude to the local people of Kitakyushu, Japan for their peaceful hospitality and enjoyed playing, jogging, cycling, living in this beautiful country.

At last I would like to thank my grandparents and parents for their blessing and encouragement during my study. I also like to thanks my younger sister and brother for their time to time suggestions for maintaining my good health and interesting life throughout the academic career.

## Abstract

The issues of increasing demand of energy and limited amount of available conventional energy sources necessitates highly efficient electrical energy conversion system to control power from generation to consumer end. To achieve environment friendly and high efficiency transmission and distribution of electrical energy, power electronics technology emerges as an adequate option. Power electronics converter is used as an application of solid state devices for control and conversion of electrical power. Voltage source inverter is mainly utilized for the highly efficient electrical energy conversion within recently introduced grid codes in different renewable energy generations, industrial processes, motor drives and (hybrid) electric vehicle. Further evaluated topology of voltage source inverters evolves modular cascaded H-bridge multilevel inverter (CHMLI) which holds some advantages such as, lower switching frequency operation, less total harmonic distortion, modularity in the structure and distributed power stress on power semiconductor devices, medium voltage-high power operation.

The main focus of the work are field programmable gate array (FPGA) based digital control of CHMLI and its application to the grid.FPGA provides number of advantages such as higher performance, lower cost, and robustness of solution, DSP (digital signal processing) capabilities and solution customization.

The first chapter focusing on the energy and electricity demand and future scenario, role of power electronics, general trend in technological innovation and literature review for the presented work that includes multilevel inverters, essential role of modulation and control, power grid issues with available solutions and limitations of the currently available solutions.

In chapter 2, open loop control with phase shifted (PS) and level shifted (LS) carrier based sinusoidal pulse width modulations are implemented for CHMLI connected to linear load. Performance of PS and LS carrier based modulation is investigated using FPGA based digital control for five, seven and nine level inverter. In addition to open loop control of CHMLI, FPGA hardware-in-loop co-simulation is proposed for controller prototyping of CHMLI. Third harmonics injected PWM is used for control of CHMLI. Performance of five and seven level inverter is investigated by real time co-simulation for phase shifted and level shifted carrier based THIPWM.

In chapter 3, a novel design of LCL filter is proposed considering modified constraints of lower switching frequency operation. LCL interfaced distribution static compensator (DSTATCOM) is analyzed and three phase grid connected system model is developed in MATLAB/Simulink. LCL filter with CHMLI based system offers some adequate benefits such as reduced inductance, wider bandwidth, better ripple attenuation, less harmonics in pcc voltage. The results are demonstrated for a linear/non-linear load under unbalanced conditions, considering the voltage sag and swell in the system due to a disturbance in the load.

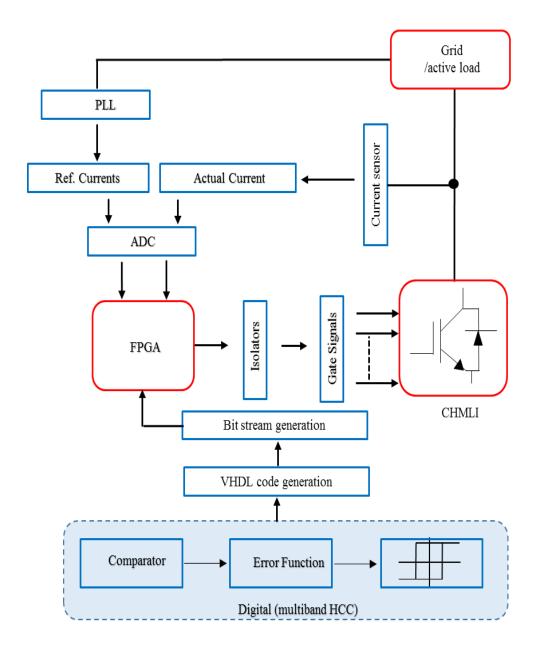

In chapter 4, digital multiband hysteresis current controller (HCC) is proposed for grid connected CHMLI that offers functions of close loop controller and implicit modulator. Using sinusoidal pulse width modulations with linear control techniques always possess some delays and steady state error therefore need of complex controller design arises. Digital multiband HCC is able to drive the close loop system with improved stability and possess certain easiness in implementation of digital circuitry. Experimental prototype of grid connected CHMLI is developed and controller implementation is done using Xilinx system generator based model design for FPGA.

In chapter 5, digital multiband HCC is proposed for DSTATCOM application and comparison of linear control techniques such as PI controller with LS, PS and digital multiband HCC is carried out. Leading advantages of digital multiband HCC over linear controller under load abnormalities are demonstrated.

Chapter 6, this chapter concludes the work presented in whole dissertation, summarizes the work and leads to the future possibilities in the ongoing research.

# List of Figures

| 1.1  | Gross domestic product (GDP) growth over six decades with energy<br>intensity followed by energy consumption by region (source: 2017 | 2  |

|------|--------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | The gradual change in energy source mix continues over the decades (source: 2017 energy outlook)                                     |    |

| 1.3  | Classification of converters for high-power drives (>1 MW).                                                                          | 7  |

| 1.4  | General block diagram of the medium voltage drive.                                                                                   | 8  |

| 1.5  | One phase leg of an inverter with (a) two levels, (b) three levels, and (c) n levels.                                                | 9  |

| 1.6  | Diode clamped multilevel inverter topology                                                                                           | 11 |

| 1.7  | Capacitor clamped multilevel inverter topology                                                                                       | 12 |

| 1.8  | Cascaded H-bridge multilevel inverter topology.                                                                                      | 12 |

| 1.9  | Modular multilevel inverter                                                                                                          | 14 |

| 1.10 | General Classification of gate signal generation methods for voltage source inverters                                                | 15 |

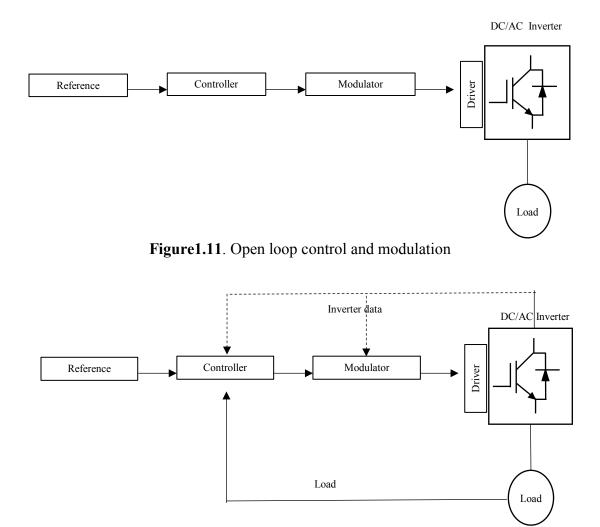

| 1.11 | Open loop control and modulation                                                                                                     | 16 |

| 1.12 | Close loop control and modulation                                                                                                    | 16 |

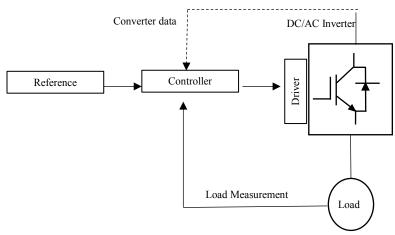

| 1.13 | Close loop control with implicit modulation                                                                                          | 17 |

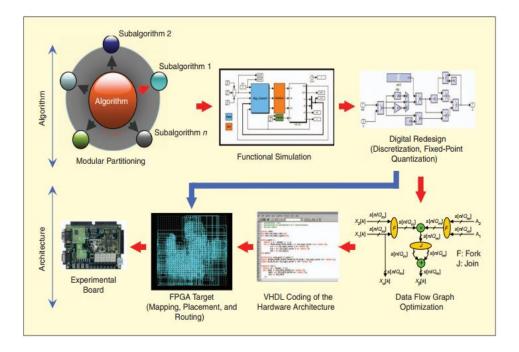

| 1.14 | Design Methodologies for FPGA based real time implementation                                                                         | 20 |

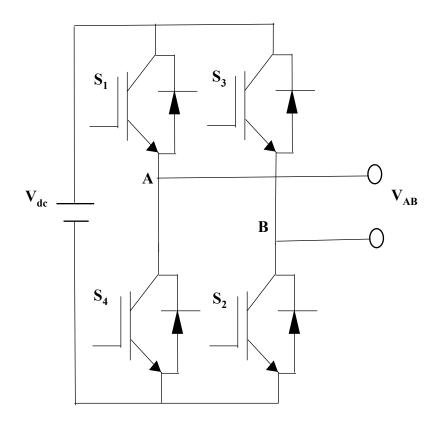

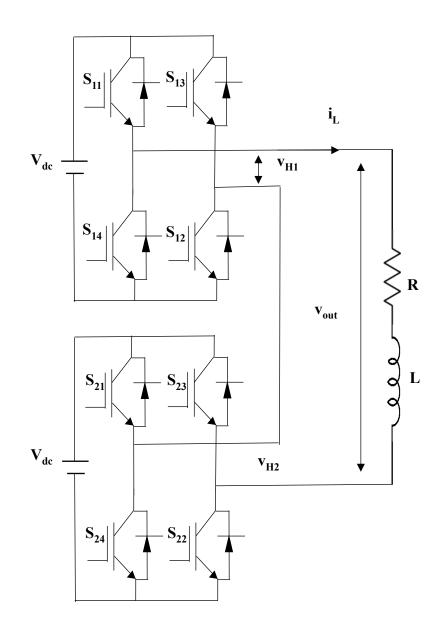

| 2.1  | Single phase H-bridge inverter                                                                                                       | 29 |

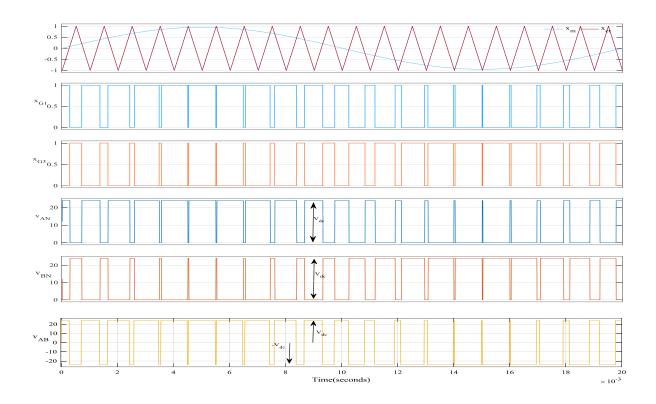

| 2.2  | Bipolar modulation of H-bridge inverter.                                                                                             | 31 |

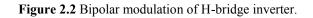

| 2.3  | Unipolar modulation of H-bridge inverter                                                                                             | 31 |

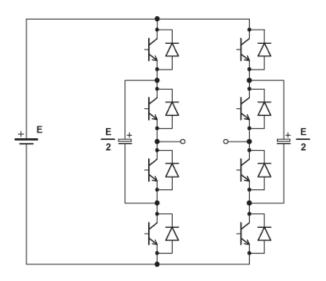

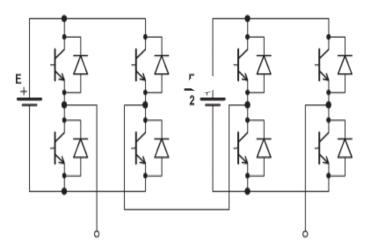

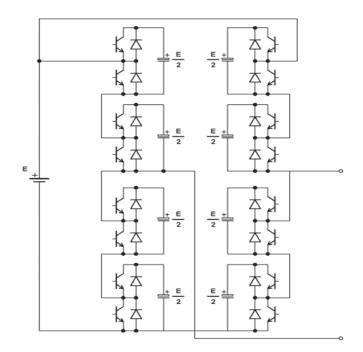

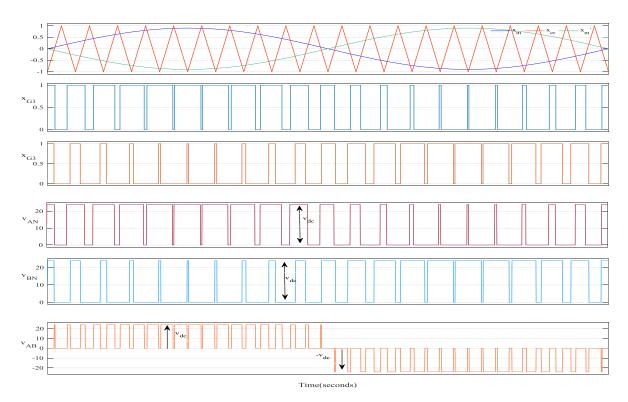

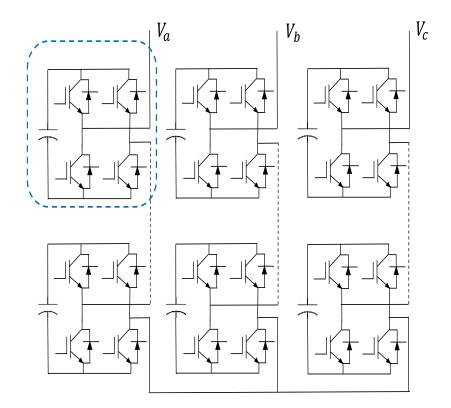

| 2.4  | Three phase CHMLI topology                                                                                                           | 32 |

| 2.5  | Single phase five level inverter connected to linear load                                                                            | 34 |

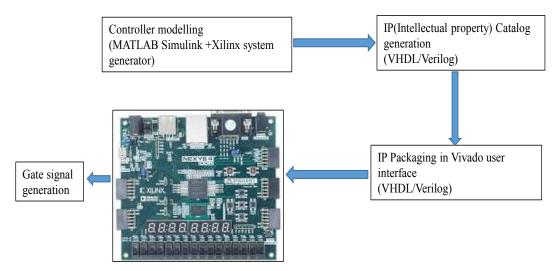

| 2.6  | Mrthodology of digital control based on FPGA                                                                                         | 36 |

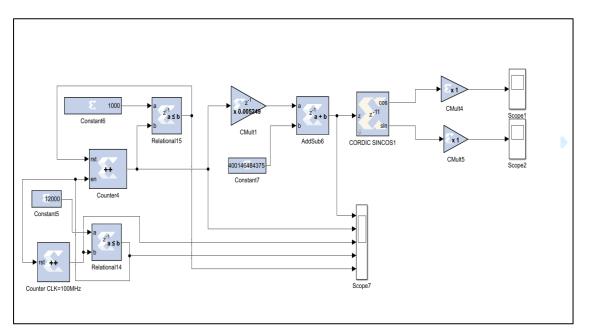

| 2.7  | XSG block set based modulating wave (sinusoidal wave) generation in Simulink                                                         | 36 |

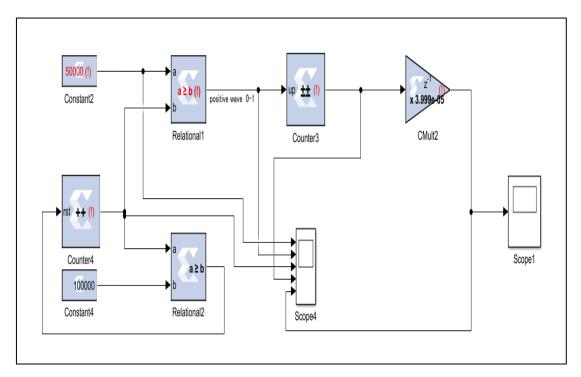

| 2.8  | XSG block set based carrier wave (triangular wave) generation in simulink                                                            | 37 |

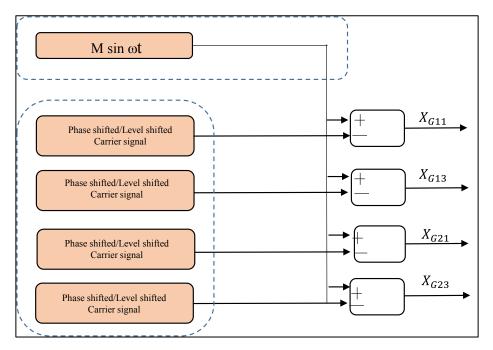

| 2.9  | Carrier based pulse width modulation for five level inverter                                                                         | 38 |

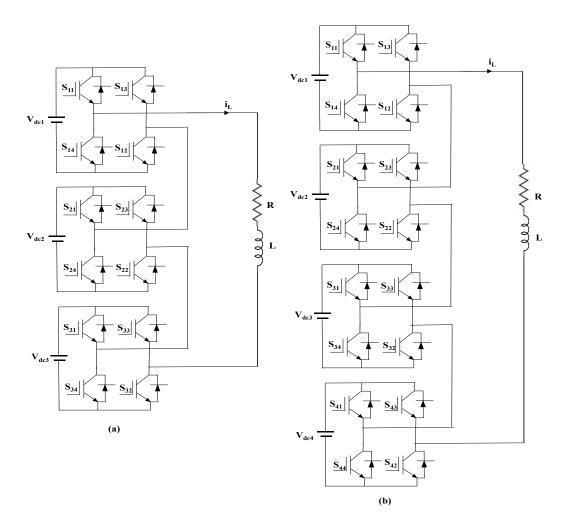

| 2.10 | (a) Seven level (b) Nine level inverter connected to linear load                                                                     | 39 |

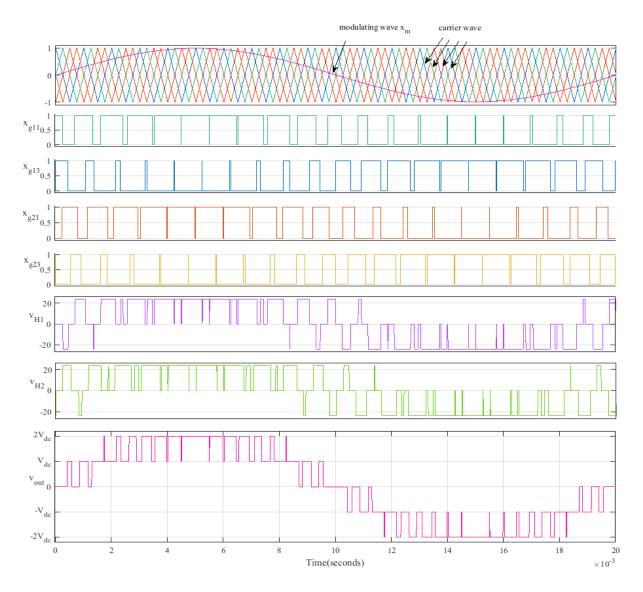

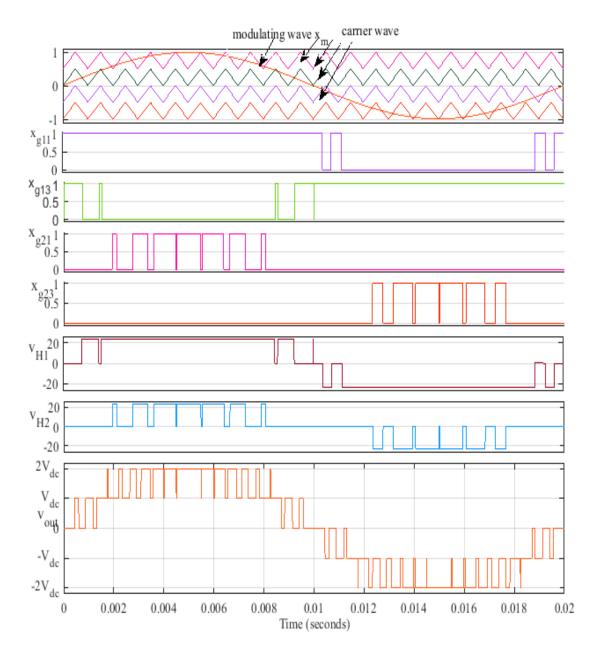

| 2.11 | Phase shifter carrier based PWM for five level inverter                                                |    |

|------|--------------------------------------------------------------------------------------------------------|----|

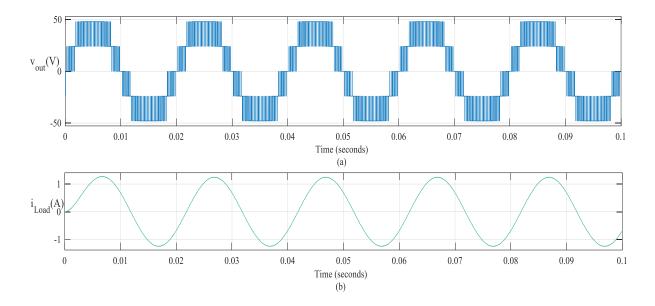

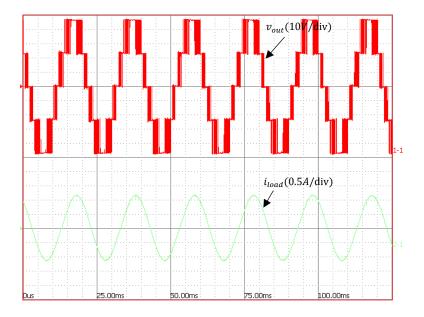

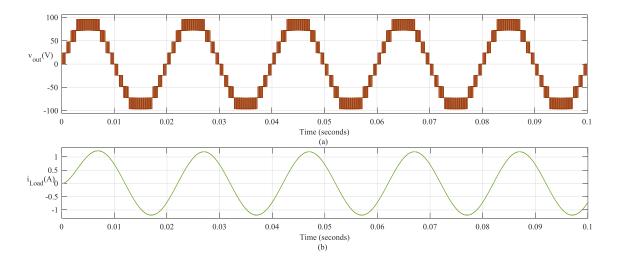

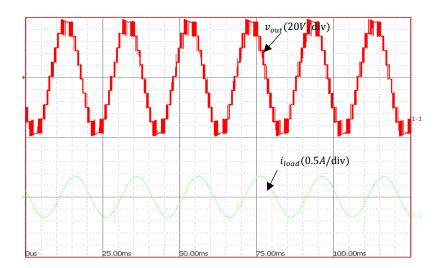

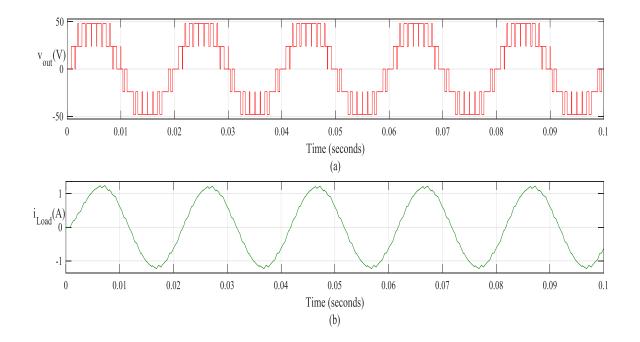

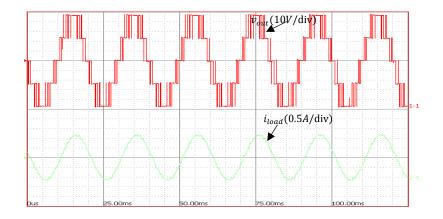

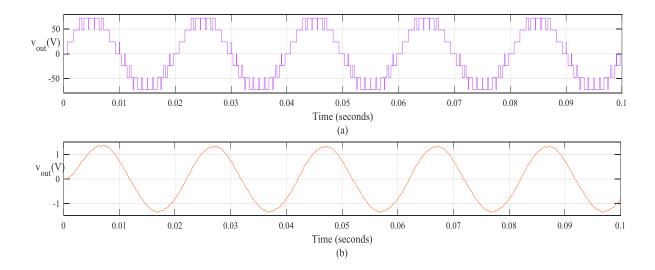

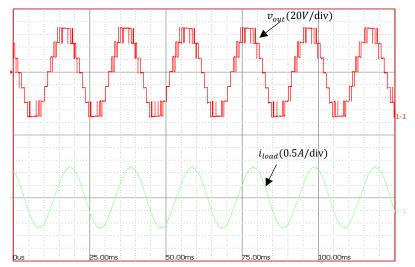

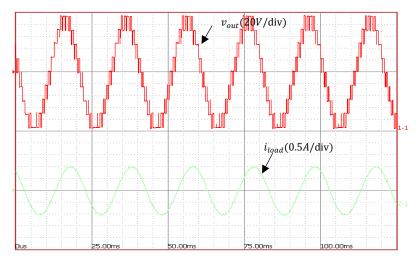

| 2.12 | (a) Phase shifted carrier based five level inverter output voltage, (b) load current                   | 41 |

|      | (c) Experimental results of five level inverter for phase shifted modulation                           |    |

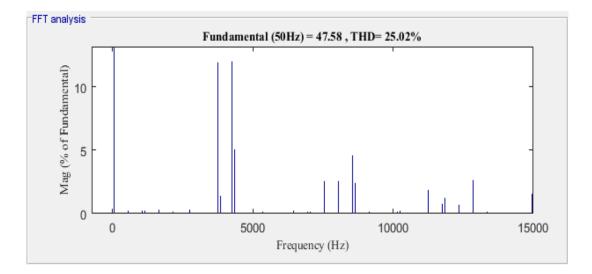

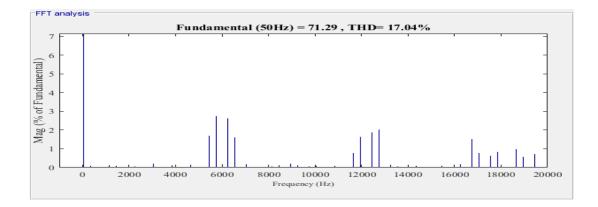

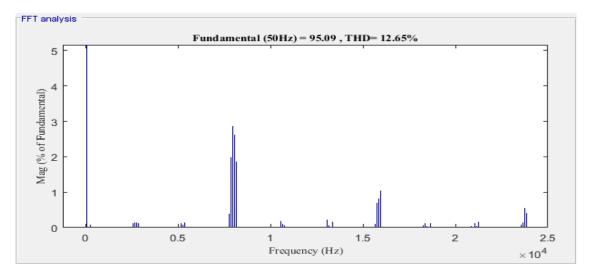

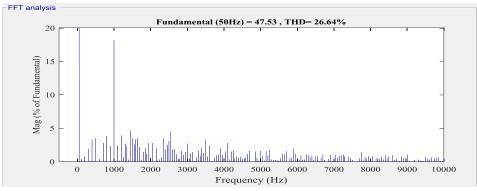

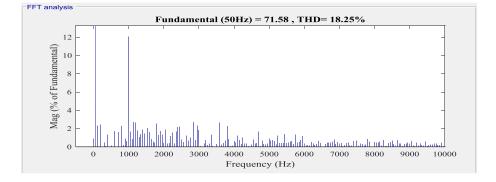

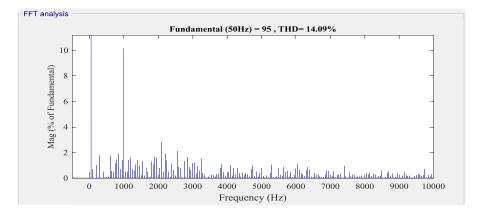

| 2.13 | FFT analysis of inverter output voltage                                                                | 42 |

| 2.14 | Phase shifted carrier based (a) seven level inverter output voltage, (b) load current                  | 43 |

|      | (c)Experimental results of seven level inverter for phase shifted modulation.                          | 43 |

| 2.15 | FFT analysis of seven level inverter output voltage.                                                   | 43 |

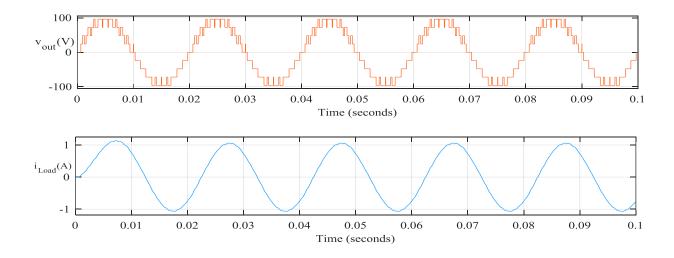

| 2.16 | Phase shifted carrier based (a) Nine level inverter output voltage, (b) load current                   | 44 |

|      | (c)Experimental results of nine level inverter for phase shifted modulation.                           | 45 |

| 2.17 | FFT analysis of nine level inverter output voltage.                                                    | 45 |

| 2.18 | Level shifted carrier based PWM for five level inverter                                                | 46 |

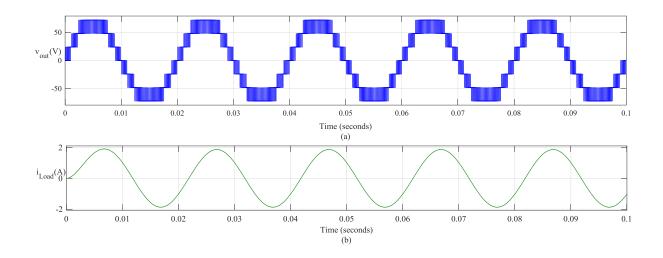

| 2.19 | 9 Level shifted carrier based Five level Inverter (a) output voltage, (b) load current.                |    |

|      | (c)Experimental results of five level inverter for level shifted modulation.                           | 48 |

| 2.20 | FFT analysis of five level inverter output voltage.                                                    |    |

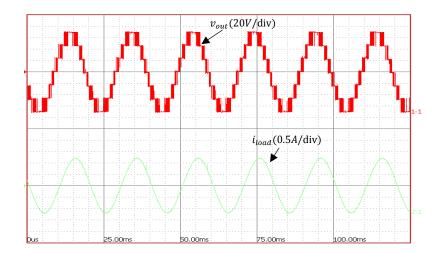

| 2.21 | 1 Level shifted carrier based seven level Inverter (a) output voltage, (b)<br>load current.            |    |

|      | (c)Experimental results of seven level inverter for level shifted modulation.                          | 49 |

| 2.22 | FFT analysis of seven level inverter output voltage.                                                   | 49 |

| 2.23 | Level shifted carrier based nine level Inverter (a) output voltage, (b) load current.                  | 49 |

|      | (c)Experimental results of nine level inverter for level shifted modulation.                           | 50 |

| 2.24 | FFT analysis of nine level inverter output voltage.                                                    | 50 |

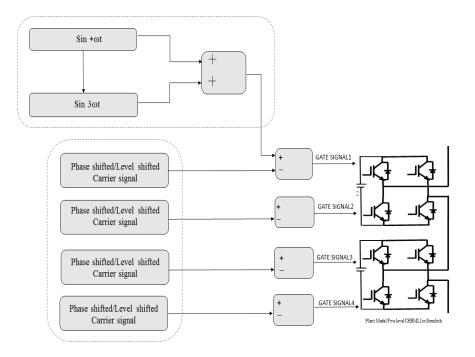

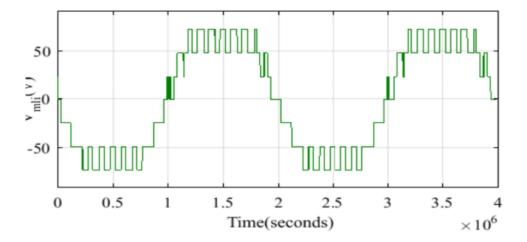

| 2.25 | 5 Third harmoincs injected PWM for five level CHMLI.                                                   |    |

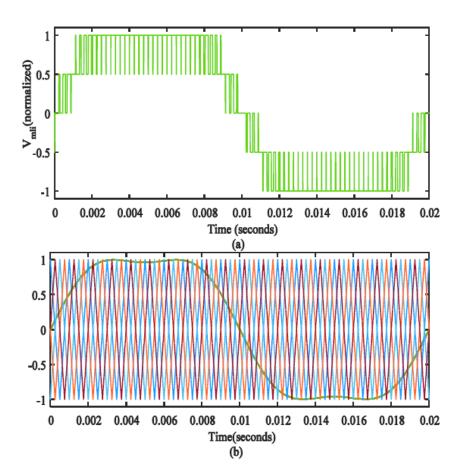

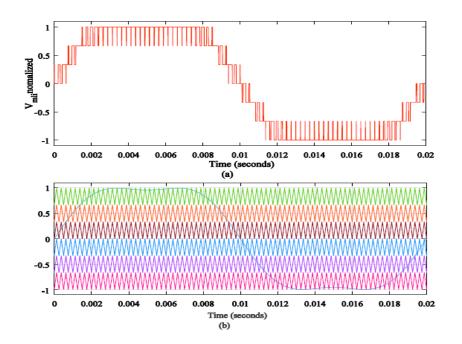

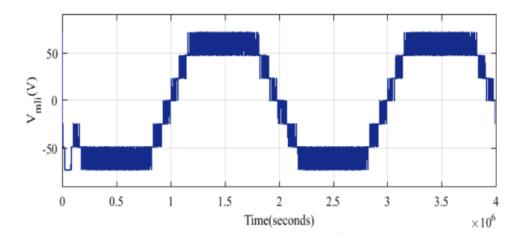

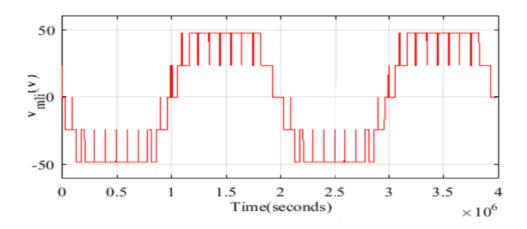

| 2.26 | Phase shifted carrier based THIPWM (a) five level output voltage, (b) modulating wave and carrier wave | 54 |

| 2.27 | Level shifted carrier based THIPWM (a) seven level output voltage, (b) modulating wave and carrier wave                                                                 | 55 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

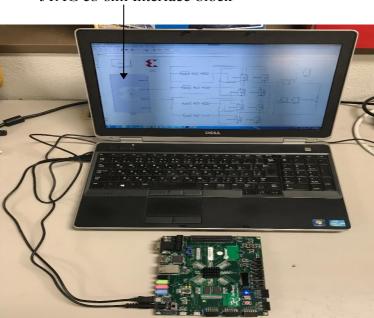

| 2.28 | Hardware in loop (FPGA Zed board) co-simulation setup                                                                                                                   |    |

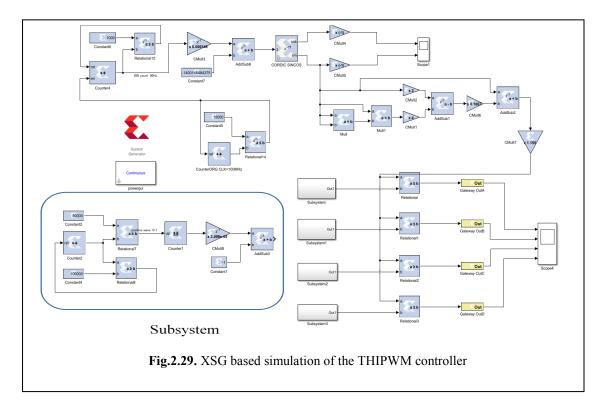

| 2.29 | XSG based simulation of the THIPWM controller                                                                                                                           |    |

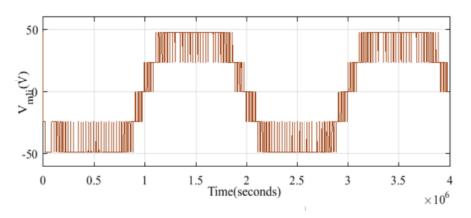

| 2.30 | Output voltage of five level inverter based on phase shifted THIPWM                                                                                                     | 57 |

| 2.31 | Output voltage of five level inverter based on phase shifted THIPWM                                                                                                     | 58 |

| 2.32 | Output voltage of five level inverter based on phase shifted THIPWM                                                                                                     | 58 |

| 2.33 | Output voltage of five level inverter based on phase shifted THIPWM                                                                                                     | 58 |

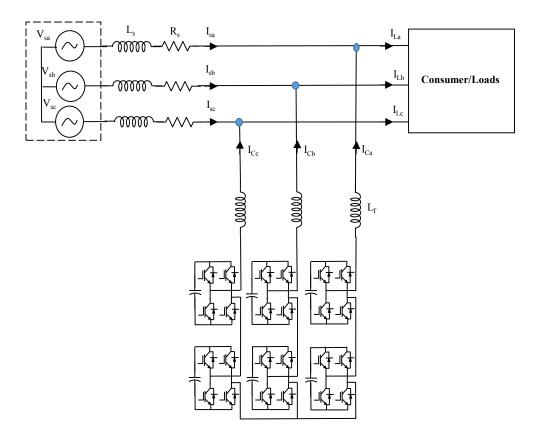

| 3.1  | Three-phase cascaded H-bridge multilevel inverter (CHBMLI) structure.                                                                                                   | 64 |

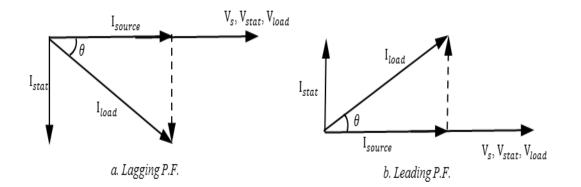

| 3.2  | Phasor diagrams of DSTATCOM with (a) leading and (b) lagging PF loads system.                                                                                           | 65 |

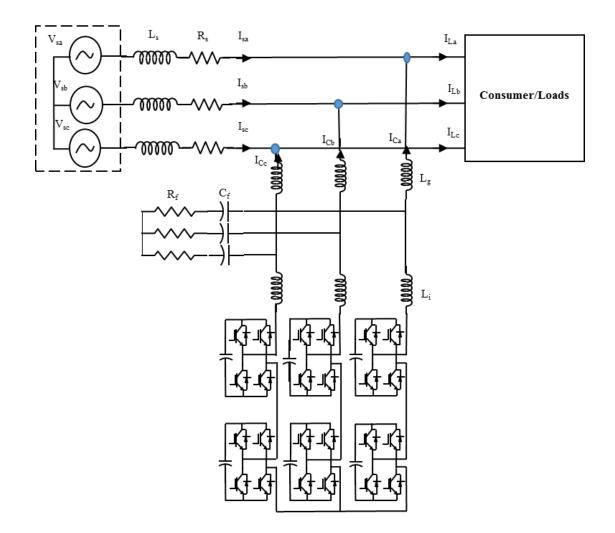

| 3.3  | Shunt-connected distribution static compensator (DSTATCOM)                                                                                                              | 66 |

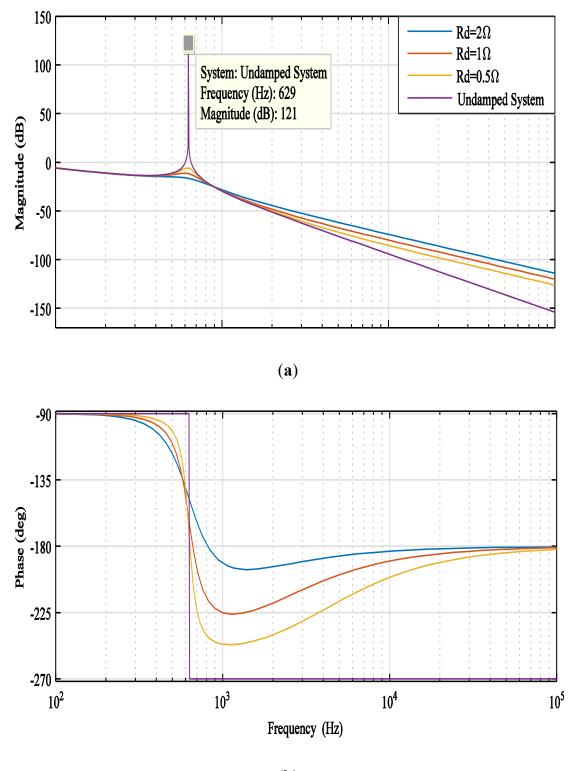

| 3.4  | Block diagram of control algorithm used for reactive power compensation.                                                                                                | 69 |

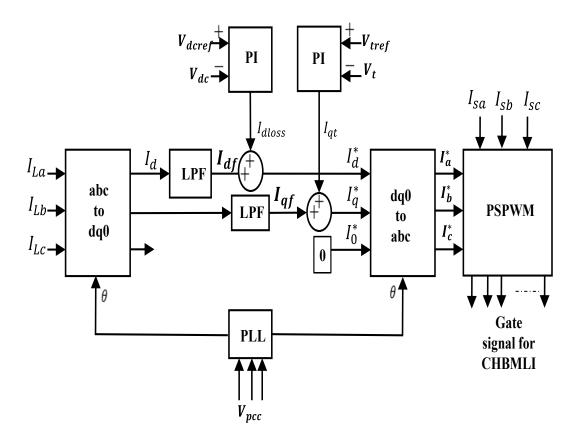

| 3.5  | Bode diagram of the LCL filter. (a): Magnitude vs. Frequency; and (b): Phase vs. Frequency                                                                              | 74 |

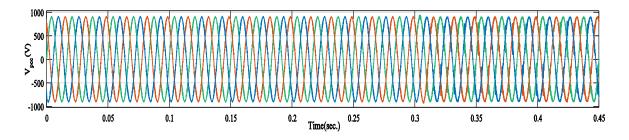

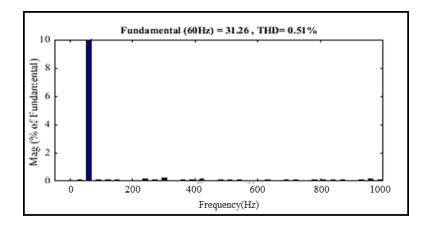

| 3.6  | Point of common coupling (PCC) voltage under a balanced load (0.8 PF), unbalanced load, and nonlinear load at a time of 0–0.15, 0.15–0.3, and 0.3–0.45 s, respectively. |    |

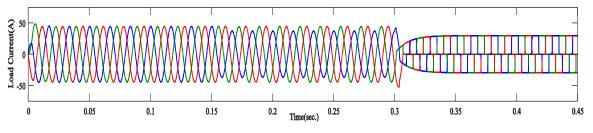

| 3.7  | Load current under a balanced load (0.8 PF), unbalanced load, and nonlinear load at a time of $0-0.15$ , $0.15-0.3$ , and $0.3-0.45$ s, respectively.                   | 76 |

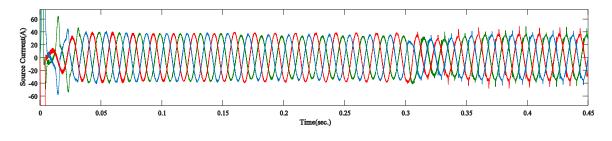

| 3.8  | Source current under a balanced load (0.8 PF), unbalanced load, and nonlinear load at a time of $0-0.15$ , $0.15-0.3$ , and $0.3-0.45$ s, respectively.                 | 76 |

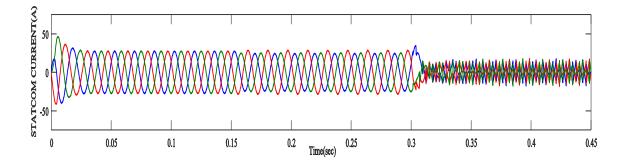

| 3.9  | DSTATCOM current under balanced (0.8 PF), unbalanced, and non-<br>linear loads at times of 0–0.15, 0.15–0.3, and 0.3–0.45 s, respectively.                              | 76 |

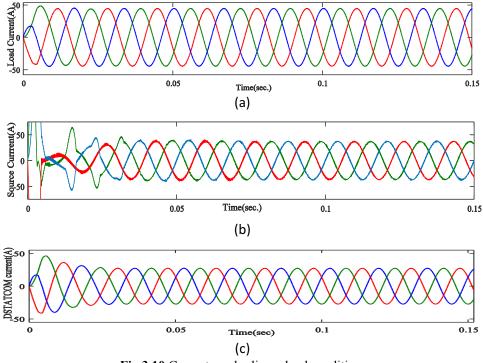

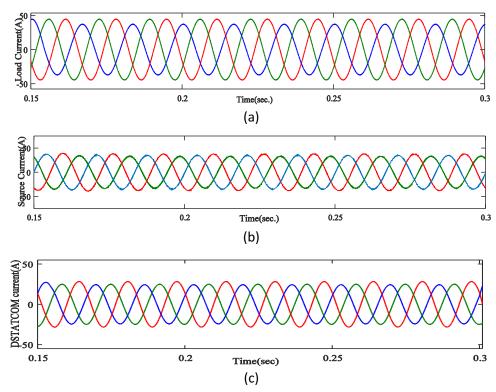

| 3.10 | Currents under linear load conditions. (a) Load current; (b) source current; and (c) DSTATCOM current.                                                                  | 77 |

| 3.11 | Currents under unbalanced load conditions. (a) Load current; (b) source current; and (c) DSTATCOM current.                                                              | 77 |

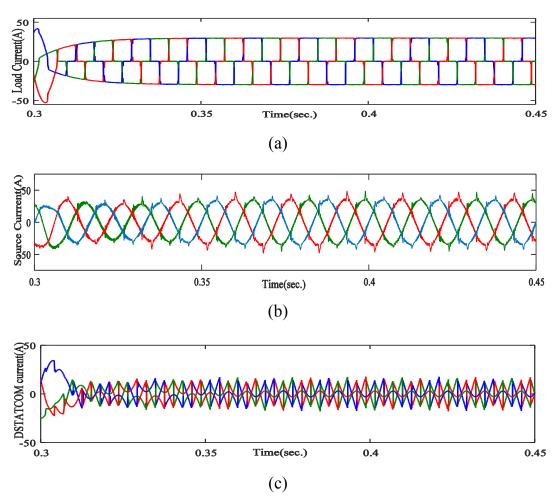

| 3.12 | Currents under nonlinear load conditions. (a) Load current; (b) source current; and (c) DSTATCOM current.                                                               | 78 |

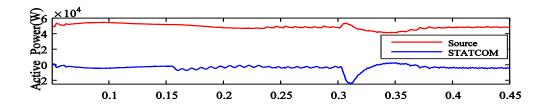

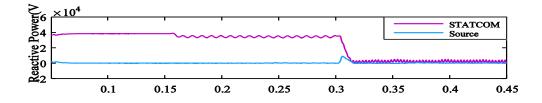

| 3.13 | Active power supplied by source and DSTATCOM under different load conditions.                                                                                          |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.14 | Reactive power supplied by source and DSTATCOM under different load conditions.                                                                                        |     |

| 3.15 | Load power required under different load conditions.                                                                                                                   | 79  |

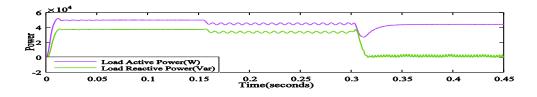

| 3.16 | (a) Peak amplitude of PCC voltage during load change; and (b) zoomed view.                                                                                             | 80  |

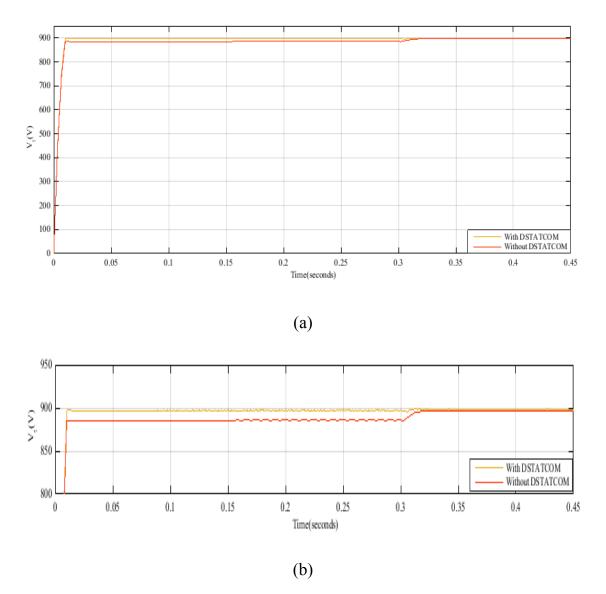

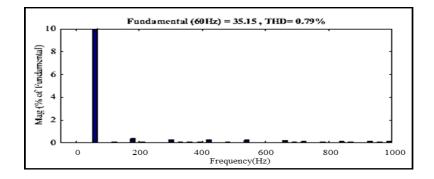

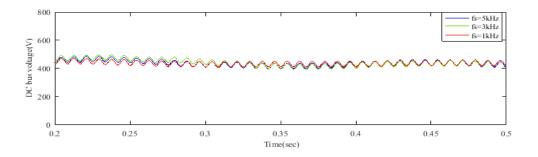

| 3.17 | THD of source current under linear load conditions.                                                                                                                    | 81  |

| 3.18 | THD of source current under unbalanced load conditions.                                                                                                                | 82  |

| 3.19 | THD of source current under nonlinear load conditions.                                                                                                                 | 82  |

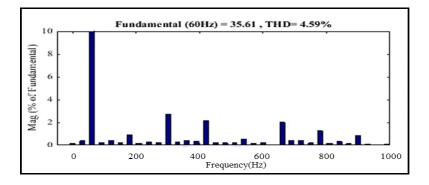

| 3.20 | DC bus voltage ripples for different capacitor values.                                                                                                                 | 83  |

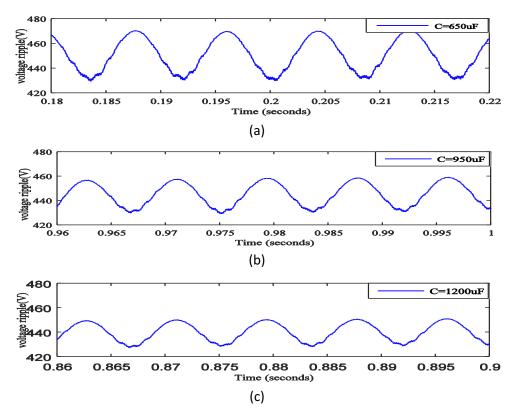

| 3.21 | DC bus voltage of 450 V and voltage ripples at different switching frequencies.                                                                                        | 84  |

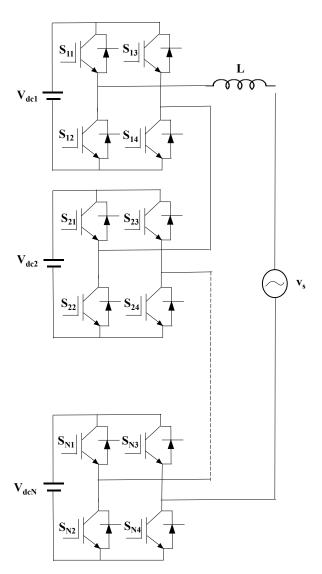

| 4.1  | Grid connected CHMLI                                                                                                                                                   | 88  |

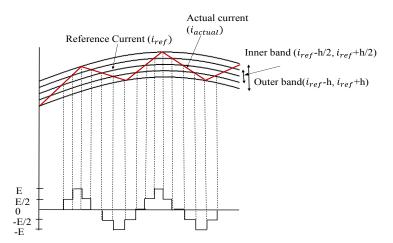

| 4.2  | Control technique for CHMLI                                                                                                                                            | 89  |

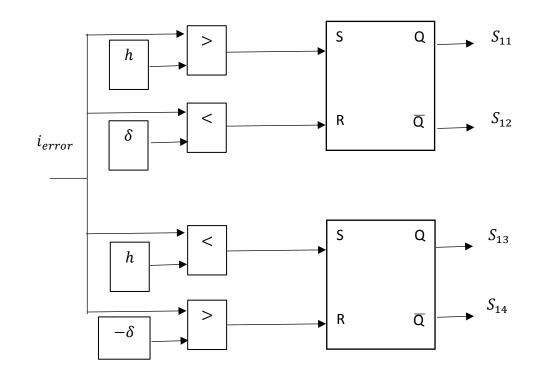

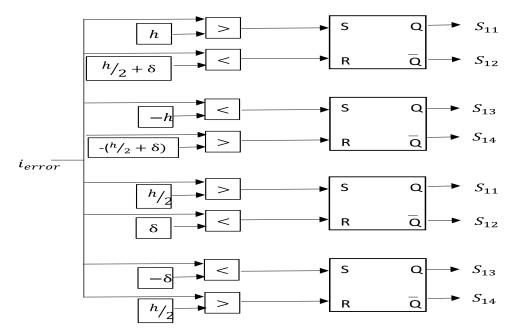

| 4.3  | Multiband HCC for thee level inverter                                                                                                                                  | 90  |

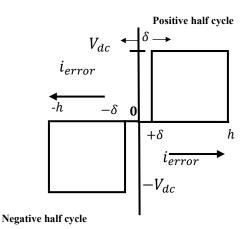

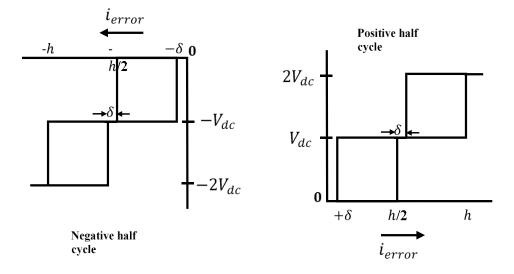

| 4.4  | Output voltage and hysteresis band variation                                                                                                                           | 91  |

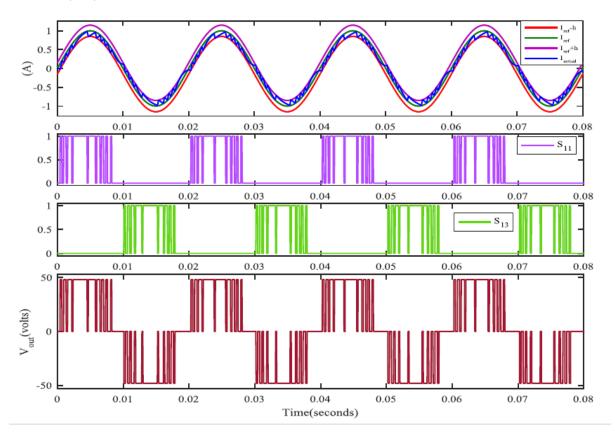

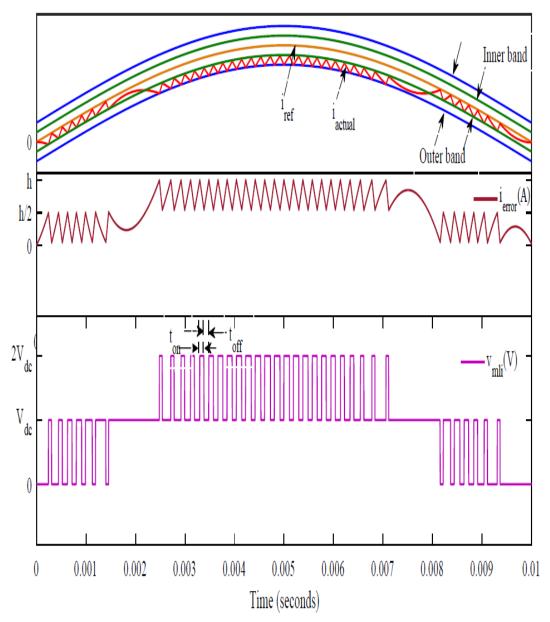

| 4.5  | Multiband HCC controlled inverter output voltage with corresponding gate signals and actual current with reference current for three level inverter.                   | 91  |

| 4.6  | (a) Output voltage and hysteresis band variation                                                                                                                       | 93  |

|      | (b) Multiband HCC for the Five Level Inverter                                                                                                                          | 93  |

| 4.7  | Multiband HCC controlled inverter output voltage with corresponding gate signals and actual current with reference current for five level inverter.                    | 94  |

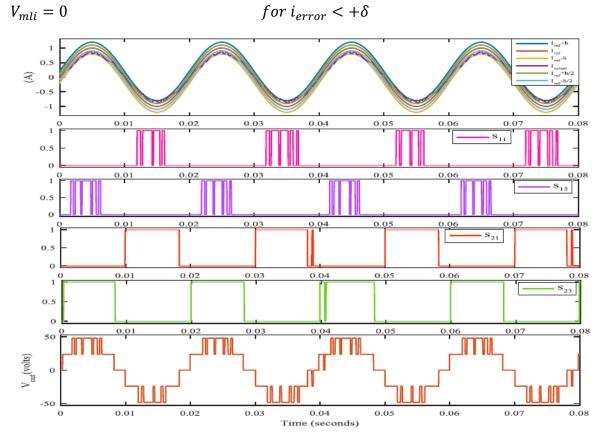

| 4.8  | Multiband HCC controlled inverter output voltage with current error, reference current and actual current.                                                             | 96  |

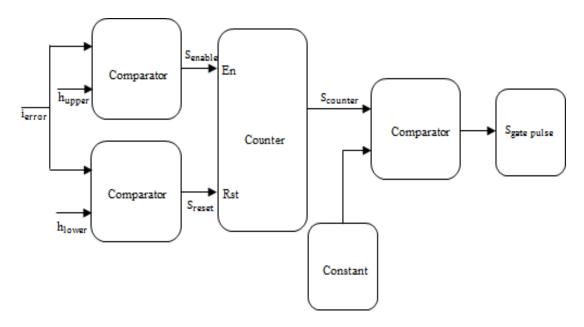

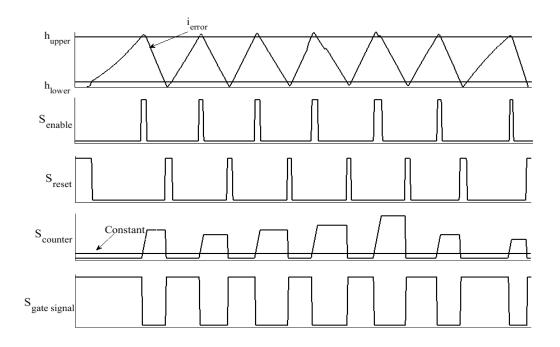

| 4.9  | Block diagram of XSG based Hysteresis controller                                                                                                                       | 100 |

| 4.10 | Intermediate signal synthesis and operation of digital hysteresis controller.                                                                                          | 100 |

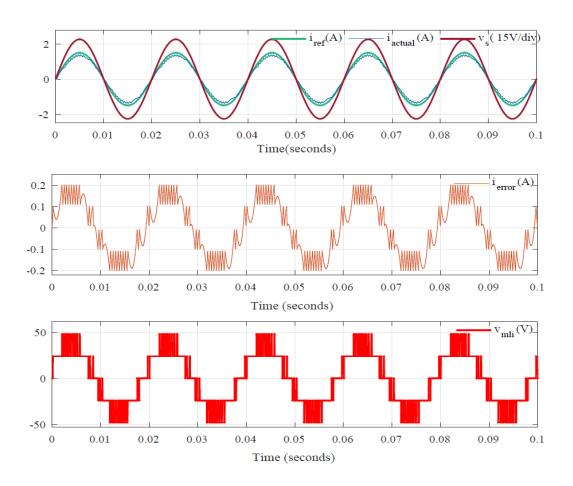

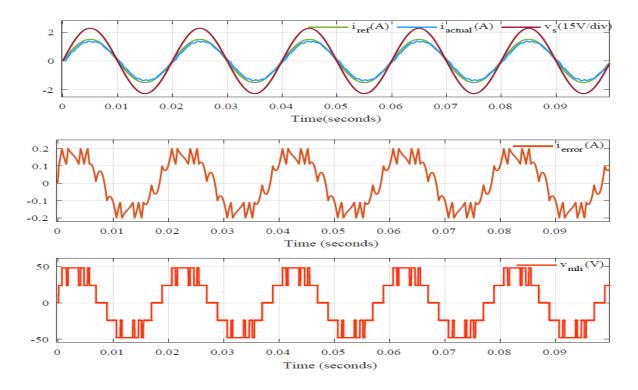

| 4.11 | Grid voltage, reference current, actual current and Multiband HCC controlled inverter output voltage with corresponding current error when $h = 0.2A$ and $L = 33$ mH. | 102 |

| 4.10 |                                                                                                                                                                                                 | 102 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.12 | Grid voltage, reference current, actual current and Multiband HCC controlled inverter output voltage with corresponding current error when $h = 0.2A$ and $L = 66mH$ .                          | 103 |

| 4.13 | Grid voltage, reference current, actual current and Multiband HCC controlled inverter output voltage with corresponding current error when $h = 0.1A$ and $L = 33$ mH.                          | 103 |

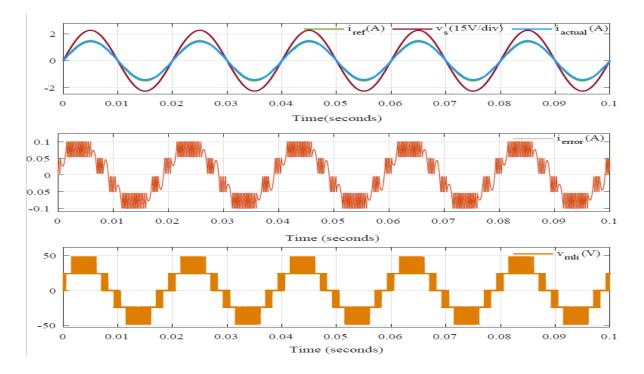

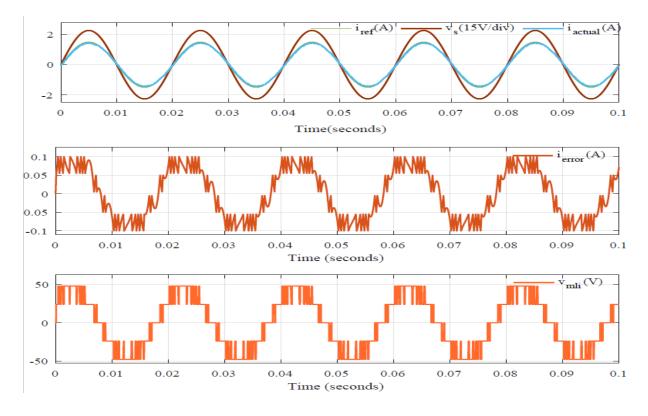

| 4.14 | Grid voltage, reference current, actual current and Multiband HCC controlled inverter output voltage with corresponding current error when $h = 0.1A$ and $L = 66mH$ .                          | 104 |

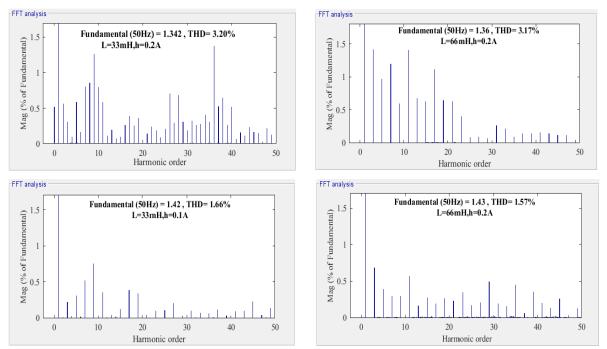

| 4.15 | FFT analysis of the actual current and Corresponding THD for different values of hysteresis band and inductance.                                                                                | 104 |

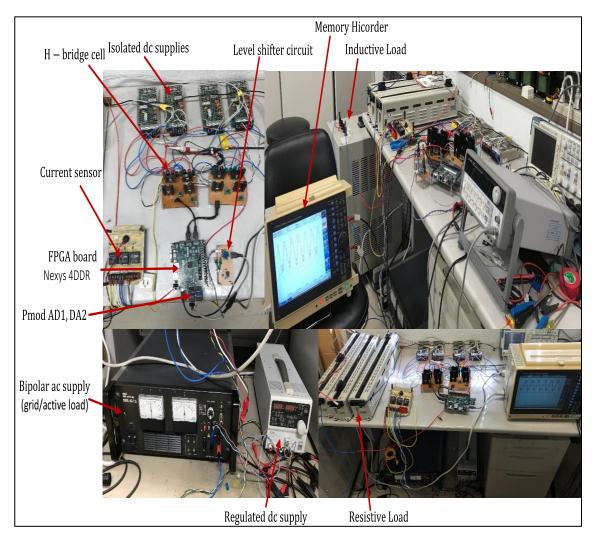

| 4.16 | Experimental set up for the system                                                                                                                                                              | 105 |

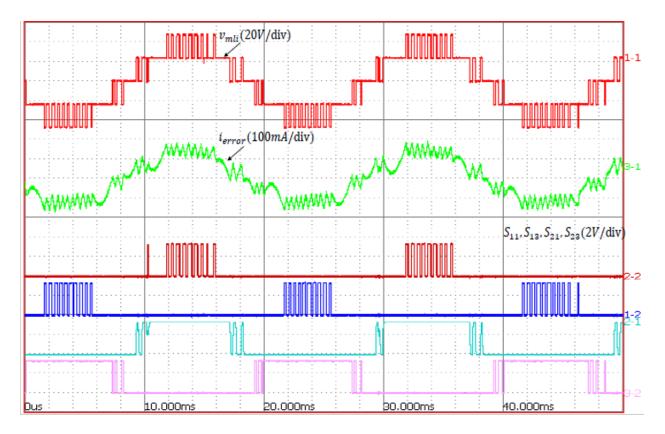

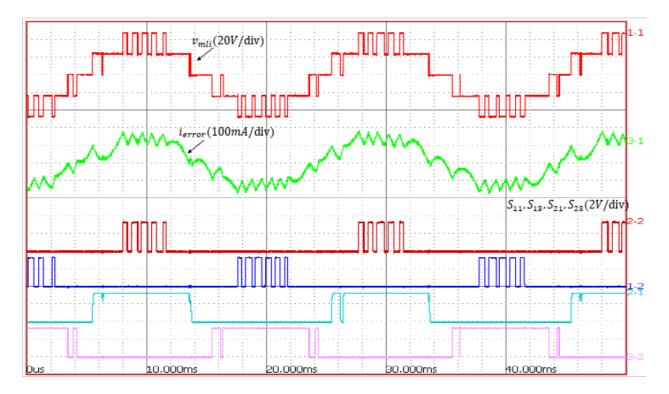

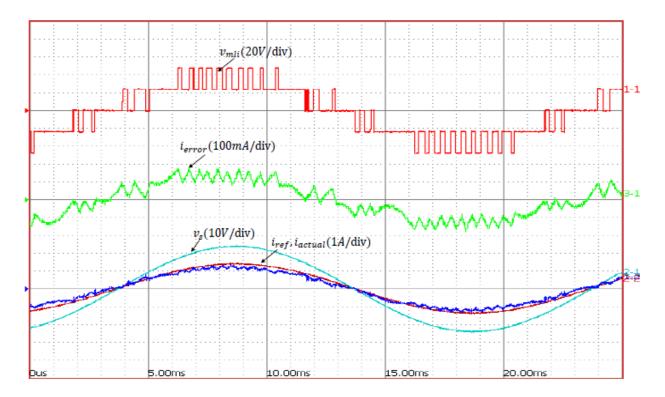

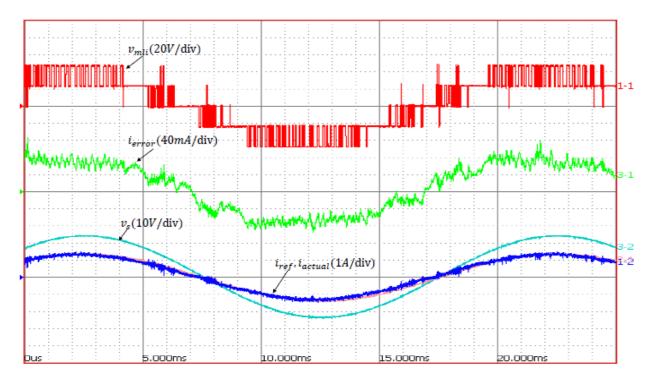

| 4.17 | Experimental results for generated five level output voltage, current error and corresponding gate signal when $L = 66mH$ and $h=0.2A$ .                                                        | 106 |

| 4.18 | Experimental results for generated five level output voltage, current error and corresponding gate signal when $L = 66mH$ and $h=0.2A$ .                                                        | 107 |

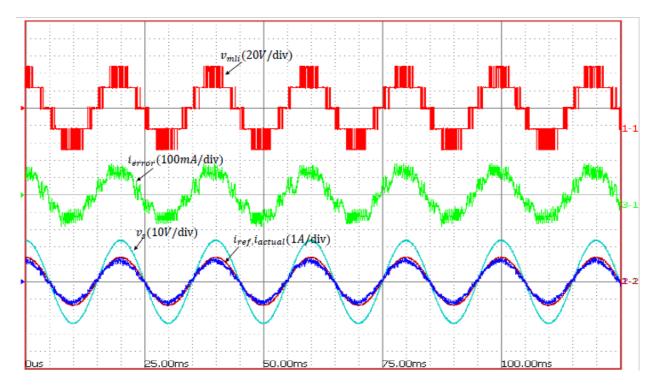

| 4.19 | Experimental results for the five level voltage output, current error, grid Voltage, actual current and $L = 33mH, h = 0.2A$ .                                                                  | 108 |

| 4.20 | Experimental results for the five level voltage output, current error, grid voltage, actual current and reference current with $L = 33mH,h = 0.2A(zoomed view)$ .                               | 108 |

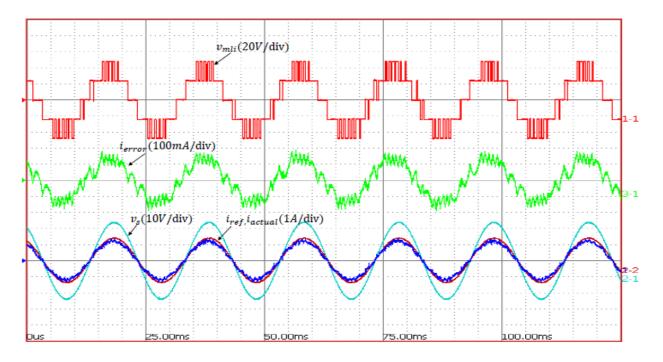

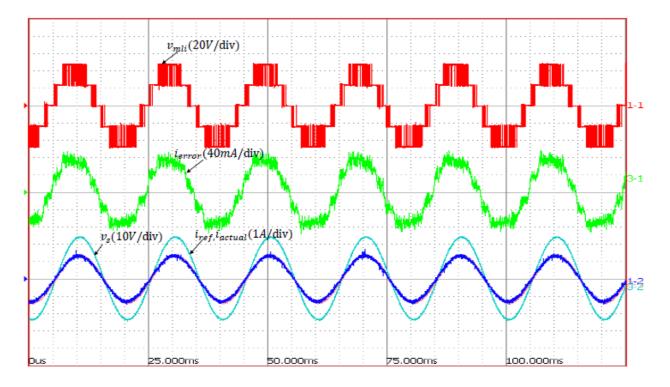

| 4.21 | Experimental results for the five level voltage output, current error, grid voltage, actual current and reference current with $L = 66mH, h = 0.2A$ .                                           | 109 |

| 4.22 | Experimental results for the five level voltage output, current error, grid voltage, actual current and reference current with $L = 66 \text{mH}, \text{h} = 0.2 \text{A}(\text{zoomed view}).$ | 109 |

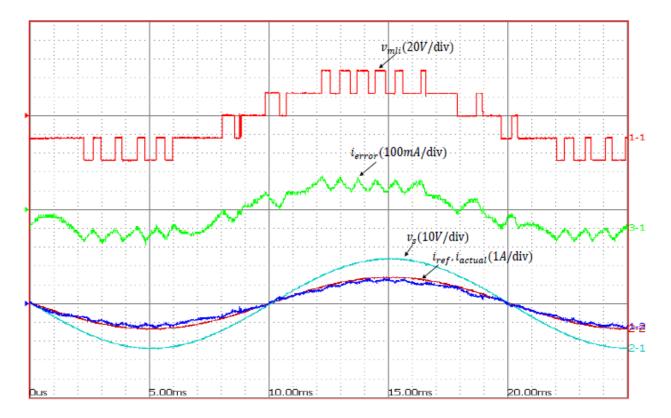

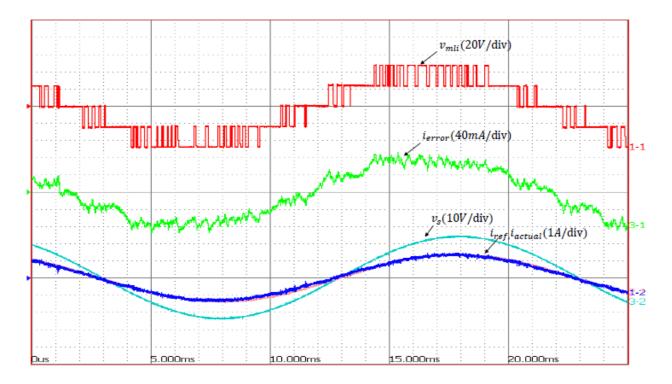

| 4.23 | Experimental results for the five level voltage output, current error, grid voltage, actual current and reference current with $L = 33 \text{mH}, \text{h} = 0.1 \text{A}.$                     | 110 |

| 4.24 | Experimental results for the five level voltage output, current error, grid voltage, actual current and reference current with $L = 33mH,h = 0.1A(zoomed view)$ .                               | 110 |

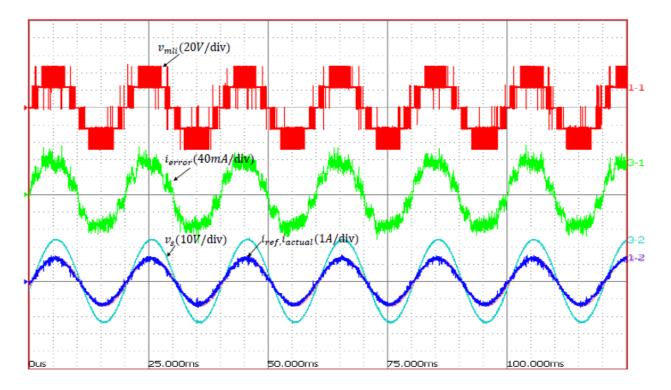

| 4.25 | Experimental results for the five level voltage output, current error, grid voltage, actual current and reference current with $L = 66mH$ , $h = 0.1A$ .                                        | 111 |

| 4.26 | Experimental results for the five level voltage output, current error, grid voltage, actual current and reference current with L =66mH, $h = 0.1A.(zoomed view)$                                | 111 |

| 5.1  | Operational diagram of CHMLI based DSTATCOM                                                                                                                                                     | 114 |

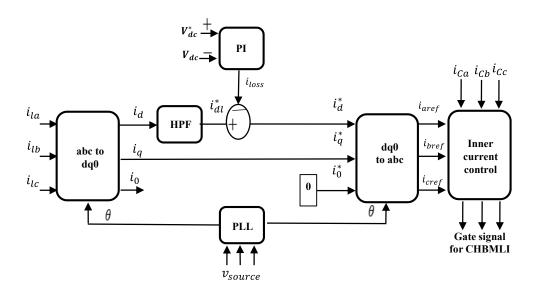

| 5.2  | Current control algorithm for generation of reference current                                                                                                                                   | 115 |

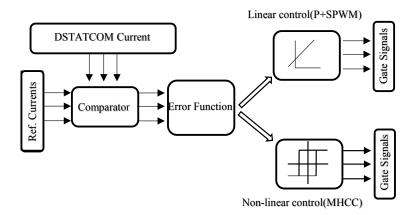

| 5.3  | Inner current control for DSTATCOM                                                           | 116 |

|------|----------------------------------------------------------------------------------------------|-----|

| 5.4  | CHB multilevel inverter output corresponding to multiple band                                | 117 |

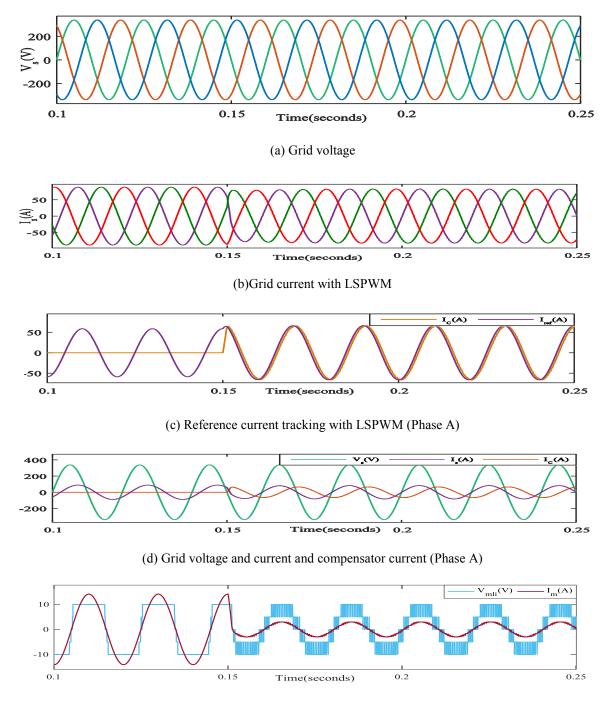

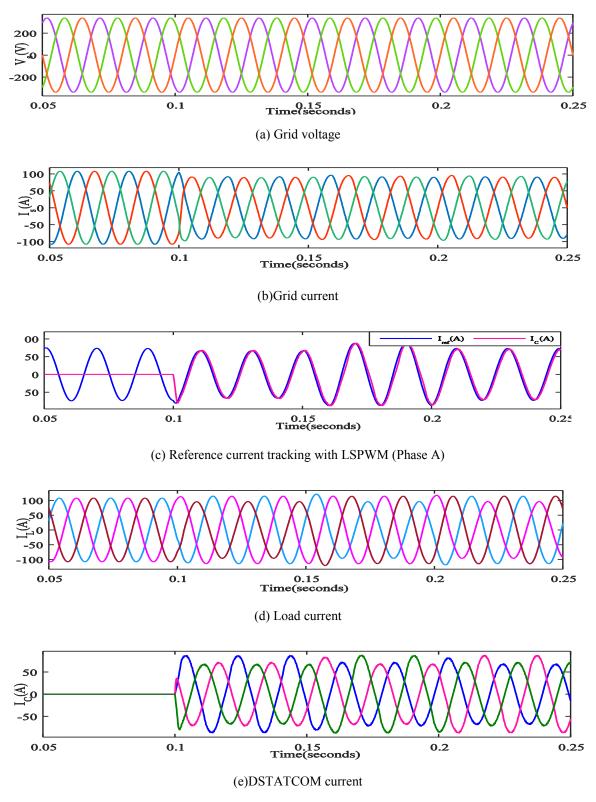

| 5.5  | Performance of LSPWM with linear load condition (DSTATCOM switched at t=0.15 sec.            | 119 |

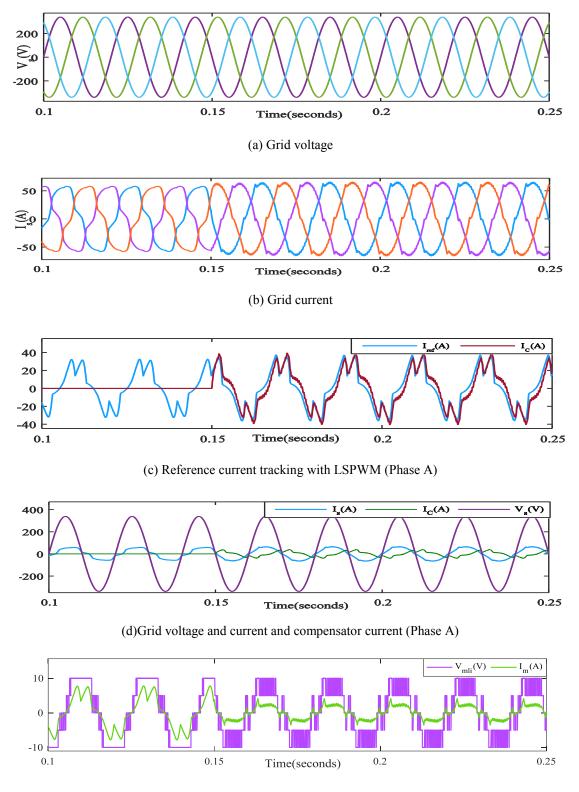

| 5.6  | Performance of LSPWM with unbalanced load condition (unbalance load switched at t=0.1 sec.)  | 120 |

| 5.7  | Performance of LSPWM with non-linear load condition (DSTATCOM switched on at t=0.15sec.)     | 121 |

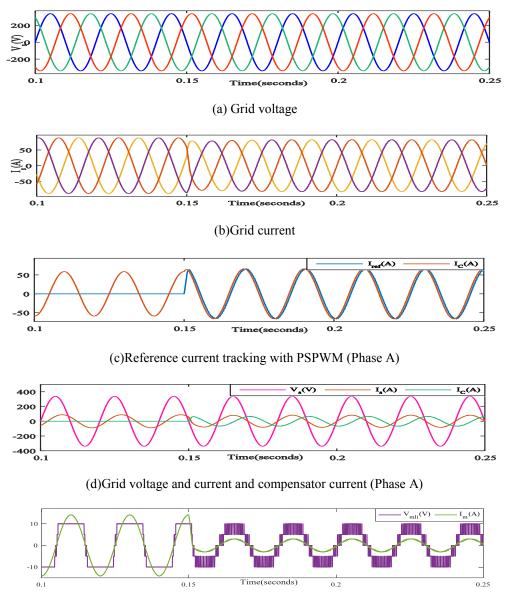

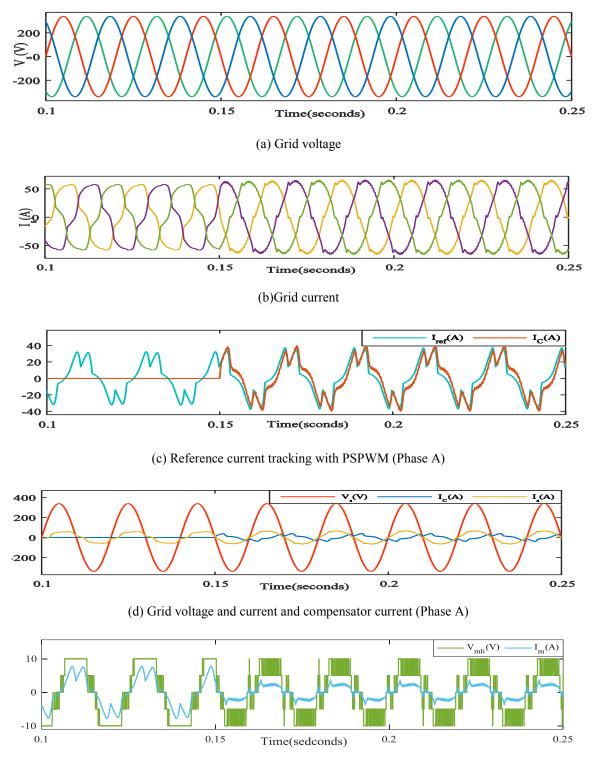

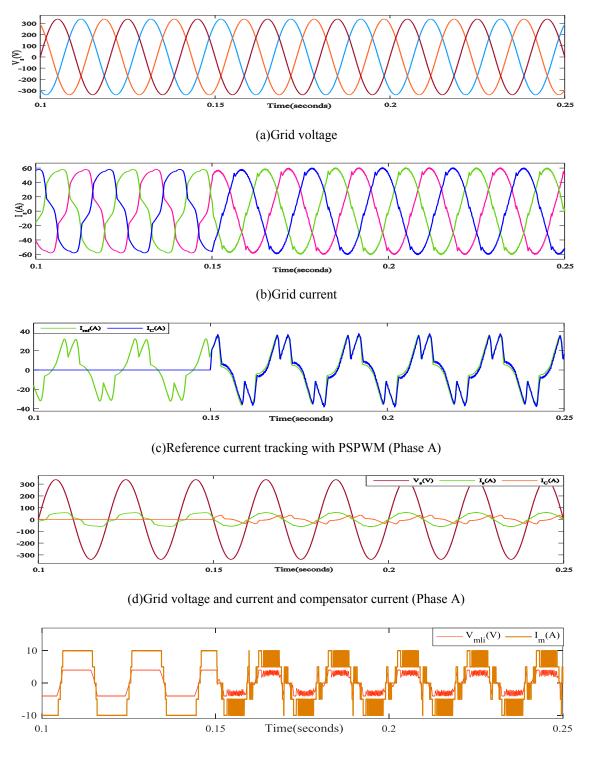

| 5.8  | Performance of PSPWM with linear load condition (DSTATCOM switched on at t=0.15 sec.         | 122 |

| 5.9  | Performance of PSPWM with Unbalance load condition (unbalancing at t=0.1s)                   | 123 |

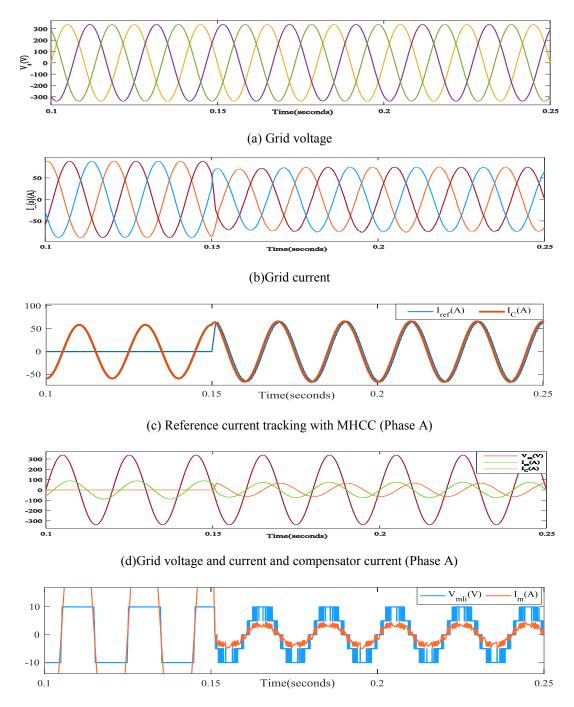

| 5.10 | Performance of PSPWM with Non-linear load condition (DSTATCOM is switched on at t=0.15 sec.) | 124 |

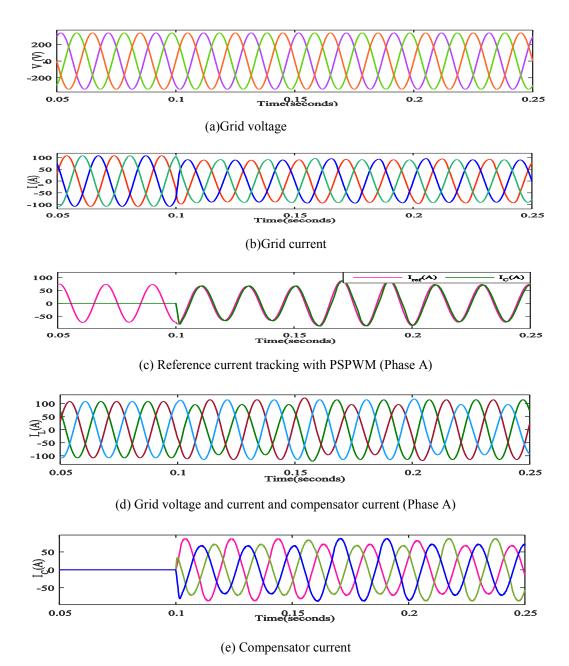

| 5.11 | Performance of MHCC with linear load condition (DSTATCOM switched on at t=0.15 sec.          | 125 |

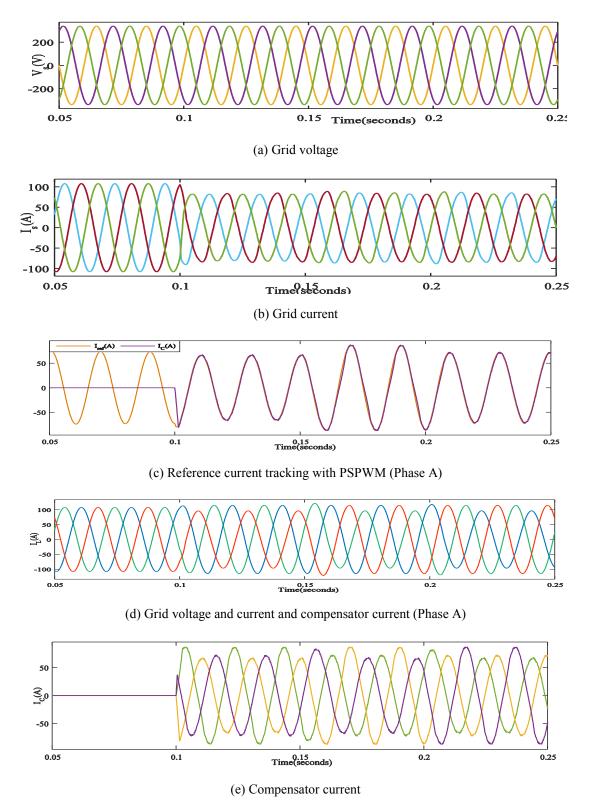

| 5.12 | Performance of MHCC with unbalanced load condition (unbalancing at t=0.1 seconds.            | 126 |

| 5.13 | Performance of MHCC with non-linear load condition (DSTATCOM switched on at t=0.15 seconds.  | 127 |

| 1.1 | Comparison of conventional and multilevel inverters                   | 9   |

|-----|-----------------------------------------------------------------------|-----|

| 2.1 | Voltage level and switching state of single phase five level inverter | 30  |

| 2.2 | Fundamental Output voltage of CHMLI                                   | 59  |

| 3.1 | Parameters for the DSTATCOM system                                    | 75  |

| 5.1 | Parameters for multiband HCC based DSTATCOM                           | 118 |

| 5.2 | Comparison of PSPWM, LSPWM and MHCC for grid connected system         | 128 |

| 5.3 | THD of grid current (is) under different load condition               | 128 |

| 5.4 | THD of voltage at PCC (Vpcc) under different load condition           | 129 |

# **LIST OF TABLES**

# **CONTENTS**

| S.No. | CHAPTER NAME                                                             | Page  |

|-------|--------------------------------------------------------------------------|-------|

| 1.    | Introduction                                                             | 1-26  |

|       | 1.1 Energy and Electricity                                               | 01    |

|       | 1.2 General trends & Literature Review                                   | 3     |

|       | 1.3 Objectives                                                           | 24    |

|       | 1.4 Organization of Dissertation                                         | 25    |

| 2.    | Cascaded H-bridge Multilevel Inverter And FPGA<br>Hardware Co-simulation | 27-60 |

|       | 2.1 General                                                              | 27    |

|       | 2.2 H-bridge Inverter                                                    | 28    |

|       | 2.2.1 Bipolar Pulse Width Modulation                                     | 29    |

|       | 2.2.2 Unipolar Pulse Width Modulation                                    | 30    |

|       | 2.3 Cascaded H-bridge Multilevel Inverter                                | 30    |

|       | 2.4 Experimental evaluation: FPGA based digital control                  | 36    |

|       | 2.5 Carrier based Pulse width modulation                                 | 38    |

|       | 2.5.1 Phase shifted carrier based PWM technique                          | 39    |

|       | 2.5.2 Level shifted carrier based PWM technique                          | 45    |

|       | 2.6 Third harmonics injected PWM                                         | 51    |

|       | 2.6.1 THIPWM for phase shifted carriers                                  | 54    |

|       | 2.6.2 THIPWM for level shifted carriers                                  | 54    |

|       | 2.7 FPGA hardware co-simulation for THIPWM controlled CHMLI              | 55    |

|       | 2.7.1 Discussion on Hardware Co-simulation results                       | 57    |

|       | 2.7.2 Performance of phase shifted THIPWM                                | 57    |

|       | 2.7.3 Performance of level shifted THIPWM                                | 59    |

|       | 2.8 Conclusion                                                           | 59    |

| 3.    | LCL filter interfaced DSTATCOM                                           | 61-84 |

|       | 3.1 General                                                              | 61    |

|    | 3.2 System Description and Design                        | 63     |

|----|----------------------------------------------------------|--------|

|    | 3.2.1 Basis Structure                                    | 63     |

|    | 3.2.2 Implemented System                                 | 64     |

|    | 3.2.3 DC Link System                                     | 66     |

|    | 3.2.4 Reference Current Generation for CHMLI             | 68     |

|    | 3.3 SPWM for CHMLI                                       | 70     |

|    | 3.4 Grid Interface Filter                                | 70     |

|    | 3.4.1 LCL Filter                                         | 70     |

|    | 3.4.2 Design constraints for LCL Filter                  | 71     |

|    | 3.4.3 Proposed LCL Filter for CHMLI based system         | 73     |

|    | 3.5 Performance Evaluation, Results and Discussion       | 73     |

|    | 3.5.1 System Performance                                 | 73     |

|    | 3.5.1.1 Linear Load Condition                            | 73     |

|    | 3.5.1.2 Non-Linear Load Condition                        | 77     |

|    | 3.5.2 Power Quality Analysis                             | 79     |

|    | 3.5.2.1 Voltage Disturbance                              | 79     |

|    | 3.5.2.2 Fast Fourier Transform Analysis                  | 80     |

|    | 3.5.3 Effect of System Parameters                        | 82     |

|    | 3.5.3.1 DC Link Capacitor                                | 82     |

|    | 3.5.3.2 Switching Frequency                              | 83     |

|    | 3.6 Conclusion                                           | 84     |

| 4. | Multiband Hysteresis Current Controlled CHMLI            | 85-104 |

|    | 4.1 General                                              | 85     |

|    | 4.2 Grid Connected Cascaded H-bridge Multilevel Inverter | 87     |

|    | 4.2.1 Control strategy                                   | 87     |

|    | 4.3 Digital Hysteresis Current Control for CHMLI         | 89     |

|    | 4.3.1 Multiband HCC                                      | 90     |

|    | 4.3.1.1 Three level operation                            | 90     |

|    | 4.3.1.2 Five level operation                             | 93     |

|    | 4.3.2 Effect of Parameters                                            | 97      |

|----|-----------------------------------------------------------------------|---------|

|    | 4.3.3 Effect of Equal Band Division                                   | 99      |

|    | 4.4 Digital HCC Based on Xilinx System Generator                      | 99      |

|    | 4.5 Performance Evaluation of Digital Multiband HCC                   | 101     |

|    | 4.5.1 Simulation Results                                              | 101     |

|    | 4.5.2 Experimental Verification                                       | 105     |

|    | 4.6 Conclusion                                                        | 112     |

| 5. | Multiband HCC for Cascaded H-bridge inverter based DSTATCOM           | 113-129 |

|    | 5.1 General                                                           | 113     |

|    | 5.2 Cascaded H-bridge Inverter based DSTATCOM                         | 113     |

|    | 5.2.1 DSTATCOM System and Operation                                   | 113     |

|    | 5.2.2 Direct Current Control SRFT for Reference Current<br>Generation | 114     |

|    | 5.2.3 Current control and Modulator                                   | 116     |

|    | 5.3 Multiband Hysteresis Current Controller for DSTATCOM              | 117     |

|    | 5.4 Performance Evaluation of DSTATCOM                                | 118     |

|    | 5.4.1 Performance under Level Shifted PWM                             | 118     |

|    | 5.4.2 Performance under Phase Shifted PWM                             | 122     |

|    | 5.4.3 Performance under MHCC                                          | 125     |

|    | 5.5 Conclusion                                                        | 129     |

| 6. | Conclusion                                                            | 130-131 |

|    | References                                                            | 132-142 |

# CHAPTER 1 Introduction

### **1.1 Energy and Electricity**

The development in social and economic life of human kind persuaded the need of energy and its management to deliver at best efficiency. We have achieved certain compatibility to use available resources by growing technology and creating man made machines. Since last 100 years the technology word evaluated for the external and internal progress of a manufacturing, transmission, and distribution.

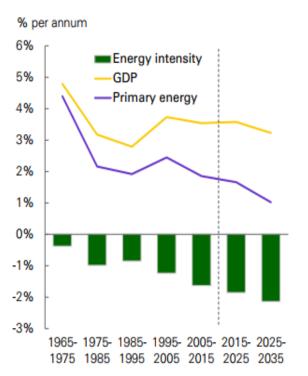

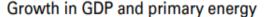

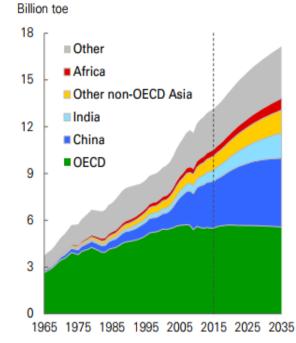

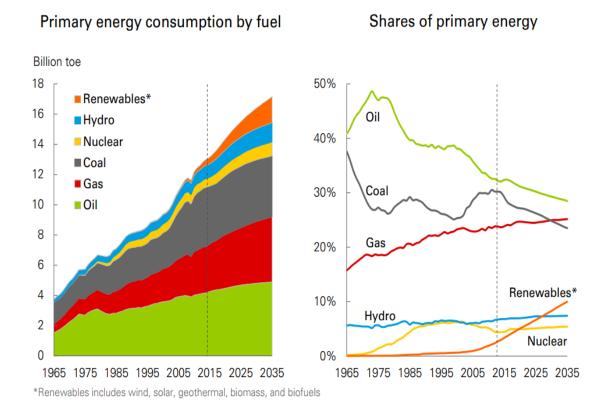

Now we are living in real world which is a global society and where nations are increasingly independent bodies to confront for competitiveness of global demand and supply of energy sources. The world economy is expected to almost double over the next 20 years, with growth rate of averaging 3.4% per annum. Fig.1.1 shows how the energy consumption will take place according to different geographical regions: OECD (organization for economic co-operation and development) and other countries. In Fig.1.2, it is shown that present scenario of contribution of different kind of energy sources to the global energy consumption. What happens today in India and Japan, for example, affects USA and vice-versa. All the nation are facing industrial competitiveness in the marathon of global market and progress for sustainable economic position. As we know that energy prices are increasing due to limitation of conventional energy sources. Electrical energy has become one of the leading source to drive machines and so forth many industrial and domestic processes. In such a competitive environment power electronics technology with motion control is having a dominance and progressive development in the area of electrical energy conversion systems. [1]-[3].

To achieve environment friendly electrical energy generation, transmission and distribution power electronics technology emerged as an adequate option and spread to every corner of industrial, commercial, transportation, aerospace, residential, military and utility grid systems[4]-[5]. For the controlled operation and management of electrical energy it is required to control the voltage, current, power and frequency from generation to the consumer end. The commercial availability of electricity has been started particularly by the invention of induction motors then the age of solid state electronics by the invention of transistors in 1948, and commercially thyristor was

introduced in 1958[6] and processed the evolution of modern power electronics. After gradual development to the age of integrated circuits, computers, communication and robotics, now it has been reached to world of internet. Energy consumption in the world has been increased through over last six decades. During these development ages the growth in generation and consumption in proportion to cater the need of increasing population of the world, we had hardly considered their adverse effect on environment.

Energy consumption by region

Figure.1.1 Gross domestic product (GDP) growth over six decades with energy intensity followed by energy consumption by region (source: 2017 energy outlook)[5]

We can say that most of the sources are finishing so renewable ones are the adequate option for environment friendly clean power system. The available or developing electrical energy sources has strong daily and seasonal pattern. And the electric power demand at consumer end could have different characteristics. Therefore it would be difficult to operate an electrical system installed with only renewable generation systems due to high uncertainty and unavailability in renewable energy generation in course of time. The better option to utilize these energy sources connected with grid at distribution level [7]-[9].

#### **1.2 General Trends and Literature Review**

In conventional power system, large scale power generation units (plants) located at adequate places generate most of the power. Then followed by generation, it is transferred to the large consumers or distribution station through long transmission lines. The control and monitoring is continuously done by control centers mainly to ensure power quality namely voltage and frequency. However power system is changing since last two decade as large number of dispersed generation units including renewable and non-renewable such as photovoltaic (PV) generation, wind turbines, small hydro, fuel cells, gas, heat and power station have emerged[10]-[14].

The generator operate at a fixed speeding at conventional generation stations, and so total operation can be done on fixed frequency but present time sources such as wind mills generates voltage with variable frequency, similarly fuel cell and PV generated power cannot fed to the grid directly, or cannot be connected to the grid directly. Here so forth power electronics plays a important role in matching characteristics of these sources to the power grid that is associated with the conventional

energy sources. The parameters such as voltage, frequency, control of reactive and active power, high order harmonics minimization etc. are need to be controlled and optimized using power electronics technology[15].

Power electronics being the electrical energy conversion technology, plays vital role in modern industrial process and renewable energy integration to the grid [16]. It is a very essential part of the system to match the characteristics of generated power and required power by consumer. To achieve high efficiency performance of grid connected system one need to have control on power electronics energy conversion system [17]-[20].

It is well known that high efficiency and fast switching silicon power semiconductor devices e.g. thyristor, triac, gate turn-off thyristor (GTO), power MOSFET, insulated gate bipolar transistor (IGBT), and integrated gate-commuted thyristor (IGCT) comprises the power electronics. And application of these fast switching devices includes regulated dc and ac power supplies, uninterruptable power supplies electromechanical processes, lighting and heating control, distribution static synchronous compensator(DSTATCOM), static var generator(SVG), static var compensator(SVC), active power filters(APFs), HVDC transmission systems, flexible ac transmission systems(FACTS), grid integration of PV and fuel cell converters, dc and ac circuit breakers, high-frequency heating, energy storage, motor drives application that includes computer and peripherals , motor starters, transportation system, home appliances, paper and textile mills, pumps, compressors, cement and rolling mills, machinery tools and robotics, including constant frequency variable speed systems., etc. In the 21st century the widespread application of power electronics is kind of industrial revolution which has been somewhat unmatched in the history [21]-[22].

Power electronics technology associates with efficient energy conversion, control and conditioning of electrical energy from source to load. In present scenario communities are working on improvement in the efficiency of power electronics converters [23]. In this process evolution of faster devices, improved topologies, advance control are key steps are being taken by researchers. Normally power electronics converters are being the part of system to convert the provided electrical power in its customized form with its own efficient capabilities. So for the example the efficiency of the system sometimes is less than efficiency of the converter in some application, such as motor drive application, PV system, etc. [24].

Application of power electronics converters for environment friendly electrical system increased in recent years. Likewise power electronics converters are main controllable unit in the renewable energy source integration to the grid and electrification of the automotive industry [25]-[26]. These two application of power electronics converters has been grown rapidly in past years and still growing on. In addition the improved electrical drives has been developed using power electronics converters and most of these drives consume easily available electrical energy in the world [27]-[28].Power electronics converters uses semiconductor devices that can be operated in switching mode to convert and control power, the conversion can be any type such as ac to dc (rectification mode),dc to ac(inversion mode),dc to dc (buck, boost or buck-boost conversion mode), and ac to ac for frequency variation of voltage regulation (at constant frequency) mode[28].

A power conditioning unit is needed for low voltage distribution system for integration of renewable energy sources or operation in non-ideal load conditions for a grid tied application. Solar PV, fuel cells, thermoelectric generator, ultra-capacitors are some example of low voltage dc output energy sources. These low voltage dc sources need to have a conditioned high voltage level before making to ac grid. Some of the low voltage dc and high voltage ac for grid connected application has been proposed to manage some specific issues, such as, low cost, high efficiency, and robustness [29]. The circuit topologies for the power conversion or conditioning is always concerns with the voltage and current levels.

Keeping main focus on the dc-ac inverters can be voltage source inverter or current source inverter. Voltage source inverters have been widely used in the recent applications [30]. If there is a expectation of unity power factor, then some of the switches can be replaced by diodes and some are operated at fundamental frequency, which permits to use reduced number of semiconductor devices efficiently with different combinations for example dual buck, dual boost, and dual buck boost inverters [31]-[34].

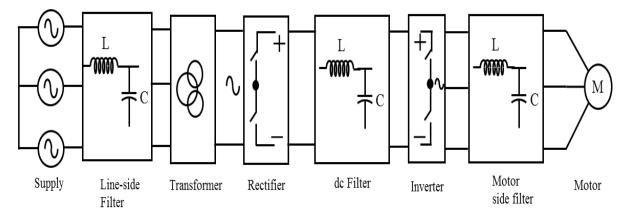

For the designing and optimization tool for the three phase voltage source inverters it has been employed with front end rectifiers. Generally IGBT based voltage source inverters with diode front rectifiers is one of the conventional choice for the three phase inverter fed ac motor drives[35]-[36]. The essential stages are front end rectifier, inverter, the dc link capacitor, the electromagnetic interference harmonic filter. So these components have inter-dependencies and tradeoffs in the power converter, there should be system end optimization and design for the three phase voltage source inverters to describe cost and performance of the system [37][39].

These inverters require high frequency sinusoidal pulse width modulation (SPWM) and output filters to attain sinusoidal current output. And the losses associated with the high switching frequency are non-trivial. Application of the voltage source inverters where efficiency is concerned mostly, some possible improvements has been revived [40]. Such as soft switching inverters, dual buck, boost and buck-boost inverter, multilevel inverters [41][42].

Soft switching inverters are introduced for the motor drive applications using zero voltage switching (ZVS) or zero current switching (ZCS) techniques. Use of cool MOS as primary switching devices and IGBTs as auxiliary switches are used to attain high efficiency energy conversion. The voltage balancing can be done using front end diode dc-dc converter using well balanced split voltage. The components which are added to soft switched inverters are non-negligible and if the power factors has to near unity, it's essential to use dual buck type circuits where one set of antiparallel switches are replaced with diodes [42].To improve efficiency with fast switching ultrafast diode can be employed to avoid low-voltage conduction drop and reverse recovery loss. MOSFETs are optional devices which can be used to speed up the conduction and maintaining the lower cost. The benefit of these type of circuits are robustness with the high efficiency up to 99% and circuits arraignment can avoid shoot through failure[45].Similarly buck switch pair concept can be adopted to dual boost and dual buck boost voltage source inverters.

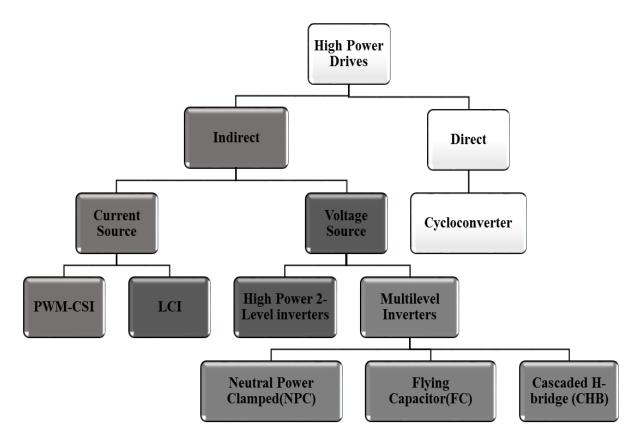

Voltage source inverters shown in Fig. 1.3 are common type of inverter that has been used for drive application [46].Classification can be done on the basis of fundamental parameter topology and connection type of direct and indirect. The former one uses directly connection between sources to load directly using logical semiconductor devices. In other hand later is connected in two stages: rectification and inversion and normally tied up with an energy storage devices. In the direct conversion type one of the common type of converter is used which is cyclo converter in high power application. It interfaces between power supply and machine directly with the use of array of power semiconductor devices. And it converts the three phase ac voltage with variable switching frequency and variable magnitude .Although it has limitation in dynamic performance but it performs the task of power flow in both the direction in very efficient way [47].Matrix

converters are also one of the emerging topology in this family but still needs more research for industrialization and high power application [48].

Indirect converters are well established for industrial and medium power drive application, the primary classification are current source and voltage source topologies with dependency on energy storage components. So as per requirement of the application these converters are employed with the optional line and motor side filters. To reduce line current distortion phase shifted transformer with multiple windings are commonly used. The common topology of rectifiers that has been used with the indirect converters are multiphase diode or thyristor rectifiers and pulse width modulated rectifiers [49]. The capacitor that provides stiff dc voltage can be used as filter or smoothing inductor can be adequate option for filter.

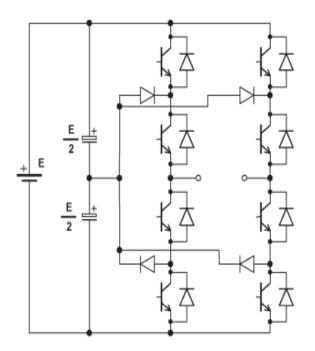

Classification of high power application voltage source inverter of indirect type is darkened in the diagram shown in Fig.1.4 had got more attention and noticeably developed. Voltage source inverters are more efficiently used for industrial application in last two decades compared to current source inverters. Due to limited power rating of semiconductor of devices conventional two level inverter belongs to low and medium voltage application. Series connection of two level inverter with bulky transformers make it enable for high voltage application. Or switching devices can be connected in series to meet increased voltage rating demand. And use of increased number of semiconductor devices with capacitors and diodes permitted a more advent use of these additional switches originates the multilevel voltage source inverters to enhance the quality of input and output parameters [50]-[52].

Figure 1.3 General block diagram of the medium voltage drive [46].

Figure1.4. Classification of converters for high-power drives (>1 MW).

In last two decade industries have grown rapidly and power system become more dependent on power electronics. All started with the higher power machinery which has reached to megawatt level such as ac drives are connected to medium voltage grid and it is difficult to connect these high power devices directly to the grid. To overcome with this problem a new family of inverters has come in industrial and commercial use in last two decade i.e. multilevel inverter (MLI). Although full scale industrialization is still not achieved due to complex control and design of system [53].

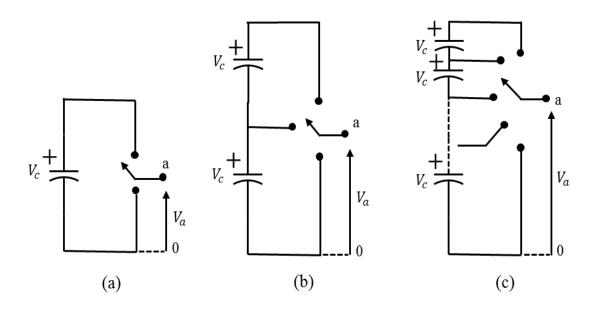

MLIs comprises an array of power semiconductor devices that generates synthesized stepped output voltage from capacitor voltage. Commutation of switches that permits cumulative addition of voltage across capacitors by which high voltage output can be achieved by maintaining low voltage across power semiconductor devices. The basic extended schematic diagram of capacitor voltage source inverters are shown in Fig.1.5 to generate two level, three levels and more level of output voltage. For the generation of levelled output ideal power switches are shown with different positions.

Figure 1.5 One phase leg of an inverter with (a) two levels, (b) three levels, and (c) n levels [53].

In (a) two level inverter output (two values) i.e. positive value and negative value with respect to ground or negative terminal of capacitor. In other hand using three level of inverter, three values i.e. positive value, negative value and zero or more levels can be generated. For single phase, m is defined as the number of levels or steps generated then steps in voltage between two phases of the load are 2m+1. Similarly for wye connected load the steps in phase voltage can be determined. The terminology of multilevel inverters started by Nabae [54] and it started with three level inverter. The output voltage have more steps generating a staircase waveform, by increasing the number of levels in the inverter, which possess less harmonic distortion.

The reason behind there has been lots of attention paid to MLIs, because these inverters has some attractive features which are summarized as follows,

- 1. MLIs can generate synthesized output voltage with very low distortion and low dv/dt.

- 2. The load current supplied by MLIs consists very low distortion.

- 3. Common mode voltage has been very critical issue with conventional inverters, MLIs offers very smaller common mode voltage.

- 4. In addition some novel or hybrid PWM control can be implemented to achieve low stress on switching devices.

- 5. MLIs can operate at lower switching frequency compared to conventional multilevel inverters.

- 6. For medium voltage high power applications transformers can be eliminated from the systems as it offers less stress on switches.

- 7. The electromagnetic interference can be tolerated by use of MLIs and many more.

Table 1.1 shows the basic comparison between multilevel inverters and conventional two level inverters.

| S.No. | Conventional VSI                                                     | Multilevel Inverters                                                 |

|-------|----------------------------------------------------------------------|----------------------------------------------------------------------|

| 1     | High total harmonic distortion(THD) in output voltage                | Low THD in output voltage                                            |

| 2     | Higher switching stress on power<br>switches                         | Reduced switching stress on power semi-<br>conductor devices.        |

| 3     | Not suitable for high voltage application.                           | Applicable for high voltage high power application.                  |

| 4.    | Higher voltage levels cannot be produced                             | Higher voltage level can be produced.                                |

| 5.    | Electromagnetic interference (EMI) is high due to high dv/dt.        | Since dv/dt is low the EMI from the system is low                    |

| 6.    | Higher switching losses due to high operational switching frequency. | Lower switching losses due to lower operational switching frequency. |

| 7.    | Power bus structure hence control scheme is simple.                  | Complexity in control scheme increases as number of level increases. |

Table 1.1 Comparison of conventional and multilevel inverters

The results shown in a patent [58] are evident that the multilevel topology have been in the research since last 35 years but not commercialized on full scale yet. As in that patent cascaded inverter was evaluated by connecting H-bridges to isolated dc sources to generate synthesized staircase output ac voltage [59]. Following the manipulation in cascaded MLIs , diodes has been used to

block sources at different steps and diode clamped MLIs were introduced [60]. The diode clamped inverters become very common at that time three level output voltage was achieved by introducing mid-level voltage as neutral point voltage in addition named as neutral point clamped(NPC) MLIs. NPC inverter topology doubled the device voltage level effectively with any restriction of precise voltage matching and this topology is prevailed for research and commercial usage.

The application as an extended multilevel inverters for NPC topology was found in [61].Besides early recognition of the cascaded MLIs and its broad level application did not subjugated till 1990s.Two major applications have been found that to advocate its use in motor drive and utility grids [62][63].As requirement of medium voltage high power inverter increases with the development and vast industrialization, cascaded inverters has drawn major interest ever since. Many patents can be found on the cascaded multilevel inverter use for regenerative type motor drive or utility grids [64][65]. A major MLI topology which was introduced followed by cascaded MLIs and diode clamped is capacitor clamped MLI [66]. These three topologies of multilevel inverters are extensively used in medium voltage high power application. The application of MLIs are extended but not limited to laminators, mills, blowers, conveyors, pumps, fans compressors and so on.

Figure 1.6 Diode clamped multilevel inverter topology [61]

Figure 1.7 Capacitor clamped multilevel inverter topology [66]

Figure 1.8 Cascaded H-bridge multilevel inverter topology [72]

The use of multilevel inverters tremendously increased in last few years for renewable energy source integration to grid. MLIs have used for medium voltage high power applications as a static synchronous reactive power compensator and motor drives. Due to limitation of currently available power semiconductor devices MLIs are gaining attention for these application and unique alternatives for the conventional inverters because it can operate at lower switching frequency [67]. In these topologies current and power sharing between power semiconductor devices can be done easily. For lower power applications (less 10kW) where high efficiency is a major concern MLIs have been competing with the conventional inverters which operates at high switching

frequency .Although low prices of power semiconductor devices and some new power devices technologies have fulfilling the current demand of high performance inverters needed in renewable energy source integration, MLIs have been used for these extended application [68].

MLIs, specially three level inverter emerges as good solution for trading off the performance and cost in high voltage high power application. The key advantages of MLIs are good harmonics spectrum, reduced power stress on switches, and making possible to use minimum size of inductor filter and better dynamic response[69]. In other hand control or modulation techniques are bit complex for MLIs, there are some critical issues with different topologies such as for diode clamped MLI, dc link voltage at neutral point need to be regulated and for cascaded inverters there's need of isolated dc sources for the each H-bridge cell and need to regulate the voltage across each bridge in some application to avoid uneven power stress or undesired harmonics spectrum[70][71].

Some other application of the MLIs have found in the literature such as static synchronous compensator (STATCOM), static var compensator (SVC), superconductivity magnetic storage system (SMES) [72]-[75]. A grid connected cascaded H-bridge MLI for the photovoltaic power source integration is presented in [76]. In this thesis main attention is kept to cascaded H-bridge multilevel inverters (CHMLI) due it's some of the advantageous qualities over other topologies. CHMLI establishes a capable alternative, among the available MLI topologies, benefiting with modular structure that can be prolonged to make possible transformer less connection to the grid [77]-[78]. Additionally, this topology features cost effective lower rating of the power semiconductors in comparison to the standard two-level configurations [79]. Last but not the least, This CHMLI features numerous degrees of freedom that make possible its operation even under faulty conditions and hence reliability of the system can be managed to be good enough. In spite of all these characteristics, the cascaded multilevel topology has also some disadvantages, such as isolated dc source requirement and complex control of dc bus voltage regulation in some application such as PV string panels are not grounded and additional actions need to be taken in order to dodge currents due to stray capacitances between the earth and the panel [80].

In last few years apart from well-known topologies of multilevel inverter such as CHMLI, diode clamped multilevel inverter and capacitor clamped inverters, some new inverter topologies have been introduced in the industry, especially for the application in medium voltage high power

application. And some example for those topologies are: five level active NPC [81], modular multilevel converters (MMC) [82] transistor clamped converters (TCC) [83], stacked multi-cell [84] etc. Some of the leading key factors for these new topologies are: higher power density, lower torque ripples and fault tolerant capabilities.

Figure1.9 Modular multilevel converter [82]

All these new topologies requires special attention to the modulation control. Some established control techniques which are accepted for the conventional and multilevel inverters are not applicable to these new topologies. Such as open-winding fed drives also possess several different space vector distribution and need to be extended from straight forward classical method[85]-[88].

Modulation techniques are the method to provide gate signals for the power semiconductor devices to obtain switched output waveform in a way to maintain adjustability with an arbitrary magnitude, frequency and phase. Which is important for the proper control of inverter or power controlled by inverter. In starting days of power electronics converters generally pulse width modulation (PWM)[88] has been adopted as mainstream modulation technique for the conventional two level inverters. It has simplicity and effectiveness in a process of generating pulsed or switched voltage output with frequency is matching with the reference signal.

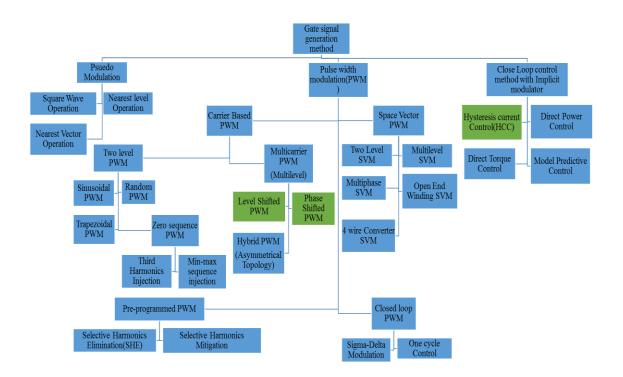

Figure1.10 General Classification of gate signal generation methods for voltage source inverters [89].

However it's evident that every new converter topology requires a novel modulation techniques for the corresponding switching pattern to generate the switched output voltage. Generalized classification for the gate pulse generation techniques for voltage source inverters are shown in Fig1.10[89].The challenges with different topology of converters, are to be dealt with the modulation technique such as dc voltage balancing, circulating current, extra available switching redundancies and some other issues.

As shown in Fig.1.11 and 1.12, voltage source inverters can operate in open loop or close loop control loop that generates reference voltage or current for determining the switching signals [90]. In the open loop operation of the inverter modulator has to generate the switching signal based on the reference that does not depend on any measurements. Normally in this case on certain operation point, the reference is externally determined by operator or outer loop control. These type of controller are used in applications such as pumps, fans, and fixed frequency drives where dynamics of the system is not a major issue. These open loop controllers for inverter gained huge success and become primarily useful due to its extreme simplicity at the verge of using a fixed operation point usually leads to performance degradation.

Figure 1.12 Close loop control and modulation

To overcome the drawbacks of the open loop controllers, close controller has been introduced. In this case main objective of the controller is to track one or combination of references define by user or customer. It can be any variables in various electric application such as voltage current, torque, active power, reactive power, flux etc. The controller generates the reference for the modulator and it is usually the voltage reference, and modulator has to generate reference for next sampling time [91]. This modulation scheme become very common solution where customize phase, frequency and amplitude is required for robust performance of adjustable speed drive or any other applications. There are two control techniques are mainstream controller which are used proportional-integral (PI) controller in synchronous reference frame and proportional-resonant (PR) controller in stationary frames in applications of active harmonic filters [92]. In last one decade closed loop controllers have been emerged as a better option because these controllers offer close loop implicit modulator with in controller as shown in Fig 1.13. These controllers are termed as direct controller and conceptually simple for the digital implementation in the system to generate switching signal for the inverter as in direct consequence of the controller avoiding extra burden of modulator. During last decade these type of controller which itself works as a modulator has been successfully introduced to the industry level. For example hysteresis current control or direct torque current control comprises implicit modulation with in direct controller [93].

Figure 1.13 Close loop control with implicit modulation

In modulation process of a power converters, due to instant switching pattern it might be chance of overlapping and short circuit in in the power converter so before final feeding of gate signal to the devices it is essential to insert a dead time to avoid the shoot through of inverter arms. The higher dynamic switching of inverter switches waiting time or dead time is necessary to sustain safe operation. The dead time cannot be exceeded by certain limit due to increment of nonnegligible phenomena and low order harmonics in voltage/current if high power devices are used in high power systems. There are some methods have been proposed to insert dead time without its adverse effects [94].

The commonly used open loop and close loop modulation techniques for conventional inverters are extended for multilevel inverters. Some established modulation techniques still needs to be enhanced for different multilevel inverter topology [95][96].Usually controllers are designed to track a desired reference in any close loop control system to achieve some specified targets such

#### A Digitally Controlled Grid Connected Modular Cascaded H-bridge Multilevel Inverter

as reactive power compensation, active power control, dc-link voltage control, phase current balancing etc. by switching converter. The modulator generates a gate pulse in result inverter pertains desired switched average waveform over the sampling period. By use of duty cycle concept modulator has to generate switching sequence to properly switch the semiconductor devices. In the output voltage, harmonics spectrum evidences the undesired harmonics present due to high frequency switching. This is advocated by industrial and research societies that these undesired harmonics are required to be eliminated so this leads to the requirement of costly and bulky passive filters [97]. By adopting lower switching frequency and optimized design of harmonics filter for the system, the situation can be handled possibly.

Since controller and modulator plays an essential role and these are key element of power electronics system. Advanced control for open loop, close loop and close loop with implicit modulator is needed to implement either based on software or hardware prototype to check its reliability in term of processing time and cost. The prime challenges for a power electronics engineer are listed as following,

- The management of the input/output power, bidirectional flow, maintaining the better efficiency to satisfy the operational expectancy.

- Control operation and prototyping that offers high precision, flexibility, communication capability and reliability.

- Reduced complexity with corresponding reduced cost.

To achieve these expected functioning of a control unit in power electronics system in spite of disturbances and non-ideal conditions, a controller is required to interact between converter and load or grid on the basis of sampled measurement of input and output.

In early days evolution of control system consisting analog system was considered which possesses some disadvantages such as

- Passive component, large number of subsidiary parts in results lower reliability and increasing hardware complexity with required wider space.

- Limitation of the applicability of simple PI controllers and lower level of computation.

- The effect of aging, temperature dependency and maintenance.

• And the most important one it is not possible to reconfigure the controller without changing the hardware circuit.

However the analog controller are still having better bandwidth and rapidity in terms of presently growing alternatives for control systems. In the field of power electronics and drives, high performance of controller is essential due to involvement of complexity, high precision and short interval of control time. One of the optimal solution to overcome these issues, real time digital controller has been introduced in 1970s and become more attractive to power electronics. Digital controller allow user to implement complex control strategies with inherent algorithm and mathematical calculations. [98].

Growing interest for the real time digital controller to implement and made it applicable in power electronics and drives is due to, the tremendous advantages of digital controller over analogous one. Some leading advantages are flexibility, reduced design time and possibility to implement complex control in real time. Real time digitally controlled system can implemented using several technological methods, such as microcontrollers, digital signal processors (DSPs), field programmable gate array (FPGA), real time prototyping, programmable logic controllers(PLCs) etc. Among all these microcontrollers, DSPs and FPGA are used commonly due to their leading advantages for power electronics converters.

However the current DSPs offers higher integration rate and timing performance but it cannot achieve bandwidth of analog controller [99]. The primary reason is integration of these digital controller to analog environment with the use of interfaces such as analog to digitals (ADCs), and zero order hold circuits. Since these interface circuits introduces delay which is burden for the processors and reduces the bandwidth of the close loop control system by effecting computing time mainly [100].

It's evident that a digital controller can execute quasi-instantaneous control algorithm which is great advantage of cumulating both analog and digital controllers. In this process it leads to a third category of controllers the digital quasi-analog controller. FPGA emerges as a good candidate for these expectations in present time scenario [101]. FPGA accelerates the processing time of a control due to its ability to implement a specific architecture that is suitable for the salient features of the algorithm to implement [102].FPGA can be defined as matrix of configurable logic blocks

(combinational and/or logical) interconnected with each other with reprogrammable capabilities [103].FPGA based control design considerations can be summarized as shown in Fig.1.14.The possible ways of control design with FPGA can be easy for the control engineer who is not expert in the area of digital circuit design. Therefore it totally depend on the application engineer and there capabilities that which methodology to follow and more details can be found in [104].

Figure1.14.Design methodologies for FPGA based real time implementation [104].

Some key steps to be taken by a control engineer to real time implementation of FPGA based control.

- 1. Validation of the synthesis of the controller in time continuous mode via MATLAB Simulink.

- Designing of the system on digital platform with fixed point simulation and it crucial because it includes digital realization of filter, sampling time fixation, some modifications have be done to make it less complex in[104].

- 3. Optimizing the data flow graph of the control algorithm to get the balance in terms of time and area performances.

- 4. To generate or obtain a HDL code for the architecture.

- 5. To implementation on FPGA which is an automatic process to map, place and route design and analyze its dynamic and static performance.

- 6. At final step the controller validation can be done on experimental setup or using hardware in loop co-simulation.

With the growing development of advanced controller design and its testing in real time becomes essential for prior validation. Hardware co-simulation is method used by researcher and industrial processes in data acquisition, control strategies in large number of processes concerned with cost, safety and full scale prototyping. The real time FPGA based controller design requires knowledge and development of HDL. XSG provides a midlevel platform for implementing controller through co-simulation process. Its importance for the power electronics technology is to rapid testing of controller without expertness in HDL programming. The prototyping of controller can easily done using FPGA hardware co-simulation [105].

For the evaluation of the performance of controller an application based analysis is important. In this thesis three type of controller such as open loop control, close loop control and close loop control with implicit modulation are adopted in general. For open loop controller (LSPWM and PSPWM) a linear inductive load is connected to CHMLI, for close loop high performance control system(LCL filter interfaced system) is developed for CHMLI based DSTATCOM and close loop control with implicit modulation ( digital multiband HCC) is performed on single phases grid connected CHMLI system. All of these applications are significant in present day's electricity usage and efficiency should be improved to tackle the energy issues. Before concluding the introduction part of the thesis it is essential to focus some light on literature review of available DSTATCOM.

As power converters adequately offers highly capable and efficient electrical energy flow in a close loop system for any application such as DSTATCOM, motor drive, industrial processes and electric vehicles. Adding more application of power electronics converters in a low, medium and high power system including renewable energy integration, distribution generation etc.

Now a days consumption of power concerns with the reactive load such as fan, pumps, etc. These loads requires and force the grid to draw lagging power factor currents and in results grid had to supply reactive power to the different loads. Condition of unbalanced load may worsens the

situation. In other hand in very poor power factor load condition, excessive reactive power need to be supplied from the grid which causes feeder losses and reduced active power supply capability of the grid. The grid including transformers and generator affected by these reactive and unbalanced load. Distribution static compensator (DSTATCOM) emerges as good option as a compensator at distribution level.

DSTATCOM comprises the voltage source inverters and the close loop controller to aid the required operation. The important attempts to controller design with the topology manipulation has been done for the DSTATCOMs. Two level inverters based DSTATCOM has become very common in the last twenty years .Moreover DSTATCOM performance depends on the control technique applied, there are many control techniques available for these system control such as instantaneous reactive power theory (IRPT), synchronous reference theory (SRFT), current control techniques combined with dc bus voltage regulation, power balance theory [106], computation based on per phase, neural network scheme [107]. Apart from the control method in DSTATCOM application the topology variation has been attempted for inverter. By designing and control of a multilevel inverter based DSTATCOM the improved and transformer less system has been utilized .CHMLI has been used for this application in mainstream technology. Many attempts by the improved control, improved filter size, dynamic controller with implicit modulator has been proposed for the multilevel inverter based DSTATCOM [108].

Since it's difficult to connect conventional inverter based DSTATCOMs to the utility grid or medium voltage system, due to high power stress on single power devices. CHMLI which consists H-bridge modules have gained more attention among all available topology of multilevel inverter. It possess some disadvantage such as balancing dc bus voltage at each H-bridge cell to get a proper operation of DSTATCOM. The basic objective of the multilevel inverter based DSTATCOM is to force the grid to supply only active component of power and remaining current responsible for the reactive power or unbalancing of load are supplied by the DSTATCOM system [109]. Some of the leading benefits of using multilevel inverter are lower operating switching frequency, smaller filter size, lower electromagnetic interference, low power stress on devices, lower acoustic noise.

The ultimate use of multilevel inverters in a DSTATCOM system is an elimination of transformer from the system. Also it is noticed that these topologies offers better dynamic behavior in continuous control, in results reduces the power quality problems .Application of CHMLI for the distribution system has been proposed and discussed in [110]. In all the prosed work it is advocated that assumption of source stiffness, it means the voltage at the common coupling point (PCC) must be regulated and kept fluctuation less despite of variation in the load or current injected by the shunt device. However in practical applications it not possible because these shunt devices inject some circulating currents to the grid and affects the supply in certain points. If the stiffness of the grid is kept by increasing impedance of the supply side in result degraded performance of the DSTATCOM is possible [111-112].

The complete literature review consisting energy and electricity, future scenario, role of power electronics in 21<sup>st</sup> century, modern power electronics converters, and essential role of modulation, control system, digital real time control and FPGA technology is carried out in this dissertation. Some key issues which has been noticed and focused for the presented work in this thesis.

- In an electrical system, it is required to control the voltage, current, power, frequency, from generation end to user end.

- To achieve environment friendly electrical energy conversion system for the better future for power systems and sustainability. Power electronics technology emerges as adequate option and spread to every corner of growing technology. For operation and control of electrical power conversion, there is need of special attention and rigorous attempts to be made.