# A Grid Synchronization PLL Method Based on Mixed Second- and Third-Order Generalized Integrator for DC-Offset Elimination and Frequency Adaptability

Zhang, Chunjiang; Zhao, Xiaojun; Wang, Xiaohuan; Chai, Xiuhui; Zhang, Zhe; Guo, Xiaoqiang

Published in: IEEE Journal of Emerging and Selected Topics in Power Electronics

Link to article, DOI: 10.1109/JESTPE.2018.2810499

Publication date: 2018

**Document Version** Peer reviewed version

Link back to DTU Orbit

*Citation (APA):* Zhang, C., Zhao, X., Wang, X., Chai, X., Zhang, Z., & Guo, X. (2018). A Grid Synchronization PLL Method Based on Mixed Second- and Third-Order Generalized Integrator for DC-Offset Elimination and Frequency Adaptability. IEEE Journal of Emerging and Selected Topics in Power Electronics, 6(3). https://doi.org/10.1109/JESTPE.2018.2810499

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- · You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# A Grid Synchronization PLL Method Based on Mixed Second- and Third-Order Generalized Integrator for DC-Offset Elimination and Frequency Adaptability

Chunjiang Zhang, Xiaojun Zhao, Xiaohuan Wang, Xiuhui Chai, Zhe Zhang, Senior Member, IEEE, and Xiaoqiang Guo, Senior Member, IEEE

Abstract—The second order generalized integrator (SOGI) has been widely used to implement grid synchronization for grid-connected inverters, and from grid voltages it is able to extract the fundamental components with an output of two orthogonal sinusoidal signals. However, if there is a dc offset existing in the grid voltages, the general SOGI's performance suffers from its generated dc effect in the lagging sine signal at the output. Therefore, in this paper, a mixed second- and third-order generalized integrator (MSTOGI) is proposed to eliminate this effect caused by the dc offset of grid voltages. A detailed theoretical analysis on the proposed MSTOGI is presented to reveal the mechanism of eliminating the dc offset. After that, the MSTOGI is applied to a phase-locked loop (PLL) and thereby establish an MSTOGI-PLL which is more adaptable to various grid conditions and power quality. Moreover, a frequency-adaptive control scheme is added to the proposed MSTOGI-PLL to eliminate the phase difference between the PLL output and the grid in grid-connected applications where the grid frequency may vary. Finally, the experimental results from a laboratory prototype are given to demonstrate and verify the effectiveness of the proposed MSTOGI-PLL in terms of steady-state performance, dynamic response and frequency adaptability.

*Index Terms*—Third-order generalized integrator (TOGI), phase-locked loop (PLL), synchronization, non-ideal grid.

#### I. INTRODUCTION

GRID synchronization plays a vital role in grid-connected inverters, and is usually implemented by phase-locked loops (PLLs) [1]-[2]. An accurate PLL result cannot only

Chunjiang Zhang, Xiaojun Zhao, Xiaohuan Wang, Xiuhui Chai and Xiaoqiang Guo are with the Department of Electrical Engineering, Yanshan University, Qinhuangdao 066004, China (e-mail: zhangcj@ysu.edu.cn; zhaoxiaojun@ysu.edu.cn; wxh@ysu.edu.cn; xhchai@ysu.edu.cn; gxq@ysu.edu.cn).

Zhe Zhang is with the Department of Electrical Engineering, Technical University of Denmark, Kgs. Lyngby, 2800, Denmark (e-mail: zz@elektro.dtu.dk).

reduce total harmonic distortion (THD) but also improve waveform quality of grid currents, and thereby ensure the grid currents are in phase with the grid voltages which enhances stability of grid-connected systems. However, the PLL performance suffers from major power quality issues in the grid-connected system such as voltage waveform distortions, harmonics, voltage frequency variations etc. Therefore, the implementation of accurate phase locking under non-ideal grid voltage conditions has become a research hotspot in recent years [3]-[5].

1

A synchronous reference frame phase-locked loop (SRF-PLL) [6]-[7] has been widely used in grid-connected systems due to its simple structure, fast dynamic response and easy software implementation. However, if grid voltages are in the presence of imbalance or harmonics, the result of SRF-PLL will produce errors, and thereby cannot accurately track the fundamental positive sequence component of the grid voltages, and even affects the stability of grid-connected systems. In order to overcome this drawback of SRF-PLL under non-ideal grid voltage conditions, a double decoupled synchronous reference frame phase-locked loop (DDSRF-PLL) has been proposed and studied in [8]-[9]. The DDSRF-PLL can extract positive and negative sequence components from grid voltages, and thereby obtain better results of PLL by using a decoupling network to eliminate oscillation. However, the low-pass filters (LPFs) employed in the DDSRF-PLL introduces a time delay which slows dynamic response [10]; moreover, the control algorithm is rather complex to implement. Compared with the DDSRF-PLL, the second-order generalized integrator phase-locked loop (SOGI-PLL) [11] not only has a simpler structure but also can effectively achieve accurate phase locking even under non-ideal grid voltage conditions and at the same time eliminate the delay introduced by LPFs in the DDSRF-PLL. Due to its superior performance, the SOGI-PLL has been investigated very extensively nowadays. In a single-phase or three-phase system, a single SOGI-PLL (SSOGI-PLL) [12] or dual SOGI-PLL (DSOGI-PLL) [13] is usually used to synchronize with the grid, respectively. When grid voltages contain a dc offset, however, the SSOGI and DSOGI will generate an error in the extraction of the fundamental components of the grid voltages leading to an

Manuscript received June 26, 2017; revised October 13, 2017 and December 17, 2017; accepted February 9, 2018. Date of publication xxx, 2018; date of current version xxx, 2018. This work was supported by the National Natural Science Foundation of China under Grant 51477148 and Grant 51607154. (*Corresponding author: Xiaojun Zhao.*)

#### inaccurate PLL result.

To eliminate the influence of the dc offset on PLL, a LPF is added to the subtraction branch of the input signal and the orthogonal output signal of the SOGI in [14]. However, how the cut-off frequency of the LPF is selected is not clearly described. An additional branch to eliminate dc offset is added for the SRF-PLL in [15], specifically, the dc offset of the d-axis from the grid voltages is estimated by using the integral operation, and then the dc offset is eliminated by using the proportional-integral (PI) controller. However, if this method is applied to the SOGI-PLL, it can only ensure that the phase-locked result is not affected by the dc offset, and the orthogonal output signal of the SOGI still exists the dc offset. The linear Kalman filter technique is employed to eliminate dc offset in [16]. However, the algorithm of the technique is rather complex resulting in a large amount of digital discretization, which is not conducive to digital control implementation. Two SOGI blocks are connected in series to form a cascaded generalized integrator PLL (CGI-PLL) in [17], which also is able to eliminate the dc offset in the input signal. Compared with [16], the CGI-PLL is easier to implement. Since the both transfer functions of CGI are fourth-order functions, the discretized digital control implementation is slightly more complex than the phase-locked method proposed in this paper. A notch filter branch is added to eliminate dc offset in the general SOGI in [18], but at the same time, a new parameter is introduced into the SOGI, which needs to consider the effects of the original parameter and the new parameter on the phase-locked system increasing the selection difficulty of the SOGI parameters.

In this paper, a mixed second- and third-order generalized integrator phase-locked loop (MSTOGI-PLL) is proposed by adding an extra branch to eliminate the dc offset of input signals in the general SOGI, thus, to establish a third-order generalized integrator (TOGI). The proposed MSTOGI-PLL, unlike [18], does not introduce a new parameter, and can accurately lock the phase under the non-ideal grid voltage conditions, such as imbalance, including dc offsets and harmonics. Moreover, if there is no a frequency-adaptive function for the MSTOGI-PLL, grid frequency variations within a certain range e.g., 50±0.5Hz can lead to a phase difference, resulting in that the PLL output will lead or lag to the grid voltages. To overcome this drawback, the PLL output is fed back to the MSTOGI, so that the overall MSTOGI-PLL can realize frequency adaptability against the phase difference between the PLL output and the grid [19], [20], and thereby accurately track the grid voltages under frequency variations.

This paper is organized as follows. After this introduction and in Section II, the general SOGI is presented and from a detailed theoretical analysis, its drawback is discussed, so that the MSTOGI is proposed accordingly, followed by the mechanism of the proposed MSTOGI to eliminate dc offsets in Section III. Then, the principle of applying the MSTOGI to the PLL with an additional frequency-adaptive capability is given. Finally, comprehensive experimental results of steady-state, dynamic and frequency-adaptive operations with the grid voltages having imbalance, dc offsets, harmonics, a step-up, a phase jump and frequency variations are presented in Section V, to verify the validity and feasibility of the proposed MSTOGI-PLL method in the grid-connected systems.

2

# II. ANALYSIS OF THE PROPOSED MSTOGI

#### A. Analysis of the general SOGI

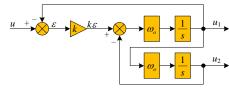

A general SOGI structure is shown in Fig. 1, where  $u, \varepsilon$  and k represent the input signal, the error signal and the damping factor respectively. If the resonant frequency of the SOGI  $\omega_o$  equals the frequency of the input signal  $\omega_s$ , two orthogonal output signals i.e.  $u_1$  and  $u_2$  are with the same amplitude but a 90 ° phase shift; furthermore,  $u_1$  and u have the same amplitude and phase.

Fig. 1. Block diagram of a general SOGI structure.

The closed-loop transfer functions of the general SOGI are described in (1) and (2).

$$G_{1}(s) = \frac{u_{1}(s)}{u(s)} = \frac{k\omega_{0}s}{s^{2} + k\omega_{0}s + \omega_{0}^{2}}.$$

(1)

$$G_2(s) = \frac{u_2(s)}{u(s)} = \frac{k\omega_0^2}{s^2 + k\omega_0 s + \omega_0^2}.$$

(2)

The quality factor of the transfer function  $G_1(s)$  obtained by (1) can be expressed as

$$Q = \frac{1}{k}.$$

(3)

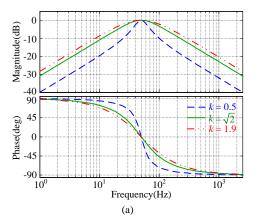

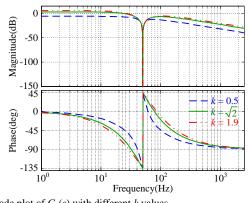

The Bode plots of  $G_1(s)$  and  $G_2(s)$  with different values of k are illustrated in Figs. 2(a) and 2(b), respectively, where the resonant frequency  $\omega_0=2\pi\cdot 50$  rad/s. It can be clearly seen from Fig. 2(a) that  $G_1(s)$  is a second-order band-pass filter (BPF) with a unity gain and zero phase shift at the resonant frequency  $\omega_0$ . The damping factor k determines the bandwidth of  $G_1(s)$ , and the lower value of k, the better filtering effect of  $G_1(s)$ , but the stronger dependence on the resonant frequency  $\omega_0$ . Moreover, the output signal  $u_1$  will produce a large amplitude attenuation and a phase difference when the resonant frequency  $\omega_0$  is not equal to the input frequency  $\omega_s$ .

Fig. 2. Bode plots of  $G_1(s)$  and  $G_2(s)$  with different values of k. (a) Bode plot of  $G_1(s)$ . (b) Bode plot of  $G_2(s)$ .

From Fig. 2(b),  $G_2(s)$  is a second-order LPF with a unity gain and 90° phase shift at the resonant frequency  $\omega_0$ . *k* determines the static gain of  $G_2(s)$ , which means that the lower value of *k*, the better filtering effect of  $G_2(s)$ , but the longer dynamic response time. Therefore, a trade-off should be considered when choose the value *k*, and the choice of *k* will be discussed in Section III.

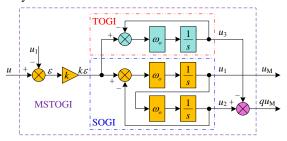

# B. The proposed MSTOGI

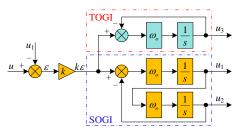

Due to  $G_1(s)$ 's band-pass filtering feature, a dc offset, if any, of input signal is eliminated by  $G_1(s)$ , which means that the signal  $u_1$  does not contain any dc offset. From the SOGI structure perspective,  $u_1$  removes the dc offset through a negative feedback branch to the input signal u as shown in Fig. 1. Since  $G_2(s)$  is a LPF, once u contains any dc offset,  $u_2$  will produce a dc offset with the gain of k, that results in an error in the amplitude detection of u and also affects the follow-up PLL on grid voltages. Therefore, a third-order generalized integrator (TOGI) is proposed by adding a branch to eliminate the dc offset as shown in the dashed box in Fig. 3. From Fig. 3, the so-called MSTOGI which combines both the general SOGI and the new TOGI can be established.

Fig. 3. Block diagram of the MSTOGI structure.

In the MSTOGI structure, the transfer functions of  $u_1(s)$  to u(s) and  $u_2(s)$  to u(s) are  $G_1(s)$  and  $G_2(s)$ , respectively, as given in (1) and (2). The transfer function  $G_3(s)$  of  $u_3(s)$  to u(s) can be expressed in (4).

$$G_3(s) = \frac{u_3(s)}{u(s)} = \frac{k\omega_0(s^2 + \omega_0^2)}{(s + \omega_0)(s^2 + k\omega_0 s + \omega_0^2)}.$$

(4)

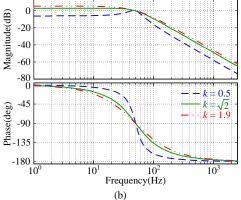

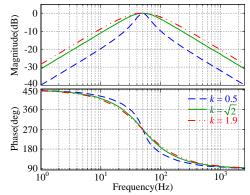

From (4) it can be seen that  $G_3(s)$  is a third-order transfer function; then, the bode plot of  $G_3(s)$  is shown in Fig. 4 with different values of k.

Fig. 4. Bode plot of  $G_3(s)$  with different k values.

From Fig. 4,  $G_3(s)$  is a notch filter with a band stop centered at  $\omega_0$ , and the gain of  $G_3(s)$  at  $\omega_0$  is equal to zero. Although intuitively  $G_3(s)$  can only provide a very limited attenuation on dc offset, but it is able to make  $u_3$  not contain any component or effect from  $\omega_0$  of the input signal even if the input signal contains  $\omega_0$  component. It is because that the magnitude (dB) of  $G_3(s)$  at  $\omega_0$  is negative infinity, and thus the component is blocked. This feature of  $G_3(s)$  can be used to eliminate the dc offset in the input signal. Therefore, it is necessary to comprehensively analyze the mechanism of eliminating dc offset by the proposed MSTOGI.

# III. DC OFFSET ELIMINATION MECHANISM

In the steady state, let's assume the input signal u(t) is a sine wave with a dc offset.

$$u(t) = U_{\rm dc} + U_{\rm m}\sin(\omega_{\rm s}t + \varphi_{\rm s}) \tag{5}$$

where  $U_{dc}$  is the dc offset,  $U_m$  is the sine wave amplitude,  $\omega_s$  is the grid frequency, and  $\varphi_s$  is the phase jump angle, when  $\varphi_s = 0$  or  $\varphi_s \neq 0$ , this represents that the input signal u(t) is in the absence or presence of a phase jump.

In s-domain, u(s) can be expressed by (6).

$$u(s) = \frac{U_{\rm dc}}{s} + \frac{U_{\rm m}(\omega_{\rm s}\cos\varphi_{\rm s} + s\sin\varphi_{\rm s})}{s^2 + \omega_{\rm s}^2}.$$

(6)

Therefore,  $u_1(s)$  can be derived from (1) and (6).

$$u_{1}(s) = \frac{k\omega_{0}s}{s^{2} + k\omega_{0}s + \omega_{0}^{2}} \left(\frac{U_{dc}}{s} + \frac{\omega_{s}\cos\varphi_{s} + s\sin\varphi_{s}}{s^{2} + \omega_{s}^{2}}U_{m}\right).$$

(7)

Applying the inverse Laplace transform to (7), the steady-state output of  $u_1(t)$  can be obtained as [21]:

$$u_{1\infty}(t) = mU_{\rm m}\sin(\omega_{\rm s}t + \varphi_{\rm s} + \varphi) \tag{8}$$

$$m = \frac{k\omega_{\rm o}\omega_{\rm s}}{\sqrt{k^2\omega_{\rm o}^2\omega_{\rm s}^2 + (\omega_{\rm o}^2 - \omega_{\rm s}^2)^2}}$$

(9)

$$p = \arctan \frac{\omega_o^2 - \omega_s^2}{k\omega_o \omega_c} \tag{10}$$

It can be seen from (8) clearly that  $u_{1\infty}(t)$  is a sine wave whose amplitude is determined by the attenuation factor *m* and the phase shift is determined by the angle  $\varphi$ . The analysis of *m* and  $\varphi$  will be given afterwards.

Similarly, the steady-state output of  $u_2(t)$  can be obtained,

$$u_{2\infty}(t) = kU_{\rm dc} - m\frac{\omega_{\rm o}}{\omega_{\rm s}}U_{\rm m}\cos(\omega_{\rm s}t + \varphi_{\rm s} + \varphi).$$

(11)

4

JESTPE-2017-06-0436

From (11),  $u_{2\infty}(t)$  always contains the dc offset of  $kU_{dc}$ ; thus, it implies that the general SOGI is not able to eliminate the dc offset completely. Meanwhile,  $u_{2\infty}(t)$  contains a cosine component whose amplitude is determined by m,  $\omega_0$  and  $\omega_s$ , and its phase is 90 °lagging behind  $u_1$ .

The steady-state output of  $u_3(t)$  can be obtained in (12).

$$u_{3\infty}(t) = kU_{\rm dc} - k\omega_{\rm o}U_{\rm m}\sqrt{\frac{1-m^2}{\omega_{\rm o}^2 + \omega_{\rm s}^2}}\cos(\omega_{\rm s}t + \varphi_{\rm s} + \varphi - \varphi_{\rm c}).$$

(12)

where  $\varphi_{\rm c} = \arctan(\omega_{\rm s}/\omega_{\rm o})$ .

From (12), it can be seen that  $u_{3\infty}(t)$  contains the same dc offset  $kU_{dc}$  as  $u_{2\infty}(t)$ . The further analysis of the coefficients m and  $\varphi$  in (9) and (10) based on  $\omega_0$  and  $\omega_s$  is carried out and the amplitude and phase of the output signals  $u_1(t)$ ,  $u_2(t)$  and  $u_3(t)$  with respect to the input signal u(t) are expressed by (13) and (14), respectively.

$$\begin{cases} m = 1 \quad \omega_{0} = \omega_{s} \\ m < 1 \quad \omega_{0} \neq \omega_{s} \end{cases}$$

(13)

$$\varphi = \begin{cases} + \arctan \frac{\omega_{0}^{2} - \omega_{s}^{2}}{k\omega_{0}\omega_{s}} \quad \omega_{s} < \omega_{0} \\ 0 \quad \omega_{0} = \omega_{s} \\ - \arctan \frac{\omega_{s}^{2} - \omega_{0}^{2}}{k\omega_{0}\omega_{s}} \quad \omega_{s} > \omega_{0} \end{cases}$$

(14)

If  $\omega_0 \neq \omega_s$ , the parameter *m* can provide attenuation on the amplitude of  $u_1(t)$ ,  $u_2(t)$  and  $u_3(t)$ ; on the other hand, the parameter  $\varphi$  can introduce a phase shift.

However, if  $\omega_0 = \omega_s$ , (8), (11) and (12) can be rewritten as

$$u_{1\infty}(t)_{|\omega_0=\omega_{\rm s}} = U_{\rm m}\sin(\omega_{\rm s}t + \varphi_{\rm s}).$$

(15)

$$u_{2\infty}(t)_{|\omega_0=\omega_{\rm s}} = kU_{\rm dc} - U_{\rm m}\cos(\omega_{\rm s}t + \varphi_{\rm s}).$$

(16)

$$u_{3\infty}(t)_{|\omega_0=\omega_{\rm s}} = kU_{\rm dc} \,. \tag{17}$$

Obviously,  $u_{1\infty}(t)$  is an ac signal without any dc offset, and its ac part is the same as that of the input signal u(t).  $u_{2\infty}(t)$  contains the dc offset of  $kU_{dc}$ , and its ac part is a cosine wave with the same amplitude and frequency as the input signal.  $u_{3\infty}(t)$  only contains the dc offset  $kU_{dc}$ . Furthermore, if the phase jump angle  $\varphi_s \neq 0$ ,  $u_{1\infty}(t)$  and  $u_{2\infty}(t)$  will also have a same phase jump angle  $\varphi_s$  as the input signal, and closely follow the phase change of the input signal u(t).

Therefore, as shown in Fig. 5 these three output signals of the MSTOGI can be reconstructed to have dc offset elimination capability.

Fig. 5. Block diagram of reconfigured MSTOGI structure.

The orthogonal output signals of the reconfigured MSTOGI can be expressed as

$$\begin{cases} u_{\rm M} = u_1 \\ q u_{\rm M} = u_2 - u_3 \end{cases}$$

(18)

The transfer function from u(s) to  $u_M(s)$  is  $G_1(s)$ , as shown in (1).  $G_4(s)$ , the transfer function from u(s) to  $qu_M(s)$ , can be expressed as

$$G_4(s) = \frac{qu_{\rm M}(s)}{u(s)} = \frac{k\omega_{\rm o}s(\omega_{\rm o} - s)}{(s + \omega_{\rm o})(s^2 + k\omega_{\rm o}s + \omega_{\rm o}^2)}.$$

(19)

The Bode plots of  $G_4(s)$  with different values of k are plotted in Fig. 6. Apparently,  $G_4(s)$  is a BPF with a unity gain and 90° phase shift at the resonant frequency  $\omega_0$ , which has the similar amplitude-frequency characteristic as  $G_1(s)$ . Moreover,  $G_4(s)$ has a large attenuation in both low and high frequency bands, which can effectively eliminate the dc offset and high-frequency harmonics existing in the input signal.

Fig. 6. Bode plot of  $G_4(s)$  with different k values.

Fig. 7. Pole-zero maps of the MSTOGI with different k values. (a) Pole-zero map of  $G_1(s)$ . (b) Pole-zero map of  $G_4(s)$ .

Fig 7 shows the pole-zero maps of the MSTOGI with different k values. It can be observed that all the poles are in the left half-plane, indicating that the system stability can be guaranteed. It can be clearly seen from Fig. 7(a) that the complex-conjugated poles of  $G_1(s)$  move far away the

imaginary axis and close to the real axis by increasing k from 0.2 to 2, indicating that the greater the damping factor k is, the better stability and faster dynamic response but the worse filtering performance will be. However, after k = 2, all the poles of  $G_1(s)$  are on the real axis, and these poles are split into two parts. One part moves far away from the imaginary axis. And the other moves toward the imaginary axis, becoming the dominant poles, indicating that the stability and dynamic response will be deteriorated.

The analysis of Fig. 7(b) is similar as that of Fig. 7(a). The difference is that there is a pair of symmetric pole and zero (+314 and -314) in Fig. 7(b), which will not affect the amplitude-frequency characteristics of  $G_4(s)$ , but affects the phase-frequency characteristics of  $G_4(s)$ . Therefore,  $G_4(s)$  has the similar amplitude-frequency and different phase-frequency characteristics as  $G_1(s)$ . Based on the analysis of the MSTOGI's bode plots and pole-zero maps, considering the tradeoff between the transient response speed and filtering performance, the parameter of k is chosen as  $\sqrt{2}$ , which is also consistent with the requirement of the filter quality factor of  $G_1(s)$  i.e. Q = 0.707.

In summary, the proposed MSTOGI can adapt to a variety of non-ideal grid conditions to accurately extract the fundamental component of grid voltages through the above theoretical analysis.

#### IV. FREQUENCY-ADAPTIVE PLL

From (13), (14), Fig. 2(a) and Fig. 6,  $u_{\rm M}$  which equals to  $u_1$ has different outputs depending on  $\omega_s$  and  $\omega_o$ : (a) when  $\omega_s$  is less than  $\omega_0$ ,  $u_M$  leads the input u by a phase angle with an attenuated amplitude; (b) when  $\omega_{\rm s}$  is equal to  $\omega_{\rm o}$ ,  $u_{\rm M}$  is synchronized with u and has the same amplitude; (c) when  $\omega_s$  is greater than  $\omega_0$ ,  $u_M$  lags u by a phase angle with an attenuated amplitude. Similarly, when  $\omega_s$  is not equal to  $\omega_o$ ,  $qu_M$  also has the same phenomenon of phase leading or lagging and amplitude attenuation. It can conclude that only when  $\omega_0 = \omega_s$ , the output signals of the MSTOGI,  $u_M$  and  $qu_M$  have no amplitude attenuation or a positive or negative phase difference. In other words, the MSTOGI must always operate at the input signal frequency  $\omega_s$  in order to guarantee phase locking accurately. Therefore, in this paper, the output of PLL is fed back to the MSTOGI to make the system frequency-adaptive against frequency variations.

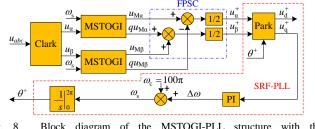

The block diagram of the proposed MSTOGI-PLL structure is shown in Fig. 8. Firstly, the three-phase voltages  $u_{abc}$  are translated from the abc-frame to the  $\alpha\beta$ -frame by applying the Clark transform to obtain  $u_{\alpha}$  and  $u_{\beta}$ . Then, input  $u_{\alpha}$  and  $u_{\beta}$  into the dual MSTOGIs, and thereby the orthogonal signals  $u_{\alpha}$ , and  $u_{\beta}$ ,  $u_{M\beta}$  and  $qu_{M\beta}$  can be generated. These signals as inputs are added to the fundamental positive sequence calculator (FPSC) to extract the fundamental positive sequence components  $u_{\alpha}^{+}$ and  $u_{\beta}^{+}$ . Finally,  $u_{\alpha}^{+}$  and  $u_{\beta}^{+}$  are translated to the dq-frame by using the Park transform and an embedded SRF-PLL as shown in the dashed box is employed to synchronize with the grid.

In Fig. 8,  $\omega_s$  is fed back to the MSTOGI to make the system frequency-adaptive. The purpose of adding  $\omega_c$  is to speed up the

adjustment speed of the PLL; otherwise to achieve the same adjustment speed, must increase the bandwidth of the PLL's PI controller that will cause larger overshoot of  $\omega_0$  and even lead to the system instability.

Fig. 8. Block diagram of the MSTOGI-PLL structure with the frequency-adaptive feature.

Since the orthogonal signals  $u_{\alpha}$ ,  $u_{\beta}$ ,  $u_{M\beta}$  and  $qu_{M\beta}$  generated by the MSTOGIs are the fundamental components of the grid voltages, to extract the fundamental positive sequence components, the following expression on the  $\alpha\beta$ -frame can be obtained by using the symmetrical components method in [22].

$$\begin{bmatrix} u_{\alpha}^{+} \\ u_{\beta}^{+} \end{bmatrix} = \frac{1}{2} \begin{bmatrix} 1 & -q \\ q & 1 \end{bmatrix} \begin{bmatrix} u_{\alpha} \\ u_{\beta} \end{bmatrix}.$$

(20)

where  $q = e^{-j\pi/2}$  is a phase-shift operator to obtain the quadrature-phase signal from the original in-phase signals.

The signals  $u_{\alpha}$ ,  $u_{\beta}$ ,  $u_{M\beta}$  and  $qu_{M\beta}$  just satisfy the requirement for (20), where the MSTOGI plays a role in filtering out the dc component and harmonics of the four signals. The transformation of (20) is implemented in the FPSC (see the dash-dotted box in Fig. 7) of the MSTOGI-PLL.

According to (20), the FPSC in the MSTOGI-PLL can be expressed as

$$u_{\alpha}^{+} = \left(u_{\mathrm{M}\alpha} - qu_{\mathrm{M}\beta}\right) / 2 \,. \tag{21}$$

$$u_{\beta}^{+} = \left(q u_{M\alpha} + u_{M\beta}\right) / 2.$$

(22)

The value of k affects not only the filtering effect and dynamic performance of the MSTOGI, but also the bandwidth of the embedded SRF-PLL, which directly relates to the choice of the PI controller parameters in the Fig. 8. To satisfy the stability and also optimize the settling time in the amplitude, frequency and phase step changes for the MSTOGI-PLL, the PI controller parameters of the embedded SRF-PLL need to be matched with the k, and the relationship between them can be found in [23]. Note that the lowest harmonic of the input signal disturbances is the third-order harmonic ( $3\omega_s$ ) in [23]. For the three-phase three-wire system, in this paper, the considered lowest harmonic is the fifth-order harmonic ( $5\omega_s$ ).

Besides, the dynamic performance of the MSTOGI-PLL is proportional to its bandwidth. To achieve a faster transient response, the bandwidth should be chosen as high as possible. However, the higher the bandwidth is, the weaker the ability of the MSTOGI-PLL to suppress low-harmonics will be. Considering the influence of the fifth-order harmonic in the three-phase input voltages on the MSTOGI-PLL, thus, the bandwidth of the embedded SRF-PLL is set to  $2\pi50$  rad/s (as shown in [24]), and the PI controller parameters are:  $k_p$ = 314.16 and  $k_i$  = 9763. This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/JESTPE.2018.2810499, IEEE Journal of Emerging and Selected Topics in Power Electronics

JESTPE-2017-06-0436

# V. EXPERIMENT AND ANALYSIS

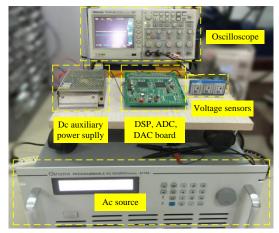

A laboratory prototype is built to implement the comparative experiments among the general SOGI-, MSTOGI- and SRF-PLL, as shown in Fig. 9. It mainly includes five parts: (a) digital signal processor (DSP) TMS320F28335, analog-to-digital converter (ADC) and digital-to-analog converter (DAC); (b) 15V dc auxiliary power supply; (c) ac source (Chroma-61704); (d) oscilloscope; (f) three voltage sensors which convert the high voltages of the ac source to low voltages.

Fig. 9. The laboratory prototype of the general SOGI-, MSTOGI- and SRF-PLL.

# A. Steady-State Performance

The experiment is carried out in three cases:

Case I: unbalanced grid voltages: phase A has the rated voltage, the voltage of phase B increases by 15%, and the voltage of phase C decreases by 15%;

Case II: grid voltages with a dc offset: phase A is shifted up by 0.7V;

Case III: grid voltages with low-order harmonics: the harmonic contents of each phase are shown in Table I.

| TABLE I<br>Low-Order Harmonic Ratio of Grid Voltages |         |      |      |     |  |

|------------------------------------------------------|---------|------|------|-----|--|

| Lov                                                  | THD (%) |      |      |     |  |

| 5th                                                  | 7th     | 11th | 13th |     |  |

| 5%                                                   | 5%      | 5%   | 5%   | 10% |  |

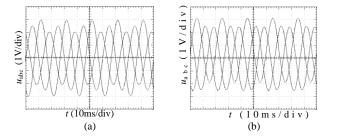

The experimental results of Case I, II and III are shown in Fig. 10. The three-phase grid voltages are measured by voltage sensors and then send the sensed analog signals to the DSP through its internal ADC. After the DSP operation, the output signals of the SOGI-PLL and the MSTOGI-PLL,  $u_{\alpha}^{+}$ ,  $u_{\beta}^{+}$  and  $\theta^{+}$  are obtained by an external DAC.

Fig. 10. Input signals of three-phase grid voltages. (a) Unbalanced grid voltages. (b) Grid voltages with a dc offset. (c) Grid voltages with low-order harmonics.

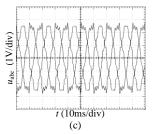

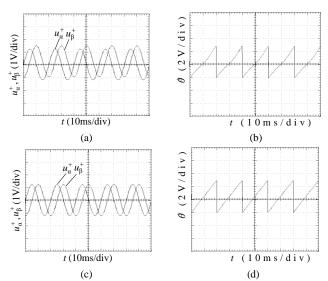

Fig. 11 shows the comparative experimental results of the SOGI- and the MSTOGI-PLL in Case I. The experimental results of the SOGI-PLL are consistent with the MSTOGI-PLL:  $u_{\alpha}^{+}$  and  $u_{\beta}^{+}$  are a pure sine and cosine waves, respectively. Meanwhile, the phase angle  $\theta^{+}$  is not affected by the unbalanced grid voltages, and is able to accurately track the fundamental positive sequence component of the grid voltages.

Fig. 11. Experimental results of SOGI- and MSTOGI-PLL in case I. (a) General SOGI output results. (b) General SOGI-PLL output result. (c) MSTOGI output results. (d) MSTOGI-PLL output result.

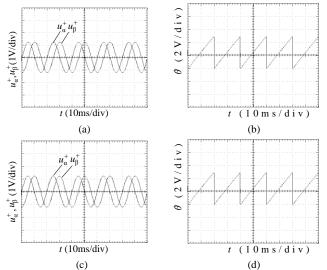

Fig. 12. Experimental results of SOGI- and MSTOGI-PLL in Case II. (a) General SOGI output results. (b) General SOGI-PLL output result. (c) MSTOGI output results. (d) MSTOGI-PLL output result.

2168-6777 (c) 2018 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

# 7

JESTPE-2017-06-0436

Fig. 12 shows the comparative experiments of SOGI- and MSTOGI-PLL in Case II.  $u_{\beta}^{+}$  of the SOGI is shifted up due to the added dc offset, which means that  $u_{\alpha}^{+}$  and  $u_{\beta}^{+}$  are unbalanced, which results in the q-axis component  $u_{q}^{+}$  after the Park transform must be oscillating, and the SOGI-PLL output  $\theta^{+}$  exists an error. In contrast, the MSTOGI is able to completely eliminate the dc offset; thus, its phase locking performance is not affected.

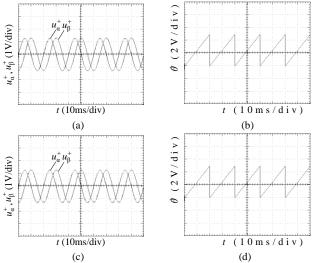

Fig. 13 shows the comparative experiments of the SOGI- and MSTOGI-PLL in Case III. It can be clearly seen from Fig. 2 and Fig. 6 that the SOGI/MSTOGI has the different attenuation for harmonic sequences, that is, the attenuation of the SOGI/MSTOGI to low-order harmonics is less than that of high-order harmonics, resulting in a little distortion in  $u_{\alpha}^{+}$  and  $u_{\beta}^{+}$ . Meanwhile, since the bandwidth of the embedded SRF-PLL is selected to be 50Hz in this paper, this will further guarantee the accuracy of the PLL output  $\theta^{+}$ . Therefore, both the general SOGI-PLL and the proposed MSTOGI-PLL have the ability to suppress the low-order harmonics.

Fig. 13. Experimental results of SOGI- and MSTOGI-PLL in case III. (a) General SOGI output results. (b) General SOGI-PLL output result. (c) MSTOGI output results. (d) MSTOGI-PLL output result.

Based on the steady-state experimental results above, it can be verified that the MSTOGI has the greater adaptability to the non-ideal grid voltages, and its output results are not affected by grid voltage imbalance, dc offset or low-order harmonics.

#### B. Dynamic Performance

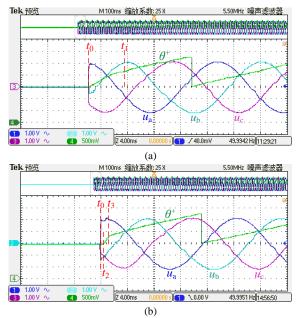

This section compares the phase locking accuracy and speed of the SRF- and MSTOGI-PLL from a grid voltage step-up and discusses the impact in terms of a phase jump of -30 °in the grid voltages on the MSTOGI-PLL.

The SRF-PLL structure can be obtained by the following changes in Fig. 7: the two MSTOGIs and FPSC are removed, and then  $u_{\alpha}$  and  $u_{\beta}$  are directly input into the Park transform.

Fig. 14 shows the comparative experiments of dynamic performance for SRF- and MSTOGI-PLL with a grid voltage step-up. In Fig. 14(a), the grid voltages step up from zero at  $t_0$ , the SRF-PLL output i.e. the phase angle  $\theta^+$  reacts instantaneously at  $t_0$ . However, during the interval of  $t_0 \sim t_1$

(5.6ms), the phase angle  $\theta^+$  produces an error, resulting in  $\theta^+$  increases nonlinearly with an upward bulge. Also,  $\theta^+$  lags to phase A, leading to inaccurate grid voltage tracking.

In Fig. 14(b), after the grid voltages step up, at the beginning the MSTOGI-PLL has no phase output during the interval of  $t_0 \sim t_2$  (0.5ms), and it starts to output the angle  $\theta^+$  at  $t_2$  with an error (the rising slope is steeper). However, the grid voltages can be accurately tracked after 1.3ms ( $t_2 \sim t_3$ ) which is significantly less than 5.6ms of the SRF-PLL.

Fig. 14. Experimental results of dynamic performance with the grid voltage step-up. (a) Dynamic performance of the SRF-PLL. (b) Dynamic performance of the MSTOGI-PLL. (Time: 4 ms/div)

From the above dynamic experimental results, it can be verified that the establishment time of the MSTOGI-PLL output is slightly slower than that of SRF-PLL, but the dynamic response time of the phase locking in terms of accuracy for the MSTOGI-PLL is obviously better than that of SRF-PLL.

Fig. 15. Experimental results of dynamic performance with a phase jump of  $-30^{\circ}$  in the grid voltages. (Time: 10 ms/div)

Fig. 15 shows the dynamic performance of the MSTOGI-PLL with a phase jump of -30 ° in the grid voltages.  $u_a$  occurs with a phase jump of -30 ° at  $t_4$ , resulting in that  $u_a^+$ ,  $u_\beta^+$  and  $\theta^+$  cannot accurately track  $u_a$ . During the interval of the transition time ( $t_4 \sim t_5$ ), the amplitude of  $u_a^+$  and  $u_\beta^+$  decreases, and the phase of  $u_a^+$  leads the input  $u_a$  by a phase angle. With the gradual adjustment of MSTOGI-PLL to  $u_a^+$ ,  $u_\beta^+$  and  $\theta^+$ , they can completely track  $u_a$  at  $t_5$  (the system reaches a steady state),

which is consistent with the theoretical analysis in Section III. The transition time of the MSTOGI-PLL is 10ms with a phase jump of  $-30^{\circ}$ . It can be proved by the Fig. 15 that the phase jump has the impact on the MSTOGI-PLL in transient state and no impact on the MSTOGI-PLL in steady state.

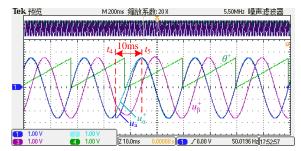

#### C. Frequency-Adaptive Performance

Based on the theoretical analysis in Section IV, when the resonant frequency of the MSTOGI is fixed at 50Hz and if the grid frequency is less than 50Hz, the angle  $\theta^+$  will lead the grid voltages, and if the grid frequency is greater than 50Hz, the angle  $\theta^+$  lags the grid voltages.

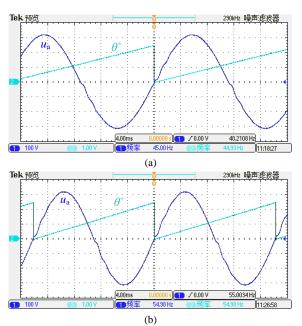

Fig. 16 shows the experiments of the grid frequency at 45Hz and 55Hz without the added frequency-adaptive feature for the MSTOGI-PLL.

Fig. 16. Experimental results of the MSTOGI-PLL without the frequency-adaptive feature. (a) Grid frequency 45Hz. (b) Grid frequency 55Hz. (Time: 4 ms/div)

According to (14), Fig. 16(a) and (b), the theoretical and actual values of phase relation between the output  $\theta^+$  of MSTOGI-PLL and the phase A of grid voltages  $u_a$  can be obtained in Table II, where the symbols "+" and "-" indicate that  $\theta^+$  leads or lags to  $u_a$ , respectively. Table II shows that the actual values match the theoretical values.

| TABLE II                                                                                    |                |

|---------------------------------------------------------------------------------------------|----------------|

| Theoretical and Actual Values of Phase Relation Between $\theta^{\scriptscriptstyle +}$ and | u <sub>a</sub> |

| Frequency | Theoretical values | Actual values |

|-----------|--------------------|---------------|

| 45Hz      | +16.62°            | +16.20°       |

| 55Hz      | -15.11°            | -15.84°       |

Fig. 17 shows the experiments of the grid frequency at the frequencies of 45Hz and 55Hz with the frequency-adaptive feature given in Fig. 8. Experimental results show that the MSTOGI-PLL can accurately track the grid voltages even with large frequency variations.

Fig. 17. Experimental results of MSTOGI-PLL with frequency-adaptive. (a) Grid frequency 45Hz. (b) Grid frequency 55Hz. (Time: 4 ms/div)

In summary, from the above experimental results it can be verified that the proposed MSTOGI method not only has the superior adaptability to non-ideal grid voltage conditions but also can achieve fast dynamic response.

# VI. CONCLUSION

Due to the fact that the general SOGI cannot eliminate the effect caused by grid voltage dc offset, this paper proposed a new MSTOGI method by combining second- and third-order generalized integrator. Firstly, the transfer functions of the MSTOGI have been analyzed to reveal the mechanism of dc offset eliminating. Then, the result of the PLL is fed back to the MSTOGI in order to compensate for a leading or lagging phase difference due to the grid frequency deviation, so that the entire MSTOGI-PLL has the frequency adaptability against the phase difference between the phase-locked output and the grid. Finally, experiments have been carried output to analyze and compare the SRF-PLL and the proposed MSTOGI-PLL in terms of steady-state characteristics and dynamic responses. It is verified that the MSTOGI-PLL has superior performance to achieve phase locking precisely and fast. Moreover, the MSTOGI-PLL is simple and easy to implement, which makes it a favorable PLL method candidate in practice.

#### References

- T. Tran, T. Chun, H. Lee, H. Kim and E. Nho, "PLL-based seamless transfer control between grid-connected and islanding modes in grid-connected inverters," *IEEE Trans. Power Electron.*, vol. 29, no. 10, pp. 5218-5228, Oct. 2014.

- [2] G. De Donato, G. Scelba, G. Borocci, F. G. Capponi and G. Scarcella, "Fault-decoupled instantaneous frequency and phase angle estimation for three-phase grid-connected inverters," *IEEE Trans. Power Electron.*, vol. 31, no. 4, pp. 2880-2889, Apr. 2016.

- [3] C. Subramanian, and R. Kanagaraj, "Single-phase grid voltage attributes tracking for the control of grid power converters," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 2, no. 4, pp. 1041-1048, Dec. 2014.

- [4] X. Guo, W. Wu, and Z. Chen, "Multiple-complex coefficient-filter-based phase-locked loop and synchronization technique for three-phase grid

interfaced converters in distributed utility networks," *IEEE Trans. Ind. Electron.*, vol. 58, no. 4, pp. 1194-1204, Apr. 2011.

- [5] L. Zheng, H. Geng and G. Yang, "Fast and robust phase estimation algorithm for heavily distorted grid conditions," *IEEE Trans. Ind. Electron.*, vol. 63, no. 11, pp. 6845-6855, Nov. 2016.

- [6] L. Tong, X. Zou, S. Feng, Y. Chen, Y. Kang, Q. Huang and Y. Huang, "An SRF-PLL-based sensorless vector control using the predictive deadbeat algorithm for the direct-driven permanent magnet synchronous generator," *IEEE Trans. Power Electron.*, vol. 29, no. 6, pp. 2837-2849, Jun. 2014.

- [7] S. Golestan and J. M. Guerrero, "Conventional synchronous reference frame phase-locked loop is an adaptive complex filter," *IEEE Trans. Ind. Electron.*, vol. 62, no. 3, pp. 1679-1682, Mar. 2015.

- [8] P. Rodr guez, J. P. J. Bergas, J. I. Candela, R. P. Burgos and D. Boroyevich, "Decoupled double synchronous reference frame PLL for power converters control," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 584-592, Mar. 2007.

- [9] M. Reyes, P. Rodriguez, S. Vazquez, A. Luna, R. Teodorescu and J. M. Carrasco, "Enhanced decoupled double synchronous reference frame current controller for unbalanced grid-voltage conditions," *IEEE Trans. Power Electron.*, vol. 27, no. 9, pp. 3934-3943, Sep. 2012.

- [10] L. Hadjidemetriou, E. Kyriakides and F. Blaabjerg, "A new hybrid PLL for interconnecting renewable energy systems to the grid," *IEEE Trans. Ind. Appl.*, vol. 49, no. 6, pp. 2709-2719, Nov. 2013.

- [11] J. Matas, M. Castilla, J. Miret, L. G. Vicuña and R. Guzman, "An adaptive prefiltering method to improve the speed/accuracy tradeoff of voltage sequence detection methods under adverse grid conditions," *IEEE Trans. Ind. Electron.*, vol. 61, no. 5, pp. 2139-2151, May 2014.

- [12] F. Xiao, L. Dong, L. Li, and X. Liao, "A frequency-fixed SOGI-based PLL for single-phase grid-connected converters," *IEEE Trans. Power Electron.*, vol. 32, no. 3, pp. 1713-1719, Mar. 2017.

- [13] S. Golestan, M. Monfared and F. D. Freijedo, "Design-oriented study of advanced synchronous reference frame phase-locked loops," *IEEE Trans. Power Electron.*, vol. 28, no. 2, pp. 765-778, Feb. 2013.

- [14] M. Ciobotaru, R. Teodorescu, V. G. Agelidis, "Offset rejection for PLL based synchronization in grid-connected converters," in *Proc. Twenty-Third Annu. IEEE Appl. Power Electron. Conf. and Exposit.*, Texas, USA, Feb. 24-28, 2008, pp. 1611-1617.

- [15] S. Hwang, L. Liu, H. Li and J. Kim, "DC offset error compensation for synchronous reference frame PLL in single-phase grid-connected converters," *IEEE Trans. Power Electron.*, vol. 27, no. 8, pp. 3467-3471, Aug. 2012.

- [16] M. S. Reza, M. Ciobotaru and V. G. Agelidis, "Grid voltage offset and harmonics rejection using second order generalized integrator and Kalman filter technique," in *Proc. 7th Int. Power Electron. and Motion Control Conf.*, Harbin, China, Jun. 2-5, 2012, pp. 104-111.

- [17] A. Kulkarni and V. John, "Design of a fast response time single-phase PLL with DC offset rejection capability," in *Proc. IEEE Appl. Power Electron. Conf. and Exposit. (APEC)*, California, USA, Mar. 20-24, 2016, pp. 2200-2206.

- [18] M. K. Ghartemani, S. A. Khajehoddin, P. K. Jain, A. Bakhshai and M. Mojiri, "Addressing DC component in PLL and notch filter algorithms," *IEEE Trans. Power Electron.*, vol. 27, no. 1, pp. 78-86, Jan. 2012.

- [19] J. A. Suul, A. Luna, P. Rodríguez and T. Undeland, "Voltage-sensor-less synchronization to unbalanced grids by frequency-adaptive virtual flux estimation," *IEEE Trans. Ind. Electron.*, vol. 59, no. 7, pp. 2910-2923, Jul 2012.

- [20] P. Rodriguez, A. Luna, R. S. M. Aguilar, I. E. Otadui, R. Teodorescu and F. Blaabjerg, "A stationary reference frame grid synchronization system for three-phase grid-connected power converters under adverse grid conditions," *IEEE Trans. Power Electron.*, vol. 27, no. 1, pp. 99-112, Jan. 2012.

- [21] Giuseppe Fedele, Andrea Ferrise and Pietro Murac, "An adaptive quasi-notch filter for a biased sinusoidal signal estimation," in *Proc. 2011* 9th IEEE Int. Conf. on Control and Autom. (ICCA 2011), Santiago, Chile, Dec. 19-21, 2011, pp. 1060–1065.

- [22] P. Rodr guez, R. Teodorescu, I. Candela, A.V. Timbus, M. Liserre and F. Blaabjerg, "New positive-sequence voltage detector for grid synchronization of power converters under faulty grid conditions," in *Proc. 37th IEEE Power Electron. Spec. Conf.*, Jeju, Korea, Jun. 18-22, 2006, pp. 1–7.

- [23] S. Golestan, M. Monfared, F. D. Freijedo and J. M. Guerrero, "Dynamics assessment of advanced single-phase PLL structures," *IEEE Trans. Ind. Electron.*, vol. 60, no. 6, pp. 2167-2177, Jun. 2013.

[24] A. Kulkarni and V. John, "A novel design method for SOGI-PLL for minimum settling time and low unit vector distortion," in *Proc. 39th Annu. Conf. of the IEEE Ind. Electron. Society*, Vienna, Austria, Nov. 10-13, 2013, pp. 274–279.

**Chuangjiang Zhang** received the B.S. degree in electrical engineering from Northeast Heavy Machinery Institute, Heilongjiang, China, in 1983, the M.S degree in power electronics from Yanshan University, Hebei, China, in 1988, and the Ph.D. degree in power electronics from Harbin Institute of Technology University, Harbin, China, in 2008, respectively.

From 1995 to 2000, he was an Associate Professor with Yanshan University, where since 2000 he has been a Professor and also the Director at the Key Laboratory of Power Engineering of Hebei Province. From 2004 to 2016, he was a dean of the school of electrical engineering, Yanshan University. Since 2016 he has been a President of the Periodical Press, Yanshan University. His current research interests include grid-connected inverter, microgrid control, energy storage systems and dc/dc converter.

Xiaojun Zhao received the B.S. and M.S. degrees in electrical engineering from Yanshan University, Qinhuangdao, China, in 2009 and 2012, respectively, where he is currently working toward the Ph.D. degree in the Department of Electrical Engineering, Yanshan University.

His current research interests include control technology of grid-connected inverters and high power UPS system.

Xiaohuan Wang received the B.S., M.S., and Ph.D. degrees in electrical engineering from Yanshan University, Qinhuangdao, China, in 2002, 2005 and 2011, respectively. She is currently an associate professor with the Department of Electrical Engineering and Automation, Yanshan University.

Her current research interests include control technology of grid-connected inverters and distributed generation inverters.

Xiuhui Chai received the B.S., M.S., and Ph.D. degrees in electrical engineering from Yanshan University, Qinhuangdao, China, in 2007, 2010 and 2016, respectively, where she is currently working toward the postdoctoral degree in power electronics. She is currently a lecturer in the Department of Electrical Engineering and Automation, Yanshan

University.

Her current research interests include direct-drive wind energy conversion system and doubly-fed wind energy conversion system.

**Zhe Zhang** (M'11–SM'16) received the B.Sc. and M.Sc. degrees in power electronics from Yanshan University, Qinhuangdao, China, in 2002 and 2005, respectively, and the Ph.D. degree from the Technical University of Denmark, Kgs. Lyngby, Denmark, in 2010.

He is currently an Associate Professor with the Department of Electrical Engineering, Technical University of Denmark. From 2005 to 2007, he was an Assistant Professor with Yanshan University. From June 2010 to August 2010, he was with the University of California, Irvine, CA, USA, as a Visiting Scholar. He was a Postdoctoral Researcher and Assistant Professor at the Technical University of Denmark during 2011 and 2014. He has authored or coauthored more than 100 transactions and international conference papers. His current research interests include piezoelectric actuator and transformer-based power conversion systems, soft-switching power converters, multiple-input dc-dc converters and multilevel dc-ac inverters for renewable energy systems, hybrid electric vehicles, and uninterruptable power supplies.

**Xiaoqiang Guo** (M'10–SM'14) received the B.S. and Ph.D. degrees in electrical engineering from Yanshan University, Qinhuangdao, China, in 2003 and 2009, respectively.

He has been a Postdoctoral Fellow with the Laboratory for Electrical Drive Applications and Research (LEDAR), Ryerson University, Toronto, ON, Canada.

He is currently a professor with the Department of Electrical Engineering, Yanshan University, China. He has authored/coauthored more than eighty technical papers, in addition to eleven patents. His current research interests include high-power converters and ac drives, electric vehicle charging station, and renewable energy power conversion systems.

Dr. Guo is a Senior Member of the IEEE Power Electronics Society and IEEE Industrial Electronics Society. He is an active Referee for IEEE Transactions on Industrial Electronics and IEEE Transactions on Power Electronics.