# A Linear RF Power Amplifier with High Efficiency for Wireless Handsets

Wael Yahia Refai

Dissertation submitted to the faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

In

**Electrical Engineering**

William A. Davis, Chair Louis J. Guido Mantu K. Hudait Werner E. Kohler Majid Manteghi

> February 19, 2014 Blacksburg, VA

#### Keywords:

power amplifier, power efficiency, linearity, broadband, matching network, impedance transformation, converged power amplifier, wireless handset, class-J, GaAs HBT.

Copyright Wael Y. Refai, 2014 All rights reserved.

# A Linear RF Power Amplifier with High Efficiency for Wireless Handsets

#### Wael Yahia Refai

#### **ABSTRACT**

This research presents design techniques for a linear power amplifier with high efficiency in wireless handsets. The power amplifier operates with high efficiency at the saturated output power, maintains high linearity with enhanced efficiency at back-off power levels, and covers a broadband frequency response. The amplifier is thus able to operate in multiple modes (2G/2.5G/3G/4G). The design techniques provide contributions to current research in handset power amplifiers, especially to the converged power amplifier architecture, to reduce the number of power amplifiers within the handset while covering all standards and frequency bands around the globe.

Three main areas of interest in power amplifier design are investigated: high power efficiency; high linearity; and broadband frequency response. Multiple techniques for improving the efficiency are investigated with the focus on maintaining linear operation. The research applies a new technique to the handset industry, class-J, to improve the power efficiency while avoiding the practical issues that hinder the typical techniques (class-AB and class-F). Class-J has been implemented using GaN FET in high power applications. To our knowledge, this work provides the first implementation of class-J using GaAs HBT in a handset power amplifier.

The research investigates the linearity, and the nature and causes of nonlinearities. Multiple concepts for improving the linearity are presented, such as avoiding odd-degree harmonics, and linearizing the relationship between the output current and the input voltage of the amplifier at the fundamental frequency. The concept of bias depression in HBT transistors is introduced with a bias circuit that reduces the bias-offset effect to improve linearity at high output power.

A design methodology is presented for broadband matching networks, including the component loss. The methodology offers a quick and accurate estimation of component values, giving more degrees of freedom to meet the design specifications. It enables a trade-off among high out-of-band attenuation, number/size of components, and power loss within the network.

Although the main focus is handset power amplifiers, most of the developed techniques can be applied to a wide range of power amplifiers.

#### **ACKNOWLEDGEMENTS**

First, I would like to express my sincere appreciation to my advisor Dr. William A. Davis for his patience in guiding me through the research. His invaluable guidance and support assisted me passing through the difficult times of the research.

I would like to thank TriQuint Semiconductor Inc. for sharing the TQHBT3 design kits with Virginia Tech, sponsoring the tape-out of both the GaAs HBT die and the module laminate, and measuring the implemented design. Special gratitude to: Dr. David Halchin (director of North Carolina design center) for his decision to sponsor the tape-out of the GaAs die and the laminate, Mr. Steve Brown for his efforts in sharing the TQHBT3 design kits with Virginia Tech, Mr. Stephen Bachhuber for his valuable technical discussions and advice during the tape-out process, Mr. David Lee for his efforts in setting up the automated test bench for measuring the modules, and Ms. Donna Vasseur for her role in assembling the modules for testing.

Also, I would like to thank Keysight Technologies Inc., formerly Agilent Technologies Inc., for providing an educational license for "Advanced Design System" (ADS) software.

Finally, I'm grateful to my parents for their significant support and encouragement during my graduate studies.

## **TABLE OF CONTENTS**

| ABSTRACT                                                                  | ii  |

|---------------------------------------------------------------------------|-----|

| ACKNOWLEDGEMENTS                                                          | iii |

| TABLE OF CONTENTS                                                         | iv  |

| LIST OF FIGURES                                                           | vii |

| LIST OF TABLES                                                            | xi  |

| 1. Introduction                                                           | 1   |

| 1.1 – Research Motivation                                                 | 1   |

| 1.2 – Background                                                          | 3   |

| 1.2.1 – Power Efficiency                                                  | 3   |

| 1.2.2 – Linearity                                                         | 4   |

| 1.2.3 – Broadband Matching Networks                                       | 5   |

| 1.2.4 – Semiconductor Device Technology                                   | 6   |

| 1.2.5 – Power Amplifiers for Wireless Handsets                            | 6   |

| 1.3 – Dissertation Overview                                               | 7   |

| 2. High Efficiency Techniques for Linear Power Amplifiers                 | 9   |

| 2.1 – Introduction                                                        | 9   |

| 2.1.1 – Class-A Power Amplifier                                           | 10  |

| 2.1.2 – Load-Pull Technique                                               | 13  |

| 2.2 – Reduced Conduction Angle Operation                                  | 14  |

| 2.2.1 – Observations on the Fourier Series of a Truncated Sinusoid        | 15  |

| 2.2.2 - The Optimum Load for Class-AB, B, and C                           | 18  |

| 2.2.3 - Maximum Linear Output Power and Power Efficiency of Ideal Class-B | 19  |

| 2.2.4 - The Practical Implementation of Class-AB, B, and C Load           | 21  |

| 2.3 – High Efficiency Utilizing the Generated Harmonics                   | 22  |

| 2.3.1 – The Real Power of Periodic Signals                                | 23  |

| 2.3.2 – Class-J Operation                                                 | 26  |

| 2.3.3 – Class-F Operation                                                 | 36  |

| 2.4 – Summary                                                             | 37  |

| Appendix                                                                  | 38  |

| A2.1 – Derivation of the Collector Current Components                     | 38  |

| 3. Linearity in RF Power Amplifiers and Bias Circuits                     | 43  |

|    | 3.1 – Introduction                                   | . 43 |

|----|------------------------------------------------------|------|

|    | 3.2 – Nonlinearities in Power Amplifiers             | . 44 |

|    | 3.2.1 – The Nature of Nonlinearities                 | .44  |

|    | 3.2.2 – The Transistor Effect on Linearity           | . 47 |

|    | 3.2.3 – HBT Design Considerations                    | . 49 |

|    | 3.3 – Measurements of Linearity                      | . 52 |

|    | 3.3.1 – Two-tone Test                                | . 53 |

|    | 3.3.2 – Adjacent Channel Power Ratio (ACPR)          | . 54 |

|    | 3.3.3 – Error Vector Magnitude (EVM)                 | . 55 |

|    | 3.4 – HBT Bias Circuits                              | . 55 |

|    | 3.4.1 – Basic Bias Circuits                          | . 56 |

|    | 3.4.2 – Enhanced Bias Circuits                       | . 58 |

|    | 3.5 – HBT Bias Considerations                        | . 61 |

|    | 3.5.1 – Bias Depression                              | . 61 |

|    | 3.5.2 – Bias Circuits with a Linearization Feature   | . 63 |

|    | 3.5.3 – Ballast Resistor                             | . 64 |

|    | 3.6 – Summary                                        | . 68 |

| 4. | A Design Methodology for Broadband Matching Networks | . 69 |

|    | 4.1 – Introduction                                   | . 69 |

|    | 4.1.1 – Background                                   | . 70 |

|    | 4.2 – Single-Section Networks                        | . 72 |

|    | 4.2.1 – The L-Network                                | . 74 |

|    | 4.2.2 – The T-Network                                | . 76 |

|    | 4.3 – Broadband Networks                             | . 77 |

|    | 4.3.1 – Challenges of the Typical Design Approach    | . 79 |

|    | 4.3.2 – Design Example                               | . 79 |

|    | 4.4 – New Design Methodology                         | . 82 |

|    | 4.4.1 – Features of the Proposed Design Approach     | . 83 |

|    | 4.4.2 – The Design Process Guidelines                | . 87 |

|    | 4.4.3 – The Stagger-Tuning Considerations            | . 88 |

|    | 4.4.4 – Design Example and Comparison                | . 90 |

|    | 4.4.5 – Discussion                                   | . 96 |

|    | 4 5 – Summary                                        | 97   |

| Appendix                                                       | 99  |

|----------------------------------------------------------------|-----|

| A4.1 – Assumptions                                             | 99  |

| A4.2 – Derivation of the T-Network Design Equations            | 100 |

| A4.3 – The Design Equations of the Pi-Network                  | 104 |

| 5. The Design of a Linear Power Amplifier with High Efficiency | 107 |

| 5.1 – Introduction                                             | 107 |

| 5.2 – The Design Strategy                                      | 109 |

| 5.2.1 – High Efficiency Approach                               | 110 |

| 5.2.2 – Linearity Approach                                     | 111 |

| 5.2.3 – Class-J for High Efficiency and Linearity              | 112 |

| 5.2.4 – Advantages of Class-J in Handset Power Amplifiers      | 113 |

| 5.2.5 – The Proposed Design Process                            | 116 |

| 5.3 – A Power Amplifier Module Design                          | 117 |

| 5.3.1 – Power Stage Design                                     | 118 |

| 5.3.2 – Driver Stage Design                                    | 126 |

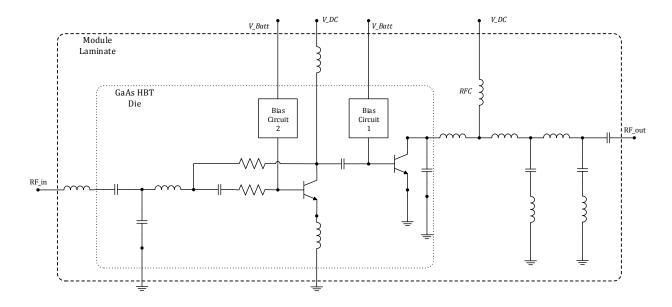

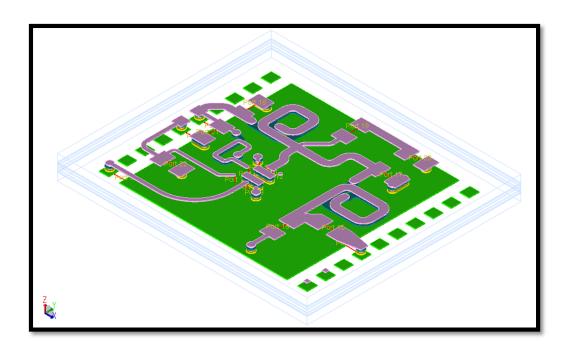

| 5.4 – The Design Schematic and Layout                          | 132 |

| 5.4.1 – Full Module Schematic                                  | 132 |

| 5.4.2 – Power Amplifier Die Layout                             | 132 |

| 5.4.3 – Module Laminate Layout                                 | 134 |

| 5.5 – Simulation and Experimental Results                      | 136 |

| 5.5.1 – Simulation Strategy                                    | 136 |

| 5.5.2 - Simulation Results                                     | 138 |

| 5.5.3 – Measurement Results                                    | 142 |

| 5.5.4 – Discussion                                             | 149 |

| 5.6 – Summary                                                  | 151 |

| 6. Conclusion                                                  | 153 |

| 6.1 – Research Summary                                         | 153 |

| 6.2 – Conclusion                                               | 155 |

| 6.3 – Significance of the Research                             | 157 |

| Ribliography                                                   | 159 |

## **LIST OF FIGURES**

| Figure 1-1 – Different power amplifier module architectures.                                        | 2            |

|-----------------------------------------------------------------------------------------------------|--------------|

| Figure 2-1 – A Basic single-stage power amplifier.                                                  | 10           |

| Figure 2-2 – A simplified I-V transfer characteristic of a transistor                               | 11           |

| Figure 2-3 – The collector current of the reduced conduction angle operation (normalized)           | ized to the  |

| maximum current (i <sub>C,Max</sub> ))                                                              | 15           |

| Figure 2-4 - The fundamental and harmonic current components vs. the conduct                        | tion angle   |

| (normalized to the maximum current (ic,Max)).                                                       | 17           |

| Figure 2-5 – A tank circuit represents an ideal load for a power amplifier that operates at         | a reduced    |

| conduction angle.                                                                                   | 18           |

| Figure 2-6 – The resultant voltage waveform of a second harmonic component that is s                | hifted by -  |

| $\pi/2$ from the fundamental component (normalized to (V <sub>DC</sub> - V <sub>CE,EOS</sub> ), the | zero value   |

| refers to V <sub>CE,EOS</sub> ).                                                                    | 22           |

| Figure 2-7 – A circuit shows the current and voltage signals at the collector/drain ter             | minal of a   |

| transistor                                                                                          | 24           |

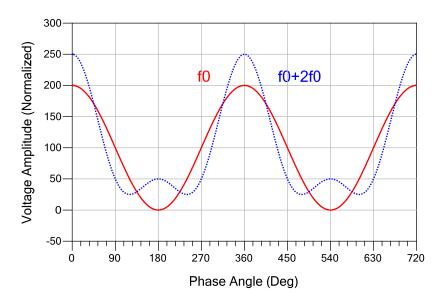

| Figure 2-8 – Class-J voltage waveform - The effect of adding a second harmonic com                  | ponent in-   |

| phase with the fundamental component (normalized to ( $V_{DC}$ - $V_{CE,EOS}$                       | ), the zero  |

| value refers to V <sub>CE,EOS</sub> ).                                                              | 27           |

| Figure 2-9 – The required load for class-J operation.                                               | 30           |

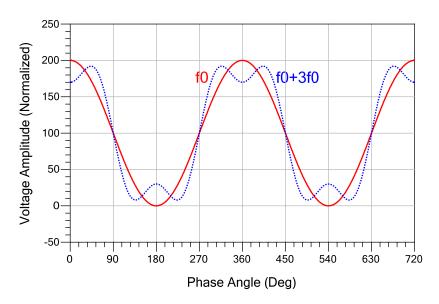

| Figure 2-10 - Class-F voltage waveform - The effect of adding a third harmon                        | ic voltage   |

| component to the fundamental component (normalized to ( $V_{DC}$ - $V_{CE,EOS}$                     | s), the zero |

| value refers to V <sub>CE,EOS</sub> ).                                                              | 36           |

| Figure 2-11 – The collector current waveform as a truncated sinusoid (normalized to                 | maximum      |

| current)                                                                                            | 38           |

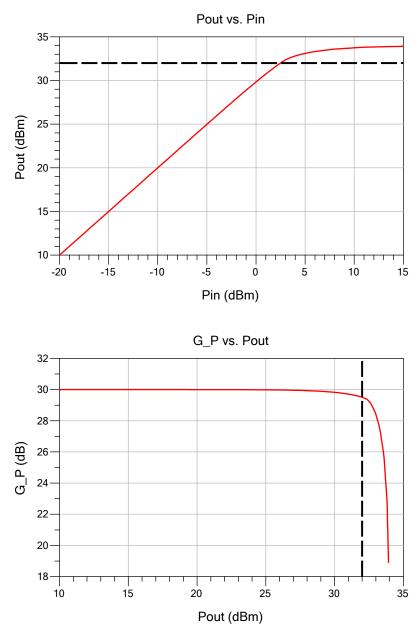

| Figure 3-1 – Output power (Pout) vs. input power (Pin), and power gain (GP) vs. output power (Pout) | ower (Pout)  |

| as input power (Pin) is swept.                                                                      | 45           |

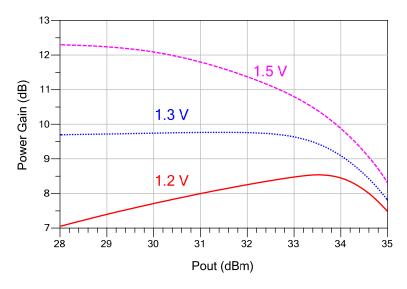

| Figure 3-2 – The effect of bias point and reduced conduction angle on linearity                     | 48           |

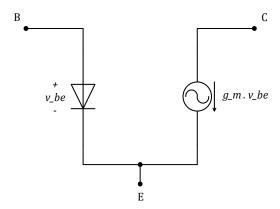

| Figure 3-3 – A simplified HBT large-signal model for operation in the active region                 | 49           |

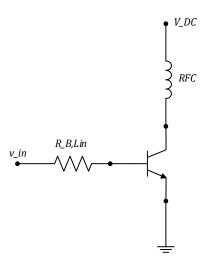

| Figure 3-4 – A Base resistor to linearize the HBT characteristics.                                  | 50           |

| Figure 3-5 – An HBT Bias circuit with a bias resistor                                               | 52           |

| Figure 3-6 – An equivalent circuit of the input section of a single-stage PA as shown in Figure | e 3-5. |

|-------------------------------------------------------------------------------------------------|--------|

|                                                                                                 | 52     |

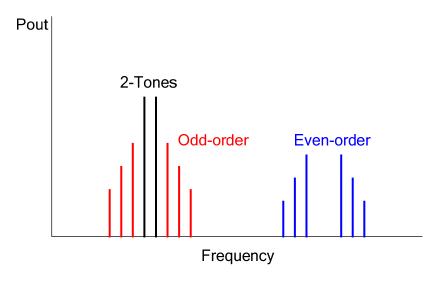

| Figure 3-7 – Spectrum of the two-tone signal, the generated IMDs and harmonics.                 | 53     |

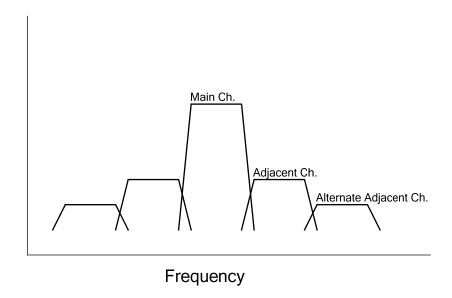

| Figure 3-8 – Adjacent channel power ratio (ACPR).                                               | 54     |

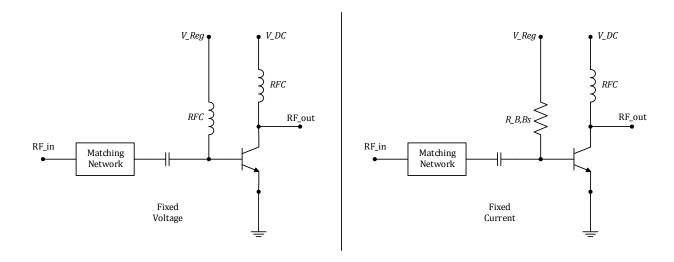

| Figure 3-9 – Bias approaches of fixed base voltage, and fixed base current.                     | 57     |

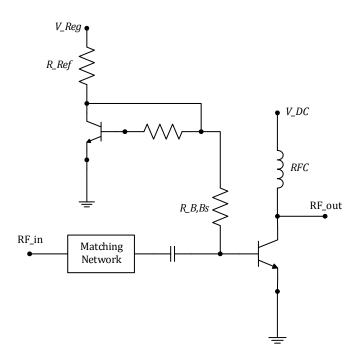

| Figure 3-10 – A bias circuit of a single diode-connected transistor.                            | 58     |

| Figure 3-11 – A bias circuit of a modified single-diode circuit with a base-current driver      | 59     |

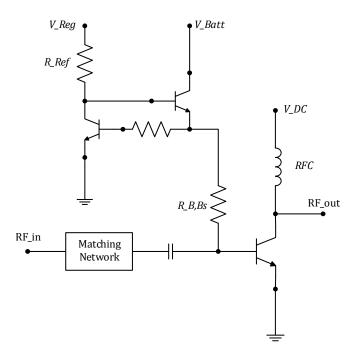

| Figure 3-12 – A bias circuit of double diode-connected transistors with an emitter follower.    | 60     |

| Figure 3-13 – An HBT with DC blocking capacitor and a bias circuit.                             | 61     |

| Figure 3-14 – An RF drive signal is coupled to a nonlinear load through a capacitor             | 62     |

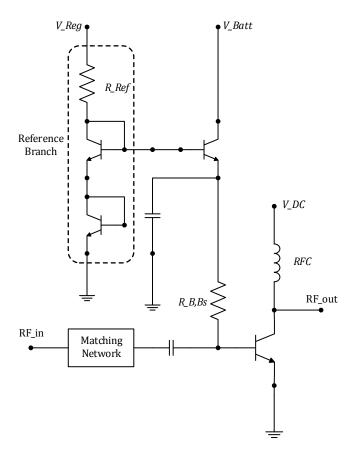

| Figure 3-15 – A Bias circuit of double-diodes with a linearization feature.                     | 64     |

| Figure 3-16 – Base ballast, and emitter ballast resistors.                                      | 65     |

| Figure 3-17 – A bypassed base ballast resistor.                                                 | 66     |

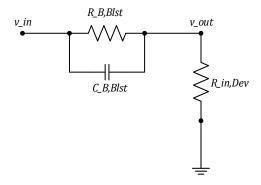

| Figure 3-18 – A bypassed base ballast resistor loaded by the input impedance of a transistor.   | 66     |

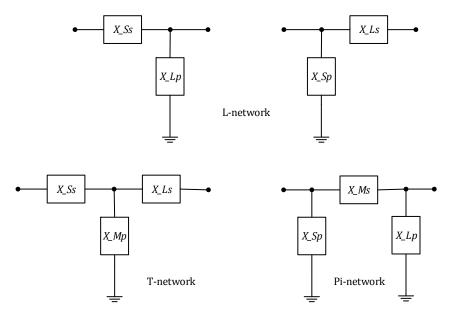

| Figure 4-1 – The L-network, T-network, and Pi-network.                                          | 72     |

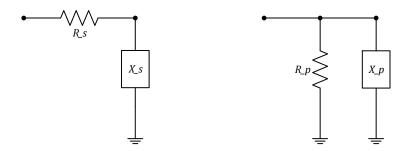

| Figure 4-2 – Series and parallel impedance configurations.                                      | 73     |

| Figure 4-3 – The down-transformation L-network.                                                 | 75     |

| Figure 4-4 – The LCL T-network.                                                                 | 76     |

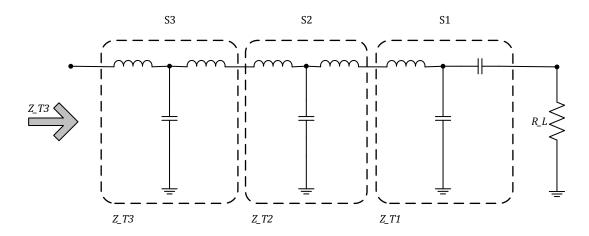

| Figure 4-5 – A typical output matching network of a power amplifier.                            | 78     |

| Figure 4-6 – The L-network with series inductor in the shunt branch                             | 80     |

| Figure 4-7 –The attenuation at out-of-band frequencies.                                         | 81     |

| Figure 4-8 – The shift in frequency response and higher insertion loss.                         | 81     |

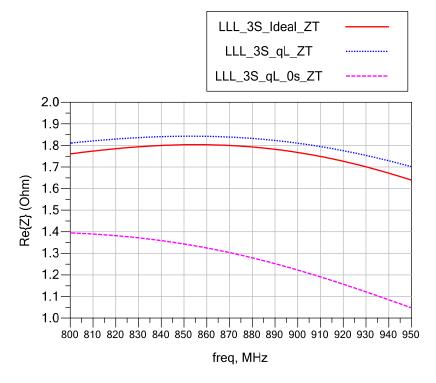

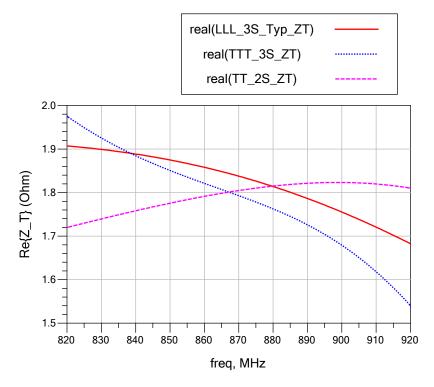

| Figure 4-9 – The deviation in the real part of the transformed impedance from the targeted      | value  |

| of 1.8 Ohm.                                                                                     | 82     |

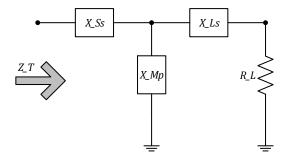

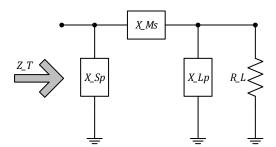

| Figure 4-10 – The proposed technique to design the matching network.                            | 83     |

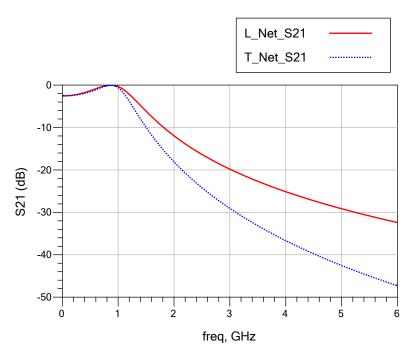

| Figure 4-11 – Comparison between the L-network and T-network.                                   | 84     |

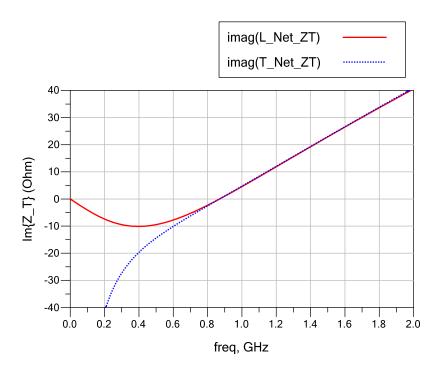

| Figure 4-12 – The imaginary part of the transformed impedance of the down-transformation        | on L-  |

| network and T-network.                                                                          | 89     |

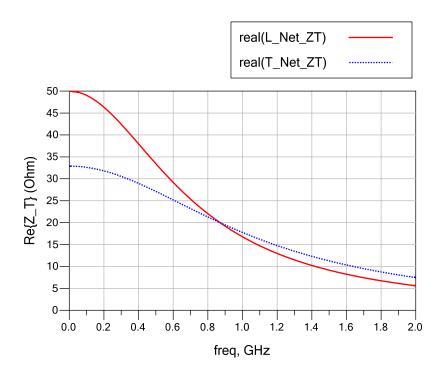

| Figure 4-13 – The real part of the transformed impedance of the down-transformation L-net       | work   |

| and T-network.                                                                                  | 90     |

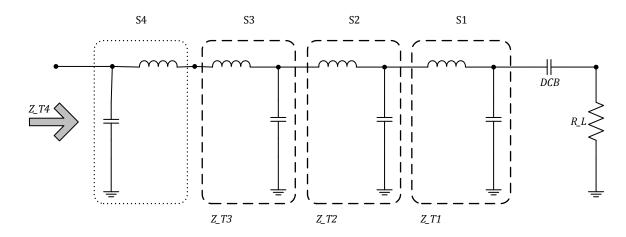

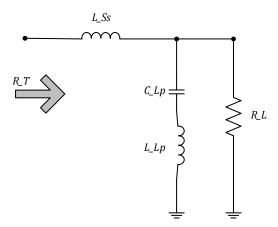

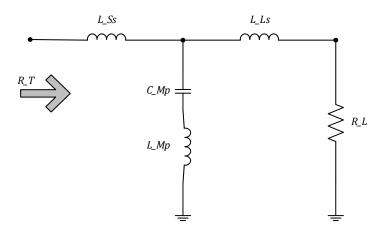

| Figure 4-14 – The L-network with series inductor in the shunt branch                            | 91     |

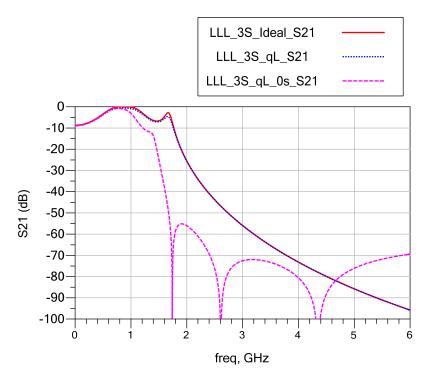

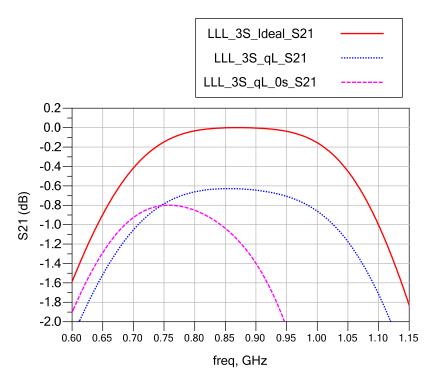

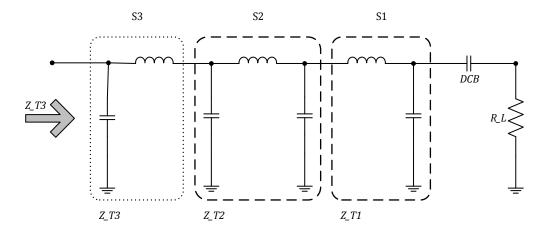

| Figure 4-15 – The LCL T-network with series inductor in the shunt branch.                   | 92       |

|---------------------------------------------------------------------------------------------|----------|

| Figure 4-16 – The real part of the transformed impedance.                                   | 94       |

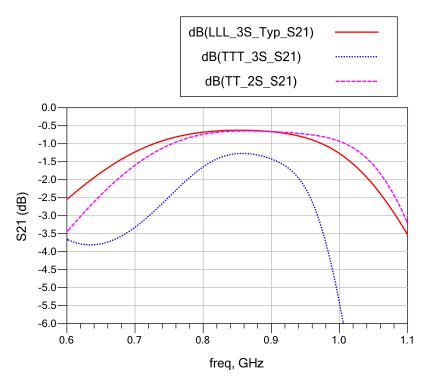

| Figure 4-17 – The frequency response.                                                       | 94       |

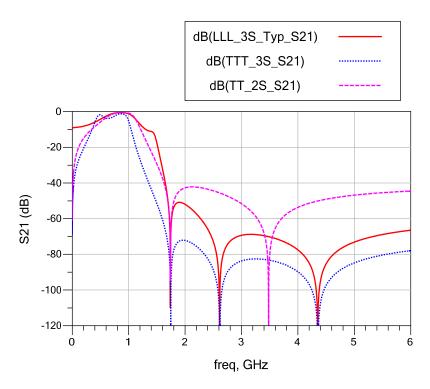

| Figure 4-18 – The harmonics attenuation.                                                    | 95       |

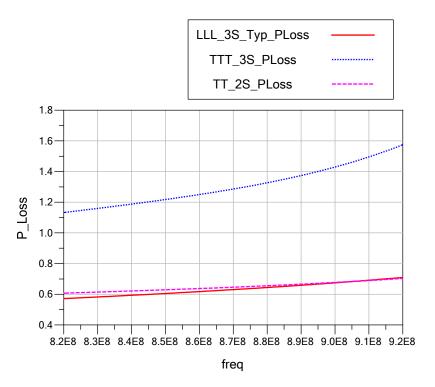

| Figure 4-19 – The power loss within the network.                                            | 96       |

| Figure 4-20 – A different configuration to analyze the matching network.                    | 97       |

| Figure 4-21 – The T-network.                                                                | 100      |

| Figure 4-22 – The Pi-Network                                                                | 104      |

| Figure 5-1 – The output and input sections of a single-stage power amplifier                | 109      |

| Figure 5-2 – A typical combined output matching network of a handset power amplifier        | 115      |

| Figure 5-3 – Class-J output matching network requirements.                                  | 116      |

| Figure 5-4 – A block diagram of the power amplifier module.                                 | 117      |

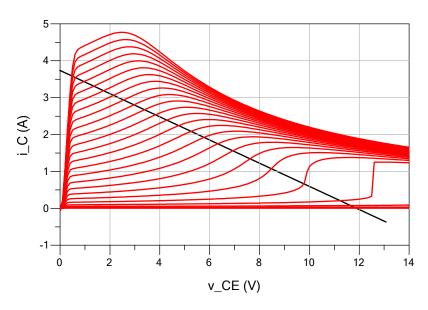

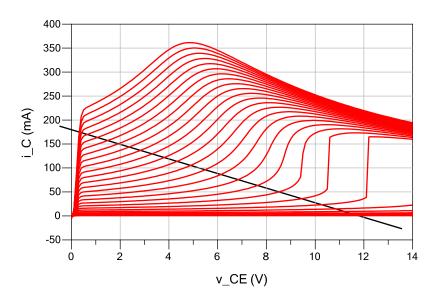

| Figure 5-5 – Power stage: I-V DC transfer characteristics (simulated), collector current    | (ic) vs. |

| collector-emitter voltage (vce) for steps of base-emitter voltage (vbe)                     | 120      |

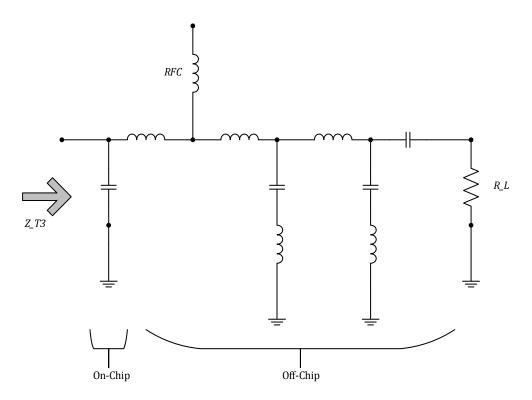

| Figure 5-6 – Output matching network.                                                       | 122      |

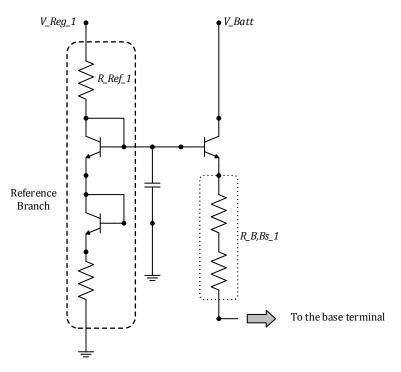

| Figure 5-7 – Power stage bias circuit.                                                      | 124      |

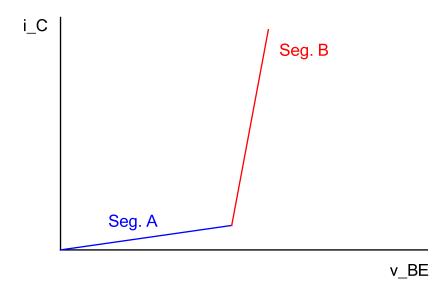

| Figure 5-8 – Approximated piecewise linear curve of collector current (ic) vs. base-emitter | voltage  |

| (VBE)                                                                                       | 124      |

| Figure 5-9 - Driver stage: I-V DC transfer characteristics (simulated), collector current   | (ic) vs. |

| collector-emitter voltage (vce) for steps of base-emitter voltage (vBE)                     | 127      |

| Figure 5-10 – The inter-stage matching network.                                             | 128      |

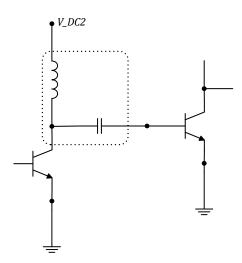

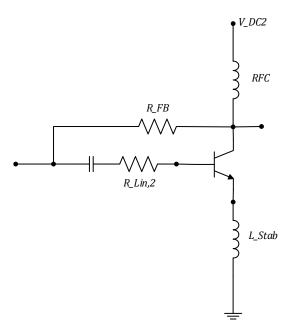

| Figure 5-11 – Driver stage bias circuit.                                                    | 129      |

| Figure 5-12 – The input matching network.                                                   | 130      |

| Figure 5-13 - A Feedback loop and an emitter inductance degeneration for stabilizing the    | e driver |

| stage.                                                                                      | 131      |

| Figure 5-14 – The full schematic of the power amplifier module.                             | 132      |

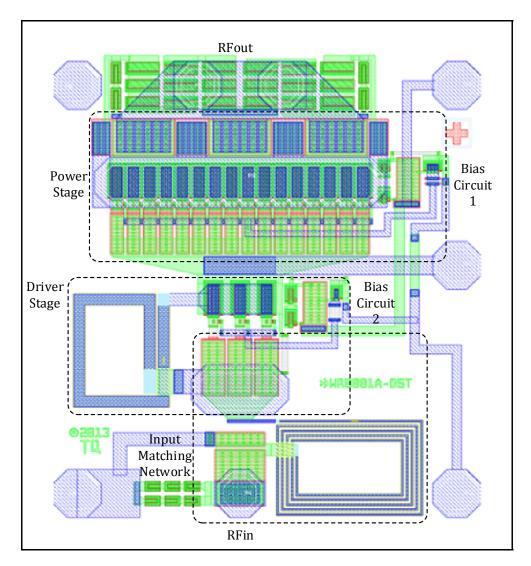

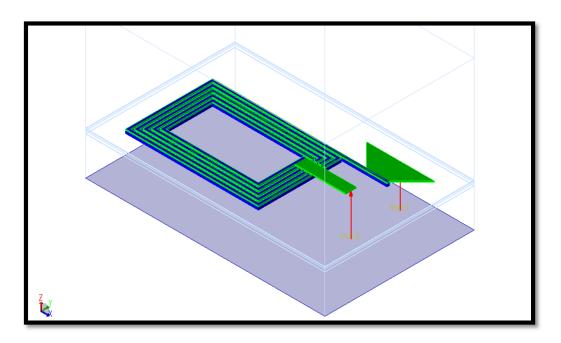

| Figure 5-15 – The layout of the GaAs HBT die.                                               | 133      |

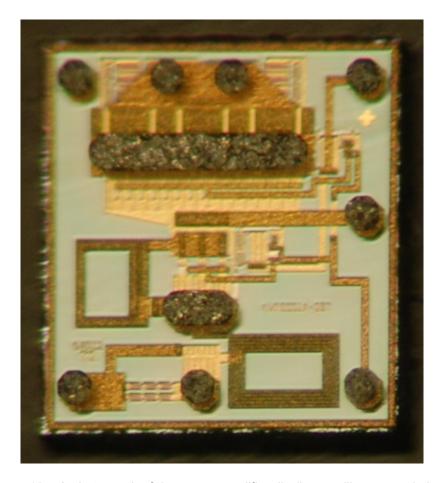

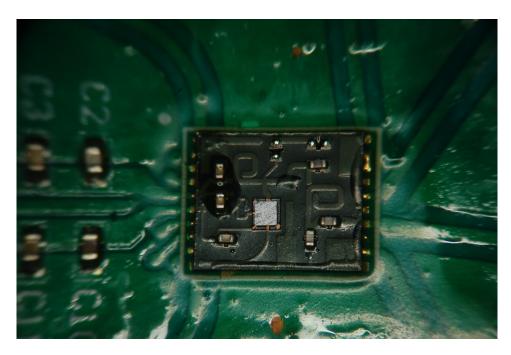

| Figure 5-16 – A photograph of the power amplifier die (bump pillars are pointing up)        | 134      |

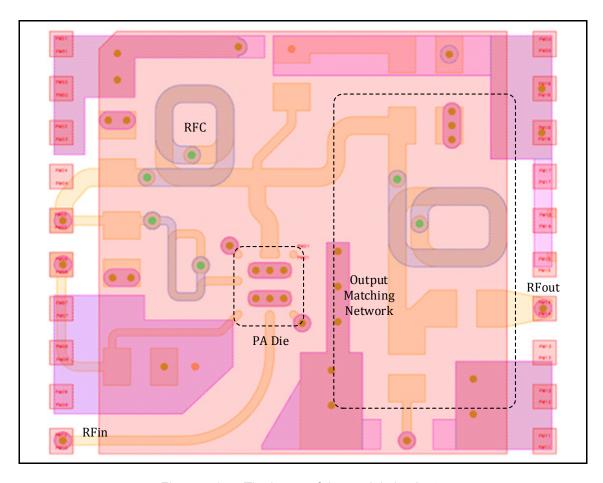

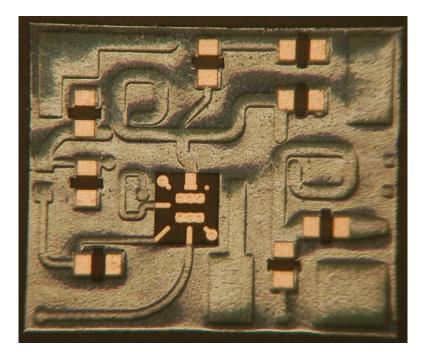

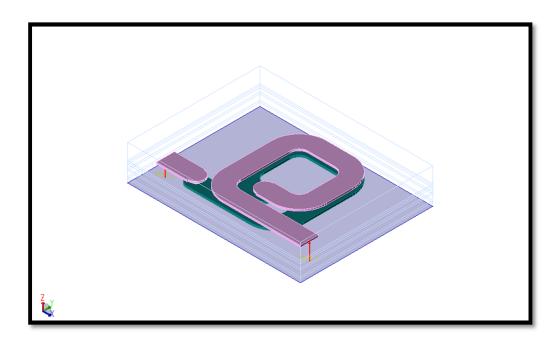

| Figure 5-17 – The layout of the module laminate                                             | 135      |

| Figure 5-18 – A photograph of the module laminate                                           | 135      |

| Figure 5-19 – EM simulation for S-parameters of an on-chip spiral inductor.                 | 136      |

| Figure 5-20 – EM simulation for S-parameters of a printed Inductor on the laminate                        | 137   |

|-----------------------------------------------------------------------------------------------------------|-------|

| Figure 5-21 – EM Simulation for S-parameters of the full module laminate.                                 | 138   |

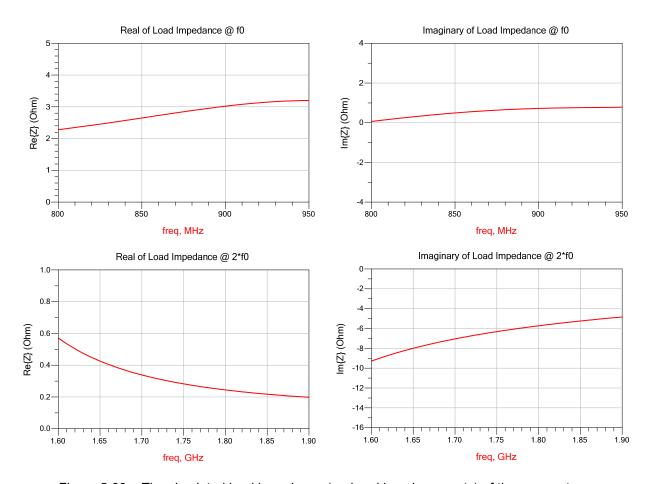

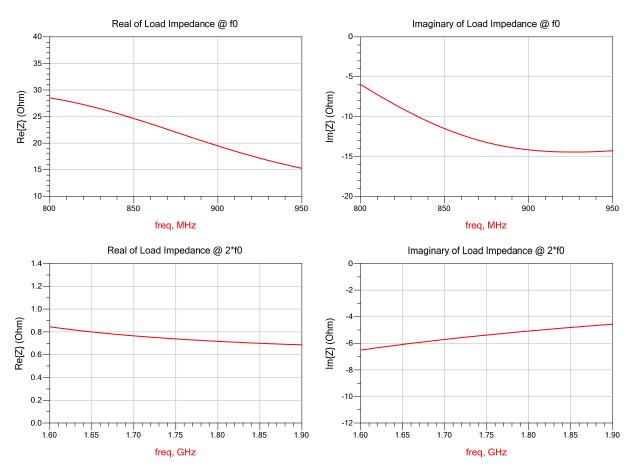

| Figure 5-22 – The simulated load impedance (real and imaginary parts) of the power stage                  | 139   |

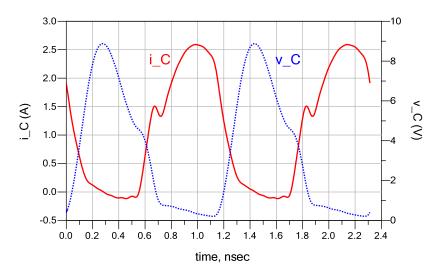

| Figure 5-23 – The collector current and voltage waveforms of the power stage.                             | 140   |

| Figure 5-24 – The simulated load impedance (real and imaginary parts) of the driver stage                 | 140   |

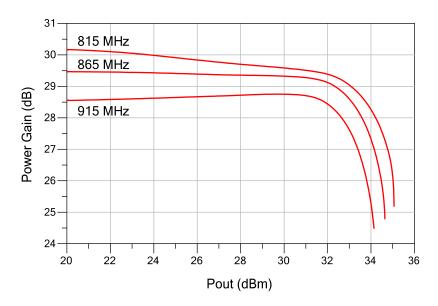

| Figure 5-25 – The simulated power gain vs. output power at f <sub>0</sub> (frequencies 815, 865, and      | 915   |

| MHz)                                                                                                      | 141   |

| Figure 5-26 – The simulated phase difference between output and input signals vs. output po               | wer   |

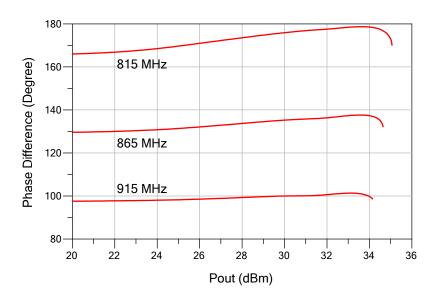

| at fo (frequencies 815, 865, and 915 MHz).                                                                | 141   |

| Figure 5-27 – The simulated power added-efficiency vs. output power at f <sub>0</sub> (frequencies 815, 8 | 865,  |

| and 915 MHz).                                                                                             | 142   |

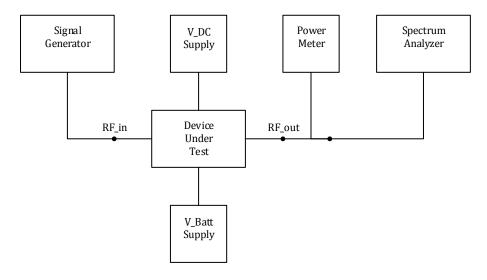

| Figure 5-28 – The fully assembled power amplifier module on evaluation board for testing                  | 143   |

| Figure 5-29 – A block diagram of the test environment.                                                    | 143   |

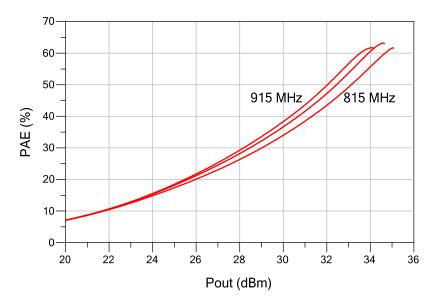

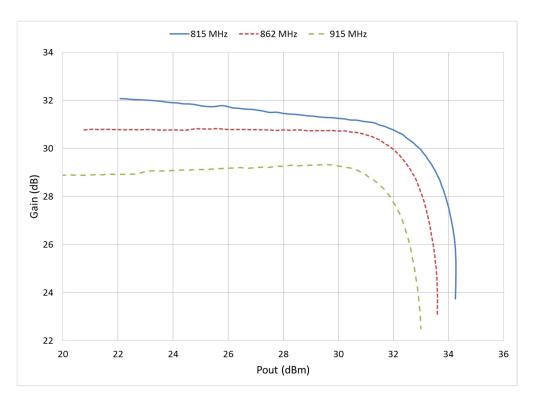

| Figure 5-30 – 2G/GSM: The measured power gain vs. output power at $f_0$ (multiple frequenci               | ies). |

|                                                                                                           | 145   |

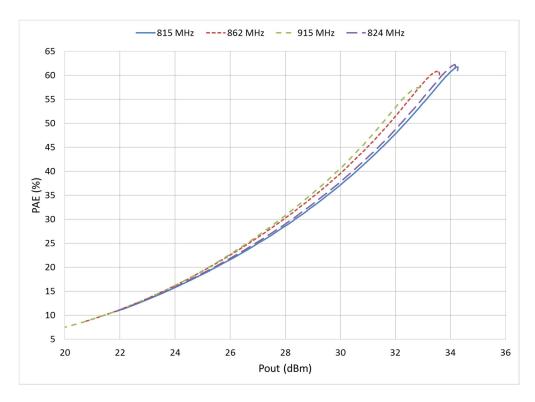

| Figure 5-31 – 2G/GSM: The measured power-added efficiency (PAE) vs. output power a                        | at fo |

| (multiple frequencies).                                                                                   | 145   |

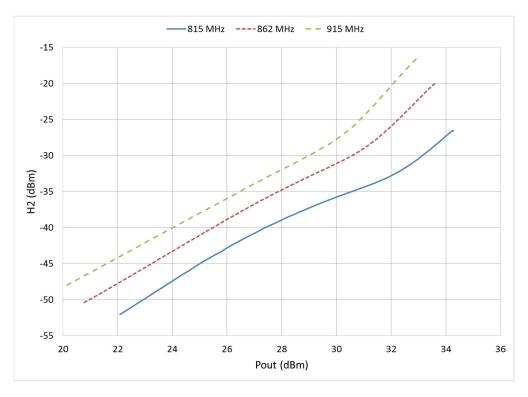

| Figure 5-32 $-$ 2G/GSM: The measured second harmonic output power vs. output power a                      | at fo |

| (multiple frequencies).                                                                                   | 146   |

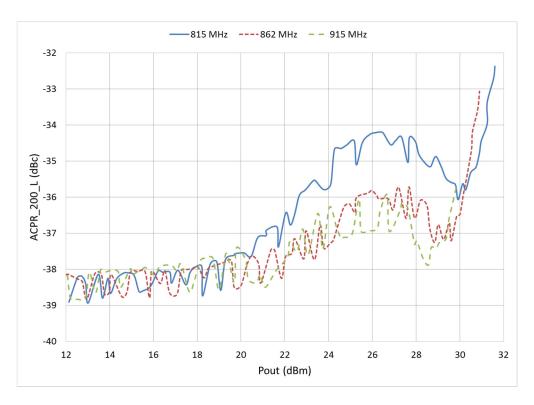

| Figure 5-33 – 2.5G/EDGE: The measured ACPR-200 (worst of upper/lower) vs. output power                    | er at |

| f <sub>0</sub> (multiple frequencies).                                                                    | 147   |

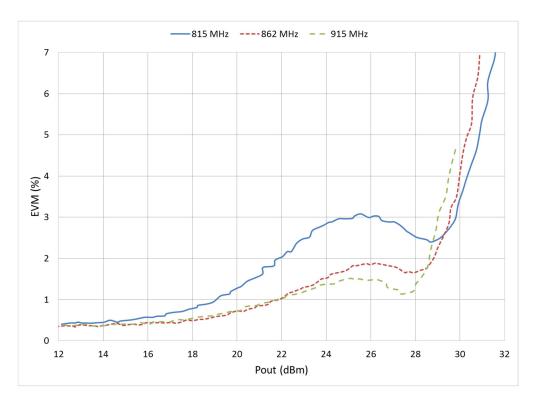

| Figure 5-34 – 2.5G/EDGE: The measured EVM vs. output power at f <sub>0</sub> (multiple frequencies).      | 148   |

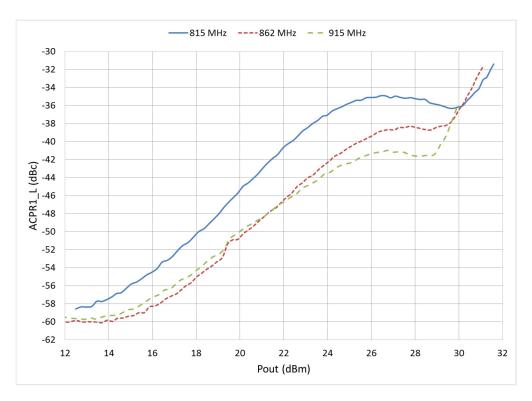

| Figure 5-35 – 3G/W-CDMA: The measured ACPR1 (worst of upper/lower) vs. output power a                     | at fo |

| (multiple frequencies).                                                                                   | 149   |

## **LIST OF TABLES**

| Table 2-1 – The power amplifier classification based on the conduction angle | 14  |

|------------------------------------------------------------------------------|-----|

| Table 4-1 – The component values of the typical design process without loss  | 80  |

| Table 4-2 – The component values of design LLL_3S_Typ.                       | 92  |

| Table 4-3 – The component values of design TTT_3S                            | 92  |

| Table 4-4 – The component values of design TT_2S.                            | 92  |

| Table 5-1 – The design targeted specifications                               | 108 |

| Table 5-2 – Test environment settings.                                       | 144 |

| Table 5-3 – 2.5G/EDGE: test settings.                                        | 147 |

| Table 5-4 – 3G/W-CDMA: test settings.                                        | 148 |

#### 1.

#### Introduction

#### 1.1 - Research Motivation

The RF power amplifier is an important element in any wireless communications system. The power amplifier provides a significant power amplification to the transmitted signal, leading to the consumption of most of the system power. Hence, there is continuous research to improve the power efficiency of the power amplifier and extend the battery lifetime of the handset.

The continuous growth in wireless communications applications has led to a fast growing market of wireless handsets (such as cell phones and tablets). It has created an environment with a high demand for better performance and higher data rates, and has led to the coexistence of multiple industrial standards<sup>1</sup> (2G/2.5G/3G/4G). Each standard utilizes a different modulation scheme with different linearity requirements. For example, the 2G standard uses Gaussian Minimum Shift Keying (*GMSK*) modulation that generates a constant envelope signal, not requiring linear amplitude amplification. In contrast, the 4G standard utilizes Quadrature Amplitude Modulation (*QAM*) which mandates a high degree of linear amplification.

The recent expansion of the cellular market has required more frequency bands to cover multiple standards (2G/3G/4G). The spectrum that covers the cellular usage around the globe (including most common bands) can be divided into three major bands: low band (695 MHz – 915 MHz), mid band (1710 MHz – 2025 MHz), and high band (2300 MHz – 2700 MHz). Each major band is organized into many assigned narrower bands which are used in different regions around the globe.

To meet the current market demands, handset manufacturers are targeting the design of a single handset that covers the latest standards (3G/4G) with a backward compatibility to the earlier standards (2G/2.5G), while exhibiting a broadband coverage over one or more of the major frequency bands.

<sup>&</sup>lt;sup>1</sup> - The terms "standard" and "mode" are used throughout the dissertation referring to the cellular standard 2G/GSM, 2.5G/EDGE, 3G/W-CDMA, and 4G/LTE.

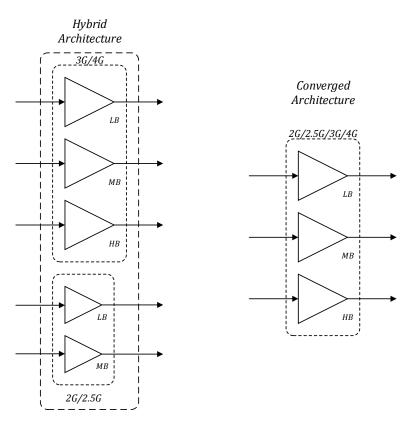

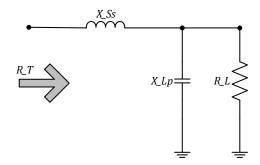

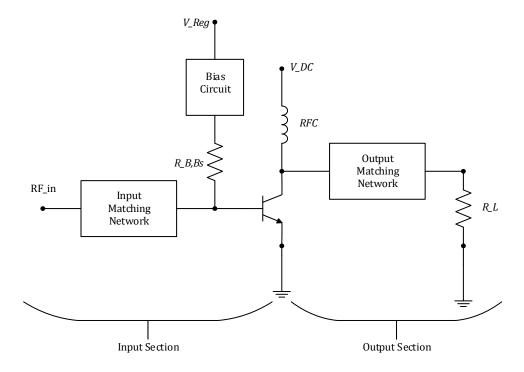

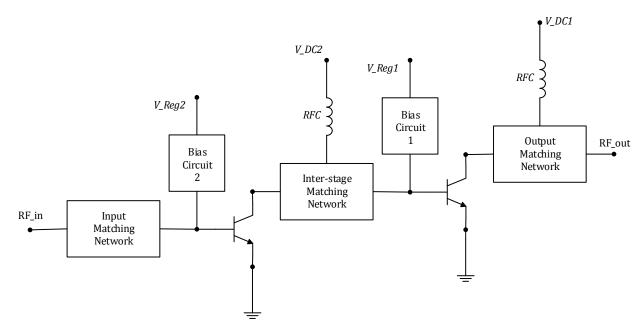

Different power amplifier architectures have been proposed to achieve such a coverage of multiple standards with a broadband response, as shown in Figure 1-1. One power-amplifier module architecture, known as a "hybrid power amplifier", is to design a single module that contains multiple power amplifiers. The architecture includes two power amplifiers for the 2G/2.5G modes where one covers the low band and the other covers the mid band. At least, three more linear power amplifiers are needed for the 3G/4G modes, where each amplifier covers a part or the full bandwidth of one of the major bands. Another architecture, known as a "converged power amplifier", is a single module that contains multiple power amplifiers, where each power amplifier covers one of the major frequency bands while operating in different modes (2G/2.5G/3G/4G).

Figure 1-1 – Different power amplifier module architectures.<sup>2</sup>

The two architectures show there is a trade-off between performance and cost/size. The hybrid approach provides better performance since each power amplifier is dedicated to a specific mode and a single frequency band. The converged approach provides less cost and board area,

<sup>&</sup>lt;sup>2</sup> - The "LB", "MB", and "HB" refer to the low, mid and high bands, respectively.

eliminating two or more power amplifiers with the associate matching networks. Typically the power amplifiers that operate in the 2G/2.5G modes are the ones to be eliminated. The design solution to a converged power amplifier architecture is required to exhibit three characteristics: high linearity, high efficiency, and broadband frequency response in order to operate in the different modes (2G/2.5G/3G/4G) with minimal or no reconfiguration as suggested by Cheng and Young [1]. This solution is simpler in terms of cost and circuit complexity compared to more complex architectures that require system integration such as those presented by McCune [2], and Daehyun, et al. [3].

As a result, there is a demand for a linear power amplifier that operates with high efficiency at the saturated output power level (in the 2G mode), maintains a high linearity with enhanced efficiency at back-off output power levels (in the 2.5G/3G/4G modes), and covers a broadband frequency response. Such a power amplifier represents a solution to the "converged power amplifier" architecture. It should be noted, the required output power level in the 2G mode, is higher than the required output power levels in the 2.5G/3G/4G modes where linearity is required. Such a distribution of the needed power levels for these modes is suitable to be covered by a single power amplifier, since the power amplifier would operate at the saturated power level in the 2G mode and operates at back-off power levels in the 2.5G/3G/4G modes.

#### 1.2 - Background

Three major areas of interest in the power amplifier design are: achieving high power efficiency, operating with high linearity, and covering a broadband frequency response.

#### 1.2.1 - Power Efficiency

The power amplifier consumes the majority of the power in a wireless transmitter system. Hence, there is continuous research to improve the power efficiency of the power amplifier. Over time, different techniques to improve the power efficiency have been proposed, where each technique is recognized as a class of power amplifier.

A fundamental technique to improve the efficiency of the power amplifier is to reduce the quiescent bias level, which is known as the reduced conduction angle operation (class-AB, B, and C). By reducing the quiescent bias level, the transistor conducts for a portion of the RF cycle rather than a full RF cycle as in class-A operation.

A different technique to increase the power efficiency uses the generated harmonics within the power transistor to engineer the voltage waveform at the collector/drain terminal of the transistor. Class-F where the third harmonic is utilized, Raab [4], and class-J where the second harmonic is utilized, Cripps, et al. [5], are examples of such a technique. It is important to note that these techniques of utilizing the generated harmonics provide linear operation of the fundamental frequency as well as improving the efficiency. Therefore, they are suitable for a linear power amplifier application where a modulated signal of varying envelope is transmitted. One variation of class-F is Class-AB/F, as presented by Daehyun, et al. [6], which can achieve linearity and high efficiency at the maximum output power.

Another technique to obtain high power efficiency depends on operating the transistor as a switch, such as class-D, El-Hamamsy [7], and class-E, Sokal and Sokal [8]. Due to the switching operation of the transistor, no linear relationship exists between the amplitudes of the input and output signals.<sup>3</sup> Hence, such a technique is suitable to a power amplifier application where a modulated signal with a constant envelope is transmitted since a linear operation is not required.

#### 1.2.2 - Linearity

The nonlinear operation of the power amplifier causes the generation of unwanted distortion products, which extend out of the intended channel of the transmitted signal. The requirement for linearity in radio frequency power amplifiers arises from the necessity of achieving minimum interference with other channels in the frequency spectrum. Also, as cellular standards apply digital modulation schemes, with both of the amplitude and phase are varying, the need for a linear power amplifier increases, since the nonlinearity of the power amplifier causes not only a spectral spreading, but also amplitude and phase distortions of the transmitted signal.

Different natures of nonlinearity occur in the power amplifier. The nonlinearities can be categorized into a weak nonlinearity and a strong nonlinearity, Maas [9]. A weak nonlinearity occurs when the power amplifier operates in the varying output power range. While the strong nonlinearity appears when the power amplifier operates at the saturated output power.

The transistor characteristics have an effect on linear operation. For example, the exponential relationship between the collector current and the base-emitter voltage of the HBT exhibits an

<sup>&</sup>lt;sup>3</sup> - The class-D is common at audio frequencies to obtain a linear output from a pulse-width modulated input at a switching rate far above the frequencies of use.

expansive transconductance<sup>4</sup> that can be utilized to reduce the nonlinearity inherited from the operation with a reduced conduction angle, Cripps [10]. Also, the elimination of the odd-degree components at the output terminal of the transistor may improve the linearity, Cripps [11].

Utilizing an HBT transistor in a power amplifier shows a bias depression phenomenon that degrades linearity at high output power. Such a behavior of HBT requires employing a bias circuit that provides temperature compensation as well as a bias depression reduction in order to improve linearity.

#### 1.2.3 - Broadband Matching Networks

One technique of designing a matching network is to use tables of impedance-transforming networks of low-pass filter form. Such tables are presented by Matthaei [12] for a Chebyshev response and by Cristal [13] for a maximally-flat (Butterworth) response. This technique provides a ladder network of series inductances and shunt capacitances.

Another technique of designing matching networks is based on single-section matching networks of different topologies (L-network, T-network, and Pi-network). A set of design equations for each topology is derived by combining the concepts of series/parallel resonance with series/parallel impedance transformation. A broadband frequency response can be achieved by cascading multiple sections.

The Smith chart has been used as a tool for designing lumped and distributed matching networks. Both narrow-band and broadband matching networks can be designed using the Smith chart following the typical topologies (L-network, T-network, and Pi-network), as presented by Gonzalez [14]. In power amplifiers, the Smith chart provides an insight of the load that is presented to the transistor since load-pull contours are usually plotted on the Smith chart.

Techniques of designing broadband matching networks using transformers have been available for decades, as presented by Clarke and Hess [15]. Although, using transformers for broadband matching networks provides better results compared to other techniques, it has a restricted application in industry due to limitations that require designing for small die and module size. Recently, investigations to implement on-chip transformers as part of output matching networks were carried out, Hoseok, et al. [16].

5

<sup>&</sup>lt;sup>4</sup> - The transconductance increases as the input drive level increases.

#### 1.2.4 - Semiconductor Device Technology

Gallium Arsenide (*GaAs*) semiconductor is one of the compound materials that enables low device parasitics and high power density, making it suitable for high power and RF applications. High band-gap semiconductors, such as Gallium Nitride (*GaN*), offers a high voltage operation and higher power density compared to GaAs. Recently, GaN technology has seen a significant process improvement and expansion in applications.

In the cellular industry, Laterally Diffused Metal Oxide Silicon (*LDMOS*) is used in high power applications such as power amplifiers for base stations. GaAs HBT is widely used in low power mobile devices, since it requires a single supply voltage – a good feature in any application where the circuit is supplied from a battery. As recent standards, such as 4G/LTE, specify a lower output power, power amplifier designs using silicon CMOS technology have been investigated as a replacement to GaAs HBT, Chang-Ho, et al. [17]. Recent results shows that silicon CMOS is still not surpassing the linearity and high efficiency that GaAs HBT is providing.

GaAs HBT has more features making in the dominant technology of the power amplifier in handsets. GaAs HBT exhibits a high power density, allowing for a smaller device size than other technologies, saving on both die and module areas. With high linearity requirements, multiple approaches can be applied to linearize the relationship between the output current and the input voltage of an HBT-based amplifier at the signal frequency.

GaAs HBT process technology available from TriQuint has been selected to implement a design that validates the techniques proposed in the research, TriQuint [18]. The process features an InGaP emitter technology with a maximum junction current density of 20 kA/cm<sup>2</sup>.

#### 1.2.5 - Power Amplifiers for Wireless Handsets

The typical power amplifier module for handsets consists of a multi-chip package. The module includes a power amplifier (GaAs HBT) and a controller (silicon CMOS) providing the regulated bias voltages needed for the power amplifier and other control signals. The module may also include a silicon-on-insulator (SOI) switch that provides routing to different frequency bands. All chips are mounted on a high frequency multi-layer laminate. Typically, the output matching networks are implemented on the laminate. In order to reduce the number of discrete components, almost all inductors in matching networks of power amplifier modules are printed planar inductors, Franco [19].

#### 1.3 - Dissertation Overview

The design of a linear power amplifier with high efficiency that covers a broadband frequency response requires investigating three major areas of interest in the power amplifier design: achieving high efficiency, operating with high linearity, and designing a broadband matching network.

Chapter 2 presents multiple techniques to improve the power efficiency of a linear power amplifier. The chapter presents a full analysis and investigations of the techniques with detailed calculations of the required load impedance and the maximum theoretical efficiency that can be achieved for each technique.

Chapter 3 presents investigations of the nonlinearities in RF power amplifiers. The chapter presents the nature and causes of nonlinearities. The effect of operating the power amplifier in a reduced conduction angle as well as the effect of odd-degree harmonics at the output of the transistor are considered. The effect of HBT transistor on linearity is investigated, as well as multiple bias circuits that provide temperature compensation and improved linearity.

Chapter 4 presents a new design methodology for matching networks. The methodology considers the inductor loss in the design process and provides an accurate impedance transformation while providing more degrees of freedom to meet a variety of specifications.

Chapter 5 introduces the proposed design process to achieve a linear power amplifier that operates with high efficiency and can operate in different modes. The implemented power amplifier module is presented as well as the simulated and measured results that validate the proposed design process.

Chapter 6 presents the summary and the conclusion of the research.

(This page left intentionally blank)

## **High Efficiency Techniques for Linear Power Amplifiers**

#### 2.1 - Introduction

The power amplifier consumes the majority of the power in a wireless transmitter system. Hence, there is continuous research to improve the power efficiency of the power amplifier. Over time, different techniques to improve the power efficiency have been proposed, where each technique is recognized as a class of power amplifier.

The class-A power amplifier is considered the simplest power amplifier, sharing many aspects of the small-signal RF amplifier. However, class-A is not considered one of the high-efficiency classes. The analysis of class-A is presented in this chapter to establish a reference for comparison with the other high-efficiency classes, allowing many of the behaviors of the other classes to be interpreted in terms of the operation of class-A.

A fundamental technique to improve the efficiency of the power amplifier is to reduce the quiescent bias level, which is known as the reduced conduction angle operation (class-AB, B, and C). By reducing the quiescent bias level, the transistor conducts for a portion of the RF cycle rather than a full RF cycle as in class-A. Hence, the class-A and the other classic classes (class-AB, B, and C) are defined based on the quiescent bias point.

A different technique to increase the power efficiency uses the generated harmonics within the power transistor to engineer the voltage waveform at the collector/drain terminal of the transistor. Class-F where the third harmonic is utilized, Raab [4], and class-J where the second harmonic is utilized, Cripps, et al. [5], are examples of such a technique. It is important to note that these techniques provide linear operation of the fundamental frequency as well as improving the efficiency. Therefore, it is suitable for linear power amplifier applications where a modulated signal of varying envelope is transmitted.

Another technique to obtain high power efficiency depends on operating the transistor as a switch, such as class-D, El-Hamamsy [7], and class-E, Sokal and Sokal [8]. Due to the switching operation of the transistor, no linear relationship exists between the amplitudes of the input and output signals. Hence, such a technique is suitable to power amplifier applications where a modulated signal with a constant envelope is transmitted since a linear operation is not required.

#### 2.1.1 - Class-A Power Amplifier

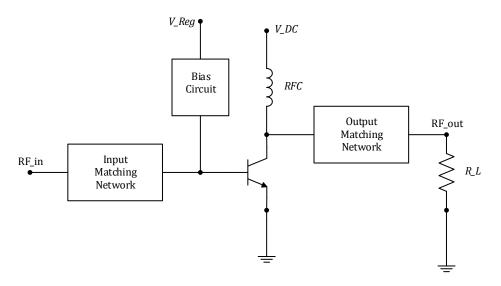

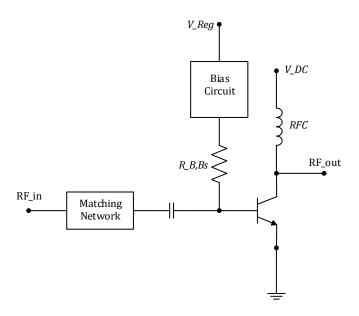

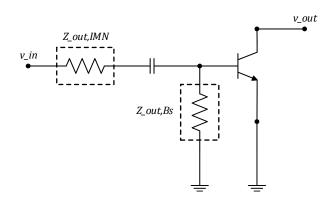

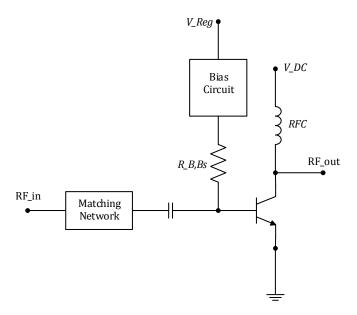

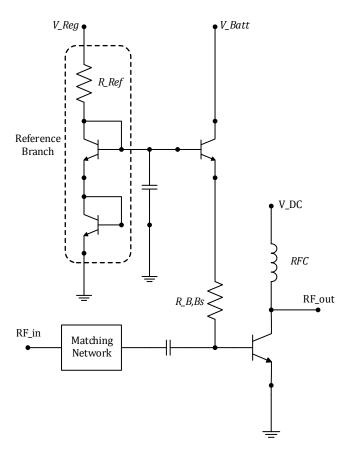

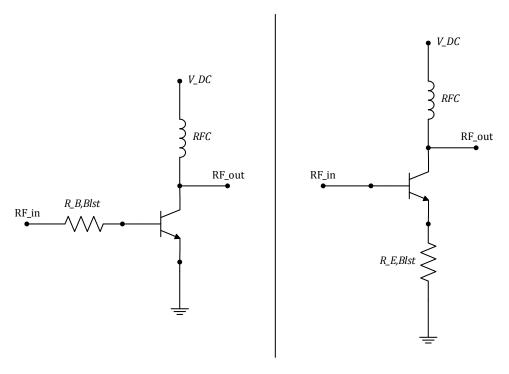

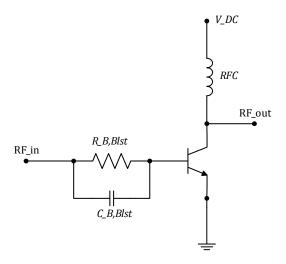

A basic single-stage power amplifier that may represent a class-A power amplifier is shown in Figure 2-1. In class-A power amplifier, the transistor is biased in the middle of the *I-V* transfer characteristic. For linear operation, the current and voltage signals are constrained such that both do not exceed the limits of cut-off and saturation.

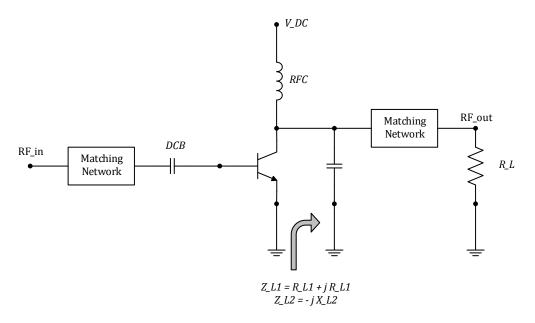

Figure 2-1 – A Basic single-stage power amplifier.

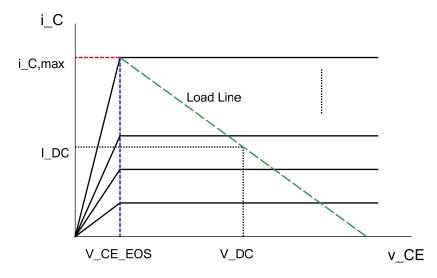

Figure 2-2 shows a simplified *I-V* transfer characteristic of a typical transistor. Several key assumptions are illustrated in the figure and maintained throughout this chapter and the following chapters:

- The output resistance of the transistor is infinite.

- The transistor operates as a voltage-controlled current source with a linear transconductance.

- The reference plane of the load location is taken at the transistor output current source.

The associated output reactance of the transistor is considered to be a part of the output matching network.

Figure 2-2 – A simplified I-V transfer characteristic of a transistor.

The optimum resistive load needed to obtain the maximum linear output power from a transistor with the given *I-V* transfer characteristic in Figure 2-2 is computed as

$$R_{L,opt,A} = \frac{V_{ce,Max}}{I_{c,Max}} \tag{2-1}$$

$$V_{ce,Max} = V_{DC} - V_{CE,EOS} \tag{2-2}$$

$$I_{c,Max} = \frac{i_{c,Max}}{2} = I_{DC}$$

(2-3)

where  $V_{CE,EOS}$  is the edge of saturation voltage. The  $V_{ce,Max}$  is the maximum voltage amplitude for linear operation. The  $I_{C,Max}$  is the maximum current amplitude for linear operation. The  $i_{C,Max}$  is the maximum instantaneous collector current for a given transistor, which is determined by the maximum current handling capability of the device. The  $V_{DC}$  is the DC supply voltage which is specified by the system. The  $I_{DC}$  is the DC collector current component.

The optimum power (maximum linear output power) achieved by presenting the optimum load to the transistor is calculated as

$$P_{opt,A} = \frac{1}{2} V_{ce,Max} I_{c,Max} = \frac{1}{2} (V_{DC} - V_{CE,EOS}) I_{DC}$$

(2-4)

The corresponding maximum power efficiency of class-A ( $\eta_{Max,A}$ ) is given by

$$\eta_{Max,A} = \frac{P_L}{P_{DC}} = \frac{\frac{1}{2} (V_{DC} - V_{CE,EOS}) I_{DC}}{V_{DC} I_{DC}}$$

(2-5)

where  $P_L$  is the power delivered to the load (in Watts). The  $P_{DC}$  is the consumed DC power (in Watts). Assuming an ideal transistor where  $V_{CE,EOS}$  is very small and approaching a value of zero, then the efficiency for an ideal transistor ( $\eta_{ideal,A}$ ) is given by

$$\eta_{ideal,A} = \frac{\frac{1}{2} V_{DC} I_{DC}}{V_{DC} I_{DC}} = 50\%$$

(2-6)

which is the well-known result of the ideal class-A power efficiency. From Equations (2-5) and (2-6), a general relationship between the maximum efficiency for a transistor with an edge of saturation voltage ( $V_{CE,EOS}$ ) and the efficiency for an ideal transistor ( $V_{CE,EOS} = 0$ ) can be given as

$$\eta_{Max} = \frac{(V_{DC} - V_{CE,EOS})}{V_{DC}} \eta_{ideal}$$

(2-7)

Another term that is widely used to indicate the power efficiency is the power-added efficiency (PAE)

$$PAE = \frac{P_L - P_{in}}{P_{DC}} \tag{2-8}$$

where  $P_{in}$  is the input power (in Watts). The advantage of this form is it highlights both the conversion of the DC power into the RF signal power and the power gain of the amplifier.

#### 2.1.1.1 - Observations on Class-A Operation

The assumption that the transistor has a linear transconductance introduces a false expectation that class-A is a fully linear power amplifier. Real transistors exhibit a weak nonlinearity within the class-A region of operation. Operation at the optimum output power, where the full range of current and voltage are utilized, forces the voltage and current to swing across the weakly-nonlinear region. Therefore, in general, a class-A power amplifier is not a linear power amplifier. Such an observation mandates presenting short-circuit terminations to the harmonic components for proper operation of class-A.

For linear operation, the input drive should be maintained below the value that causes the voltage and current to increase beyond the limits of cut-off or saturation. Once the voltage or current reaches either cut-off or saturation, the output power starts to compress until it reaches the 1dB compression point.<sup>5</sup> A further increase in the input drive signal leads to a higher compression level to the point that the output power saturates.

Applying the optimum load, with the full range of voltage and current utilized, produces the highest 1dB compression point as well as the highest maximum linear output power for a given transistor. For a given maximum collector current ( $i_{C,Max}$ ), as the load deviates from the optimum load, by increasing or decreasing the load, the 1dB compression point decreases as well as the maximum linear output power. Decreasing the load reduces the available voltage swing and causes the current to reach cut-off faster than the case of the optimum load. While, increasing the load reduces the available current swing and causes the voltage signal to swing into the saturation region of the transistor where the output current is function not only of the input voltage but also the output voltage. As a result, increasing the load distorts the peak of the current waveform and generates many harmonic components with high levels. This is an important observation in terms of achieving the maximum range of linear operation for a given transistor, as a higher 1dB compression point indicates a larger linear output power range.

#### 2.1.2 - Load-Pull Technique

The load-pull technique is a fundamental method to determine the optimum load for a given transistor through a laboratory measurement or simulation. At a single frequency, the technique is implemented by tuning the load impedance presented to the collector/drain of the transistor. Typically, the tuning is carried out on the impedance at the fundamental frequency while presenting a constant impedance to harmonic components. Such an approach causes a major limitation to determine the optimum load when implementing one of the advanced high-efficiency classes, where the generated harmonics are employed to improve the power efficiency. An advanced load-pull system, which is not widely exploited, would tune the impedance at the fundamental as well as the second and third harmonic components, such as those introduced by Benedikt, et al. [20] and Hashmi, et al. [21].

<sup>5</sup> - The 1dB Compression point refers to the output power level where the large-signal gain has decreased by 1dB from the small-signal gain.

The results of the load-pull measurement is a plot on the Smith chart that contains a point representing the optimum load that achieves the optimum output power. The plot typically contains two or more contours, each contour representing a specified output power level lower than the optimum power. It should be noted that during the load-pull measurement/simulation, the gain of the amplifier may vary along each contour and the input power has to be adjusted accordingly to maintain the output power level. Simple techniques to predict the load-pull contours for a transistor that operates as a class-A power amplifier has been proposed, such as those by Cripps [22], and Kondoh [23].

It is instructive to interpret those contours in terms of the complex power. Each contour can be described as a contour for the same real power, but with a different apparent power (which is the magnitude of the complex power). The minimum apparent power on each contour equals the real power of the contour for the given transistor. Such a point of view indicates that applying a load other than the optimum load may cause the transistor to operate at a higher power capacity than what is really needed, in order to supply the additional reactive power.

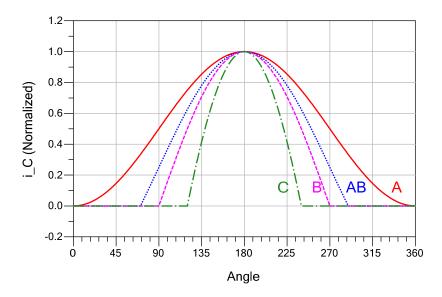

### 2.2 - Reduced Conduction Angle Operation

The reduced conduction angle technique is a classic approach to achieve higher power efficiency than what is typically offered by a class-A power amplifier. In class-A, the collector current conducts during the full RF cycle  $(2\pi)$ . The concept of the reduced conduction angle operation is to bias the transistor at a lower quiescent bias point while the input drive signal turns on the transistor during a portion of the RF cycle  $(< 2\pi)$ , causing the collector current to conduct only during that same portion. A classic set of operating classes of power amplifier (Class-AB, B, and C) have been defined based on the conduction angle value, as shown in Table 2-1.

| Class | Conduction Angle                         |

|-------|------------------------------------------|

| A     | $2\pi (360^{\circ})$                     |

| AB    | $\pi (180^{\circ}) - 2\pi (360^{\circ})$ |

| В     | $\pi (180^{\circ})$                      |

| С     | $0 - \pi (180^{\circ})$                  |

Table 2-1 – The power amplifier classification based on the conduction angle.

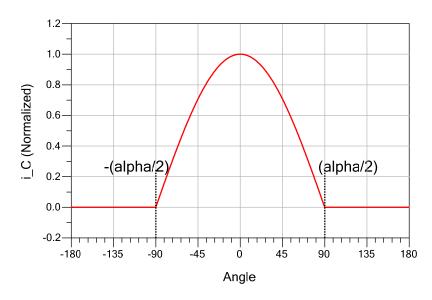

In order to utilize the maximum power capacity of the transistor, the full range of the collector current should be used between cutoff and the maximum collector current ( $i_{C,Max}$ ). Therefore, when operating at a reduced conduction angle, the input drive signal is required to increase compared to the class-A operation in order to restore the peak of the collector current to the maximum value. A typical observation is the power gain decreases as the conduction angle decreases. Figure 2-3 shows the instantaneous collector current, normalized to the maximum current, for each one of the classes that are defined in Table 2-1, assuming the input drive signal is increased to generate a collector current with a peak value that equals the maximum current.

Figure 2-3 – The collector current of the reduced conduction angle operation (normalized to the maximum current (i<sub>C,Max</sub>)).

It should be noted that in order to achieve the highest possible power gain for a single-stage power amplifier, it is generally found that the smallest transistor capable of delivering the needed output power should be utilized. As the transistor periphery increases the power gain decreases, which might cause a significant degradation in the power-added efficiency.

#### 2.2.1 - Observations on the Fourier Series of a Truncated Sinusoid 6

Due to the low quiescent bias point, the collector current takes the shape of a truncated sinusoid when operating at a reduced conduction angle, as shown in Figure 2-3. A Fourier series analysis

<sup>&</sup>lt;sup>6</sup> - A detailed derivation of the DC, fundamental, and harmonic components, using the Fourier series analysis is presented in appendix A2.1.

is needed to understand the relationship between the frequency components of the collector current (DC, fundamental, and harmonics) and the conduction angle. Following the analysis presented by Cripps [10], it is assumed the input drive signal varies with the conduction angle to produce a collector current waveform with a peak value equals the maximum current ( $i_{C,Max}$ ).

The instantaneous collector current is represented as

$$i_{C}(\theta) = \begin{cases} I_{DC,Q} + I_{c} \cos(\theta), & \left(-\frac{\alpha}{2} < \theta < \frac{\alpha}{2}\right) \\ 0, & \left(-\pi < \theta < -\frac{\alpha}{2}\right), \left(\frac{\alpha}{2} < \theta < \pi\right) \end{cases}$$

(2-9)

where  $I_c = i_{C,Max} - I_{DC,Q}$ , which is the amplitude of the generated current signal. The  $I_{DC,Q}$  is the quiescent DC collector current. The  $i_{C,Max}$  is the maximum instantaneous collector current for the given transistor. The  $\alpha$  is the conduction angle. Writing the instantaneous collector current in terms of  $i_{C,Max}$ , and  $\alpha$

$$i_{C}(\theta) = \begin{cases} \frac{i_{C,Max}}{\cos\left(\frac{\alpha}{2}\right) - 1} \left(\cos\left(\frac{\alpha}{2}\right) - \cos(\theta)\right), & \left(-\frac{\alpha}{2} < \theta < \frac{\alpha}{2}\right) \\ 0, & \left(-\pi < \theta < -\frac{\alpha}{2}\right), \left(\frac{\alpha}{2} < \theta < \pi\right) \end{cases}$$

(2-10)

Applying Fourier series analysis to the instantaneous collector current given in Equation (2-10), the DC current component is computed as

$$I_{DC} = \frac{1}{2\pi} \cdot \frac{i_{C,Max}}{\cos\left(\frac{\alpha}{2}\right) - 1} \cdot \left(\alpha\cos\left(\frac{\alpha}{2}\right) - 2\sin\left(\frac{\alpha}{2}\right)\right) \tag{2-11}$$

While the fundamental  $(I_1)$ , second  $(I_2)$ , and third  $(I_3)$  harmonic current components are found to be

$$I_1 = \frac{1}{\pi} \cdot \frac{i_{C,Max}}{\cos\left(\frac{\alpha}{2}\right) - 1} \cdot \left(\frac{1}{2}\sin(\alpha) - \frac{\alpha}{2}\right)$$

(2-12)

$$I_2 = \frac{1}{\pi} \cdot \frac{i_{C,Max}}{\cos\left(\frac{\alpha}{2}\right) - 1} \cdot \left(\frac{1}{6}\sin\left(\frac{3\alpha}{2}\right) - \frac{1}{2}\sin\left(\frac{\alpha}{2}\right)\right) \tag{2-13}$$

$$I_3 = \frac{1}{\pi} \cdot \frac{i_{C,Max}}{\cos\left(\frac{\alpha}{2}\right) - 1} \cdot \left(\frac{1}{12}\sin(2\alpha) - \frac{1}{6}\sin(\alpha)\right)$$

(2-14)

Equation (2-11) shows that the DC current component is a linear function of the maximum current ( $i_{C,Max}$ ), for a given conduction angle. For a varying input signal, the maximum current value is a function of the input drive level. Hence, the DC current component follows the input drive signal, decreasing or increasing. This is an important observation for designing the bias circuit for a power amplifier that operates at a reduced conduction angle. As increasing the input drive mandates the bias circuit to supply a higher DC current than the quiescent current.

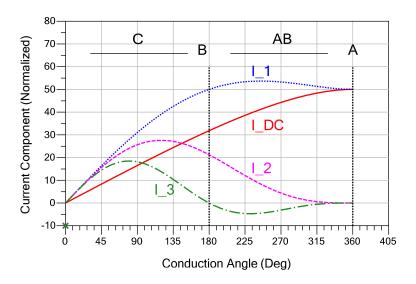

Figure 2-4 shows that the DC current component decreases as the conduction angle decreases, which is the main advantage of applying the reduced conduction angle technique. A lower DC current component causes a lower DC power consumption for a given DC supply voltage while maintaining the needed output signal level. Therefore, reducing the conduction angle is a necessary step towards achieving a higher power efficiency than in class-A.

Figure 2-4 – The fundamental and harmonic current components vs. the conduction angle (normalized to the maximum current (ic,Max)).

From Figure 2-4, it is observed that the fundamental current component in class-B operation equals the same value as in class-A, for the same maximum collector current ( $i_{C,Max}$ ). Also, the corresponding DC component is lower in class-B than in class-A. Therefore, applying the load of class-A to class-B causes the same output power level at the fundamental frequency for both of

the classes, but a lower DC power consumption is achieved in class-B, leading to a higher power efficiency. It is interesting to note that the second harmonic current component exists with a relatively high level in class-B (about 42% of the fundamental component), while all odd-order harmonic components equal zero in class-B.

As the conduction angle decreases below  $\pi$ , which is defined as class-C, both the fundamental and the DC current components decrease. This decrease causes a reduction in the DC power consumption as well as the output power at the fundamental frequency. Due to the reduction of the output power and the requirement to increase the input drive signal, class-C typically suffers from a much lower power gain than in class-A.

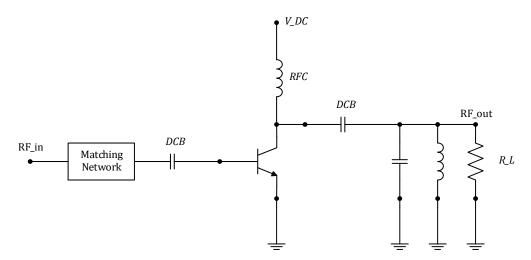

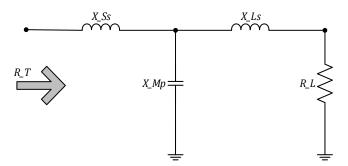

#### 2.2.2 - The Optimum Load for Class-AB, B, and C

The Fourier series analysis has displayed that operating at a reduced conduction angle generates many harmonic components of the collector current due to the truncated sinusoid waveform. As presented by Lee [24], and Krauss, et al. [25], the typical implementation of class-AB, B, and C presents a short circuit to the generated harmonic current components. Therefore, no voltage component is generated at those frequencies. While a resistive load is presented to the fundamental current component, generating a voltage component at the fundamental frequency. Such a load is ideally implemented by a tank circuit with a high quality factor, as shown in Figure 2-5.

Figure 2-5 – A tank circuit represents an ideal load for a power amplifier that operates at a reduced conduction angle.<sup>7</sup>

.

<sup>&</sup>lt;sup>7</sup> - RFC refers to an RF choke. DCB refers to a DC block.

The tank circuit represents an ideal implementation that approximates the real output matching network. Realistic power amplifiers, operating in class-AB, B, and C, are implemented with an output matching network that contains two or more matching sections. These networks exhibit some non-ideal effects at the harmonic frequencies that must be considered in the final design.

Operating at a reduced conduction angle, in order to achieve the maximum output power from a given transistor with the *I-V* transfer characteristic shown in Figure 2-2, the maximum peak of the input drive signal is required to produce a collector current with a peak value equals the maximum collector current ( $i_{C,Max}$ ). For each conduction angle of operation, there is a specific fundamental current component produced. The optimum load is determined as the resistive load to allow the fundamental voltage amplitude to reach the maximum value ( $V_{DC} - V_{CE,OS}$ ), as shown in Figure 2-2. Hence, the optimum load can be calculated by

$$R_{L,opt} = \frac{V_{ce1,Max}}{I_{c1,Max}} \tag{2-15}$$

$$V_{ce1,Max} = V_{DC} - V_{CE,EOS} \tag{2-16}$$

where  $V_{CE,EOS}$  is the edge of saturation voltage. The  $V_{cel,Max}$  is the maximum voltage amplitude of the fundamental component. The  $I_{cl,Max}$  is the maximum current amplitude of the fundamental component for a current waveform that reaches the maximum instantaneous current ( $i_{C,Max}$ ).

It should be noted that in order to maintain linear operation, the transistor should not be overdriven, where the drive signal increases beyond the value that causes the collector current to reach the maximum current ( $i_{C,Max}$ ). Overdriving the transistor causes the collector current waveform to be clipped, generating a high level of harmonic components. Also, the load at the fundamental frequency should not increase such that the collector voltage signal swings into the saturation region. Such a situation causes many higher harmonic current components to be generated with a higher level and mixed within the transistor.

# 2.2.3 - Maximum Linear Output Power and Power Efficiency of Ideal Class-B

Many high efficiency techniques for linear power amplifiers rely on biasing the transistor in deep class-AB (ideal class-B). In order to establish a reference for comparison with high efficiency

techniques, it is necessary to calculate the optimum output power (maximum linear power) and the power efficiency of an ideal class-B operation.

For ideal class-B (where the conduction angle  $\alpha = \pi$ ), the optimum power achieved by presenting the optimum load to the transistor can be calculated by

$$P_{opt,B} = \frac{1}{2} V_{ce1,Max} I_{c1,Max,B}$$

(2-17)

From Equation (2-12), the maximum amplitude of the fundamental current component ( $I_{c1,Max,B}$ ) is computed to be

$$I_{c1,Max,B} = 0.5 * i_{c,Max} (2-18)$$

From Equation (2-11), the DC current component in class-B operation is calculated to be

$$I_{DC} = \frac{1}{\pi} * i_{C,Max} \tag{2-19}$$

Writing the fundamental current component ( $I_{CI,Max,B}$ ) in terms of the DC current component ( $I_{DC}$ ) by utilizing Equation (2-19) into Equation (2-18)

$$I_{c1,Max,B} = \frac{\pi}{2} * I_{DC}$$

(2-20)

From Equation (2-20) into Equation (2-17), the optimum power of class-B can be calculated as

$$P_{opt,B} = \frac{1}{2} V_{ce1,Max} I_{c1,Max,B} = \frac{\pi}{4} (V_{DC} - V_{CE,EOS}) I_{DC}$$

(2-21)

The corresponding maximum power efficiency is given by

$$\eta_{Max,B} = \frac{P_L}{P_{DC}} = \frac{\frac{\pi}{4} (V_{DC} - V_{CE,EOS}) I_{DC}}{V_{DC} I_{DC}}$$

(2-22)

where  $P_L$  is the power delivered to the load (in Watts). The  $P_{DC}$  is the consumed DC power (in Watts). Assuming an ideal transistor where  $V_{CE,EOS}$  is very small and approaching a value of zero, then the efficiency for an ideal transistor ( $\eta_{ideal,B}$ ) is given by

$$\eta_{ideal,B} = \frac{\frac{\pi}{4} V_{DC} I_{DC}}{V_{DC} I_{DC}} = 78.5\%$$

(2-23)

which is the typical result of the ideal class-B maximum power efficiency.

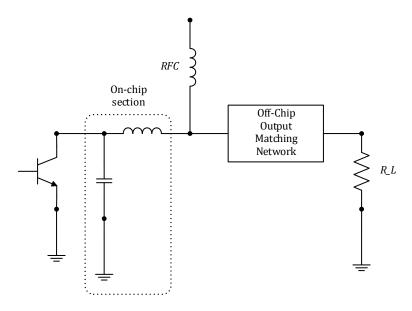

#### 2.2.4 - The Practical Implementation of Class-AB, B, and C Load

The classic reduced conduction angle operation (class-AB, B, and C) requires presenting a short-circuit termination to all harmonics (second harmonic and higher) in order to obtain a sinusoidal voltage waveform of the fundamental frequency at the collector/drain terminal of the transistor. In real power amplifier designs, the short-circuit termination is implemented by adding a large shunt capacitor at the collector terminal while the rest of the matching network presents an inductive reactive component that resonates out the capacitor at the fundamental frequency. The issue of such an implementation is the maximum capacitor value available may not be large enough to present a good short-circuit or at least a very low impedance, especially at the second harmonic which exists with a high level, as shown in Figure 2-4. Such a situation occurs for power amplifiers designed as integrated circuits where the power transistor and the shunt capacitor are implemented on a die.

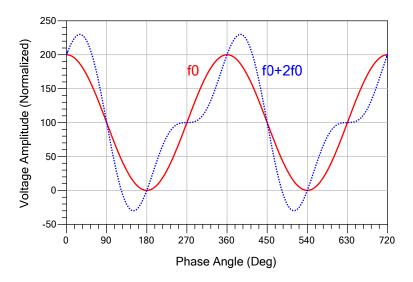

Cripps [10] has introduced a detailed analysis of the effect of presenting a capacitive termination to the second harmonic current component while presenting a pure resistive load at the fundamental frequency. The analysis shows that both the output power and power efficiency degrades. This degradation results from presenting such a combination of terminations to the fundamental and the second harmonic current components causes the second harmonic voltage component to be shifted by  $-\pi/2$  from the fundamental voltage component. The resultant voltage waveform has a higher maxima and a lower minima than a sinusoid of the fundamental frequency, as shown in Figure 2-6.

As the minima of the voltage waveform decreases below the edge of saturation voltage  $(V_{CE,EOS})$ , the collector current becomes a function of both the input and output voltage signals. Hence, the collector current waveform deviates from the pure half-wave sinusoid causing the fundamental current component to decrease. As a result, both of the output power at the fundamental frequency and the power efficiency decrease. It is important to note that such a

voltage waveform causes a degradation in linearity as well, since higher harmonic current components are generated with a higher level and mixed within the transistor.

Figure 2-6 – The resultant voltage waveform of a second harmonic component that is shifted by  $-\pi/2$  from the fundamental component (normalized to ( $V_{DC}$  -  $V_{CE,EOS}$ ), the zero value refers to  $V_{CE,EOS}$ ).

The results of the presented analysis caused many to pursue different techniques to eliminate the second harmonic voltage component, such as adding a second-harmonic trap at the collector terminal (or double second-harmonic traps in broadband designs).

### 2.3 - High Efficiency Utilizing the Generated Harmonics

Advanced techniques of achieving high power efficiency in power amplifiers have been proposed where the generated current harmonics are utilized to engineer the voltage waveform at the collector/drain of the power transistor. The main concept of applying these techniques is to raise the minima of the waveform above the edge of saturation voltage ( $V_{CE,EOS}$ ). This increase of the minima allows an increase in the fundamental voltage component by increasing the load impedance magnitude at the fundamental frequency, and restoring the minima of the voltage waveform back to the edge of saturation voltage. Such an increase of the fundamental voltage component may transfer into an increase in the fundamental output power without increasing the

22

<sup>&</sup>lt;sup>8</sup> - The  $V_{DC}$  is the DC supply voltage. The  $V_{CE,EOS}$  is the edge of saturation voltage.

consumed DC power, since the bias point has not been changed. As a result, both the power efficiency and the power gain may increase.

The techniques which utilize the generated harmonics rely on biasing the power transistor around the deep class-AB (ideal class-B) where the collector current takes the form of a truncated sinusoid (almost a half-wave sinusoid). Such a current waveform contains a high level of the second harmonic component. Though the third harmonic does not exist in the ideal class-B, as the bias point moves away from the ideal class-B a moderate level of the third harmonic component appears. Hence, the harmonic current components that can be utilized are mainly the second and third harmonics. Higher harmonic components have a much lower level which make them difficult to use. The technique utilizing the third harmonic component is known as class-F, Raab [4], while the technique utilizing the second harmonic component is known as class-J, Cripps, et al. [5].

A major difference exists between the harmonic terminations used for the classic reduced conduction angle operation (class-AB, B, and C) and the harmonic terminations used for class-F or class-J operation. As discussed in Section 2.2.2, the effective application of the classic reduced conduction angle operation requires presenting a short-circuit termination to all harmonic current components (second harmonic and above) to obtain a sinusoidal collector voltage waveform at the fundamental frequency. But, in order to utilize the second harmonic component (class-J) or the third harmonic component (class-F), specific harmonic terminations are required in each case. Presenting specific terminations to the generated harmonic current components shapes the voltage waveform as needed, and causes the waveform to deviate from the typical sinusoid obtained in the classic reduced conduction angle operation.

It should be noted that utilizing the generated harmonics is carried out at the collector/drain terminal of the power transistor while the rest of the output matching network of the power amplifier is required to reject the generated harmonics in order to meet emission specifications.

### 2.3.1 - The Real Power of Periodic Signals

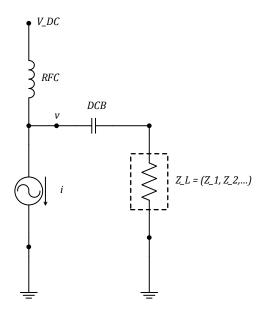

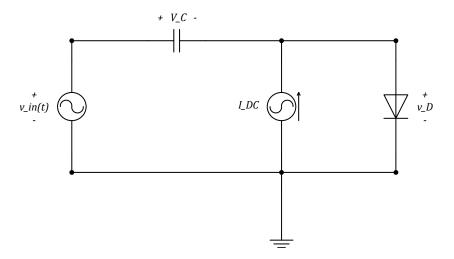

Utilizing the generated harmonics to enhance the power efficiency mandates operating the amplifier with both the collector current and voltage containing harmonic components. Figure 2-7 shows a circuit diagram containing a current source representing the voltage-controlled current source of a transistor and a general load impedance presented at the collector/drain terminal of the transistor. The circuit also shows the RF choke and the DC block required for a proper operation.

Figure 2-7 – A circuit shows the current and voltage signals at the collector/drain terminal of a transistor.

Assuming a general case where the collector current is a periodic signal that contains all harmonic components. The collector current signal can be written as

$$i = I_{DC} + \sum_{k=1}^{\infty} I_k \cos(k\omega_0 t - \theta_{i,k})$$

(2-24)

where  $I_{DC}$  is the DC current. The  $I_k$  is the amplitude of the  $k^{th}$  harmonic. The  $\omega_0$  is the angular fundamental frequency. The  $\theta_{i,k}$  is the phase angle of the  $k^{th}$  harmonic current component. Assuming that a general load is presented to the transistor at the collector terminal such that a periodic voltage signal is created which contains all harmonic components. The collector voltage signal can be written as

$$v = V_{DC} + \sum_{k=1}^{\infty} V_k \cos(k\omega_0 t - \theta_{v,k})$$

(2-25)

where  $V_{DC}$  is the DC voltage. The  $V_k$  is the amplitude of the  $k^{th}$  harmonic. The  $\theta_{v,k}$  is the phase angle of the  $k^{th}$  harmonic voltage component.

The real power at the collector terminal (P) is calculated by

$$P = \frac{1}{T} \int_{T} v \ i \ dt \tag{2-26}$$

Substituting from Equations (2-24) and (2-25) into Equation (2-26) while applying the following trigonometric features

$$\cos(\alpha)\cos(\beta) = \frac{1}{2}\cos(\alpha - \beta) + \frac{1}{2}\cos(\alpha + \beta)$$

(2-27)

$$\int_{T} \cos(m\omega_0 t) dt = 0$$

(2-28)

$$\int_{T} \cos(m\omega_0 t) \cos(n\omega_0 t) dt = 0 , \text{for } m \neq n$$

(2-29)

Then, the real power at the collector terminal is calculated by

$$P = V_{DC}I_{DC} + \sum_{k=1}^{\infty} \frac{V_k I_k}{2} \cos(\theta_{v,k} - \theta_{i,k})$$

(2-30)

This power is the power dissipated in the device. Equation (2-30) shows that the real power is the superposition of the individual real power terms due to the voltage and current of each frequency component (DC, fundamental, and harmonics). The equation also shows that there is no interaction among the voltage and current of different frequency components.

Aiming at achieving the maximum power efficiency of the power amplifier, it is necessary to transfer the power from the DC component to the fundamental frequency component only. Any real power appearing at any of the harmonics (at the collector terminal) is required to be suppressed by the rest of the output matching network in order to meet emission specifications.

Presenting a pure reactive termination to the  $k^{th}$  harmonic current component causes the phase difference between the voltage and current signals of the  $k^{th}$  frequency to equal  $\pm \pi/2$ . From Equation (2-30), such a phase difference forces the real power of the  $k^{th}$  frequency to equal zero. Hence, it is essential to apply a pure reactive termination at each of the harmonics that are utilized in enhancing the efficiency, while presenting a short-circuit termination to all other harmonics. As

a result, the only frequency component, other than the DC component, that contributes to the real power at the collector terminal is the fundamental frequency.

It should be noted that in such a case, a reactive power of the  $k^{th}$  frequency component is trapped within the circuit. But, the benefit of utilizing the generated harmonics and allowing the real power at the fundamental frequency to increase, far exceeds the effect of the power trapped within the circuit.

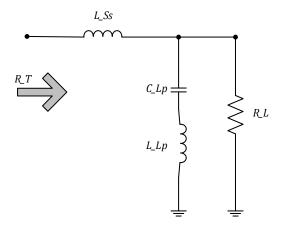

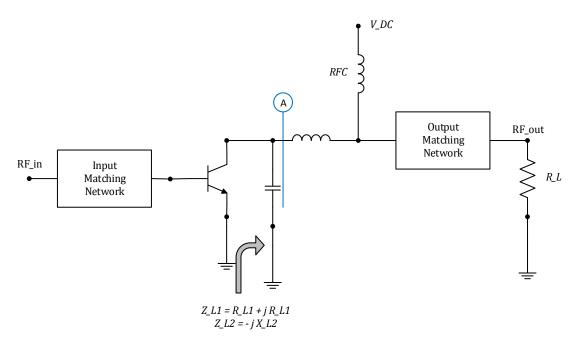

#### 2.3.2 - Class-J Operation

Cripps [10] has introduced class-J operation where it was defined to use an output matching network presenting a capacitive harmonic termination and a combination of resistive and inductive load at the fundamental frequency at the collector/drain terminal of the transistor. Class-J was proposed as a method to obtain the same or higher power efficiency than what is typically offered by an ideal class-B, while avoiding the need for a short-circuit termination to all higher harmonics.

As discussed in Section 2.2.4, the classic reduced conduction angle operation (class-AB, B, and C) requires presenting a short-circuit termination to all harmonics. As the second harmonic termination deviates from the ideal short-circuit, both the output power and the power efficiency degrade. The results of the presented analysis in Section 2.2.4 may give a false expectation that the existence of the second harmonic voltage component at the collector terminal has a damaging effect on the performance of the power amplifier, in general.

Multiple investigations have been presented where the second harmonic component is utilized to improve the power efficiency. [Colantonio, et al. [26], 27] have proposed achieving high efficiency by manipulating the second harmonic voltage component at the output terminal of the transistor. The proposed technique utilizes the nonlinear input impedance of the transistor to obtain a second harmonic voltage component with the needed phase at the output terminal. Therefore, it is important to note that the phase of the second harmonic voltage component with respect to the fundamental voltage component is the key to achieve high power efficiency.

Cripps, et al. [5] have presented the general theoretical form of class-J operation where the collector/drain voltage waveform is defined in terms of the DC, fundamental, and other harmonic components (mainly the second and third harmonics). Wright, et al. [28] have demonstrated the effectiveness of class-J by applying the appropriate fundamental, second and third harmonic terminations to the transistor, where they were determined using an active load-pull system.

The ideal case of class-J, where only the second harmonic is utilized and all other higher harmonics are terminated with short-circuit, is more suitable to handset power amplifiers. The reason for this suitability is a shunt capacitor can be easily added at the collector of the transistor to provide the needed termination for the second harmonic current component while presenting a very low impedance (almost short-circuit) to the third and higher harmonic current components.

#### 2.3.2.1 - The Concept of Class-J by Utilizing the Second Harmonic