Abstract

## Certifying Virtual Memory Manager Using Multiple Abstraction Levels

Alexander Leo Vaynberg

#### 2013

Abstraction is the main tool that makes the creation of complex software systems tractable. However, software verification using the Hoare-logic approach has only a few methods in its arsenal to make use of abstraction, with separation logic being the most popular. Combined with recursive predicates, separation logic can be used for defining abstract data types (ADTs) and information hiding in verification. But there are limits to its application: separation logic cannot be used to define abstractions that rely on the alteration of operational semantics of primitive operations. One example of such abstraction is virtual memory: in the concrete model, any memory access goes through address translation, but in abstract model, memory accesses operate on a virtual data store that hides a particular address translation. Other examples of non-ADT abstractions include compilation, transactions, and time-sharing. Currently, these abstractions can not be implemented by current Hoare-logic verification techniques.

In our thesis, we present an alternative approach to handling abstraction in software verification that allows us to define the abstractions not expressible in separation logic. Instead of using a single machine model and a complex logic for verification, our new software verification framework makes use of multiple machine models and common static semantics expressed in simple logic. For every module of a complex software system, our framework enables us to define a new machine model with the abstract primitives natural for that module, thereby simplifying the verification of code. These machine models are then connected to each other by abstraction relations, from which our framework generates the refinements. Using these refinements, we link the modules verified at different levels of abstraction. The final result is that though we define and specify software modules at their natural levels of abstraction, we still get the proof that all modules linked together are sound with respect to the most concrete machine model. In other words, our framework merges the techniques of abstract machines and refinement with Hoare-logic style verification. To show that this approach is effective, we have used our framework to deal with the virtual address space abstraction. For a large portion of the OS kernel, the abstract address space model is more natural than the concrete address translation model, making it preferable to certify the kernel using address space primitives. However, the virtual memory manager, a complicated and error-prone part of the OS, relies on the address translation primitives to operate, and therefore can only be verified using the concrete model. Instead of using the address translation model to verify the entire kernel, which would make the verification more complicated, we use our framework to link the virtual memory manager and the rest of the kernel, both verified in their natural models. The verified linking guarantees that the entire kernel will execute correctly on the machine with address translation. Using Coq Proof Assistant, we have machine-checked the proofs of both the framework and the certification of address space abstraction to ensure correctness.

The work presented in the thesis raises the state-of-art in the field of formal software verification frameworks. Our framework is both entirely language independent and can handle self-modifying code without relying on separation logic. However, in our opinion, the main contribution of this work lies in modularity and reusability of certified code. Software verification tends to be all-ornothing deal. To be reused in a different context verified modules require new specifications, and thus new proofs. Our framework enables their refinement into the new context without re-proving them. It is our hope that our work will spur the development of reusable certified libraries and creation of ever larger certified software systems.

# Certifying Virtual Memory Manager Using Multiple Abstraction Levels

A Dissertation Presented to the Faculty of the Graduate School of Yale University in Candidacy for the Degree of Doctor of Philosophy

> by Alexander Leo Vaynberg

Dissertation Director: Zhong Shao

May 2013

Copyright © 2013 by Alexander Leo Vaynberg All rights reserved.

## Contents

| 1 | Intro | oduction                                                     | 1  |

|---|-------|--------------------------------------------------------------|----|

|   | 1.1   | Contributions                                                | 6  |

|   | 1.2   | Thesis Outline                                               | 8  |

| 2 | Over  | rview                                                        | 9  |

|   | 2.1   | Multi-Machine Verification of the Virtual Memory Manager     | 12 |

|   | 2.2   | The Framework for Multi-Layer Verification                   | 17 |

|   | 2.3   | Refinement within the Framework                              | 20 |

|   |       | 2.3.1 Code-Preserving Refinements                            | 21 |

|   |       | 2.3.2 Generating Refinements from Relations of Machine State | 23 |

|   |       | 2.3.3 Other Refinements                                      | 24 |

|   | 2.4   | Conclusion of Overview                                       | 25 |

| 3 | The   | Verification Framework                                       | 27 |

|   | 3.1   | General Machine Definitions and Actions                      | 27 |

|   |       | 3.1.1 The Language of Actions                                | 28 |

|   |       | 3.1.2 Alternative Definition of Actions                      | 32 |

|   | 3.2   | Meta-language                                                | 34 |

|   |       | 3.2.1 Meta-Language Syntax                                   | 34 |

|   | 3.3   | Static Semantics of the Meta-Language                        | 36 |

|   |       | 3.3.1 Automatic Generation of Strongest Specification        | 37 |

|   | 3.4   | Safety and Partial Correctness                               | 39 |

|   | 3.5   | Notation for Writing Down Actions                            | 41 |

|   | 3.6  | Examp    | bles of Machine Definitions and Verification  | 43  |

|---|------|----------|-----------------------------------------------|-----|

|   |      | 3.6.1    | MIPS with a Fixed Code Heap                   | 43  |

|   |      | 3.6.2    | MIPS with Self-Modifying Code                 | 50  |

|   |      | 3.6.3    | Simple Imperative Machine                     | 54  |

|   |      | 3.6.4    | Other Machines and Languages                  | 56  |

|   |      | 3.6.5    | Adequacy                                      | 57  |

|   | 3.7  | Certifi  | ed Modules and Linking                        | 59  |

| 4 | Cros | ss-Absti | raction Linking                               | 65  |

|   | 4.1  | Linkin   | g Across Abstractions                         | 65  |

|   | 4.2  | Refine   | ment Generation                               | 67  |

|   |      | 4.2.1    | Per-Procedure Refinement                      | 67  |

|   |      | 4.2.2    | Order-Preserving Refinement                   | 70  |

|   |      | 4.2.3    | Code-Preserving Refinement                    | 74  |

|   |      | 4.2.4    | Using Functions for Action Refinement         | 75  |

|   |      | 4.2.5    | The Usefulness of Code-Preserving Refinements | 76  |

|   | 4.3  | Specia   | lized Refinements                             | 76  |

|   |      | 4.3.1    | Embedding Refinement                          | 76  |

|   |      | 4.3.2    | Representation Refinement                     | 78  |

|   | 4.4  | Other ]  | Refinements                                   | 84  |

| 5 | Veri | fication | of the Virtual Memory Manager                 | 85  |

|   | 5.1  | The Pu   | rpose of the Virtual Memory Manager           | 86  |

|   | 5.2  | The Co   | ode of a Virtual Memory Manager               | 88  |

|   | 5.3  | Forma    | lized C language                              | 93  |

|   |      | 5.3.1    | The C-Machine Stack Definition                | 95  |

|   |      | 5.3.2    | The Memory Model                              | 96  |

|   |      | 5.3.3    | The Semantics of Meta-C                       | 97  |

|   |      | 5.3.4    | The Hardware Memory Model                     | 99  |

|   |      | 5.3.5    | Dealing with Special Memory Features          | 101 |

|   |      | 5.3.6    | Address Space Memory Model                    | 102 |

|     | 5.3.7    | Converting from C to Meta-C                           | 104 |

|-----|----------|-------------------------------------------------------|-----|

| 5.4 | Verific  | cation Plan                                           | 105 |

|     | 5.4.1    | The Two-Machine Approach                              | 107 |

|     | 5.4.2    | The 7-layer Certification Cake                        | 109 |

|     | 5.4.3    | Address Translation Restriction                       | 109 |

|     | 5.4.4    | The Allocated Memory Model (with Address Translation) | 112 |

|     | 5.4.5    | The Page Map Model                                    | 114 |

|     | 5.4.6    | Hardware with AT off                                  | 117 |

|     | 5.4.7    | The Non-Address Translated Allocated Memory           | 119 |

| 5.5 | Verific  | cation of Code                                        | 119 |

|     | 5.5.1    | Verification of the Memory Allocator                  | 119 |

|     | 5.5.2    | Verification of the Page Table Driver                 | 121 |

|     | 5.5.3    | Verification of the Address Space API                 | 122 |

|     | 5.5.4    | Verification of Allocator Initialization              | 123 |

|     | 5.5.5    | Verification of Page Table Initialization             | 125 |

|     | 5.5.6    | Recap of Verification                                 | 126 |

| 5.6 | Refine   | ments                                                 | 127 |

|     | 5.6.1    | Intuition About Refinements                           | 130 |

|     | 5.6.2    | AS-PMAP                                               | 132 |

|     | 5.6.3    | PMAP-ALE                                              | 135 |

|     | 5.6.4    | ALE-PE                                                | 138 |

|     | 5.6.5    | PE-HW                                                 | 140 |

|     | 5.6.6    | ALD-PD                                                | 142 |

|     | 5.6.7    | PD-HW                                                 | 143 |

| 5.7 | Initiali | zation                                                | 145 |

|     | 5.7.1    | Calling kernel-init                                   | 149 |

|     | 5.7.2    | Certifying init                                       | 150 |

| 5.8 | Putting  | g Everything Together                                 | 151 |

| 6 | Tow  | ards Re | alism                                                       | 155 |

|---|------|---------|-------------------------------------------------------------|-----|

|   | 6.1  | Transla | ation Look-aside Buffer                                     | 155 |

|   | 6.2  | Alloca  | table Page Tables                                           | 161 |

|   |      | 6.2.1   | Pushing PTROOT Register Higher                              | 162 |

|   |      | 6.2.2   | Bulk Allocation                                             | 166 |

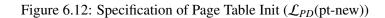

|   |      | 6.2.3   | Dynamic Initialization of Page Tables                       | 168 |

|   |      | 6.2.4   | Recapping Dynamically Allocated Page Tables                 | 171 |

|   | 6.3  | Multip  | le Address Spaces                                           | 171 |

|   |      | 6.3.1   | New Page Table Functions                                    | 172 |

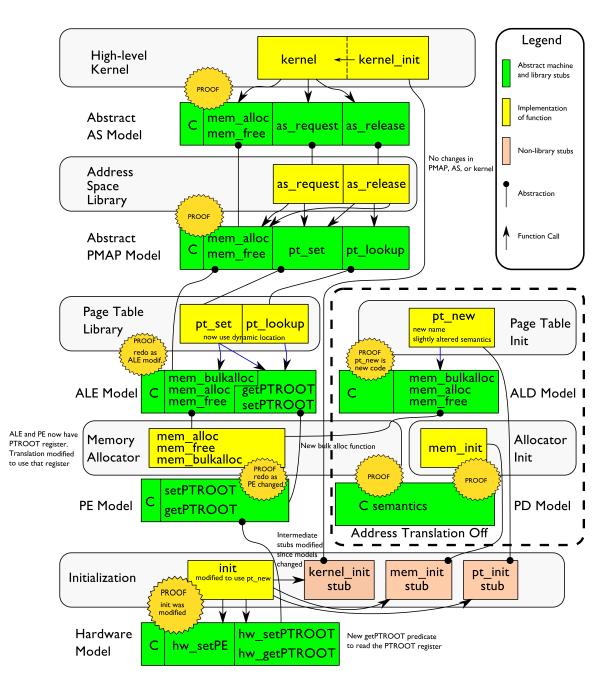

|   |      | 6.3.2   | Multiple Page Map Memory Model                              | 173 |

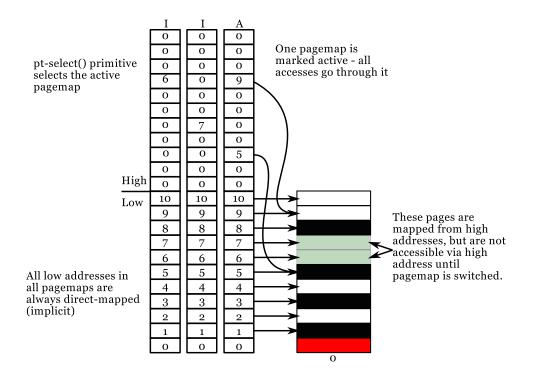

|   |      | 6.3.3   | Multiple Address Space Model                                | 176 |

|   |      | 6.3.4   | Updated Kernel and Initialization                           | 180 |

|   |      | 6.3.5   | Recap of the Relation between Memory Models of Multi-AS VMM | 181 |

|   | 6.4  | Multi-  | level Page Tables                                           | 182 |

|   |      | 6.4.1   | Verification of Multi-Level Page Table Driver               | 186 |

|   |      | 6.4.2   | Abstracting the Multi-level Page Table driver               | 190 |

|   |      | 6.4.3   | Lessons about Updating the Semantics of Low-Level Models    | 191 |

| 7 | Coq  | Implen  | nentation                                                   | 193 |

|   | 7.1  | Overvi  | ew of the Implementation                                    | 194 |

|   |      | 7.1.1   | Implementing the Certification System                       | 194 |

|   |      | 7.1.2   | Implementation of the Refinement System                     | 197 |

|   |      | 7.1.3   | Implementation of the Virtual Memory Manager                | 203 |

|   | 7.2  | Design  | Choices and Challenges                                      | 216 |

|   |      | 7.2.1   | The Simplification Problem                                  | 217 |

|   |      | 7.2.2   | The Automation Problem                                      | 218 |

|   |      | 7.2.3   | Simpler Actions                                             | 219 |

| 8 | Rela | ted Wo  | rk and Conclusion                                           | 221 |

|   | 8.1  | Relate  | d Work                                                      | 222 |

|   | 8.2  | Future  | Work                                                        | 225 |

A Proofs of Properties of Actions

# **List of Figures**

| 2.1  | Address Translation                                                 | 9  |

|------|---------------------------------------------------------------------|----|

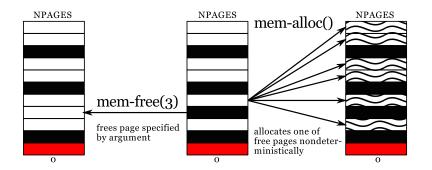

| 2.2  | Example of API of the Virtual Memory Manager                        | 10 |

| 2.3  | Diagram of Kernel Code                                              | 13 |

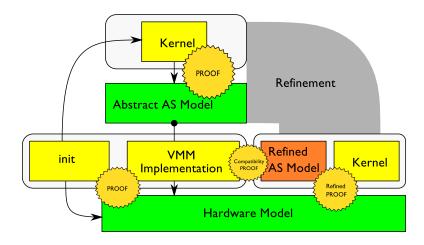

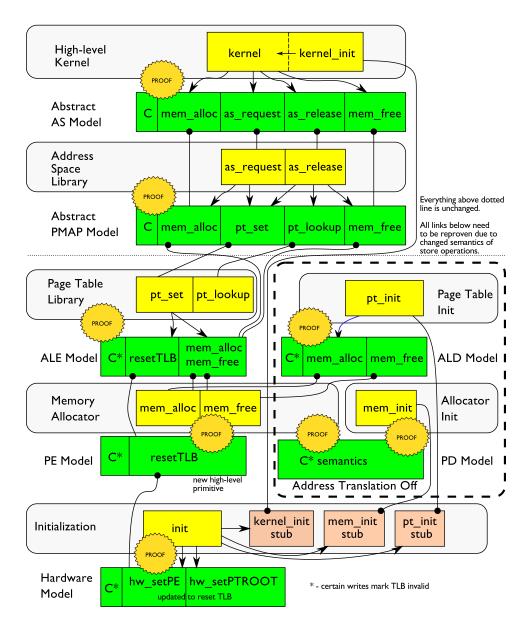

| 2.4  | Multi-Machine Verification of the Kernel                            | 14 |

| 2.5  | The Workings of Refinement                                          | 15 |

| 2.6  | The Workings of Refinement (fixed for upcall)                       | 15 |

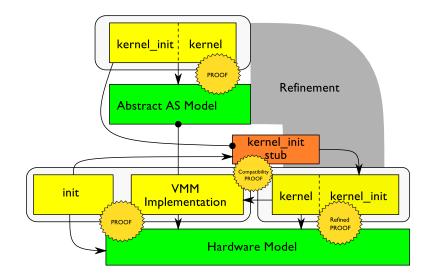

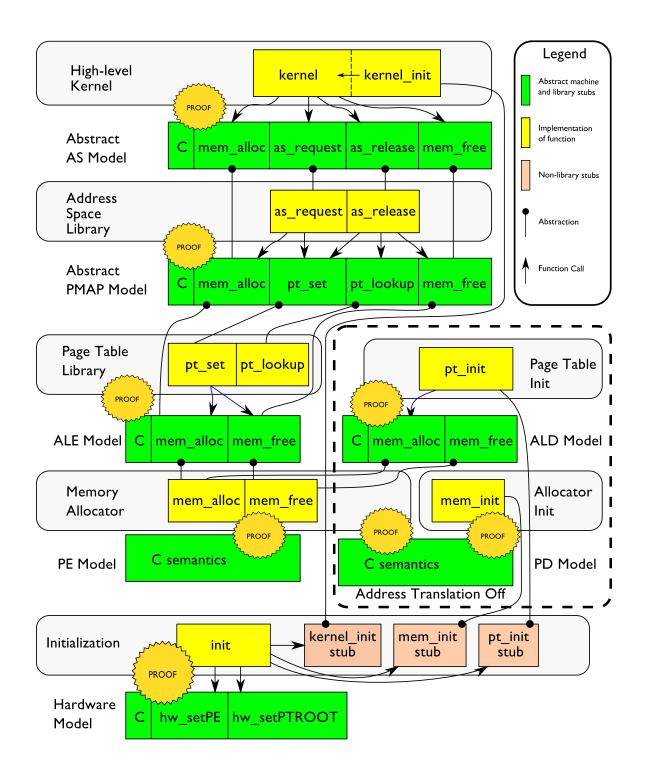

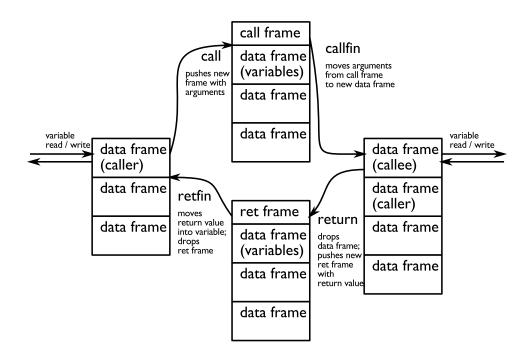

| 2.7  | Complete Plan for VMM Certification                                 | 16 |

| 2.8  | Graphical Representation of an Action                               | 18 |

| 2.9  | Action Concatenation                                                | 18 |

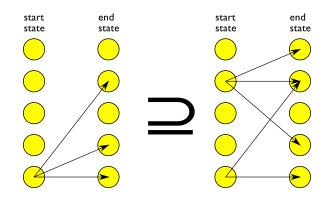

| 2.10 | Definition of Refinement                                            | 20 |

| 2.11 | Code-Preserving Refinement                                          | 21 |

| 2.12 | Relation Between Actions of Machines                                | 22 |

| 2.13 | Action Translation Preserves Weaker-than Relation                   | 22 |

| 2.14 | Action Translation Preserves Weaker-than Relation for Concatenation | 23 |

| 2.15 | Representation-based Specification Translation                      | 24 |

| 3.1  | Abstract State Machine                                              | 27 |

| 3.2  | Combinators and Properties of Actions                               | 30 |

| 3.3  | Properties of Action Combinators                                    | 32 |

| 3.4  | Combinators for (p,r)-style Actions                                 | 33 |

| 3.5  | Syntax and Semantics of the Meta-Language                           | 34 |

| 3.6  | Static Semantics of the Meta-Language                               | 36 |

| 3.7  | Automatic Generation of Strongest Specification                     | 38 |

| 3.8  | MIPS Machine with Fixed Code                                                                | 44 |

|------|---------------------------------------------------------------------------------------------|----|

| 3.9  | MIPS Code of the Fibonacci Function ( $\mathbb{Z}$ )                                        | 46 |

| 3.10 | Automatic Translation of MIPS Code into Meta-language                                       | 46 |

| 3.11 | Fibonacci Function Translated into Meta-language $(\mathbb{C}_{fib})$                       | 47 |

| 3.12 | Specifications for the Fibonacci Procedures                                                 | 47 |

| 3.13 | Automatically Generated Strong Action for Fibonacci Function                                | 48 |

| 3.14 | Alternate Translation of Fibonacci Code and its Spec                                        | 49 |

| 3.15 | MIPS machine                                                                                | 50 |

| 3.16 | Single Instruction Replacement Code                                                         | 51 |

| 3.17 | Single Instruction Replacement Meta-program $(\mathbb{C}_{ir})$                             | 52 |

| 3.18 | Single Instruction Replacement Meta-program (alternate) $(\mathbb{C}_{ira})$                | 52 |

| 3.19 | Automatically Generated Strongest Specification                                             | 53 |

| 3.20 | Single Instruction Replacement Spec $(\Psi_{ir})$                                           | 54 |

| 3.21 | Simple Imperative Language (IMP)                                                            | 55 |

| 3.22 | Conversion of IMP Programs into Meta-programs                                               | 55 |

| 3.23 | Fibonacci written in IMP and converted to $\mathcal{M}_{IMP}$                               | 56 |

| 3.24 | Standard Definition of Operational Semantics of IMP                                         | 58 |

| 3.25 | Code and Spec of the Main Module                                                            | 59 |

| 4.1  | Requirements for Relation of Actions                                                        | 71 |

| 4.2  | Requirements for a Function-Based Code-Preserving Refinement                                | 75 |

| 4.3  | Diagram of repr-refinement of Actions                                                       | 79 |

| 4.4  | $Acc_{\mathbb{I}}$ for Order-Preserving Refinement with Branch Control                      | 82 |

| 51   | Model of Address Translation                                                                | 06 |

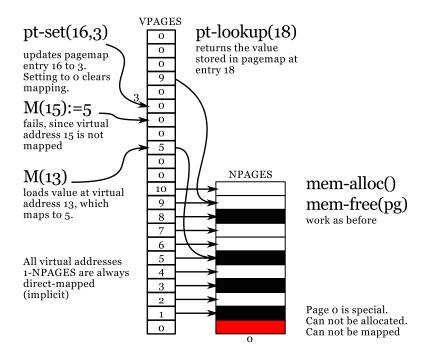

| 5.1  | Model of Address Translation                                                                | 86 |

| 5.2  | Model of Virtual Address Space          Discourse of the Kennel and Witten I Mensure Design | 87 |

| 5.3  | Diagram of the Kernel and Virtual Memory Design                                             | 88 |

| 5.4  | Hardware-Specified Constants and Functions (hw.h)                                           | 89 |

| 5.5  | Code of the Memory Allocator (mem.c)                                                        | 89 |

| 5.6  | Code of the Page Table System                                                               | 90 |

| 5.7  | Code of the Address Spaces (as.c)                                                           | 90 |

| 5.8  | Code of the Initialization (init.c)                                                                                | 90  |

|------|--------------------------------------------------------------------------------------------------------------------|-----|

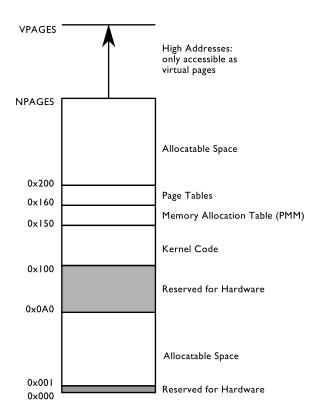

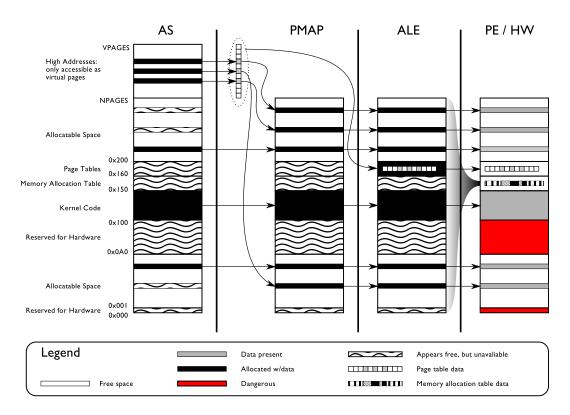

| 5.9  | Memory Map Defined by Virtual Memory Manager                                                                       | 93  |

| 5.10 | Syntax of the C-like language                                                                                      | 94  |

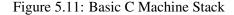

| 5.11 | Basic C Machine Stack                                                                                              | 95  |

| 5.12 | Diagram of Stack Behavior                                                                                          | 96  |

| 5.13 | Signature of the Memory Interface for the C Semantics                                                              | 97  |

| 5.14 | Primitive C-like machine                                                                                           | 98  |

| 5.15 | Page Definitions                                                                                                   | 100 |

| 5.16 | Address Translated Memory Interface $(M_{HW})$ and Stub Library $(\mathcal{L}_{HW})$                               | 100 |

| 5.17 | Address Space Memory Interface $(M_{AS})$ and Library $(\mathcal{L}_{AS})$                                         | 102 |

| 5.18 | Conversion of C into Meta-C                                                                                        | 104 |

| 5.19 | Kernel Abstraction Diagram                                                                                         | 110 |

| 5.20 | C with Paging $(\mathcal{M}_{PE})$ (PE always, fixed PTROOT, no alloc)                                             | 111 |

| 5.21 | Informal Diagram of $\mathcal{M}_{ALE}$                                                                            | 112 |

| 5.22 | Allocated Memory Model Semantics $(M_{ALE})$ and $\text{Library}(\mathcal{L}_{ALE})$                               | 113 |

| 5.23 | Page Map Memory Model                                                                                              | 115 |

| 5.24 | The Pagemap Memory Model $(M_{PMAP})$ and Library $(\mathcal{L}_{PMAP})$                                           | 116 |

| 5.25 | Hardware Machine with AT disabled $(\mathcal{M}_{PD})$                                                             | 118 |

| 5.26 | Allocatable Memory with AT Disabled Model $(\mathcal{M}_{ALD})$ and Its Library $(\mathcal{L}_{ALD})$              | 118 |

| 5.27 | The C-machine procedure of the memory allocator $(\mathbb{C}^{mem})$                                               | 120 |

| 5.28 | The Specification of Memory Allocator in the $\mathcal{M}_{PE}$ machine $(\Psi_{PE}^{mem})$                        | 120 |

| 5.29 | Code of the Page Table Driver $(\mathbb{C}^{pt})$ and Spec $(\Psi_{ALE}^{pt})$                                     | 122 |

| 5.30 | The Procedures of the Address Space API Implementation ( $\mathbb{C}^{as}$ ) and Specs ( $\Psi_{PMAP}^{as}$ )      | 123 |

| 5.31 | Procedures of Memory Initialization ( $\mathbb{C}_{PD}^{meminit}$ ) and Their Specs ( $\Psi_{PD}^{meminit}$ )      | 124 |

| 5.32 | Procedures of Page Table Driver Initialization ( $\mathbb{C}^{ptinit}$ ) and Their Specs ( $\Psi_{ALD}^{ptinit}$ ) | 126 |

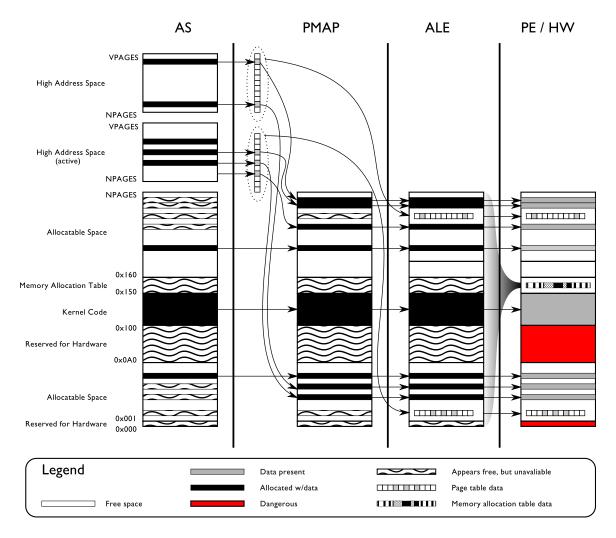

| 5.33 | Diagram of the Relation between Memory Models                                                                      | 131 |

| 5.34 | The repr-relation between AS and PMAP Models $(repr_{AS-PMAP})$                                                    | 132 |

| 5.35 | The repr-relation between PMAP and ALE Models $(repr_{PMAP-ALE})$                                                  | 135 |

| 5.36 | The repr-relation between ALE and PE Models $(repr_{ALE-PE})$                                                      | 138 |

| 5.37 | The repr-relation between PE and HW Models $(repr_{PE-HW})$                                                        | 140 |

| 5.38 | The relation between ALD and PD Memory Models $(M_{ALD} \leq M_{PD})$  | 142 |

|------|------------------------------------------------------------------------|-----|

| 5.39 | The repr-relation between PD and HW Modules $(repr_{PD-HW})$           | 144 |

| 5.40 | init Procedure                                                         | 146 |

| 5.41 | Specification of mem-init for HW Model $(a_{HW}^{mem-init})$           | 146 |

| 5.42 | Specification of pt-init for PD Model $(a_{PD}^{pt-init})$             | 147 |

| 5.43 | Specification of pt-init for HW Model $(a_{HW}^{pt-init})$             | 148 |

| 5.44 | Intermediate Specifications of kernel-init                             | 149 |

| 6.1  | Hardware Memory Model with TLB and Stub Library                        | 156 |

| 6.2  | The Code of pt-set for Hardware with TLB                               | 159 |

| 6.3  | Specs of the Page Table Driver $\Psi_{ALE}^{pt}$ with TLB modification | 159 |

| 6.4  | Plan of Verification on Hardware that Features TLB                     | 160 |

| 6.5  | ALE and PE Memory Models with PTROOT register                          | 163 |

| 6.6  | Updated Specifications of the Memory Manager $(\Psi_{PE}^{mem})$       | 164 |

| 6.7  | Updated Specs of the Memory Manager Stubs $(\mathcal{L}_{ALE})$        | 165 |

| 6.8  | Updated Code of Page Table Driver                                      | 166 |

| 6.9  | Code and Specs of the Multi-Page Allocator                             | 167 |

| 6.10 | Specs for mem-bulkalloc                                                | 168 |

| 6.11 | Code of Page Table Driver and Initialization                           | 169 |

| 6.12 | Specification of Page Table Init ( $\mathcal{L}_{PD}(\text{pt-new})$ ) | 169 |

| 6.13 | Certification Plan for VMM with Dynamically Allocated Pagetables       | 170 |

| 6.14 | Code of the pt-delete function                                         | 172 |

| 6.15 | Specifications of New Page Table Functions $(\Psi_{ALE}^{pt})$         | 173 |

| 6.16 | Multiple Page Map Memory Model Diagram                                 | 174 |

| 6.17 | Multiple Page Map Memory Model                                         | 175 |

| 6.18 | Relation Between MPMAP and ALE Models                                  | 176 |

| 6.19 | Diagram of the MAS Memory Model                                        | 177 |

| 6.20 | Multiple Address Space (MAS) Model and Its Library                     | 178 |

| 6.21 | Relation between MAS and MPMAP models of memory                        | 179 |

| 6.22 | Relation between Memory Models of Multi-AS VMM                         | 181 |

| Predicates for Realistic Address Translation                     | 182                                          |

|------------------------------------------------------------------|----------------------------------------------|

| Multi-Level Page Table Domain Predicate                          | 183                                          |

| Multi-Level Page Table Driver Code (Helper Functions)            | 185                                          |

| Multi-Level Page Table Driver Code                               | 186                                          |

| Abstract Page Table Definition                                   | 187                                          |

| Multi-level Page Table Driver Specification                      | 188                                          |

| Relation Between MPMAP and ALE with Multi-level Pagetable Models | 191                                          |

| Listing of refinement.v                                          | 198                                          |

|                                                                  | Predicates for Realistic Address Translation |

## Acknowledgements

I would like to thank my advisor Zhong Shao for his guidance throughout my graduate career. He has always pushed me to get actual results and has never let me get away with imprecision and speculation. This work would never be as detailed and as rigorous without his assistance.

I would like to thank my thesis readers, Bryan Ford, Paul Hudak, and Xinyu Feng for reading my dissertation and providing thoughtful comments. I am also grateful to the anonymous reviewers of my submitted papers for their comments that improved my work.

I am indebted to Xinyu Feng, Hongxu Cai, and Wei Wang for helping me find the direction in my research. I also owe many thanks to Rodrigo Ferreira, Antonis Stampoulis, and other members of FLINT research team for numerous informative conversations. They have never refused any request for help, and have always set an example for me and my work.

This dissertation is dedicated to my parents, Leo and Natalya, and to my wife Olga. They have always given me their support and encouragement, enabling me to do my best.

This research is based on work supported in part by DARPA grants FA8750-10-2-0254 and FA8750-12-2-0293, ONR grant N000141210478, and NSF grants 0910670 and 1065451. Any opinions, findings, and conclusions contained in this document are those of the authors and do not reflect the views of these agencies.

### Chapter 1

### Introduction

Writing software is a complex engineering task, in many ways more difficult than other forms of engineering, as the number of ways software can fail is not limited to several well-known modes of failure. Even the smallest error can lead to catastrophic results such as complete failure of USS Yorktown[45]. Failure to account for all possibilities can result in software being exploited[11, 30]. Testing software is a way to reduce the number of such errors, but it can not eliminate them completely.

For these reasons, the field of software certification evolved, taking several related paths including type theory, model-checking, and Hoare-logic[20]. Although all of those approaches are related, the research presented in this thesis is closer to the Hoare-logic approaches. The idea behind Hoare logic is that for any programming language or a machine, we can construct a model of it. This model allows to formally analyze any program running on the machine. The analysis allows us to formally show that a program has a specific behavior (called a specification) that it is logically guaranteed to follow. This approach to reasoning about the programs has yielded several frameworks for analyzing program safety and correctness such as proof-carrying code[34, 33, 3] and certified software[48, 13, 35], the latter actually being closer to the spirit of the original Hoare-logic, aiming at reduction of the number of axioms and at the simplification of the correctness proofs. The prior research on certified software has followed the ideas of foundational PCC, and has constructed frameworks for verification of real programs running on real computers, mostly focusing on the semantics of assembly languages[48, 14, 6]. Using these frameworks, our group can, at least in theory, certify all kinds of software.

However, formal certification of software using our approach is done with great difficulty, and usually on small examples. Our colleagues, using slightly different approaches, have verified larger amounts of code, but not without spending a lot more effort, while still having problems of their own. The most famous verification project, L4.verified [10, 47, 23], has managed to verify a microkernel[27] using a top down approach, where the kernel is first defined with high-level specifications, and then these specifications are refined down to more precise logical objects, which are then proven to correspond to actual data structures maintained by the code. Their approach relies on parts of their implementation, such as memory allocator and initialization, to be trusted. They have also avoided abstracting some of the complicated features of the OS, such as virtual memory, passing these towards the user programs to handle safely. The Verisoft project[40, 1] has also verified a large portion of the kernel. Their approach involves defining a machine that represents the instruction set architecture, and a machine that represents the high-level semantics from the point of view of the user program. The verification of the kernel is a large proof that the semantics of the high-level machine are correctly simulated by the underlying machine and the microkernel running on top of it. This proof has taken many years of work to develop. Our worry about their method is that, unless they have taken great care in constructing their proof, their proof may be brittle. There is no formal definition of modularity within their microkernel, and thus a change in one definition may cause changes throughout the entire simulation proof.

Although formal software certification is already useable, its use has not gained traction outside the closely-knit research community. Real-world programmers consider complete formal certification to be too difficult, not worth the cost, and therefore impractical. Although formal verification will never be as simple as mind-checking, since explicitly writing down specifications and proofs takes more work than quick consideration, if the verification became easier and more natural, the benefits would begin to outweigh the costs, and more programmers will start verifying their software.

There are several reasons why formal verification is too hard. First, the current state of formal verification forces the programmer to think about the program in a way that does not correspond to the programmer's own understanding of the program, as the formal model of the behavior of the language may not correspond to how the programmer imagines it. Second, there is a danger that verification proofs are not fully modular or reusable. It is extremely frustrating to have to re-

work verification proofs for some module just because of a small change in another module that alters some global invariant that should have been abstracted away. And third, the programmers rely on already crafted and debugged libraries when building their programs, which greatly speeds up their development. However, there are no such reusable libraries of verified code, meaning that programmers have to do verification from scratch.

All these problems are especially visible when verifying systems software, such as operating system kernels. As they have large codebases, they are written as a set of fairly independent modules, carefully separated, each considered at a separate layer of abstraction, so that it can be understood by a person. It is impossible for any person to keep track of all the invariants present in a modern kernel. Thus if there is any hope of verifying a complete kernel, then the verification itself must be modular and reusable, so that all modifications can be isolated and contained, and not create the need to re-verify everything.

What makes the abstraction in OS kernels particularly challenging is the fact that many abstractions modify the way that the kernel seems to operate - that is they seemingly alter the operational semantics of the machine. Examples of such abstractions include time-sharing, interrupt handling, and virtual memory, just to name a few. In this thesis, we focus on the problem of virtual memory abstraction.

As the OS kernel is written in C, it is natural to think that the programmer uses a C model of computation to reason about the programs. This is true, but not completely. The C model of computation does not have a single definition of how the memory is accessed. As we are dealing with OS kernels, we should assume that the memory works as hardware defines it. This means that every memory access may go through a complicated process called address translation, where an address is broken into parts, and each part as an index into page tables, which are program-controlled data tables that define how the address is translated. However, this is not how much of the kernel is reasoned about. The address translation system of the hardware is very detailed, and only a small portion of the kernel, namely the virtual memory manager, will deal with all the details of the address translation. That portion of the kernel will then provide a less-detailed and more intuitive interface to the rest of the kernel, called the address space model. The address space model hides away all the complicated address translation, instead presenting the memory as though it was a single store indexed by the virtual addresses. The programmer can then forget about the

details of address translation, and only consider the memory accesses. Thus, reasoning about the software using the address space model is not only much simpler than trying to reason about address translation, but also is independent of the hardware-dependent address translation mechanism. Thus the abstract model of memory makes reasoning more machine-independent and modular.

What this means is that the programmer reasons with the address translation model when thinking about the virtual memory manager, and the address space model when thinking about the other parts of the kernel. This presents a problem for PCC approaches, as they are defined only for one machine model. If we try to verify the kernel on the machine model that uses address spaces - then we can not certify the virtual memory manager module. If the model is address translation, then everything but VMM becomes harder to certify.

To combat similar problems, quite a bit research focused on making PCC be expressive enough to allow some abstraction within the confines of a single machine model, by using advanced approaches involving separation logic[41] and frame rules[38] to define high-level views of the machine model, such as first-class abstract data types[39]. Separation logic allows for a huge improvement in ability to reason modularly and abstractly, but it does have its limits. Its main power lies in its ability to reason about the state of the model fragmented into separate and disjoint pieces without having the need to know where each piece belongs. This approach essentially defines a model where a sub-state (a partial state) is also a valid state. The frame rule shows that a program valid under a strong specification (one that uses a very small partial state) is also valid with a larger state.

Unfortunately, separation logic is not adequate in this case - it can not be used to define the virtual address space abstraction. A more powerful, and more complex Mapped Separation Logic[24] can express some of the high-level properties of virtual memory, as it defines a separation over mappings. However, this is a specialized solution for reasoning over heaps with virtual addresses. It does not allow one to reason about the code that updates the hardware-specific address translation tables, as these can not be linked to the mappings on which the logic relies. Nor can it be used to reason about the initialization of virtual memory, when no such mappings are present.

We do not want to dismiss or belittle separation logic, and, in fact, we think it is great. However, we do want to bring attention to the fact that it does not give us an ability to perform the kinds of abstraction needed. Neither is it completely natural to use - it forces the machine model into a special form where it can be described as pieces, which might not be a natural way to think about the behavior of the machine, and thus it will require more effort from the programmer to formalize his reasoning.

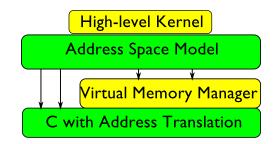

In this thesis, we develop a new framework for certifying code that allows the use complex abstractions. The new framework works by allowing the creation of separate machine models for each code module, each machine model providing the appropriate level of abstraction to make the certification of the code module simple. The framework also includes a method by which the machine models can be related. The related machine models automatically define a refinement rule by which the certified modules can be safely linked across the abstraction boundary, resulting in a proof of soundness of the entire software system.

For the example of virtual memory, we could define two machine models: the address translation model to verify the VMM, and the address space model to verify the rest of the kernel. Then our framework would help us define a refinement that will convert the abstract certification of the high-level kernel into the certification of that same code over the address translation model. Furthermore, our framework will allow us to conclude that the high-level kernel will safely link with the certified VMM code.

Currently the field of formal software verification does not have a formal framework for verifying software using multiple abstract machine models. One of our own lines of work, OCAP[12], has created a way to reason about separate modules using separate logics. For example, one module can be certified using typed assembly language[32, 31], the other using XCAP[36], and it is possible to show that the two will work together. However, this work does not allow different machine models, but only different logics that analyze code using the same machine model.

There are several works that use multiple machine models in verification of the software. However, these machine models were defined and linked in an ad-hoc way, no general framework for doing this is explored or defined. One of these works is a certified garbage collector by McCreight *et al.*[29] Although its approaches have served as an inspiration for this thesis, the work itself is limited; the two machines used in the certification of the GC use the same operational semantics only the state is abstracted. The proofs used apply only to the particular code and machine models, making the approach not reusable for other certified software. It also can not handle calls from the concrete layer into the abstract layer, meaning that it can not handle initialization, which is an important and tricky component of the software. The other example of multi-machine verification is the already mentioned Verisoft project, which links its machine models using a simulation argument. It also does not try to establish a general approach to multi-model verification, and is limited to proving linkages between the particular models used in the project.

In our thesis, we will show that our multi-machine verification framework is an improvement on the ad-hoc examples above. First, it makes the definition of machine models a faster task by allowing machine templates, and by providing common static semantics that are sound for all machines. Second, the framework provides a way to link code certified using multiple machine models in a simpler way, with smaller proof obligations than are needed by ad-hoc approaches. Third, unlike other software certification projects that make use of multi-machine verification, our framework allows for general use of upcalls, e.g. when a module certified using a more concrete machine makes calls into the more abstract module. The upcalls allow us to cleanly reason about initialization code, without the need for special cases in the relations between machines.

This new verification framework forms the first half of this thesis. The second half is devoted to applying this framework to completely verify a small virtual memory manager using multiple abstract machines, showing that our approach is effective at simplifying the verification of code that is difficult to handle traditional certification approaches. It also hints at how our framework can be used to verify other complex problems present in OS kernel verification.

#### **1.1 Contributions**

In this thesis, we have developed a new approach to software verification by allowing the complicated software to be verified not only in a modular fashion, but also in a way that each module of software can be verified using its own abstract view of the world. More specifically we have made the following contributions to the field of software verification.

1. We have developed a new framework for verification of software. This framework is novel in that it is completely machine-independent. This means that it can be instantiated with a model of any machine that works as a state-transition system, and the framework will provide a way to create specifications to the software for these machines, and to provide a way to check that the software does indeed conform to these specifications. The framework is proven sound and guarantees partial correctness (can be extended to total correctness) for any machine

definition.

- 2. The framework is an improvement over its predecessors, SCAP[15] and GCAP[6]. It supports both stack-based control workflow and self-modifying code, without requiring complex data structures and predicates to keep track of stack and code modification.

- 3. The definition of operational semantics in our framework does not use inductive definitions, but instead is a data structure presented as a mapping from operations to specifications. This means that a machine definition can be manipulated. In our example with kernels, there are two C machines, each with its own memory model. Because the machine definition is a data structure we can define our C machine parametric over the memory model, and thus quickly generate C machines, reusing many definitions.

- 4. Our framework provides a formal definition of the refinement between machines. Because the verification system is the same for all machines, we can create various useful refinements from just a few properties about the machines. For example, we have shown that a representation refinement (seen in work on certified garbage collection) is one of refinements definable in our system. We have also extended the representation refinement with invariants. Such addition allows us to use the refinement for frame rules and information hiding, which until now required the use of separation logic.

- 5. We have applied our framework to verify a virtual memory manager. We have shown how to split the VMM into multiple modules, verify each one in its own natural level of abstraction, and then link them together into one completely verified code. We have also shown that any kernel verified over the abstract address space model will correctly link with our virtual memory, guaranteeing safety over the actual model of C with address translated model of memory. This result is one of the first real verification results toward the verification of CertiKOS[17], a secure hypervisor kernel.

- 6. We have formalized our entire framework, including refinements, in Coq proof assistant. This allows us to have confidence in the soundness and correctness of our framework.

#### 1.2 Thesis Outline

The rest of this thesis will be structured as follows. In Chapter 2, we will give a non-technical overview of our framework and how it can be used. Then, we will proceed with a full technical presentation of the precise definition of abstract machine, and how the verification framework uses them in Chapter 3. Chapter 4 is devoted entirely to linking and refinements. This is where we give a technical definition of what a refinement is, as well as define automatic ways of creating these refinements. Here we also try to argue that refinements are both simple and powerful enough to be used in place of separation logic. Then, in Chapter 5, we move away from the theoretical contributions, and instead focus on the certification of a small virtual memory manager designed for simplified hardware. We show how we can extend the certification of the virtual memory manager to be more realistic and practical in Chapter 6. Chapter 7 is the guide to the Coq implementation of the framework and the verification of the VMM. Then we give a quick overview of related works and conclude in Chapter 8.

### **Chapter 2**

### Overview

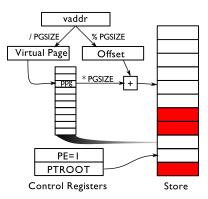

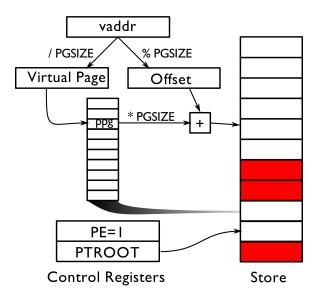

One of the most important features of the hardware is that it provides a mechanism of address translation. This feature allows the operating systems to have an indirect addressing scheme for its data, which in turn enables the kernel to provide memory protection as well as various other features. A simplified example of such address translation mechanism is shown in Figure 2.1. This model of the hardware (and its more realistic counterparts) use a portion of the memory, selected by control registers, to keep an address translation table. When address translation is turned on, all memory accesses, e.g. load and stores, are defined in terms of virtual addresses, which the hardware translates to physical addresses before carrying out the operation.

This somewhat complicated model is designed with two goals in mind: to be easy to implement in hardware, and to be as general as possible, so that software is unrestricted by the design choices of the hardware. The downside of this model is that it pushes the complexity to the software,

Figure 2.1: Address Translation

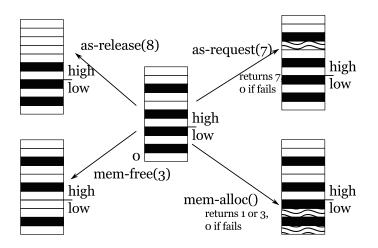

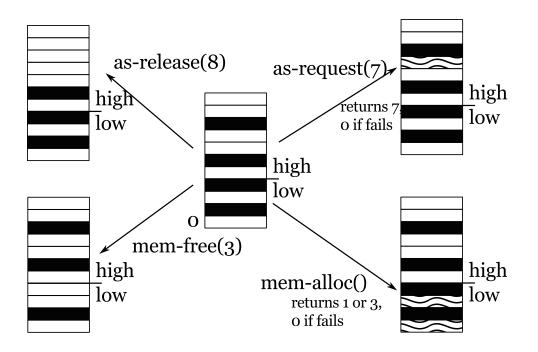

uint64\_t mem\_alloc(); // allocate some page in the low memory area

void mem\_free(uint64\_t page); // free an allocated page in the low memory area

uint64\_t as\_request(uint64\_t page); // allocate the specific page in the high memory area

void as\_release(uint64\_t page); // release a page allocated by as\_request

#### Figure 2.2: Example of API of the Virtual Memory Manager

which must now properly control and protect the translation tables, and to isolate the complexity of managing these data structures.

To handle this task, a typical OS kernel is split into two parts: the low level portions, to which we refer as the *virtual memory manager*, and the rest of the kernel, which we refer to as the *high-level kernel*. The virtual memory manager is aware of the specific details of the hardware's address translation model, and is responsible for managing the translation tables and the control registers. Then it abstracts away these details behind a simpler abstract interface for managing the indirect addresses, which it presents to the high-level kernel.

The high-level interface of the virtual memory manager is specific to the particular operating system, and will be different depending on the needs of the kernel. However, for most kernels, the abstract interface has a common feature: it makes virtual addresses appear as though they are actual memory cells. This is usually complemented by some API for managing these virtual areas. An example of such an abstract interface and its API can be seen in Figure 2.2. The high-level kernel no longer needs to know the specifics of the hardware, and manages the indirect addresses only through the abstract interface.

The abstract interface allows the programmer to have a machine-independent, abstract model of the virtual address space in mind when designing the high-level kernel. Reasoning with this model is much simpler as the programmer no longer has to consider the translation mechanism, nor the memory requires to contain the virtual memory, nor the possibility of modifying the translation tables, expect through a well-defined interface. This also has an added benefit that the kernel becomes machine independent, and given different hardware address translation implementations, will work on any of them, as long as a suitable implementation of virtual memory manager is provided.

When we try to formally certify an operating system kernel, we want to make use of this abstraction. After all, if the abstract memory model makes it easier for the programmer to mentally reason about the high-level kernel, it should be easier to formally specify and prove it, as well. However, if we try to make use of separation logic and information hiding to define such an abstraction, we will discover that we can not do it.

Consider the operational semantics of the memory store on a machine with address translation.

$$\{\{pl \rightarrow ?\}\} *1 := \forall \{\{pl \rightarrow \forall\}\}$$

where  $pl = \begin{cases} R(PTROOT) + Pg(l) *8 & \text{if } R(PE) = 1\\ l & \text{otherwise} \end{cases}$

The specification requires us to follow the entire hardware translation mechanism to get the state that results from performing the store, which is independent of the particular implementation of the virtual memory manager. Suppose now that we have implemented a virtual memory manager, and we are trying to simplify the verification of stores within the high-level code. The natural approach would be to create an abstract data type for the page tables and allocation tables that the virtual memory manager needs. Then we could try to define a lemma that modifies the specifications of the store to make use of the abstracted translation data. The result would be something like the following specification:

$\begin{array}{l} \exists pl, AT, PM \\ \{ValidAllocation(AT) \land Allocated(AT, Pg(pl)) \ast ValidPM(PM) \land Trans(PM, l, pl) \ast \{pl \leadsto ?\}\} \\ \ast 1:= \lor \\ \{ValidAllocation(AT) \ast ValidPM(PM) \ast \{pl \leadsto \nu\}\} \end{array}$

This specification is definitely more abstract, as it managed to hide the details of the translation mechanism, as well as exact locations of the page tables. However, we are still stuck with having

to carry all the page tables and allocation tables in all the specifications, as every memory access is going to require it. This means that the high-level kernel is still aware of the underlying physical memory, and that to actually reason about memory operations in the high-level kernel, we still have to translate addresses and access the physical location. No matter how hard we try, we would not be able to use separation logic to create an abstract data type that gives us the abstract model of address spaces that we are aiming for, and therefore, we can never achieve the ideal form of the specification of a store in the presence of virtual memory:

$$\{l \rightarrow ?\} *1:=v \{l \rightarrow v\}$$

The easiest way to achieve the above semantics is to simply define new semantics that incorporate virtual memory and the API as a primitive. Then we can use these new semantics to verify the high-level kernel, and use the original semantics to verify the virtual memory manager. However, we will then face the challenge of how to connect the two pieces. It is for this purpose we have created a multi-machine verification framework that we are about to describe.

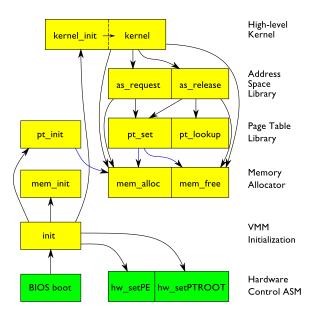

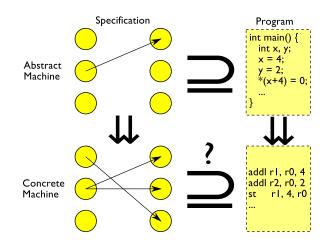

#### 2.1 Multi-Machine Verification of the Virtual Memory Manager

The goal of this thesis is to show how to verify a large software system, by breaking it up into modules, verifying each module on the abstract machine that is ideal for it, and then linking all the verified modules together in a way that guarantees the soundness of the whole system. We will demonstrate this technique on our particular implementation of a virtual memory manager that is used by some high-level kernel the details of which are not important. A diagram of an implementation of such a software system can be seen in Figure 2.3, which shows the functions of the virtual memory manager, how they interact, and how they provide an API for the high-level kernel.

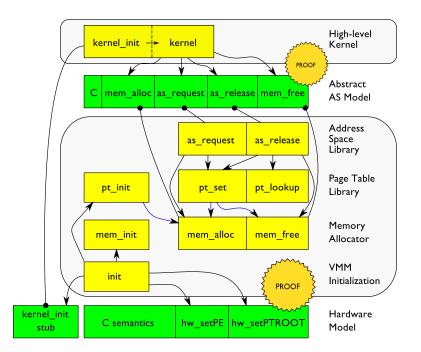

In the previous section, we have seen that the verification of the high-level kernel can be simplified if we were to analyze it against a higher-level machine model, one that assumes virtual memory and its API to be a primitive. When we do this, we get the design diagram in Figure 2.4. The new design shows a new machine model (the green block labeled *Abstract AS Model*) over which the kernel is certified. This new model is connected to the code of the virtual memory managers by

Figure 2.3: Diagram of Kernel Code

lines with circles on the end, indicating that the particular model feature is being implemented by code at the lower level of abstraction.

In a sense, what we are advocating is a meta-linguistic approach to abstraction and verification. This means that we create abstractions by defining a new language (machine model) with new operational semantics that exactly defines the abstraction in use. Such an abstraction mechanism is extremely powerful, as there is no real limitation on what the abstract language can be. Furthermore, it is a "hard" form of abstraction, meaning that there is no way to write a specification or create code that breaks the boundary of the semantics of the language. This hard abstraction guards against abstraction leaks that can be a common source of bugs in complex systems.

Although the separate verification of components in abstract machines may be easier, it is worthless if we can not guarantee the safety of the entire system when it is linked together. To link the two components, we use the notion of refinement, diagrammed in Figure 2.5. The programmer defines a relation between the abstract model and the actual hardware model, from which our framework creates a translation function that will refine the kernel, meaning that it will convert the proof of the correctness of the kernel from the abstract model to the proof of correctness of the kernel over the concrete model. However, this proof will be dependent on the compatibility of the VMM implementation, which the programmer must show. This compatibility proof is constructed from the

Figure 2.4: Multi-Machine Verification of the Kernel

fact that the VMM implementation correctly implements the primitives of the abstract machine, e.g. those lines with circles that we have seen in our kernel verification plan. Thus we get a proof of correctness of the high-level kernel and the VMM implementation linked together, meaning that they are safe to execute on the actual hardware.

However, there is one problem: we have not shown that the init can safely call the kernel. Our refinement approach to multi-machine verification handles such call (which we refer to as "upcall") as shown in Figure 2.6. In the most general sense, it is just a compatibility proof that works backwards. Instead of showing that the refined abstract primitive is compatible with the actual implementation, we show that the refined specification of the actual code is compatible with the specification with which the upcall was certified. By showing this, we guarantee that the when the kernel is refined to the hardware model, the refined specification of kernel-init will be exactly what init expects.

Our approach to defining the multi-machine verification using refinement has an additional benefit: it is chainable. This means we can use more than two machines, but layer the abstraction as we see fit. Thus, we can design the certification as a series of gradual refinements, each one being relatively easy to define. In fact, our virtual memory implementation is complex enough that it

Figure 2.5: The Workings of Refinement

Figure 2.6: The Workings of Refinement (fixed for upcall)

Figure 2.7: Complete Plan for VMM Certification

becomes beneficial to split the verification into several abstract machines, resulting our complete verification plan shown in Figure 2.7, which is the final plan that we will use to verify our virtual memory implementation.

At this point we have explained the high-level plan for multi-machine verification of our kernel. In the next section, we will give an overview of the framework that makes our approach work.

#### 2.2 The Framework for Multi-Layer Verification

The multi-machine approach to abstraction, in its naive implementation, suffers from several complications. First, the programmer must define numerous machines. Each machine must come with a sound verification system, meaning that the programmer must define static semantics and prove the soundness and correctness of the semantics. Second, the refinement and linking of code written in different machines, when done naively, ends up as an ad-hoc affair handled by meta-logical proof that connects the two static semantics. It is no wonder that most verification attempts tend to rely on a single machine model, enhanced by separation logic.

One of the goals of this thesis is to develop a framework that enables the multi-machine verification without suffering the amount of work that the naive approach seems to require. There are two problems that we are trying to solve. One is to allow the programmer to quickly define the machines that are used for verification, and the other is to allow easier definitions of refinements between machines. Our framework answers both issues.

First, our framework creates a machine-independent static semantics for any language that can be represented as a state transition system. This is done by creating a meta-language that takes a definition of a machine as a parameter. The definition supplies our meta-language with type of state and the set of operations that modify the state, with the meta-language supplying all the control flow primitives such as sequence, call, and branch. When the meta-language is instantiated with a particular machine model, the meta-language becomes a complete language, which can be used to create and analyze programs written for that machine. Because the control flow operations are defined independently from the particular machine definition, we can provide a single set of semantics for our meta-language, and prove that the semantics are sound and correct for any machine with which our meta-language is instantiated.

Figure 2.8: Graphical Representation of an Action

Figure 2.9: Action Concatenation

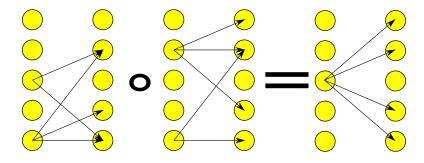

Thus a machine definition is just a set of states (of an arbitrary type), and a set of transitions between states, which we call *actions*. An example of two actions (related by a weaker-than relation) are shown graphically in Figure 2.8. The actions are the key feature of our framework. They are used to define the operational semantics of a particular machine. The effect of executing a program can be defined as an action, which consists of chaining of actions of individual operations of the program. Finally, the specifications are also actions.

An action means the following: if a state is in the domain of an action, that means that this state is safe with respect to this action - the computer executing this action from this state will not crash. The co-domain of an action is the set of possible states, one of which will be the one that machine will reach once the action completes.

Our framework defines several key operations over actions. For example, the same Figure 2.8 shows the meaning of the action on the left being weaker than the one on the right. This relation is critical for specifications, as a weaker action is a valid specification for the stronger one. Informally, one action is weaker than the other when it defines fewer valid starting states, and may result in

more final states. In the case of specifications, this can be seen clearly - the specifications can not allow additional starting states that the program can not handle, and the specifications may indicate that certain final states can occur, while the program may not be capable of producing these states. Other operations on actions, such as action composition, e.g. safely executing one action after another (Figure 2.9), and a choice/branching operation (not shown graphically) are also defined in our framework.

The operational semantics of a machine  $\mathcal{M}$  is just a named set of these actions. The names are the instructions or operations of the machine, which we refer to as  $\iota$ . Thus for example, in our definition of the MIPS machine,  $\mathcal{M}_{MIPS}(\text{addiu } r_d, r_s, w)$  will be an action over the state of the MIPS processor that corresponds to the addition operation. In high-level languages such as C, operations will correspond to higher-level commands, such as variable assignment or setting up a function call.

What is important is that many languages can be expressed as a set of possible atomic transitions in the state space, all of them can be described using our actions and machines. Every single program in such languages can then be converted into a tiny meta-language that we define.

$(Proc) \quad \mathbb{I} ::= nil \mid \iota \mid [1] \mid \mathbb{I}_1; \mathbb{I}_2 \mid \mathbb{I}_1 + \mathbb{I}_2$  $(Proc Heap) \quad \mathbb{C} ::= \{1 \rightsquigarrow \mathbb{I}\}^*$

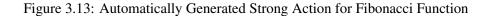

This language is defined by two things - procedures ( $\mathbb{I}$ ), which are non-looping chains of machine commands and calls into other procedures in the procedure heap ( $\mathbb{C}$ ). This language can be used to define any imperative programs, as it includes composition, choice, and recursion, as well as the ability to include any atomic operation from the definition of the machine. In our thesis, we will use this meta-language to verify programs written in MIPS assembly, IMP (a simple imperative language), and a simplified version of C. Our framework verifies programs by asking the programmer to give specifications to all procedures, and then to prove that these specifications are indeed weaker than the actions of the actual programs. If all procedures in a module have been checked in this way, we call such a module of code a certified module.

The other benefit of using the meta-language is that programs in all languages are verified in the same static semantics. This means that a single proof of soundness of the static semantics of our meta-language guarantees that the program verification is sound for all machines with which the meta-machine can be instantiated. No separate proofs of soundness for different machines are

Figure 2.10: Definition of Refinement

needed.

Thus the programmer benefits by having an ability to define the machines in a simpler way, and by not having to ever redo the soundness and correctness proof for the verification system, no matter which machine is being used. Moreover, we can use this commonality of semantics to assist in the generation of refinements that are needed to support multi-machine verification.

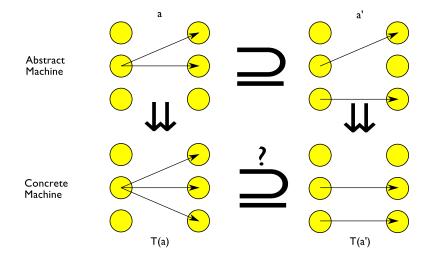

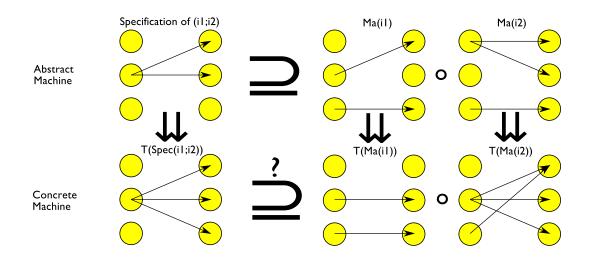

## 2.3 Refinement within the Framework

Using the meta-language allows us to verify modules in their own layer of abstraction. To connect the separate certified modules that exist at different levels of abstraction, our framework formally defines the notion of refinement. Suppose that we have two machines, the abstract one  $\mathcal{M}_A$ , and the concrete one  $\mathcal{M}_C$ . In the most general definition of the refinement, outlined in Figure 2.10, the programmer provides two functions: an action translation function that converts abstract specifications into concrete specifications, and a program translation function to convert an abstract program into a concrete program. These are marked by arrows in the diagram. Then the programmer provides a proof that if the abstract program is certified (abstract specification is weaker than the action of the abstract program) then the concrete program is also certified. Together these functions and the proof establish a refinement.

The diagram shows the refinement being created for a specific set of specifications and programs. However, it is possible to define these functions and proof to work not only for one specific

Figure 2.11: Code-Preserving Refinement

program, but for a large set of programs. In doing so, the refinement becomes general, as it can be reused for any number of programs written in the abstract machine. Such an approach is no longer ad-hoc, since the soundness of the refinement is proven once, rather that once for every program refined. However, creating these general refinements can be a lot of difficult work. As a part of our framework, we have shown several ways to automatically generate these general refinements from simpler definitions by utilizing features of our framework, such as the common meta-language and common static semantics.

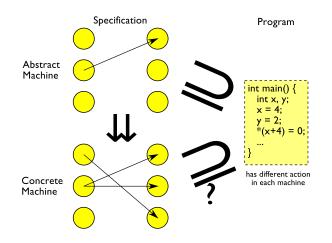

#### 2.3.1 Code-Preserving Refinements

When we consider what it would take to refine a high-level kernel from an abstract memory model to the address translated memory model, we can make a very important observation: the code of the program does not change, only the meaning of individual operations does. For example, if a high-level kernel stores a value in memory, then the refined kernel also performs the same state operation. The only difference is that in the abstract semantics, the kernel accesses a virtual page while in concrete semantics, the kernel does an address translation, followed by a store in the relevant physical page. However, the program is still exactly same.

This has several important consequences for the way we define refinements. First, for our VMM verification, since we currently are not aiming at compilation, we can define refinement without the need for relation of abstract and concrete programs. They are completely the same. Thus a general refinement can be defined by defining a function that converts abstract specifications into concrete

Figure 2.12: Relation Between Actions of Machines

Figure 2.13: Action Translation Preserves Weaker-than Relation

specifications, and a proof that the same program certified with abstract spec in the abstract machine will also be certified with the converted spec in the concrete machine (Figure 2.11).

More so, the fact that the program does not change will allow us to automatically generate the proof as well, as long as a few conditions are met. The first such condition is that the specification conversion function must work for all individual operations in the machine. In other words, if we take the semantics (action) of any operation of the abstract machine, and convert it, the resulting action must be weaker than the action defined by the concrete machine's operational semantics for that same instruction (see Figure 2.12). This guarantees that we can always refine instructions into themselves.

Figure 2.14: Action Translation Preserves Weaker-than Relation for Concatenation

We also need the conversion of actions to have several other properties as well. For example, if we take any two abstract actions where one is weaker than another, then the conversion function must preserve the weaker-than relation between them (see Figure 2.13). Similarly, if we have an action that is weaker than a chaining of two actions, then translated action must be weaker than the chaining of two translated actions (see Figure 2.14). There are a few other properties that the translation function must follow.

What is important is that if we show that an action translation obeys these few properties, then there is a proof that any program certified in the abstract machine is certified under the translated specification in the concrete machine. Thus we have succeeded in defining a refinement by defining a function that translates specifications and showing that it satisfies a few properties; our framework does the rest.

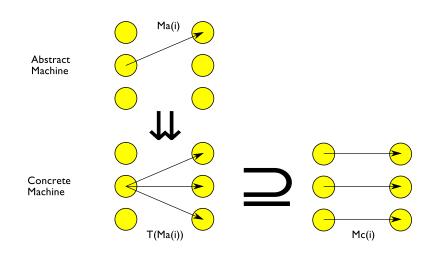

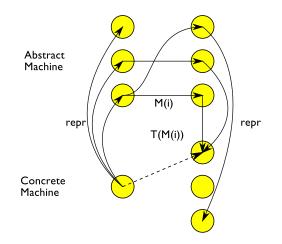

#### 2.3.2 Generating Refinements from Relations of Machine State

So far, we have not assumed that we know anything about the internal structures of the machines, relying only on the fact that they run the same programs, and leaving the definition of the specification translation function to the programmer.

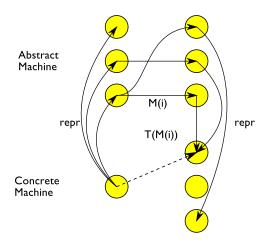

However, suppose we assume that there is a particular representation relation (repr) between the abstract and the concrete machine states. In this case, we are able to automatically define a general specification translation function based on this relation. The way we define this function is

Figure 2.15: Representation-based Specification Translation

similar to the way that McCreight[29] has defined it in his ad-hoc approach to modular verification of the garbage collector. The conversion function creates a concrete action by looking up related abstract states, running the abstract action on it, and returning the intersection of all possible results (Figure 2.15).

It is not important to understand how this conversion function works at this point. What is important is that such a conversion function always obeys all the properties we need for the conversion function to have, except one. We still need to show that for each operation in the machine, if we take the abstract operational semantics for that operation and convert it, the result must be weaker than the action defined by the operational semantics of the concrete machine. Thus, our framework automatically generates refinements that work for any program from the relation between the states of the machines and the proof of the property that the relation between the machines is preserved by every operation.

#### 2.3.3 Other Refinements

In this thesis, we also show several other ways to generate refinements. For example, if we know that an abstract machine is a projection of a concrete machine, we could automatically generate a much simpler action translation function than the very general one produced using repr. Another refinement generator we define is an extension of the repr with an invariant, that allows us to guarantee that the abstract machine preserves state information that is not contained in the abstract state.

Such a refinement allows us to use our refinements for information hiding, something that was impossible with McCreight's original repr. Other ways to generate refinements were imagined, such as refinements that allow a single process program to be embedded into a multiprocessor environment, etc., but these were not fully developed as they were not needed for the VMM verification. Still, our framework is general enough that it should be able to integrate these future refinements as well.

## 2.4 Conclusion of Overview

In the overview, we have presented the motivation for verifying the virtual memory manager and the high-level kernel that uses virtual memory using multiple abstract machines. We have presented our approach for linking these separately certified pieces, and we defined shown an informal description of the framework that makes it possible. In the rest of the thesis, we will show all the technical details needed for such verification. However, the explanation of the technical detail will start with the framework, build up the machinery needed for verification, and then give the detailed explanation of VMM certification.

We now proceed to the technical content.

## **Chapter 3**

# **The Verification Framework**

Many software verification frameworks, including our own previous work [15, 6] are practical for purposes of software verification. However, these frameworks are always tailored to the specific machine or a language. As the aim of our work is to enable verification of software at multiple abstraction layers, we need a verification system capable of handling multiple machine models. We accomplish this by making the verification framework parametric over the definitions of machines.

## **3.1** General Machine Definitions and Actions

There are two things that any machine or language has: some notion of context or state, and a set of operations over such state. In other words, a machine can be defined as data structure, which is similar to how finite state machines[44] or abstract state machines[18] are usually defined.

The exact details of the data structure that describes a machine are given in Figure 3.1. The ma-

| (State)                 | $\mathbb{S} \in \Sigma$                                     |

|-------------------------|-------------------------------------------------------------|

| (Operation)             | $\iota \in \Delta$                                          |

| (Conditional)           | $b \in \beta$                                               |

| (Cond Interp)           | $\Upsilon \in \beta \to \Sigma \to Prop$                    |

| (Action)                | $\mathtt{a} \in \Sigma \rightharpoonup \mathcal{P}(\Sigma)$ |

| (Operational Semantics) | $OS \in {\iota \rightsquigarrow a}^*$                       |

| (Language / Machine)    | $\mathcal{M} \in (\Sigma, \Delta, \beta, \Upsilon, OS)$     |

where  $\mathcal{M}(\iota) \triangleq \mathcal{M}.\mathsf{OS}(\iota)$  and  $\mathcal{M}(b) := \mathcal{M}.\Upsilon(b)$

Figure 3.1: Abstract State Machine

chine is a tuple containing several type definitions, functions, and mappings. The most important part of the machine definition is the type of the state ( $\Sigma$ ). The type of the state determines all the information that the code may access about the machine. The machine also contains a set of operations ( $\Delta$ ), which are names of all possible atomic operations that the machine can be performed. What the operations do is encoded in the operational semantics of the machine (OS), which map the individual operations to their actions. The action (a) is a state transformation relation/function which defines a particular transition from a state into a set of possible states (more on this in Section 3.1.1).

The machine definition also includes the notion of conditional type ( $\beta$ ) which describes the type of expressions that can be used for determining that branching conditions in the particular machines, which the semantics converts into predicates by using the interpreter function  $\Upsilon$ .

#### 3.1.1 The Language of Actions

In our verification system, the actions are used for three things:

- 1. To define the operational semantics of a particular machine. The definition of *M*.OS is that particular use.

- 2. To define the behavior of a particular program. Any program can be imagined as a sequence of operations, and thus a sequence of actions, which itself is an action.

- 3. To define the specifications of a program.

These uses require that our actions be expressive enough to describe certain behaviors, which include

• Non-determinism. Suppose that action a, when applied to a particular state S, does not fail and will result in one of the several states, although we do not know which. To express this, we have defined an action type to have a set of states as a codomain. Thus the set of states defined by (a S) is a set of possible final states of that action. This does not mean that the operation with this actions has to eventually result in all the states it defines. In fact, it is possible that the operation always results in a particular state within the set (or does not terminate), but the action does not provide this information.