### Advanced Packaging Technologies for Heterogeneous Integration (HI)

Ravi Mahajan, Fellow; Sandeep Sane, Principal Engineer Intel Corporation

Acknowledgments: Kemal Aygun, Kaladhar Radhakrishnan, Debendra Mallik, Gaurang Choksi, Rahul Manepalli, Chris Baldwin, Sergey Shumarayev, Ram Viswanath, Pat Stover, Wilfred Gomes, Gans Ganesan, Sriram Srinivasan, Ahmet Durgun, CM Jha, Weihua Tang, Bill Chen (ASE), Subu Iyer (UCLA), Bill Bottoms (3MTS), Samantika Sury, Robert Wisniewski, Dipankar Das, Pradeep Dubey

### **Executive Summary**

Part 1: The Package as a Compact HI Platform: Some Key Elements

- On-Package Interconnects

- High Bandwidth Signaling

- Power Delivery

- Thermal Management

- Assembly Processes

- Materials & Design Tools

Part 2: Product implementations using Advanced Packaging Technologies

### Outline

- Introduction The Package as a Compact HI Platform

- On Package Interconnects & High Bandwidth Signaling

- Power Delivery Architectures

- Thermal Management

- Assembly Process, Materials and Design Tools

- Summary

### Increased Interest in HI is Driven by

Additionally, Yield Resiliency and Time to Market Advantages Make On-Package HI Attractive

# The Package is a Compact HI Platform For Several Interesting Use Cases

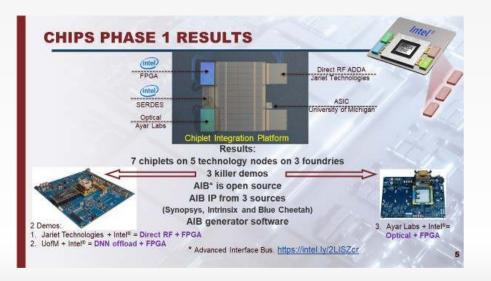

Sources: Intel Architecture Day (2021) & ERI Summit (2020). The CHIPS work is supported by the DARPA MTO office (DARPA CHIPS Program))

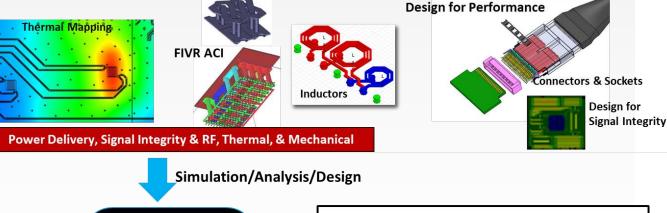

### The Package as a HI Platform – Key Focus Areas

Power-efficient, High Bandwidth On-Package IO links

Enable a diversity of off-package IO protocols

Deliver noise isolation for single ended and differential signals

Manage increasing cooling demands

Support complex power delivery architectures

Meet diverse application functionality ranging from high performance servers to flexible, wearable electronics

Meet a broad spectrum of reliability requirements for different market segments and applications

Provide cost effective, high precision quick turn assembly

### On-Package Interconnects & High Bandwidth Signaling

Power-efficient, High Bandwidth On-Package IO links

Enable a diversity of off-package IO protocols

Deliver noise isolation for single ended and differential signals

Manage increasing cooling demands

Support complex power delivery architectures

Meet diverse application functionality ranging from high performance servers to flexible, wearable electronics

Meet a broad spectrum of reliability requirements for different market segments and applications

Provide cost effective, high precision quick turn assembly

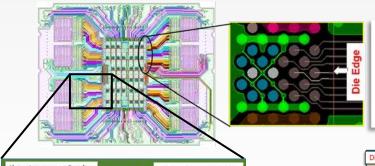

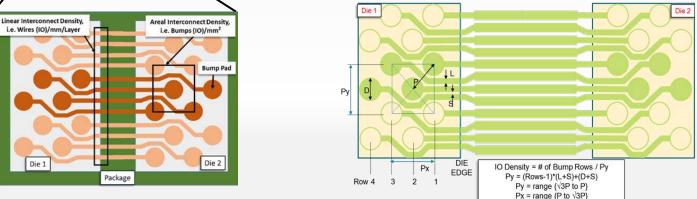

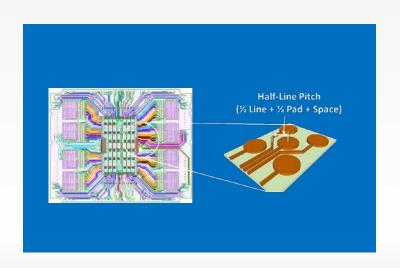

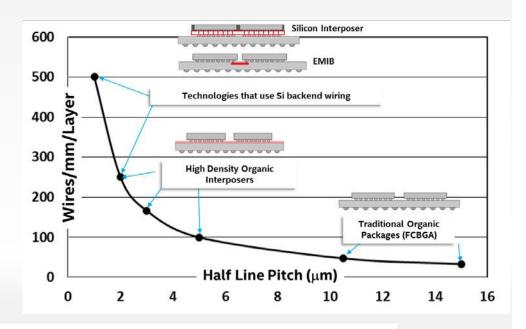

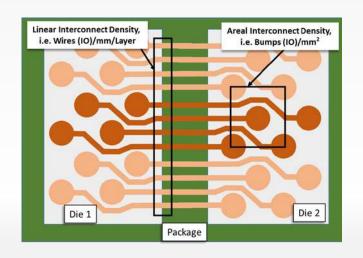

### High Density Interconnects : Physical Metrics

- Wiring Density increases Require Wire (aka IO)

Width, Space & Pad reduction (Zero Pad Ideal)

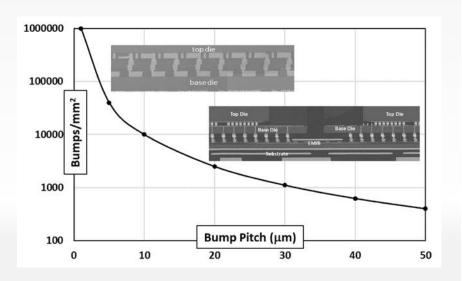

- Bump Density Increases Require Bump Pitch Shrinks

R. Mahajan et al., "Embedded Multi-die Interconnect Bridge (EMIB) -- A High Density, High Bandwidth Packaging Interconnect," 2016 ECTC

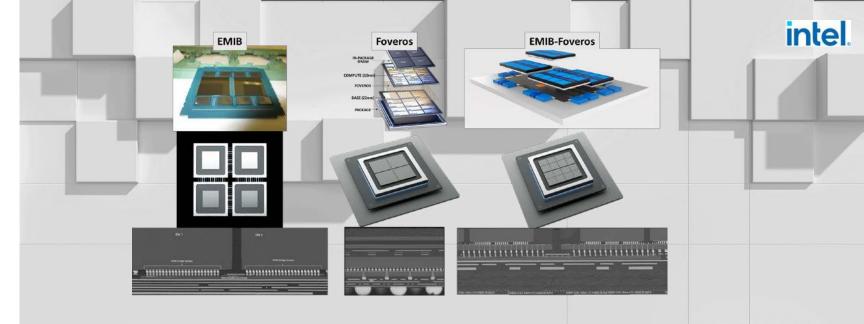

### Current State of Advanced Packaging (Intel Centric View)

### Planar Interconnects: MCP Landscape

Focus: Increased Interconnect Density + Improved Power Efficiency for Increased BW

### Vertical Interconnects: MCP Landscape

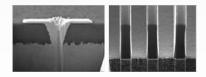

Transition from Solder Based Interconnects to Cu-Cu interconnects needed with shrinking Bump Pitch\*

\*Li et al. "Scaling Solder Micro-Bump Interconnect Down to 10 μm Pitch for Advanced 3D IC Packages" ECTC 2021

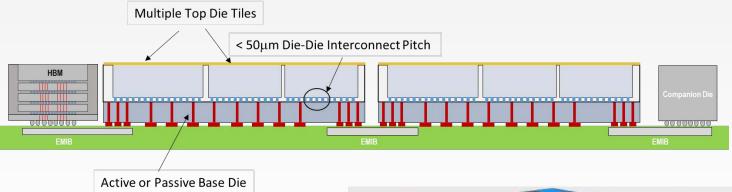

### Blending 2D and 3D

- Architecture for >> reticle sized die + High-Density Bridge links

- Increased Partitioning

Opportunities in X, Y and Z

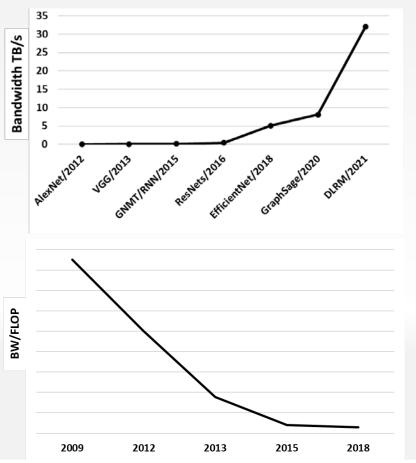

### I/O Bandwidth & Speed Scaling Trends

Reproduced with permission from Ethernet Alliance

- Growing Network & Memory (BW + Speed)

Demand

- As peak FLOPS grow BW will need to keep up

- BW Demand poses significant challenge for the physical and signaling characteristics of the package interconnect

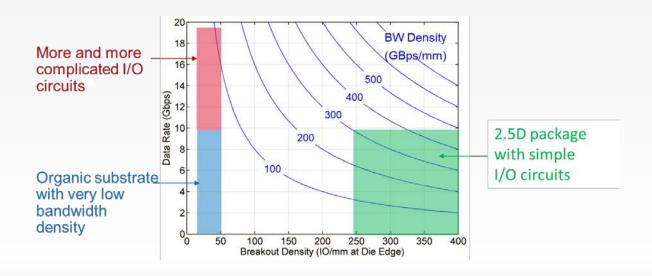

### On-Package Bandwidth Density Scaling

Enable high bandwidth density connection between dies on an 'advanced package' with simple I/O circuits and low power consumption with limited reach

R. Mahajan et al., "Embedded Multi-die Interconnect Bridge (EMIB) -- A High Density, High Bandwidth Packaging Interconnect," 2016 ECTC

### Interconnect Scaling to Enable Bandwidth Scaling

Peripheral Interconnects for Solder Based 2D Architectures

| Generations                     |                         | 1   | 2   | 3    | 4    | 5    |

|---------------------------------|-------------------------|-----|-----|------|------|------|

| Raw Bandwidth Density (GBps/mm) |                         | 125 | 250 | 500  | 1000 | 2000 |

| Package Technology              | Minimum Bump Pitch (μm) | 55  | 50  | 40   | 35   | 30   |

|                                 | IO/mm                   | 500 | 667 | 1000 | 1500 | 2000 |

|                                 | IO/mm <sup>2</sup>      | 331 | 400 | 625  | 816  | 1111 |

| Signaling Speed                 | Gbps                    | 2   | 3   | 4    | 5.33 | 8    |

Peripheral Interconnects for 2D Architectures with Aggressive pitch Scaling

| Generations                     |                         | 1   | 2   | 3    | 4    | 5     |

|---------------------------------|-------------------------|-----|-----|------|------|-------|

| Raw Bandwidth Density (GBps/mm) |                         | 125 | 250 | 500  | 1000 | 2000  |

| Package Technology              | Minimum Bump Pitch (μm) | 55  | 40  | 30   | 20   | 10    |

|                                 | IO/mm                   | 500 | 667 | 1000 | 1500 | 2000  |

|                                 | IO/mm <sup>2</sup>      | 331 | 625 | 1111 | 2500 | 10000 |

| Signaling Speed                 | Gbps                    | 2   | 3   | 4    | 5.33 | 8     |

Source: Chapter 22 in IEEE Heterogeneous Integration Roadmap (https://eps.ieee.org/technology/heterogeneous-integration-roadmap/2019-edition.html)

### Interconnect Scaling to Enable Bandwidth Scaling

Area Interconnects for 3D Architectures

| Generations                      |                            | 1   | 2    | 3    | 4    | 5     |

|----------------------------------|----------------------------|-----|------|------|------|-------|

| Raw Bandwidth Density (Gbps/mm²) |                            | 125 | 250  | 500  | 1000 | 2000  |

| Package<br>Technology            | Minimum Bump Pitch<br>(μm) | 40  | 30   | 20   | 15   | 10    |

|                                  | IO/mm <sup>2</sup>         | 625 | 1111 | 2500 | 4444 | 10000 |

| Signaling Speed                  | Gbps                       | 1.6 | 1.8  | 1.6  | 1.8  | 1.6   |

Source: Chapter 22 in IEEE Heterogeneous Integration Roadmap (https://eps.ieee.org/technology/heterogeneous-integration-roadmap/2019-edition.html)

### **Power Delivery**

Power-efficient, High Bandwidth On-Package IO links

Enable a diversity of off-package IO protocols

Deliver noise isolation for single ended and differential signals

Manage increasing cooling demands

Support complex power delivery architectures

Meet diverse application functionality ranging from high performance servers to flexible, wearable electronics

Meet a broad spectrum of reliability requirements for different market segments and applications

Provide cost effective, high precision quick turn assembly

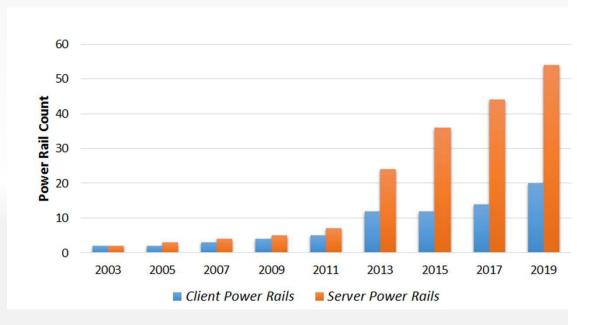

### The Evolution of Power Management

# Historical Approach (1980s to early 2000s)

- Frequency scaling → Faster (& leaky) transistors enable higher frequency

- Scale V<sub>th</sub> & device dimensions

- Increased leakage and active power

#### Shift to Multi-Core (mid 2000s)

- Slow down V<sub>th</sub> scaling & Process improvements to control leakage

- Slow down frequency scaling

- Add more cores for performance

#### Number of power rails has steadily gone up to improve power management

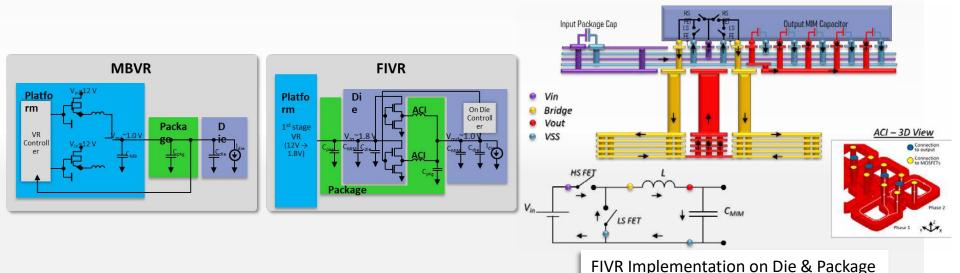

### FIVR – Fully Integrated Voltage Regulator

FIVR was introduced by Intel® on the 4<sup>th</sup> generation Core ™ Microprocessors

- Steps down the 1.8 V Vin to a range of output voltages (0.5 1.3V)

- The number of FIVR phases on a microprocessor can range from 50 to 300

A single MBVR converts the incoming platform power supply voltage to 1.8V

intel

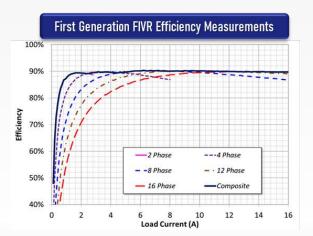

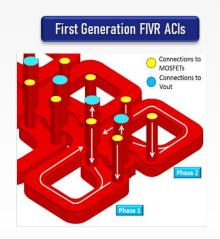

### Efficiency on First Generation FIVR

First generation of FIVR achieved an efficiency of 90% at full V<sub>out</sub> (1.08 V)

■ First generation FIVR ACI had a high Q-factor due to a large XY footprint and a 700um core

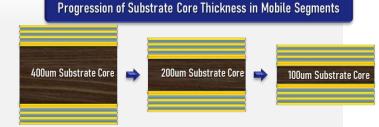

The push to thin and light devices has reduced the substrate core thickness hurting ACI performance

### Magnetic Inductor Arrays

The 10<sup>th</sup> generation Intel<sup>®</sup> Core™ microprocessors used a number of MIA modules for the different voltage domains

■ The use of magnetic inductors helps recover the loss of efficiency due to ACI area scaling

### The Package as a HI Platform – Key Focus Areas

Power-efficient, High Bandwidth On-Package IO links

Enable a diversity of off-package IO protocols

Deliver noise isolation for single ended and differential signals

Manage increasing cooling demands

Support complex power delivery architectures

Meet diverse application functionality ranging from high performance servers to flexible, wearable electronics

Meet a broad spectrum of reliability requirements for different market segments and applications

Provide cost effective, high precision quick turn assembly

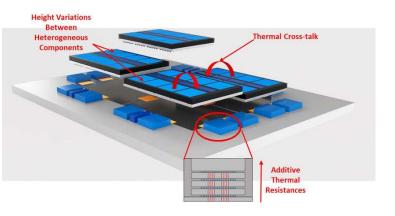

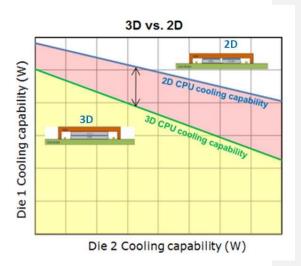

### Intel 3D Heterogeneous Package Thermals

#### **Key challenges:**

• Die-die thermal resistance, thermal cross-talk between neighboring die, and higher power density due to stacked active die → The combined effect results in lower cooling capability for 3D packages compared to 2D packages.

#### **How Intel manages Thermals:**

- Low resistance die-to-die thermal interfaces (Foveros Omni and Foveros Direct packages).

- Best in class metallic thermal interface material (TIM1) between die and integrated heat spreader (IHS).

- Thermally optimized Si floorplan and package architectures. Co-design of Si and Package for improved thermals.

### Assembly Process, Materials and Design Considerations

Power-efficient, High Bandwidth On-Package IO links

Enable a diversity of off-package IO protocols

Deliver noise isolation for single ended and differential signals

Manage increasing cooling demands

Support complex power delivery architectures

Meet diverse application functionality ranging from high performance servers to flexible, wearable electronics

Meet a broad spectrum of reliability requirements for different market segments and applications

Provide cost effective, high precision quick turn assembly

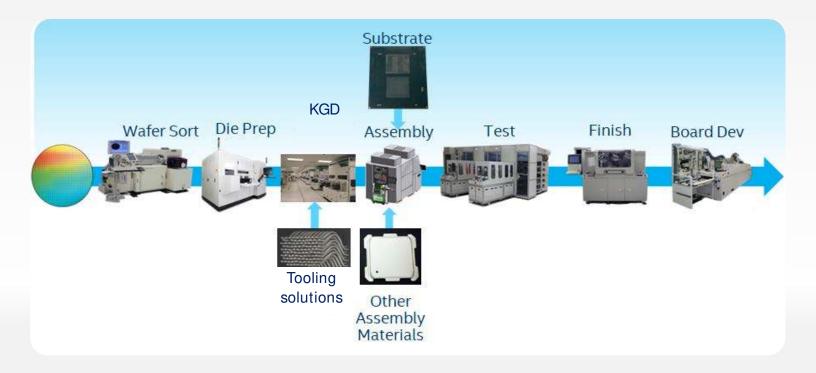

### Assembly and Test Technology Development Scope

Assembly TD Focus: High functionality, High Yield, High Quality & Reliability

### Heterogeneous packaging: Challenges and opportunities

#### Better materials

- UF/mold: Flow, Reliability, Warpage

- Fluxes: joint quality/cleanability

- Thermal interface materials

#### Improved Electrical

- Bump Current carrying capability

- HSIO and Power Delivery

- Design co-optimization

#### Fine pitch interconnect joint yield

- Die-Die, Die-Wafer, Die- Substrate

- Improved alignment/ bump Coplanarity

- Stacked die coplanarity

#### External IP/die/pkg integration

- Passivation/bump compatibility

- Design rule/ Design co-optimization

#### Advanced substrates

- Improved bump coplanarity

- Fine pitch/ Multi diameter bumping

- High density routing

#### Acceptable Reliability

- Temperature cycling

- Electromigration

- Temperature/humidity/Bias

Equipment/ Material/Process/ Design Co-optimization key to Heterogeneous Assembly & Packaging

### Advanced Substrates: Challenges & Opportunities

Large Package Form Factors: Panel/Wafer Processing

High Density Routing:

Advanced Patterning, Via

Formation, Etch

Materials: Better photoresists

Via fill /plating chemistries

Chip to Chip Bridge: EMIB: High Precision Embedding

Fine Pitch Assembly:

Planarization Technologies to enable Planar bumping & Buildup layers

Fine Pitch Heterogeneous Bumping: Advanced Buildup/RDL Cu & Bump Plating-tools/chemistries

**High BW- HSIO:**

Materials: Advanced Dielectric Materials

Smooth Cu/Barrier Layers

Equipment/ Material Advances in Substrate Panel Processes key to Heterogeneous Integration

# Design, Process & Materials Optimized for Performance, Manufacturability & Cost

Process Prototyping

Technology

Fundamentals,

Predictability

and

Performance

Enhancement

#### **Materials Development**

- Magnetic Inductors

- Low Loss Materials

- High Performance Pkg Passives

- High Performance Thermal Interface

- Integrated Heat-spreaders

- Technologies for Warpage Control

- DP & Assembly Process Materials

Characterization

### Summary

- Today there is Broad and Growing consensus that Heterogeneous Integration (HI) is a key enabler

of performance moving forward.

- On-Package Integration, using Advanced Packaging Architectures for Compact, Power Efficient, High Bandwidth Platforms is a key HI Element

- Number of Innovative package architectures are available today to facilitate power efficient, high bandwidth die-die interconnects on package → There is a roadmap to scale these interconnects in all three dimensions

- Delivering a clean power supply is important to optimize microprocessor performance

- The increase in power rails & overall power levels introduces new power delivery challenges

- Development of high efficiency, high density, high voltage IVRs will be critical to meet the requirements of future high-performance microprocessors

- Thermal Management requires Continued Materials and Co-Design Focus

- Continued Scaling of Advanced Packaging requires focus on multiple aspects including interconnect design, high-speed signaling, power delivery, thermal management, materials, assembly and process design

### **Legal Notices**

#### **Legal Notices**

All product and service plans, and roadmaps are subject to change without notice. Any forecasts of goods and services needed for Intel's operations are provided for discussion purposes only. Intel will have no liability to make any purchase in connection with forecasts published in this document. Code names are often used by Intel to identify products, technologies, or services that are in development and usage may change over time. No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

All product and service plans and roadmaps are subject to change without notice. The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade. You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

Statements in this document that refer to future plans or expectations are forward-looking statements. These statements are based on current expectations and involve many risks and uncertainties that could cause actual results to differ materially from those expressed or implied in such statements. For more information on the factors that could cause actual results to differ materially, see our most recent earnings release and SEC filings at www.intc.com.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others. This document contains information on products and/or processes in development.

### Current State of Advanced Packaging (Intel Centric View)

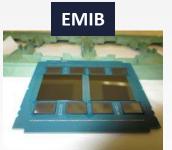

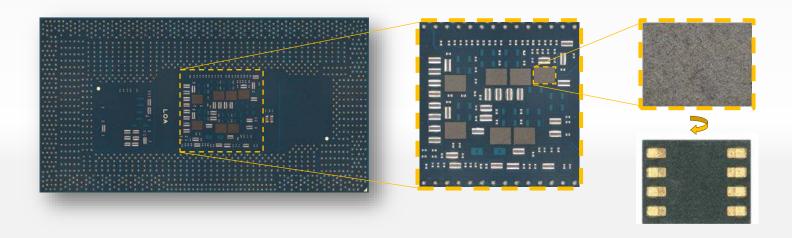

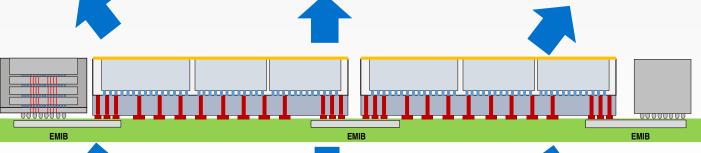

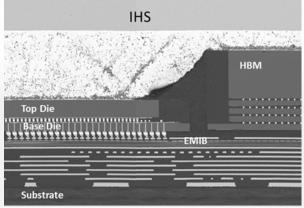

### **EMIB** Embedded **M**ulti-Die Interconnect **B**ridge

- Localized high-density wiring

- Multiple Bridges, Multiple Bridge Sizes and Bridge Technologies

- Bridge Mix and Match → Enhanced Design Flexibility

- Bridge silicon costs < Silicon interposer</li>

- No TSVs, Significantly less silicon area

- Die from Different Foundries

- Large Overall Die Area enabled

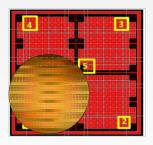

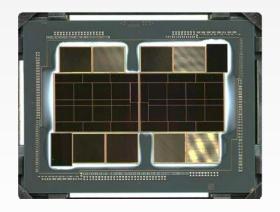

### Sapphire Rapids - EMIB Implementation

| Attribute            | SPR XCC    | SPR HBM              |

|----------------------|------------|----------------------|

| Top Die Count        | 4          | 4, + 4 HBM2E         |

| Max Top Die Size     | ~400 mm²   | ~400 mm <sup>2</sup> |

| EMIB Pitch           | 55μm       | 55μm                 |

| Core Pitch (minimum) | 100μm      | <b>100</b> μm        |

| Memory (HBM)         | N/A        | 4x 8H HBM2E          |

| Package size         | 78 x 57 mm | 100 x 57 mm          |

| EMIB count           | 10         | 14                   |

### **EMIB Link Capability**

|                                          | Intel MDF | Intel OPIO                   | Improvement due to EMIB |

|------------------------------------------|-----------|------------------------------|-------------------------|

| Packaging Tech                           | EMIB      | Standard<br>2 routing layers |                         |

| Bump Pitch (μm)                          | 55        | 110                          |                         |

| Pin Speed (Gbps)                         | 5.4       | 8 – 16                       |                         |

| Shoreline BW density (GBps/mm)           | 196       | 34.5 – 69                    | 5.68x – 2.84x           |

| Areal BW density (GBps/mm <sup>2</sup> ) | 158       | 36.7 – 73.4                  | 4.3x – 2.15x            |

| PHY power efficiency                     | 0.5       | 1.5-2.0                      | 3x - 4x                 |

**EMIB**

vs. standard package

2x bandwidth density

4X

petter powe

better power efficiency

<sup>•</sup> Intel MDF was announced in Semicon West 2019.

<sup>•</sup> Intel OPIO 8Gbps was used in a Client in 2013. Higher speeds were developed in an internal study.

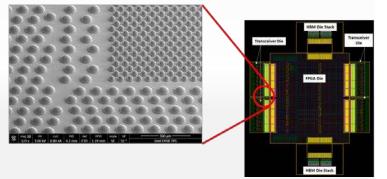

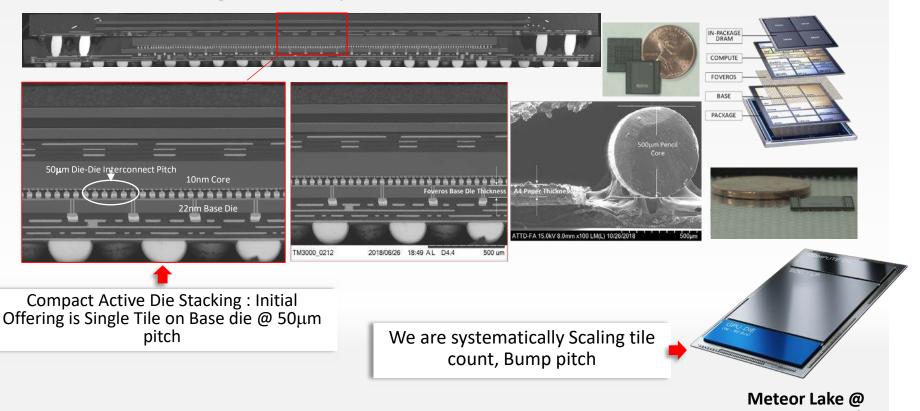

### Intel Foveros: High Density 3D

- 36μm Bump pitch

- 2. W. Gomes et al., "8.1 Lakefield and Mobility Compute: A 3D Stacked 10nm and 22FFL Hybrid Processor System in 12×12mm2, 1mm Package-on-Package," 2020 ISSCC

D. Ingerly, et al. "Foveros: 3D Integration and the use of Face-to-Face Chip Stacking for Logic Devices," 2019 IEDM

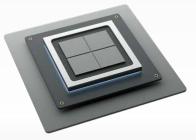

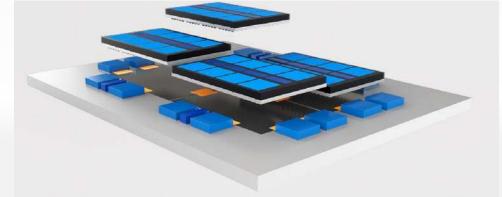

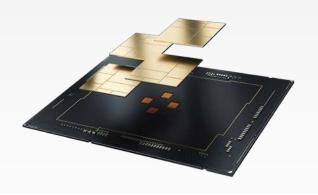

### Blending Planar and 3D MCPs (EMIB + Foveros)

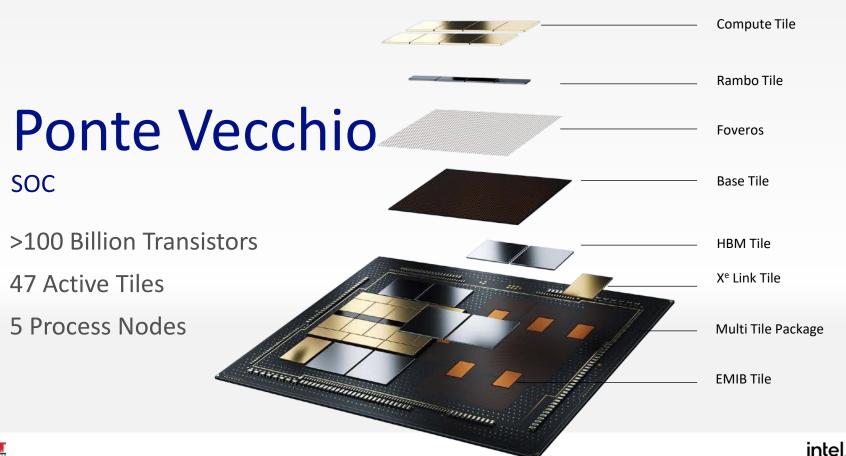

### Ponte Vecchio

| Attribute                      | PVC 2T             |

|--------------------------------|--------------------|

| D2D Pitch                      | 36µm               |

| Active Top Die Count Per Stack | 16                 |

| Max Active Top Die Size        | 41mm²              |

| Base Die Size                  | 650mm <sup>2</sup> |

| EMIB Pitch                     | 55μm               |

| Core Pitch (min)               | 100μm              |

| Memory (HBM)                   | 8x                 |

| Package size                   | (77.5 x 62.5) mm   |

| EMIB count                     | 11                 |

### Continued leadership in advanced packaging

# Embedded Multi-die Interconnect (EMIB)

bump pitch ≤ **55 microns**

- leads industry

- first 2.5D embedded bridge solution

- products shipping since 2017

#### Foveros Technology

bump pitch 50-36 microns

- wafer-level packaging capabilities

- first-of-its-kind 3D stacking solution

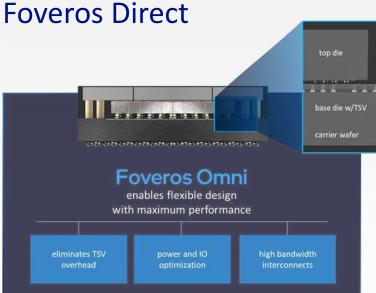

#### Foveros Omni

bump pitch ~25 microns

- next gen Foveros technology

- unbounded flexibility with performance 3D stacking technology for die-to-die interconnect and modular designs

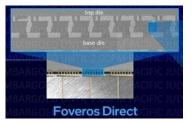

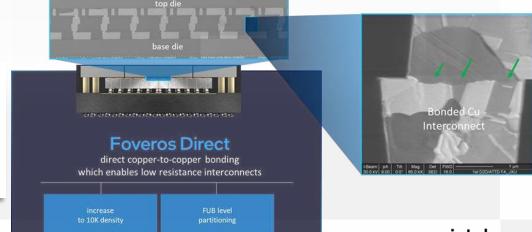

#### **Foveros Direct**

bump pitch < 10 microns

- direct copper-tocopper bonding for low resistance interconnects

- blurs the boundary between where the wafer ends and the package begins

Packaging Innovations In The Near Future: Foveros Omni and

Foveros top

THE RESIDENCE OF SHARE SHEET

Rich Interconnect Portfolio allows greater mix-and-match and better/independent interconnect optimization for Power and IO

Pitch Scaling from 25µm → ≤ 10µm leads to an order of magnitude increase in IO/mm² (1600 → ≥ 10,000)

### **Key Messages**

- Several Innovative Packaging Architectures are available today for Scaling in all 3 directions – In Today's talks we have focused mainly on the physical implementations

- Intel is using them in Client, Server and Discrete Graphics products to provide unprecedented levels of Heterogeneous Integration

- The next generation of Innovations in HI will offer increased partitioning opportunities with an enhanced interconnect portfolio and significant increases in interconnect density

# Thank you!

"Something is going to happen."

"What is going to happen?"

"Something \_\_\_\_\_."

bit.ly/2VEW6Dt

#### References

- 1. R. Mahajan, et al., "Embedded Multi-Die Interconnect Bridge (EMIB) A Localized, High Density Multi-Chip Packaging (MCP) Interconnect," *IEEE Transactions on Components, Packaging and Manufacturing Technology*, Volume: 9, Issue: 10, Oct. 2019, pp. 1952-1962.

- 2. D. Greenhill, et al, "A 14nm 1GHz FPGA with 2.5D transceiver integration" 2017 IEEE International Solid-State Circuits Conference (ISSCC) 2017 pp. 54-55 Feb 2017.

- 3. IEEE Electronics Packaging Society Heterogeneous Integration Roadmap, 2019 Edition, https://eps.ieee.org/technology/heterogeneous-integration-roadmap/2019-edition.html.

- 4. S. K. Moore, "Intel's View of the Chiplet Revolution", IEEE Spectrum, April 12, 2019; <a href="https://spectrum.ieee.org/tech-talk/semiconductors/processors/intels-view-of-the-chiplet-revolution">https://spectrum.ieee.org/tech-talk/semiconductors/processors/intels-view-of-the-chiplet-revolution</a>.

- 5. Kaby Lake G, Hot Chips 2019: https://fuse.wikichip.org/news/1634/hot-chips-30-intel-kaby-lake-g/.

- 6. D. Ingerly, et al. "Foveros: 3D Integration and the use of Face-to-Face Chip Stacking for Logic Devices," 2019 International Electron Devices Meeting, San Francisco, CA, Dec. 2019.

- 7. K. Oi, et al., "Development of New 2.5D Package with Novel Integrated Organic Interposer Substrate with Ultra-Fine Wiring and High-Density Bumps," *Proceedings of the 2014 IEEE* 64th Electronic Components and Technology Conference, Orlando, pp. 348-353.

- 8. W. Gomes, et al., "Lakefield: 3D stacked 10 nm and 22 FFL Mobile Processor System in 12x12, 1 mm POP Package," 2020 International Solid-State Circuits Conference, San Francisco, Feb. 2018.

- 9. R. Mahajan, et al., "Embedded Multi-die Interconnect Bridge (EMIB) -- A High Density, High Bandwidth Packaging Interconnect," Proc. IEEE Electronic Components and Technology Conference (ECTC), Las Vegas, NV, May 26-29, 2016, pp. 557-565.

- 10. <a href="https://www.anandtech.com/show/9390/the-amd-radeon-r9-fury-x-review">https://www.anandtech.com/show/9390/the-amd-radeon-r9-fury-x-review</a>.

- 11. D. Yu, "Advanced Heterogeneous Integration Technology Trend for Cloud and Edge," 2017 IEEE Electron Devices Technology and Manufacturing Conference, Japan, March 2017.

- 12. <a href="https://www.darpa.mil/program/common-heterogeneous-integration-and-ip-reuse-strategies">https://www.darpa.mil/program/common-heterogeneous-integration-and-ip-reuse-strategies</a>.

- 13. AIB Github: <a href="https://github.com/intel/aib-phy-hardware">https://github.com/intel/aib-phy-hardware</a>.

- 14. K. Oi, et al., "Development of New 2.5D Package with Novel Integrated Organic Interposer Substrate with Ultra-Fine Wiring and High-Density Bumps," Proceedings of the 2014 IEEE 64th Electronic Components and Technology Conference, Orlando, pp. 348-353.

- 15. M. Sunohara, T. Tokunaga, T. Kurihara and M. Higashi, "Silicon interposer with TSVs (through silicon vias) and fine multilayer wiring," in Proc. IEEE Electronic Components and Technol. Conf. (ECTC), Lake Buena Vista, FL, May 27–30, 2008, pp. 847–852.

- 16. S. Miki, H. Taneda, n. Kobayashi, K. Oi, K. Nagai, T. Koyama, "Development of 2.3D High Density Organic Package using Low Temperature Bonding Process with Sn-Bi Solder," Proceedings of the 2019 IEEE 69th Electronic Components and Technology Conference, Las Vegas, pp. 1599-1604.

- 17. A. A. Elsherbini, S. M. Liff and J. M. Swan. "Heterogeneous Integration Using Omni-Directional Interconnect Packaging," 2019 International Electron Devices Meeting, San Francisco, CA, Dec. 2019.

- 18. R. Mahajan, "Quiet Revolutions: How Advanced Microelectronics Packaging Continues to Drive Heterogeneous Integration1," 2020 19th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), 2020, pp. 1408-1412, doi: 10.1109/ITherm45881.2020.9190247.

### **Legal Notices**

#### **Legal Notices**

All product and service plans, and roadmaps are subject to change without notice. Any forecasts of goods and services needed for Intel's operations are provided for discussion purposes only. Intel will have no liability to make any purchase in connection with forecasts published in this document. Code names are often used by Intel to identify products, technologies, or services that are in development and usage may change over time. No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

All product and service plans and roadmaps are subject to change without notice. The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade. You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

Statements in this document that refer to future plans or expectations are forward-looking statements. These statements are based on current expectations and involve many risks and uncertainties that could cause actual results to differ materially from those expressed or implied in such statements. For more information on the factors that could cause actual results to differ materially, see our most recent earnings release and SEC filings at www.intc.com.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others. This document contains information on products and/or processes in development.