## Advanced SI Analysis – Layout Driven Assembly

**Fluid Dynamics**

**Structural Mechanics**

Electromagnetics

Systems and Multiphysics

Tom MacDonald RF/SI Applications Engineer II

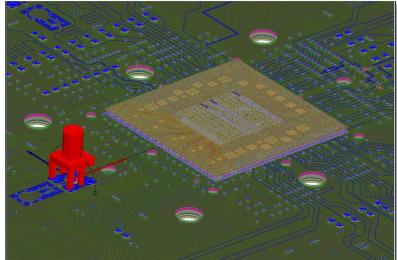

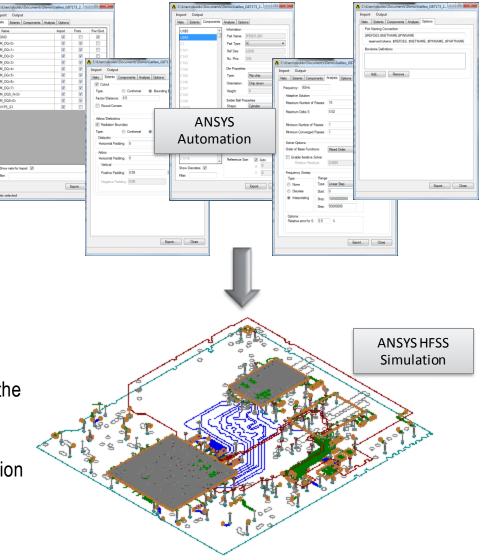

As the voracious appetite for technology continually grows, so too does the need for fast turn around times and efficient techniques for characterization. To improve timeliness of turns, ANSYS SI product suite offers new functionality to enhance the user experience with layout driven assembly. By combining HFSS for connectors and HFSS 3D Layout for boards, this methodology allows us to apply current best solving techniques to our problems for optimal turnaround time and accuracy.

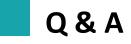

### **Design Pressures**

Layout Driven Assembly

**Multiphyics Board Analysis**

3 © 2016 ANSYS, Inc. April 25, 2016

### **ANSYS** Customer Pressures

Energy Availability Time to Market Product Lifecycle Skilled Labor

# Uncertainty

**Margin for Error**

Complexity

Competition Cost Constraints Lawsuits/Warranty Product Innovation Customer Expectations

## **ANSYS** Getting Product Designs Right

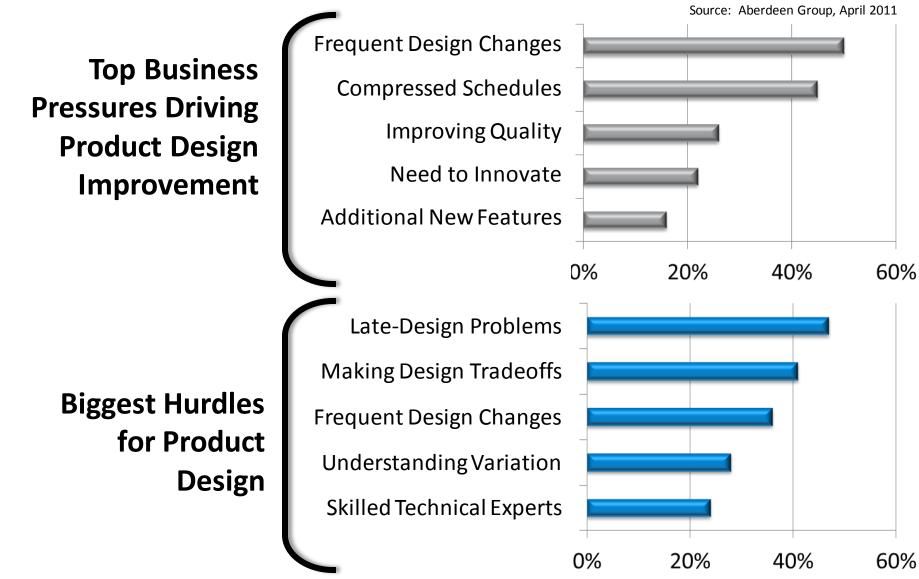

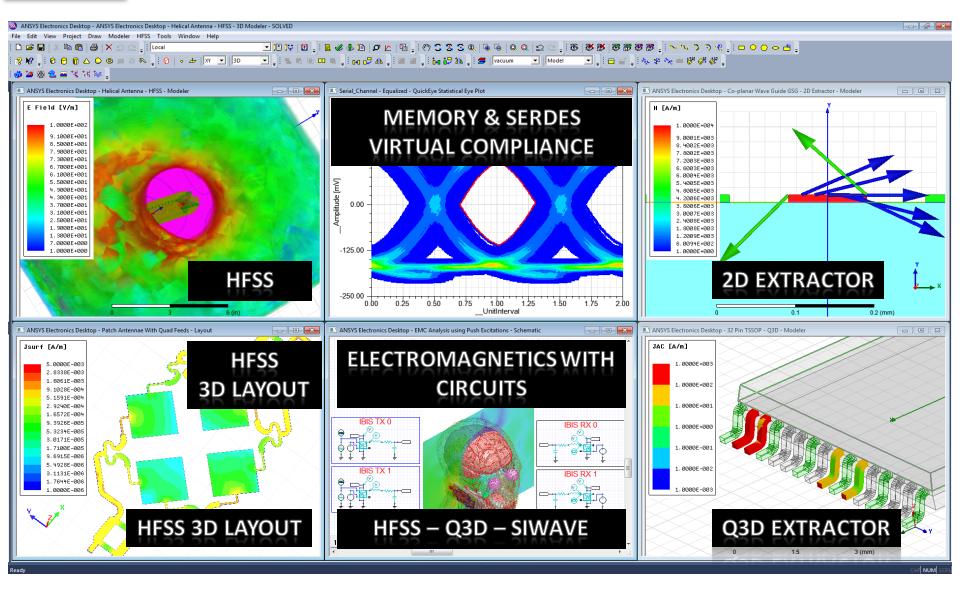

### **ANSYS** ANSYS Electronics Desktop

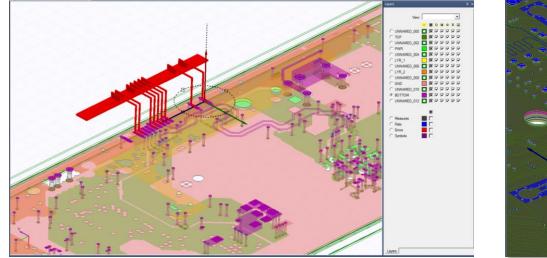

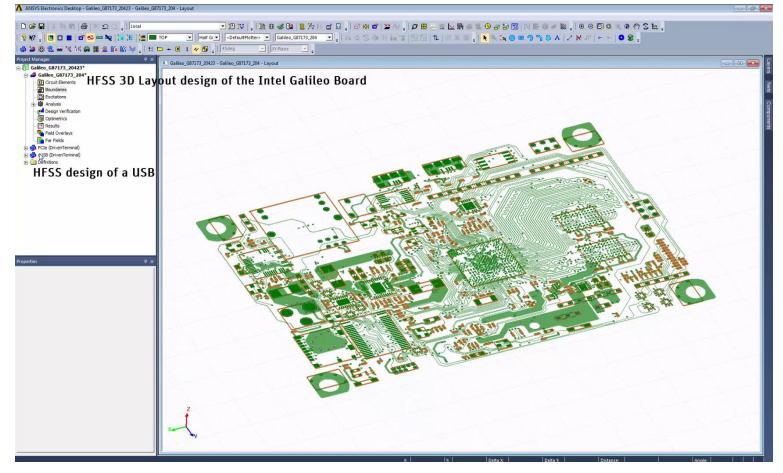

### **ANSYS** HFSS 3D Layout

### HFSS interface optimized for layout designs

### **Stackup editor**

Trace, pads, vias bond wires, solder bumps and balls Same 3D accuracy of HFSS in automated design flow

### **Layout Driven Assembly**

#### Fluid Dynamics

**Structural Mechanics**

Electromagnetics

Systems and Multiphysics

### **ANSYS** From Schematic Capture to Layout Driven Assembly

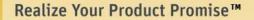

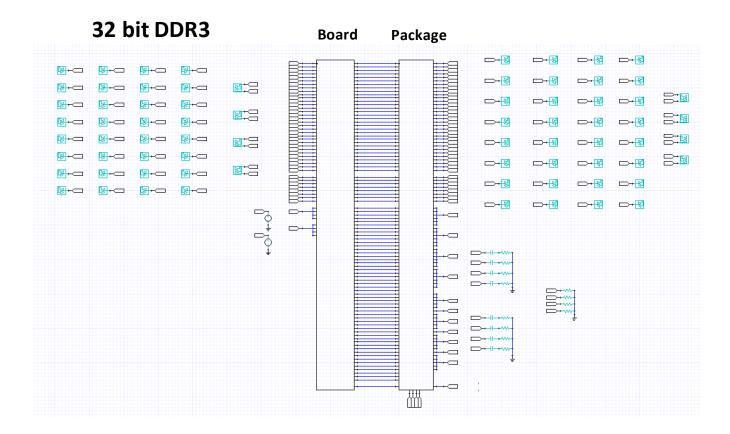

### The old way of analyzing a package system plus a board

Challenge: requires the use of 2-3 software packages

Next step: make a design change

Next step challenges:

- Keep track of touchstone revs

- Making changes to SIwave design (no variables)

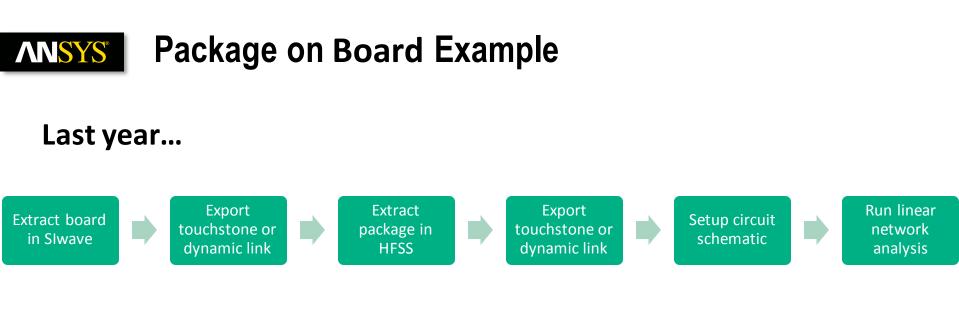

Benefit: requires the use 1 software package (Electronics Desktop)

Next step: make a design change

**Benefits:**

- No need to keep track of touchstone revs

- Layout interface enables parametric SIwave designs

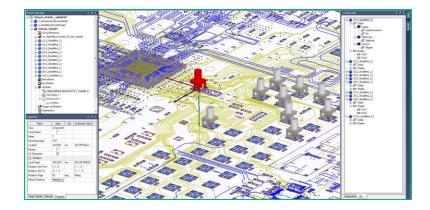

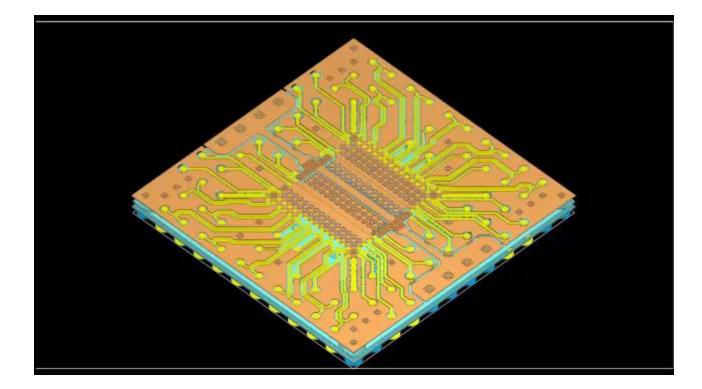

### Layout-Driven Assembly in ANSYS Electronics Desktop

Place and connect components in Layout Simulate components with 3D accuracy

ECAD and MCAD HFSS, Slwave, Q3D

Apply automated circuit simulation to capture full system behavior

#### **Ease-of-use drive 3D simulation for design engineers**

### **ANSYS** Layout Driven Assembly

Reducing hands on engineering time

Eliminate error prone system wiring

### **ANSYS** Virtual System Analysis with HFSS & SIwave

- Assemble ECAD & MCAD

- Select appropriate solver

- HFSS, SIwave or PlanarEM

- Connect TX/RX up within

Schematic circuit analysis

- LNA

- IBIS & IBIS-AMI

- QuickEye & VerifEye

- HSPICE\*

- PSPICE\*\*

\*HSPICE solver requires Synopsys license; Nexxim supports HSPICE syntax

\*\* Uses Nexxim solver with PSPICE syntax

### **ANSYS 3D Layout: Key Features**

- HFSS 3D Dynamic Link in Layout

- 3D Placement and Positioning

- Improved Capacity and Layout Rendering

|             |               |            | Vendor | Series | Part Name | Value     |

|-------------|---------------|------------|--------|--------|-----------|-----------|

| Component I |               |            | 77     | 7      | 7         |           |

| art Name:   | RES_0201_10.0 | <_R0201_11 | AVX    | 0201   | 02013A0R5 | 5e-013F   |

| art Type:   | Resistor      |            | AVX    | 0201   | 02013A100 | 1e-011F   |

| ef Des:     | R608          |            | AVX    | 0201   | 02013A120 | 1.2e-011F |

| lo. Pins:   | 2             |            | AVX    | 0201   | 02013A150 | 1.5e-011F |

|             | 1             |            | AVX    | 0201   | 02013A180 | 1.8e-011F |

| Model Info  |               |            | AVX    | 0201   | 02013A1R0 | 1e-012F   |

| Type:       | Library       |            | AVX    | 0201   | 02013A1R2 |           |

|             | Library       |            | AVX    | 0201   | 02013A1R5 |           |

|             |               | E dit      | AVX    | 0201   | 02013A1R8 |           |

|             |               |            | AVX    | 0201   | 02013A220 | 2.2e-011F |

|             |               |            |        |        | ОК        | Cance     |

Slwave technology for large PCBs and packages

- SYZ Solver

- Geometry Checks

#### Linear Network Analysis for Co-simulation

- LNA Setup and automated Net listing

- Component Models

Realize Your Product Promise™

## HFSS 3D Workflow Enhancements

**Fluid Dynamics**

**Structural Mechanics**

Electromagnetics

Systems and Multiphysics

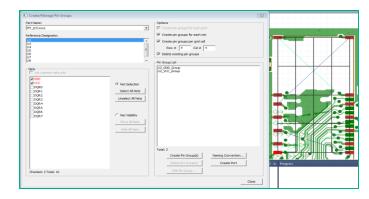

• .Net utility written to highlight layout automation

</com

- Can be run with or without GUI

- Starts from .mcm or .brd

| Nets Extents Cor | mponents Anal | ysis Options   |           |            | Import |                   |             |          |            | G\fga4     |

|------------------|---------------|----------------|-----------|------------|--------|-------------------|-------------|----------|------------|------------|

| Name             |               | Import         | Ports     | Pwr/Gnd    | Nets   |                   |             | a Analys | is Options | 1          |

| A-MII-RXD0       |               | $\checkmark$   | ✓         |            |        |                   | Component   |          | option in  |            |

| A-MII-RXD1       |               |                | 1         |            | Туре   |                   | Conf        | omal     | Boundr     | an Bay     |

| A-MII-RXD2       |               |                | 1         |            |        | r.<br>or/Distanci |             |          | . 00010    | g bux      |

| A-MII-RXD3       |               |                | ✓         |            |        |                   |             |          |            |            |

| GND              |               | V              |           | 7          |        | Round Corr        | iers        |          |            |            |

|                  |               |                |           |            | Airbe  | x/Dielectri       | cs          |          |            |            |

|                  |               |                |           |            |        | adiation B        |             |          |            |            |

|                  |               |                |           |            | x      | 1                 | Conf        | omal     | Boundir    | ng Bax     |

| ort Output       |               |                |           |            |        | ctric             |             |          |            |            |

| s Extents Con    | nponents An   | alysis         |           |            |        | tontal Pa         | dding: 0    |          |            |            |

|                  |               | formation      |           |            |        | x                 |             |          |            | _          |

| :52              | _             | Part Name:     | EDGA YOU  | V FF784 FB | GA'    |                   | dding: 0    |          |            |            |

| 53               |               |                |           | V_FF704_FD |        | rtical            |             |          |            |            |

| 1                |               | Part Type:     | IC        |            | •      | sitive Pa         | dding: 0.0  | 5        |            | sync sync  |

| 113              |               | Ref Des:       | U13       |            |        | gative P          | adding: 0.0 | 5        |            |            |

| 1                |               | No. Pins:      | 718       |            |        |                   |             |          |            |            |

| 2                |               |                |           |            |        |                   |             |          |            |            |

| 3                | -0            | ie Properties) |           |            |        |                   |             |          |            |            |

| 4                |               | Гуре:          | Flip chip |            | •      |                   |             |          |            |            |

| 5                |               | Drientation:   | Chip dow  | m ·        | - I I  |                   |             |          |            |            |

| 6                |               | leight:        | 0         |            |        |                   |             |          |            |            |

| 7                |               | neight.        | U         |            |        |                   |             |          |            |            |

| ets selected     |               |                |           |            |        |                   |             |          | _          |            |

|                  |               |                |           |            |        |                   |             |          |            | Export Clo |

|             | Import Output                                                                               |          |

|-------------|---------------------------------------------------------------------------------------------|----------|

|             | Nets Extents Components Analysis Options                                                    |          |

|             | Frequency: 10GHz                                                                            |          |

|             | Adaptive Solution                                                                           |          |

|             |                                                                                             |          |

|             | Maximum Number of Passes: 10                                                                |          |

|             | Maximum Delta S: 0.02                                                                       |          |

|             |                                                                                             |          |

|             | Minimum Number of Passes: 1                                                                 |          |

|             | Minimum Converged Passes: 1                                                                 |          |

|             | Solver Options                                                                              |          |

|             | Order of Basis Functions: Moved Order -                                                     |          |

|             | Enable Iterative Solver                                                                     |          |

|             | Relative Residual: 0.0001                                                                   |          |

|             | Frequency Sweep                                                                             |          |

|             | Type Range                                                                                  |          |

|             | O None Type: Linear Step ▼                                                                  |          |

|             | Discrete Start: 0                                                                           |          |

|             |                                                                                             |          |

| Tatte://w   | **************************************                                                      |          |

| ATTRICC.    | 1.0">                                                                                       |          |

|             | ts with specific models><br>" Type="Resistor" 55 Value="2Sohs" 51 Value="0.1nff" />         |          |

|             | 1505A" Type="Caperitor" SC Value="100mF" SE Value="0.1obm" />                               |          |

| tors should | d just be set to Other type, which requires setting to "Discrete" here. This allows for ea  | ay ports |

|             | **Discrete*/>                                                                               |          |

| Lett not m  | atobing above filters will get whatever values might be present in the Cadence files, if an | y>       |

|             |                                                                                             |          |

|             |                                                                                             |          |

|             | Spir"fales" EnableDefaultComponentValues"fales"/>                                           |          |

#### **Simulation Democratization**

- Time is best spent in design exploration and results analysis

- Unfortunately, a lot of time is spent preparing the model for simulation

- Automation of pre-processing would free up more of the engineer's time for design innovation

Realize Your Product Promise™

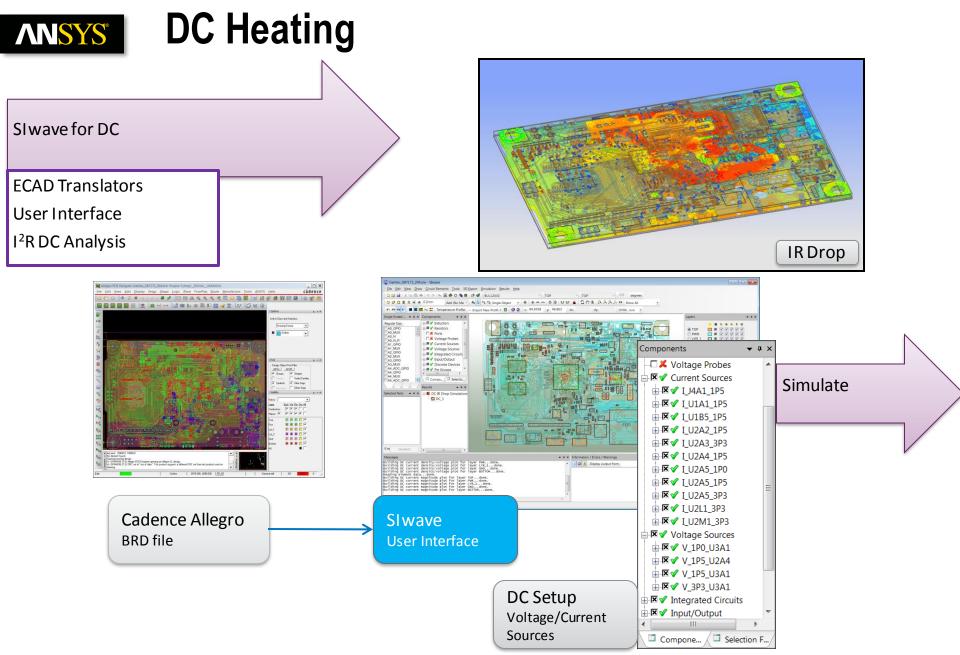

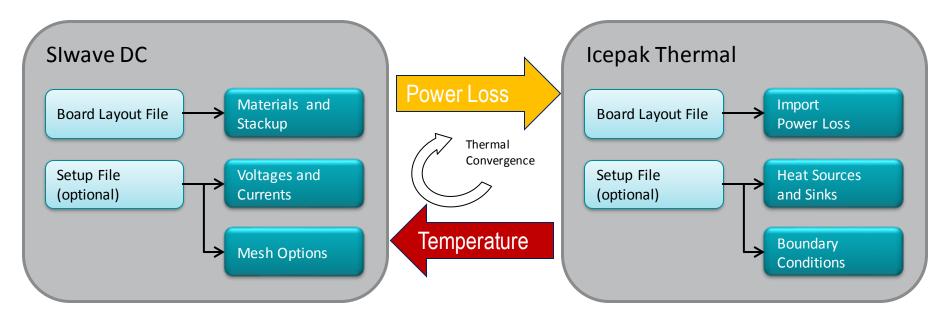

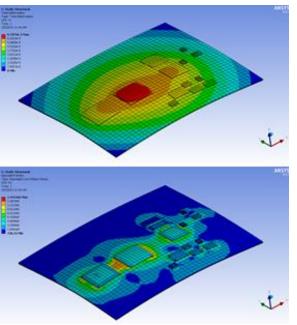

## **Multiphysics Board Analysis**

Fluid Dynamics

**Structural Mechanics**

Electromagnetics

Systems and Multiphysics

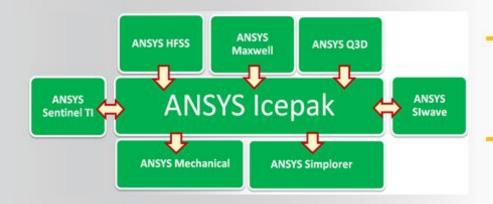

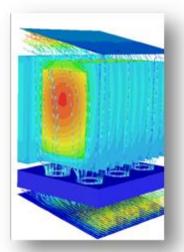

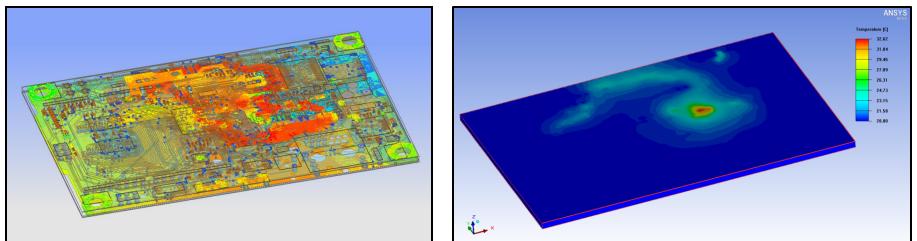

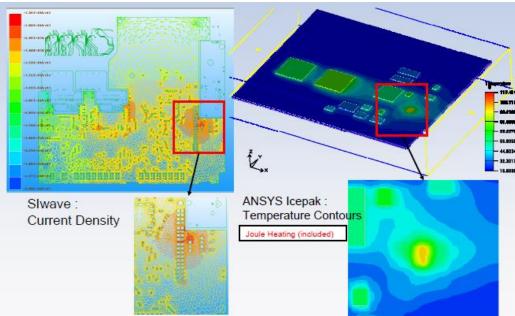

# ANSYS ANSYS Icepak

#### **Solver Validated by Experts**

ANSYS Icepak uses ANSYS Fluent as the solver engine, which is recognized as the market leader for both speed and accuracy of CFD

### **Customized for Thermal Management**

ANSYS Icepak contains a streamlined user interface with "smart objects" to rapidly create models of electronics assemblies

### Coupling Electromagnetics, Mechanical & Thermal Simulations

ANSYS Icepak can be connected to ANSYS mechanical or electromagnetic simulation solutions inside the Workbench environments to simulate the complete performance of a product

# **Two-way coupled Thermal Heating**

# **ANSYS** ANSYS Solutions for Pkg/PCB

### **Thermal Management Design Challenges**

- Thermal impact to IC

- Electric / Thermal Co-Analysis for PKG/PCB

- Automation of pre-processing would free up more of the engineer's time for design innovation

- Thermal impact for mechanical stress

- Optimization of power, weight, and thermal design requirements

Electrical / Thermal Co-Simulation

Thermal / Mechanical Co-Simulation

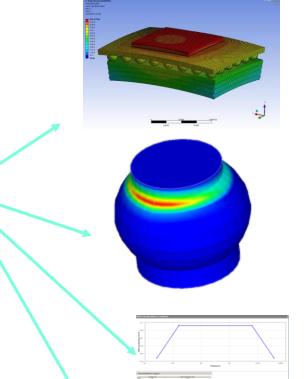

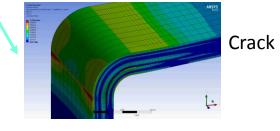

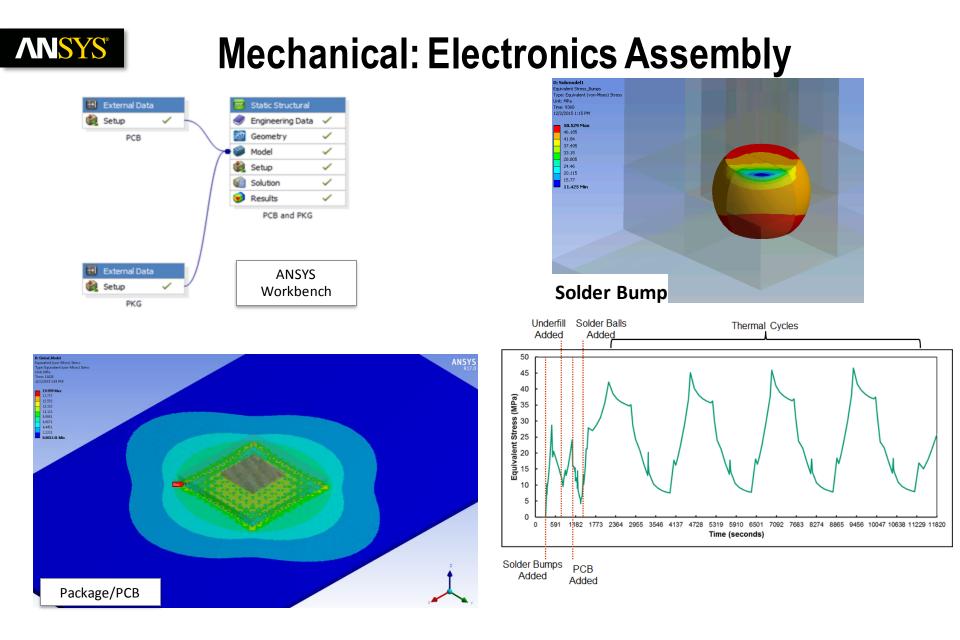

# **ANSYS** Mechanical Reliability

- ANSYS Mechanical can be used to predict stresses and deformation in the package during

- Flip Chip Attachment

- Crack Initiation and Crack Growth

**ANSYS**

**Mechanical**

- Thermal Cycling

- Solder Joint Reliability

- Shock Analysis

Layout Tool\*

Flip chip Attachment

Solder Joint Reliability

> Shock Analysis

Realize Your Product Promise™

## **Slwave Workflow Enhancements**

**Fluid Dynamics**

**Structural Mechanics**

Electromagnetics

Systems and Multiphysics

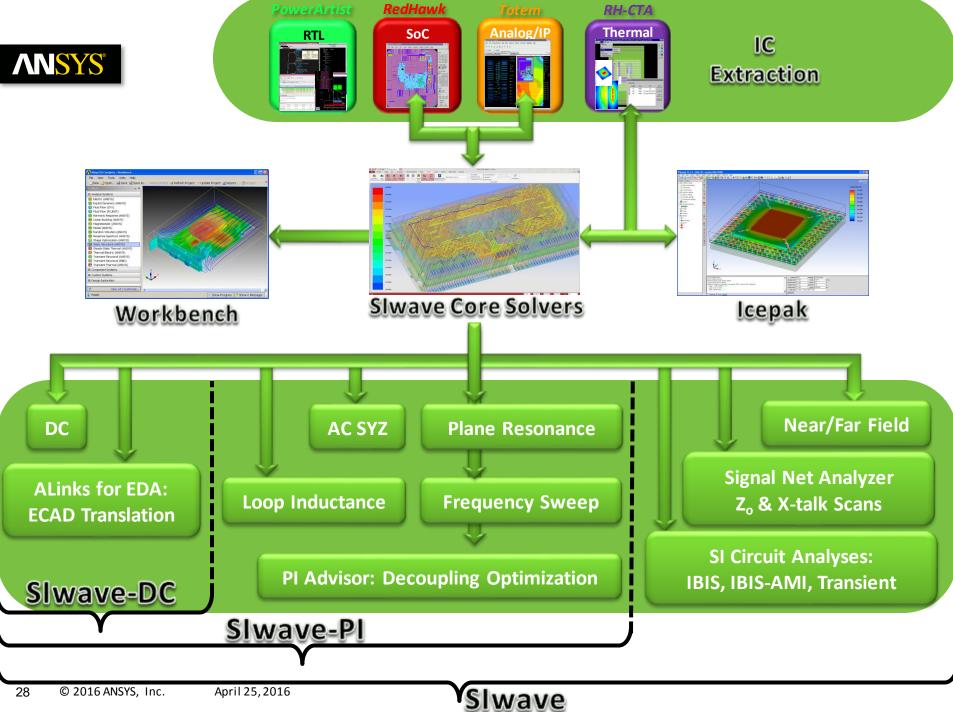

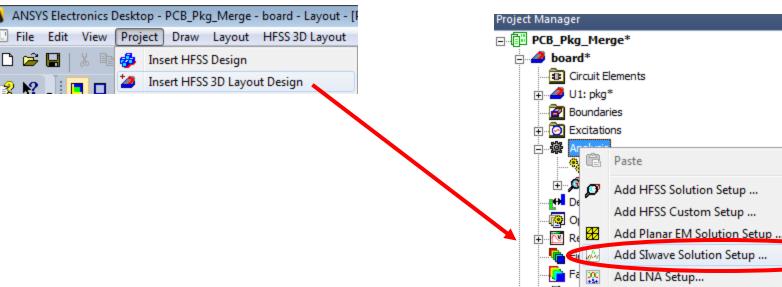

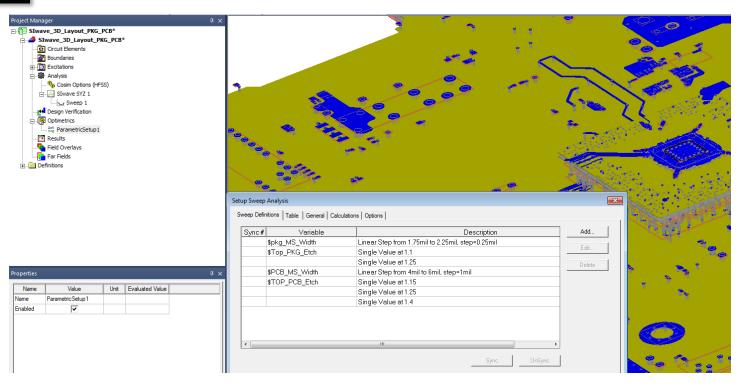

# **ANSYS** Slwave SYZ Solver Integration into AEDT 3D Layout

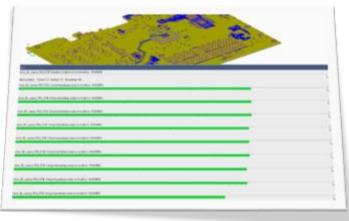

Slwave Solution Setups are now part of ANSYS Electronics Desktop 3D Layout

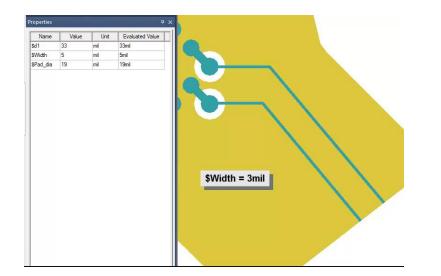

**Enables parametric solves**

**Enables usage of Electromagnetics RSM**

#### **Insert HFSS 3D Layout Design**

#### Add SIwave AC SYZ Solution

Ctrl+V

# **ANSYS** Slwave SYZ Solver Integration into AEDT 3D Layout

Slwave Solution Setups are now part of ANSYS Electronics Desktop 3D Layout

**Enables parametric solves**

Enables usage of Electromagnetics RSM so that jobs can be submitted to a cluster

| PCB_Pkg_Merge - board - Layout] |   |   |                          |

|---------------------------------|---|---|--------------------------|

| Tools Window Help               |   |   |                          |

| Edit Libraries                  | ۲ |   | 0: 🥩 🖋 🕼 🔡 📴 🕂 🖬 🖬       |

| Library Tools                   | ۲ |   | oard 💽 🔤 👍 🚭             |

| Project Tools                   | ۲ |   | Plane                    |

| Run Script                      |   |   |                          |

| Pause Script                    |   |   |                          |

| Record Script To File           |   |   |                          |

| Record Script to Project        |   |   |                          |

| Open Command Window             |   |   |                          |

| Password Manager                |   |   |                          |

| Options                         | × |   | General Options          |

| Keyboard Shortcuts              |   | ų | HPC and Analysis Options |

| Customize                       |   |   | Export Options Files     |

| E. 17.1                         |   |   |                          |

| [PCB_Pkg_Merge - board - Layout]                                                                                                                        |                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| Tools Window Help                                                                                                                                       |                                     |

| Edit Libraries<br>Library Tools<br>Project Tools<br>Run Script<br>Pause Script<br>Record Script To File<br>Record Script To File<br>Open Command Window | → 目 御 <b>父 父 隆</b> 玲 水<br>→   board |

| Password Manager<br>Options<br>Keyboard Shortcuts<br>Customize<br>External Tools                                                                        | ,                                   |

| <ul> <li>Show Queued Simulations</li> <li>Edit Active Analysis Configurat</li> <li>Import Array from Table</li> </ul>                                   | ion                                 |

| Job Management                                                                                                                                          | Select Scheduler                    |

| Calibration Wizard<br>Network Data Explorer<br>PEmag                                                                                                    | Submit Job<br>Monitor Jobs          |

| HPC and Analysis Options                                                              | X                                                                                 | Analysis Configuration                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configurations Options Design Type: 2 HFSS 3D Layout Design Available Configurations: | Configuration Details:  Make Active Configuration Name:  Local  Add Machine List: | Configuration name: Local<br>The local and interactive job configurations<br>(7 Use Automatic Scittings<br>Machines   Job Distribution   Options  <br>Machines for Distributed Analysis<br>Total Enabled Tasks: 12 Total Enabled Cores: 12<br>Name Tasks   Cores   RAM Link (10) Enabled Remove |

| -                                                                                     | Edit                                                                              | Move som<br>Machine Details:                                                                                                                                                                                                                                                                    |

|                                                                                       | OK Cancel                                                                         | C DNS Name format: www.server.com):     C UNC Name (format: \\server):     Import Machines from File     Add Machine to List                                                                                                                                                                    |

### **ANSYS**<sup>®</sup>

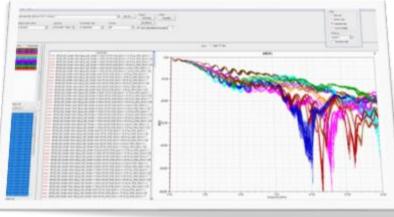

### **Slwave Parametric Design within AEDT 3D Layout**

### **ANSYS** What is Slwave-CPA?

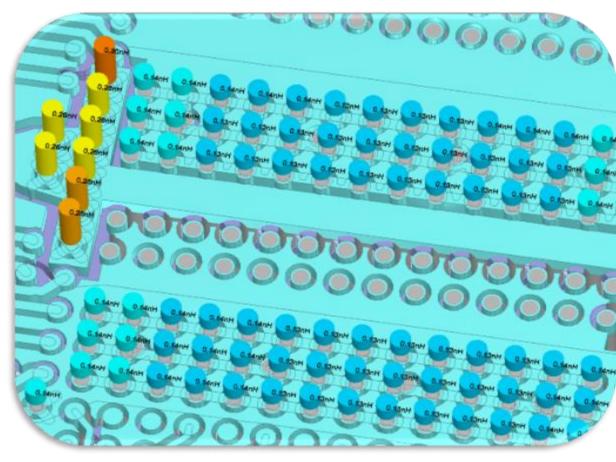

The CPA (Chip-Package-Analysis) solver is a 3D full-wave, FEM based solver for fast and accurate extraction of RLC parasitics.

It is optimized to analyze power and signal nets on packages

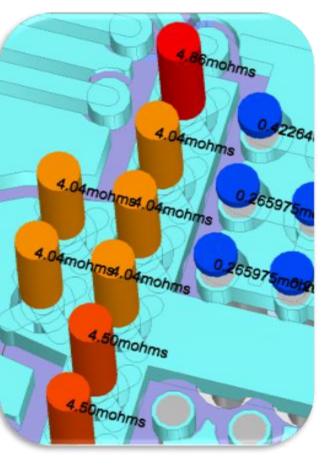

### **ANSYS** Slwave-CPA

- Automated .html reporting for partial and loop resistance/inductance

- The CPA solver is capable of producing per bump/ball resolution RLC extracted parasitics

- Visual Bar graph plotting is available for solderball/bump and Pin Groups

| Solver       | Net   | R<br>(mΩ) | L<br>(nH) | C<br>(pF) | Solve Time<br>(minutes) | Speed<br>Up | RAM<br>(MB) | RAM<br>Reduction |

|--------------|-------|-----------|-----------|-----------|-------------------------|-------------|-------------|------------------|

| Q3D<br>(TPA) | PDN A | 12.3      | 310.6     | 24.8      | 4.51                    | -           | 748         | -                |

| CPA          | PDN A | 12.9      | 312.4     | 25.8      | 0.4                     | 11x         | 210         | 4x               |

|              |       |           |           |           |                         |             |             |                  |

| Q3D<br>(TPA) | PDN B | 9.1       | 224.8     | 24.8      | 4.51                    | -           | 748         | -                |

| CPA          | PDN B | 9.2       | 230.7     | 25.9      | 0.4                     | 11x         | 210         | 4x               |

#### Flip-Chip PDN System

**Slwave-CPA**

#### Wirebond Package PDN System

| Solver       | Net   | R<br>(mΩ) | L<br>(pH) | C<br>(pF) | Solve Time<br>(Hours) | Speed<br>Up | RAM<br>(GB) | RAM<br>Reduction |

|--------------|-------|-----------|-----------|-----------|-----------------------|-------------|-------------|------------------|

| Q3D<br>(TPA) | PDN C | 1.58      | 79.2      | 128.4     | 48                    | -           | 71          | -                |

| CPA          | PDN C | 1.61      | 79.9      | 129.3     | 0.1                   | 480x        | 13          | 5x               |

|              |       |           |           |           |                       |             |             |                  |

| Q3D<br>(TPA) | PDN D | 0.16      | 12.6      | 973.4     | 48                    | -           | 71          | -                |

| CPA          | PDN D | 0.16      | 12.9      | 979.3     | 0.1                   | 480x        | 13          | 5x               |

#### Coupled Microstrip Lines

| Solver | Net     | R<br>(mΩ) | L<br>(nH) | C<br>(pF) | Solve Time<br>(Minutes) | Speed<br>Up | RAM<br>(MB) | RAM<br>Reduction |

|--------|---------|-----------|-----------|-----------|-------------------------|-------------|-------------|------------------|

| NPE    | Trace A | 386       | 3.42      | 1.17      | 3.0                     | -           | 450         | _                |

| CPA    | Trace A | 386       | 3.22      | 1.17      | 1.0                     | 3х          | 300         | 3x               |

|        |         |           |           |           |                         |             |             |                  |

| NPE    | Trace B | 386       | 3.44      | 1.19      | 3.0                     | _           | 450         | _                |

| CPA    | Trace B | 386       | 3.30      | 1.17      | 1.0                     | 3х          | 300         | 3х               |

# **ANSYS** Slwave-Q3D (TPA) Improvements

Added DC Adaptive Meshing

Added the ability to use Pin Groups with Q3D (TPA) solver

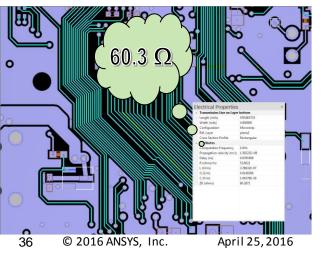

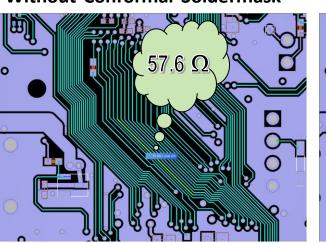

## **ANSYS** Slwave Conformal Soldermasks

|                                         | Color                          | Name                                                                                         | Туре                                    |      | 🖓 Material                       | Conductivity (S/m)        | 猗 Dielectric Fill                     | Dielectric constant | Loss tangent | Translucency | Elevation (mils) | Roughness (mi |

|-----------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------|------|----------------------------------|---------------------------|---------------------------------------|---------------------|--------------|--------------|------------------|---------------|

|                                         |                                | Top_Conformal_SM                                                                             | CONFORMAL COAT                          |      | SolderMask                       | 0                         |                                       |                     | 0.035        |              | 64.5             |               |

|                                         |                                | top                                                                                          | METAL                                   | 1.1  | EDB_copper                       | 5.8E+07                   | SolderMask                            |                     |              |              | 63.4             | HJ: 0 , HJ:   |

|                                         |                                | Dielectric_1                                                                                 | DIELECTRIC                              | 4    | EDB_FR4_epoxy                    | 0                         |                                       |                     | 0.02         |              | 59.4             |               |

|                                         |                                | plane1                                                                                       | METAL                                   | 0.65 | EDB_copper                       | 5.8E+07                   | EDB_FR4_epoxy                         |                     |              |              | 58.75            | HJ: 0 , HJ:   |

| 201700000000000000000000000000000000000 |                                | Dielectric_2                                                                                 | DIELECTRIC                              | 52   | EDB_FR4_epoxy                    | 0                         |                                       |                     | 0.02         |              | 6.75             |               |

| 15115                                   |                                | plane2                                                                                       | METAL                                   | 0.65 | EDB_copper                       | 5.8E+07                   | EDB_FR4_epoxy                         |                     |              | 0            | 6.1              | HJ: 0 , HJ:   |

|                                         |                                | Dielectric_3                                                                                 | DIELECTRIC                              | 4    | EDB_FR4_epoxy                    | 0                         |                                       |                     | 0.02         |              | 2.1              |               |

|                                         |                                | bottom                                                                                       | METAL                                   | 1.1  | EDB_copper                       | 5.8E+07                   | SolderMask                            |                     | 0.000        | 0            | 1                | HJ: 0 , HJ:   |

|                                         |                                |                                                                                              |                                         |      |                                  |                           |                                       |                     |              |              |                  |               |

|                                         |                                | Bottom_Conformal_SM                                                                          | CONFORMAL COAT                          | 1    | SolderMask                       | 0                         |                                       | 3.1                 | 0.035        |              | 0                |               |

|                                         |                                |                                                                                              |                                         | 1    | SolderMask                       | 0                         |                                       | 3.1                 | 0.035        |              | 0                |               |

|                                         | Add / Del                      | lete / Move Layer(s)                                                                         | Edit Selected Layer(s)                  | 3)   | SolderMask                       | 0                         |                                       | 3.1                 | 0.035        |              | 0                |               |

|                                         | Add / Del                      |                                                                                              | Edit Selected Layer(s)                  |      | -                                |                           |                                       |                     | 0.035        |              | 0                |               |

|                                         | Add / Del<br>Add               | lete / Move Layer(s)                                                                         | Edit Selected Layer(s)<br>Color         |      | Update D                         | Nelectric Fill SolderMask |                                       | Update              | 0.035        |              | 0                |               |

|                                         | Add / Del<br>Add<br>Add        | iete / Move Layer(s)<br>Above Selected Layer<br>Below Selected Layer                         | Edit Selected Layer(s)                  |      | Update D                         |                           | • • • • • • • • • • • • • • • • • • • |                     | 0.035        |              | 0                |               |

|                                         | Add / Del<br>Add<br>Add<br>Dei | kete / Move Layer(s)<br>Above Selected Layer<br>Below Selected Layer<br>Jete Selected Layers | Edit Selected Layer(s)<br>Color The top |      | Update D<br>Update Tr            | Velectric Fill SolderMask | 0%                                    | Update Update       | 0.035        |              | 0                |               |

|                                         | Add / Del<br>Add<br>Add<br>Dei | iete / Move Layer(s)<br>Above Selected Layer<br>Below Selected Layer                         | Edit Selected Layer(s)<br>Color         | 464  | Update D<br>Update T<br>Update T | Velectric Fill SolderMask |                                       | Update              | 0.035        |              | 0                |               |

Single Ended Zo Without Trace-Trace Coupling Without Conformal Soldermask

Single Ended Zo With Trace-Trace Coupling Without Conformal Soldermask

Single Ended Zo With Trace-Trace Coupling With Conformal Soldermask

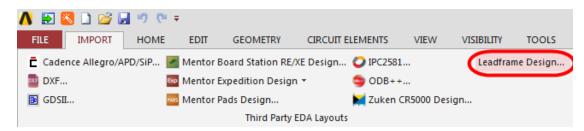

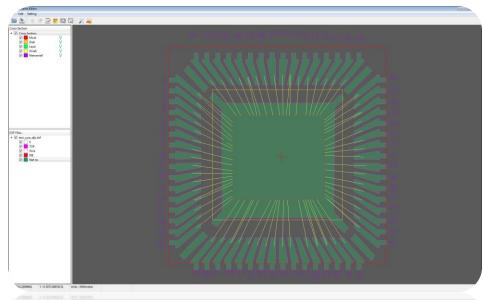

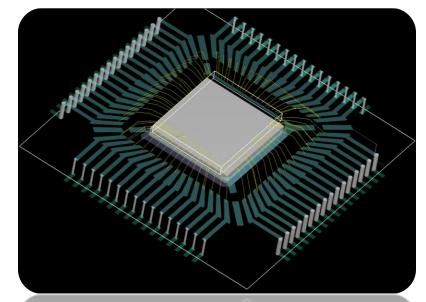

#### Lead Frame Editor

- Creates Slwave & 3D Layout .anf Geometries

- Creates HFSS & Q3D .sat Geometries

#### Lead Frame Editor

• Slwave QFP Package from Lead Frame Editor