# An Overview of High Performance Computing

Jack Dongarra

University of Tennessee

and

Oak Ridge National Laboratory

HPC As la 2005 Nov 30-Dec 3, 2005 Beijing, China

The 8th International Conference/Exhibition on

High Performance Computing in Asia-Pacific Region

# Overview

- Look at fastest computers

- >From the Top500

- Some of the changes that face us

- >Hardware

- >Software

- > Algorithms

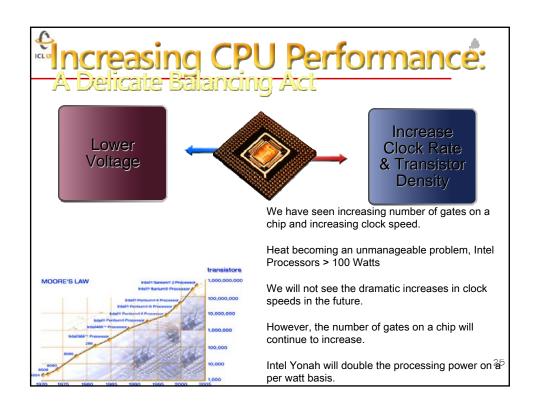

### Technology Trends: Microprocessor

Chip Capacity

# Gordon Moore (co-founder of Intel)

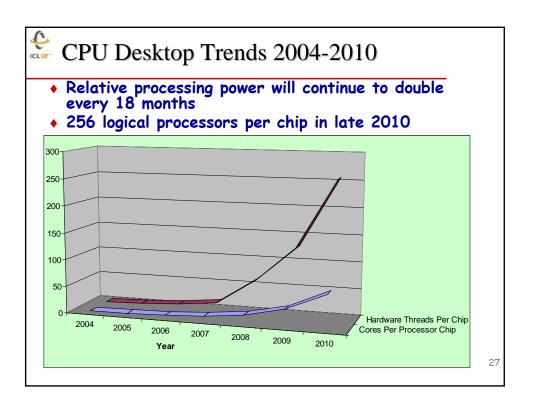

Electronics Magazine, 1965 Number of devices/chip doubles every 18 months

2X transistors/Chip Every 1.5 years "Moore's Law"

The experts look ahead

# Cramming more components onto integrated circuits

With unit cost falling as the number of components per circuit rises, by 1975 economics may dictate squeezing a many as 65,000 components on a single silicon chip

By Gordon E. Moore

Director, Research and Development Laboratories, Fairchild Semiconductor

The future of integrated electronics is the future of electronics itself. The advantages of integration will bring about a proliferation of electronics, pushing this science into many new areas.

Integrated circuits will lead to such wonders as home computers—or at least terminals connected to a central computer—automatic controls for automabiles, and personal portable communications equipment. The electronic wristwatch needs only a display to be feasible today.

But the biggest potential lies in the production of largsystems. In telephone communications, integrated circuits in digital filters will separate channels on multiplex equipment. Integrated circuits will also switch telephone circuits and perform data processing.

Computers will be more powerful, and will be organized in completely different ways. For example, memories built of integrated electronics may be distributed throughout the machine instead of being concentrated in a central unit.

addition, the improved reliability made possible by integrate circuits will allow the construction of larger processing unit Machines similar to those in existence today will be built lower costs and with faster turn-around.

#### Present and future

By integrated electronics, I mean all the various technologies which are referred to as increolectronics today as changed as the referred to a microelectronics today as tions supplied to the user as irreducible units. These techloogies were first investigated in the late 1950s. The object was to miniaturize electronic sequipment to include in creasingly complex electronic functions in limited packed with minimum weight. Several approaches evolved, including fill introduction and semiconduction integrated circuits.

Each approach evolved rapidly and converged so that each borrowed techniques from another. Many researchers believe the way of the future to be a combination of the various approaches.

already using the improved characteristics of thin-film resistors by applying such films directly to an active semiconductor substrate. Those advocating a technology based upon films are developing sophisticated techniques for the attachment of active semiconductor devices to the passive film arrays.

Both approaches have worked well and are being used in equipment today.

Electronics, Volume 38, Number 8, April 19, 1965

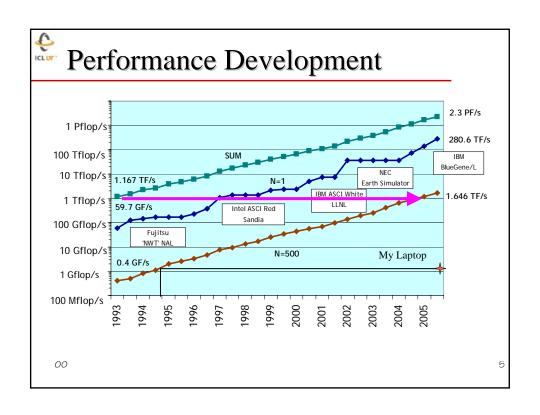

### H. Meuer, H. Simon, E. Strohmaier, & JD

- Listing of the 500 most powerful Computers in the World

- Yardstick: Rmax from LINPACK MPP

$$Ax=b$$

, dense problem

- Updated twice a year

SC'xy in the States in November

Meeting in Germany in June

- o₁ All data available from **www.top500.org**

t

| 26th List: The TOP10 |              |                                       |                |                                   |             |      |        |  |  |  |

|----------------------|--------------|---------------------------------------|----------------|-----------------------------------|-------------|------|--------|--|--|--|

|                      | Manufacturer | Computer                              | Rmax<br>[TF/s] | Installation Site                 | Country     | Year | #Proc  |  |  |  |

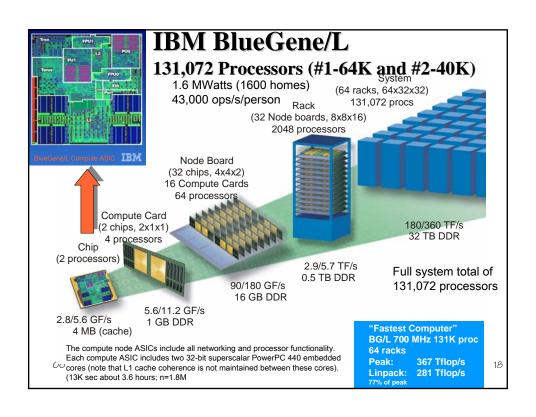

| 1                    | IBM          | BlueGene/L<br>eServer Blue Gene       | 280.6          | DOE/NNSA/LLNL                     | USA         | 2005 | 131072 |  |  |  |

| 2                    | IBM          | BGW<br>eServer Blue Gene              | 91.29          | IBM Thomas Watson                 | USA         | 2005 | 40960  |  |  |  |

| 3                    | IBM          | ASC Purple<br>Power5 p575             | 63.39          | DOE/NNSA/LLNL                     | USA         | 2005 | 10240  |  |  |  |

| 4                    | SGI          | Columbia<br>Altix, Itanium/Infiniband | 51.87          | NASA Ames                         | USA         | 2004 | 10160  |  |  |  |

| 5                    | Dell         | Thunderbird<br>Pentium/Infiniband     | 38.27          | Sandia                            | USA         | 2005 | 8000   |  |  |  |

| S<br>Q               | Cray         | Red Storm<br>Cray XT3 AMD             | 36.19          | Sandia                            | USA         | 2005 | 10880  |  |  |  |

| 7                    | NEC          | Earth-Simulator<br>SX-5               | 35.86          | Earth Simulator Center            | Japan       | 2002 | 5120   |  |  |  |

| 3                    | IBM          | MareNostrum<br>PPC 970/Myrinet        | 27.91          | Barcelona Supercomputer<br>Center | Spain       | 2005 | 4800   |  |  |  |

| 9                    | IBM          | eServer Blue Gene                     | 27.45          | ASTRON<br>University Groningen    | Netherlands | 2005 | 12288  |  |  |  |

| 0                    | Cray         | Jaguar<br>Cray XT3 AMD                | 20.53          | Oak Ridge National Lab            | USA         | 2005 | 5200   |  |  |  |

|                                              | Annual increase | Typical value in 2005               | Got Bandwidth |

|----------------------------------------------|-----------------|-------------------------------------|---------------|

| Single-chip<br>floating-point<br>performance | 59%             | 4 GFLOP/s                           |               |

| Front-side bus<br>bandwidth                  | 23%             | 1 GWord/s<br>= 0.25 word/flop       |               |

| DRAM latency                                 | (5.5%)          | 70 ns<br>= 280 FP ops<br>= 70 loads |               |

# Fault Tolerance: Motivation

- Trends in HPC:

- > High end systems with thousand of processors

- Increased probability of a node failure

Most systems nowadays are robust

- ◆ MPI widely accepted in scientific computing

➤ Process faults not tolerated in MPI model

Mismatch between hardware and (non fault-tolerant) programming paradigm of MPI.

00

29

### Reliability of Leading-Edge HPC Systems

| Sys | stem             | CPUs  | Reliability                                                                                                   |

|-----|------------------|-------|---------------------------------------------------------------------------------------------------------------|

|     | NL<br>CI Q       | 8,192 | MTBI: 6.5 hours. Leading outage sources: storage, CPU, memory.                                                |

|     | NL<br>CI White   | 8,192 | MTBF: 5.0 hours ('01) and 40 hours ('03).<br>Leading outage sources: storage, CPU, 3 <sup>rd</sup> -party HW. |

|     | tsburgh<br>mieux | 3,016 | MTBI: 9.7 hours.                                                                                              |

MTBI: mean time between interrupts = wall clock hours / # downtime periods MTBF: mean time between failures (measured)

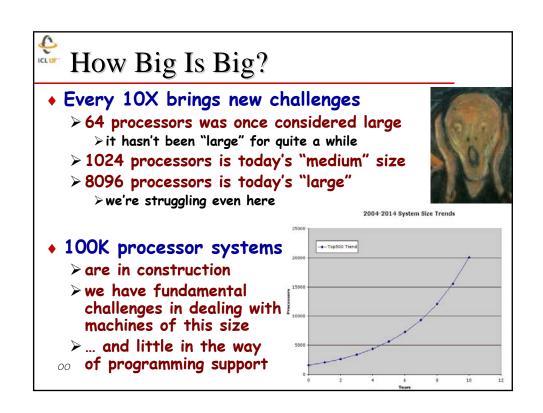

- 100K processor systems

- > are here

- we have fundamental challenges in dealing with machines of this size

- > ... and little in the way of programming support

# Future Challenge: Developing the Ecosystem for HPC

From the NRC Report on "The Future of Supercomputing":

- Hardware, software, algorithms, tools, networks, institutions, applications, and people who solve supercomputing applications can be thought of collectively as an ecosystem

- Research investment in HPC should be informed by the ecosystem point of view - progress must come on a broad front of interrelated technologies, rather than in the form of individual breakthroughs.

A supercomputer ecosystem is a continuum of computing platforms, system software, algorithms, tools, networks, and the people who know how to exploit them to solve computational science applications.

00

31

#### Real Crisis With HPC Is With The Software

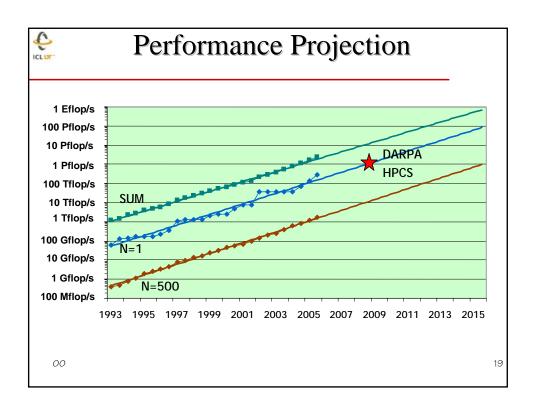

- Our ability to configure a hardware system capable of 1 PetaFlop (10<sup>15</sup> ops/s) is without question just a matter of time and \$\$.

- A supercomputer application and software are usually much more long-lived than a hardware

- > Hardware life typically five years at most.... Apps 20-30 years

- > Fortran and C are the main programming models (still!!)

- The REAL CHALLENGE is Software

- > Programming hasn't changed since the 70's

- > HUGE manpower investment

- > MPI... is that all there is?

- > Often requires HERO programming

- > Investments in the entire software stack is required (O5, libs, etc.)

- Software is a major cost component of modern technologies.

- > The tradition in HPC system procurement is to assume that the software is free... SOFTWARE COSTS (over and over)

00

00

# Summary of Current Unmet Needs

- Performance / Portability

- Fault tolerance

- Memory bandwidth/Latency

- Adaptability: Some degree of autonomy to self optimize, test, or monitor.

- > Able to change mode of operation: static or dynamic

- Better programming models

- > Global shared address space

- > Visible locality

- Maybe coming soon (incremental, yet offering real benefits):

- Global Address Space (GAS) languages: UPC, Co-Array Fortran, Titanium, Chapel)

- > "Minor" extensions to existing languages

- > More convenient than MPI

- Have performance transparency via explicit remote memory references

# EL DE

# **Next Steps**

- Software to determine the checkpointing interval and number of checkpoint processors from the machine characteristics.

- > Perhaps use historical information.

- > Monitoring

- > Migration of task if potential problem

- Local checkpoint and restart algorithm.

- > Coordination of local checkpoints.

- > Processors hold backups of neighbors.

- Have the checkpoint processes participate in the computation and do data rearrangement when a failure occurs.

- > Use p processors for the computation and have k of them hold checkpoint.

- Generalize the ideas to provide a library of routines to do the diskless check pointing.

- Look at "real applications" and investigate "Lossy" algorithms.

00

# Real Crisis With HPC Is With The Software

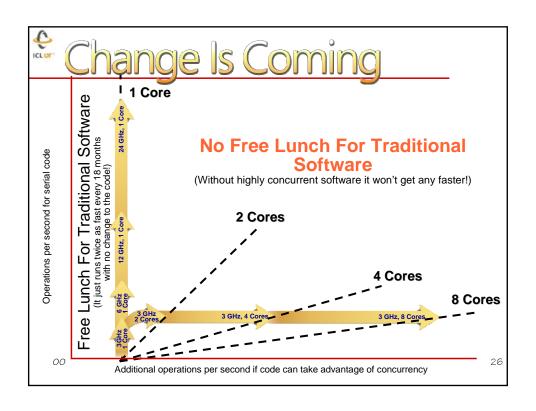

- Programming is stuck

- > Arguably hasn't changed since the 60's

- It's time for a change

- > Complexity is rising dramatically

- > highly parallel and distributed systems

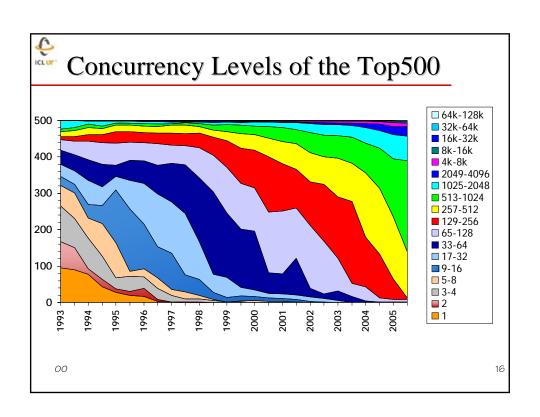

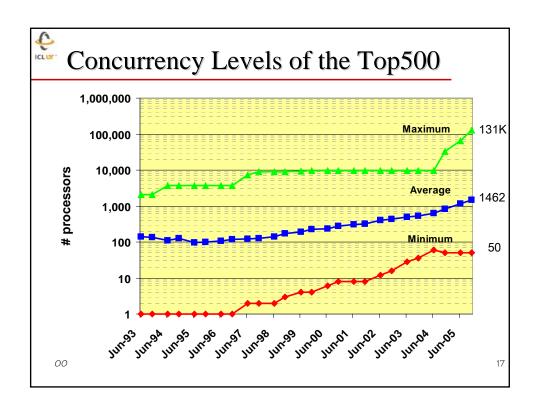

- From 10 to 100 to 1000 to 10000 to 100000 of processors!

- > multidisciplinary applications

- A supercomputer application and software are usually much more long-lived than a hardware

- > Hardware life typically five years at most.

- > Fortran and C are the main programming models

- Software is a major cost component of modern technologies.

- > The tradition in HPC system procurement is to assume that the software is free.

- $\bullet$  We have too few ideas about how to solve this  $_{oo}$  problem.

# P

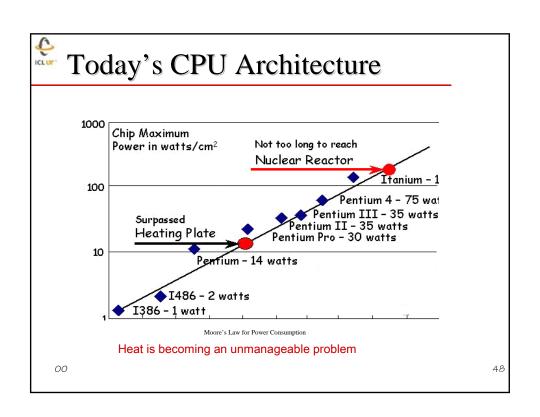

# Today's Processors

- pipelining (superscalar, OOO, VLIW, branch prediction, predication)

- simultaneous multithreading (SMT, Hyper-Threading, multi-core)

- SIMD vector instructions (VIS, MMX/SSE, AltiVec)

- caches and the memory hierarchy

- Intel added 36 instructions per year to IA-32, or 3 instructions per month!

00

00

# Self Adapting Numerical Software

- The process of arriving at an efficient solution involves many decisions by an expert.

- > Algorithm decisions

- > Data decisions

- Management of the computing environment

- > Processor specific tuning

Complex set of interaction between

Users' applications

Algorithm

Programming language

Compiler

Machine instruction

Hardware

Many layers of translation from the application to the hardware. Changing with each generation of hardware.

Proceedings of the IEEE, V: 93 #: 2 Feb. 2005 Issue on Program Generation, Optimization, and Platform Adaptation