# AN1131: Design Guide for Reducing Radiated and Conducted Emissions in Isolated Systems Using Silicon Labs' Isolators

Silicon Labs isolators are designed for minimal radiated and conducted emissions, enabling systems to meet stringent standards such as FCC Part 15, CISPR 32, and CISPR 25.

All electronic circuits generate some level of radiated and conducted emissions. If these emission levels are excessive, they may interfere with the operation of nearby or electrically connected equipment. Therefore, designers must be careful to minimize emission levels from their circuits to ensure the electromagnetic compatibility of their designs.

Meeting conducted and radiated emissions standards can be both challenging and costly if not considered early in the design cycle. Component selection and printed circuit board (PCB) design are key to reducing emissions and achieving first pass success for a given standard's profile. This design guide begins by identifying and classifying sources of radiated and conducted emissions in an isolated system and then proposes various techniques to attenuate these emissions. These discussions are followed by two case studies wherein emission reduction techniques are applied to circuit board designs that utilize the Si88241 isolator. The first case study addresses radiated emissions, and the second case study addresses conducted emissions. The effectiveness of these techniques are judged using CISPR 25 radiated and conducted emissions measurement techniques, respectively.

#### KEY POINTS

- EMC standards limit the amount of radiated and conducted emissions that can be generated by various types of electrical/ electronic equipment.

- Silicon Labs isolators are designed for minimal radiated and conducted emissions to help meet FCC Part 15, CISPR 32, and CISPR 25 standards.

- Galvanic isolation between circuits can result in additional electromagnetic coupling and emissions challenges.

- This design guide describes techniques for reducing the levels of radiated and conducted emissions in equipment that employs galvanic isolation.

## **Table of Contents**

| 1. |                                                                                                                                            | . 4  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------|------|

|    | 1.1 EMI, EMC, Radiated and Conducted Emissions, Radiated and Conducted Immunity, Coupling, and Crosstalk                                   |      |

|    | 1.2 Differential-Mode and Common-Mode Currents                                                                                             | . 6  |

|    | 1.3 Magnetic and Electric Fields, Near and Far Fields, Wave Impedance, Loop and Electric Dipole Radiators, and Antenna Reciprocity         | . 8  |

|    | 1.4 General Guidelines for Minimizing Radiated and Conducted Emissions                                                                     | . 9  |

| 2. | Radiated and Conducted Emission Standards                                                                                                  | . 10 |

|    | 2.1 IEC CISPR EMC Standards                                                                                                                | .11  |

|    | 2.2 IEC CISPR 25                                                                                                                           | .12  |

|    | 2.3 IEC CISPR 32                                                                                                                           | .13  |

|    | 2.4 FCC Title 47, Part 15, Subpart B                                                                                                       |      |

| 3. | Isolated Systems and Electromagnetic Compatibility (EMC)                                                                                   | 14   |

| 4. | Silicon Labs Isolators Are Designed to Minimize Radiated Emissions                                                                         | . 15 |

| 5. | Choosing the Best Silicon Labs Isolator Option to Reduce Emissions for a Given RF                                                          |      |

|    | Transmitter Duty Cycle                                                                                                                     | .16  |

| 6. | Techniques for Reducing Emissions from Differential-Mode Currents                                                                          | . 18 |

|    | 6.1 Selecting Proper Bypass Capacitors.                                                                                                    | .18  |

|    | 6.2 Choosing the Proper Bypass Capacitor Placement                                                                                         | .19  |

|    | 6.3 Adding Embedded Bypass Capacitor Structures for Multilayer PCBs                                                                        | .20  |

|    | 6.4 Terminating Transmission Lines                                                                                                         | .21  |

| 7. | Techniques for Reducing Emissions from Common-Mode Currents                                                                                | 22   |

|    | 7.1 Adding Capacitance Between Power Domains                                                                                               | .23  |

|    | 7.2 Using Common-Mode Chokes to Reduce Emissions                                                                                           | .25  |

| 8. | Controlling Emissions in Designs using Digital Isolators with Integrated DC-DC Controllers                                                 | 27   |

|    | 8.1 Primary-Side Loop Currents                                                                                                             | .28  |

|    | 8.2 Secondary-side Loop Currents                                                                                                           | .28  |

|    | 8.3 Using Secondary-Side Snubber Circuit to Reduce Emissions Due to Ringing                                                                | .29  |

| 9. | Case Study 1: CISPR 25 Radiated Emissions for an Si88241 Design                                                                            | 31   |

| 10 | ). Case Study 2: CISPR 25 Conducted Emissions for an Si88241 Design                                                                        | . 33 |

|    | 10.1 Conducted Emissions Measurements without any Added EMC Components                                                                     | .34  |

|    | 10.2 The Y Capacitor                                                                                                                       | .35  |

|    | 10.3 Further Optimization                                                                                                                  | .35  |

|    | 10.3.1 Overlapping Inner Ground Planes and Optimized PCB Layout                                                                            |      |

|    | 10.3.2 Optimized Snubber Design       10.3.2 Optimized Snubber Design         10.3.3 Lower Capacitance Transformer       10.1.1 Intervalue |      |

|     | 10.3.4 Common Mode Choke on the Input        | 3 |

|-----|----------------------------------------------|---|

|     | 10.4 Optimized Board First Pass Test Results | 7 |

| 11. | Summary                                      | ) |

| 12. | References                                   | ) |

| 13. | Document Change List                         | 1 |

## 1. Introduction

The first section of this design guide provides a very high-level introduction to some of the concepts associated with electromagnetic interference (EMI) and electromagnetic compliance (EMC). Although detailed discussions of these topics are beyond the scope of this document, the goal is to introduce the concepts and make the techniques presented in the subsequent sections more intuitive. For more information about EMI and EMC topics, see Section 12. References.

Section 2. Radiated and Conducted Emission Standards provides an introduction to EMC standards. Section 3. Isolated Systems and Electromagnetic Compatibility (EMC) discusses how isolation of circuits and power domains within equipment can effect emissions. Section 4. Silicon Labs Isolators Are Designed to Minimize Radiated Emissions explains how Silicon Labs isolator products are designed to minimize emissions, and Section 5. Choosing the Best Silicon Labs Isolator Option to Reduce Emissions for a Given RF Transmitter Duty Cycle provides guidance on selection of Silicon Labs isolators based on signal duty cycle.

Section 6. Techniques for Reducing Emissions from Differential-Mode Currents and Section 7. Techniques for Reducing Emissions from Common-Mode Currents discuss general methods for reducing emissions from common-mode and from differential-mode circuits, respectively. Section 8. Controlling Emissions in Designs using Digital Isolators with Integrated DC-DC Controllers provides guidelines for controlling emissions from designs using digital isolators with integrated dc-dc controllers.

To wrap things up, two case studies are presented: Section 9. Case Study 1: CISPR 25 Radiated Emissions for an Si88241 Design, which illustrates reduction in radiated emissions for an Si88241-based design, and Section 10. Case Study 2: CISPR 25 Conducted Emissions for an Si88241 Design, which demonstrates reductions in conducted emissions for an Si88241-based design.

#### 1.1 EMI, EMC, Radiated and Conducted Emissions, Radiated and Conducted Immunity, Coupling, and Crosstalk

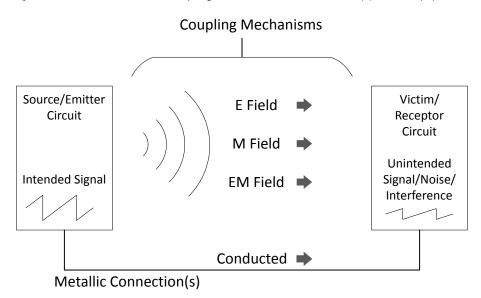

Electronic equipment can unintentionally radiate and/or conduct a broad spectrum of energy from within the equipment out into the surrounding environment. Radiated emissions are unintentional energy that escape the equipment in the form of electric, magnetic, or electromagnetic fields. Conducted emissions are unintentional energy carried out of the equipment on the equipment's power cables or attached signal cables. This emitted energy can couple into nearby *victim* equipment, resulting in unwanted signals (noise) within the victim that can interfere with its operation. The noise generated in the victim equipment as a result of these radiated or conducted emissions can be considered electromagnetic interference (EMI). The ability of the victim equipment to operate in the presence of radiated energy or conducted energy is referred to as the equipment's radiated immunity or conducted immunity, respectively.

Electromagnetic compatibility (EMC) refers to the ability of electronic equipment to operate without interfering with other equipment (without emitting excessive radiated or conducted energy) and to operate correctly within its intended operating environment (which will include some level of radiated or conducted energy from other sources). There are national and international EMC standards both for the maximum levels of radiated or conducted emissions electronic equipment should generate and for the minimum levels of radiated or conducted energy.

Conductors carry electric signals within electronic equipment. All conductors that are charged to non-zero potentials and/or that carry electrical currents act as antennas that source energy into the surrounding environment in the form of near-field electric and magnetic fields (E fields and M fields) and far-field electromagnetic fields (EM fields). Energy from these fields can couple onto other conductors within the equipment as well as radiate into the environment outside of the equipment. Conversely, all conductors act as antennas which convert energy from E fields, M fields, and EM fields into unwanted electrical voltages and currents. These received fields may be sourced by other conductors within the same equipment, or they may be present in the environment outside the equipment.

Coupling of energy from a source conductor to victim conductor through electric or magnetic fields results in unintended voltages or currents added to the victim conductor's intended signal, as depicted in Figure 1.1 Source and Victim Circuits on page 5. When the source conductor and the victim conductor are contained within the same equipment, the unintended voltage or current induced on the victim conductor is often referred to as *crosstalk* rather than interference. Coupling of the energy-storing near-field of a source conductor tor to a nearby victim conductor can reduce the signal integrity of the source conductor as well as that of the victim. Also, any conductor referred to as a source may well itself be the victim of coupling from some other conductor(s) in the equipment.

Figure 1.1. Source and Victim Circuits

There are no standards specifying the level of crosstalk that is allowable between conductors coexisting within a piece of equipment (crosstalk levels must be kept low enough to allow the equipment to operate correctly). However, internal coupling will increase the level of emissions from the victim conductor (especially if the victim conductor connects to cabling that enters/exits the equipment), and internal coupling may also decrease the immunity of the victim conductor to outside interference. As a result, managing the coupling between conductors within the equipment is crucial, both to ensure that the equipment is able to operate correctly, and to help ensure that the EMC standards for radiated and conducted emissions and immunity can be met.

This application note describes techniques for control of both radiated and conducted emissions in systems with galvanic isolation. Many of these techniques will also improve the system's radiated and/or conducted immunity, but immunity issues are not specifically addressed in this application note.

#### 1.2 Differential-Mode and Common-Mode Currents

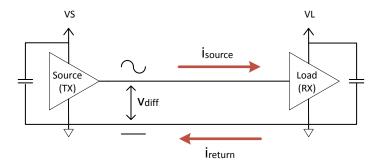

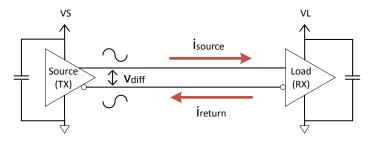

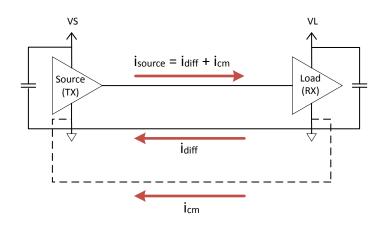

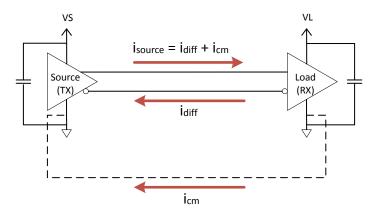

The circuits employed in electronic equipment almost always use differential-mode currents. In differential mode, current is carried from a "source" (transmitter) to a "load" (receiver) on one conductor, and the return current is carried from the load back to the source on a second conductor. There are two typical differential-mode signaling schemes: single-ended signaling and balanced differential signaling. For single-ended signaling, the return current is carried on a ground conductor or ground plane as shown in Figure 1.2 Single-Ended Differential Current on page 6. For balanced differential signaling, a dedicated conductor carries the return current as shown in Figure 1.3 Balanced Differential Current on page 6. In either case, the return current from load to source should be equal in magnitude to the signal current from source to load, leaving a net current of zero for the two conductors combined.

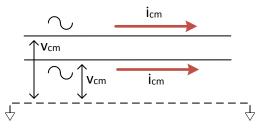

Common-mode currents are currents that flow in the same direction on two (or more) conductors as shown in Figure 1.4 Common-Mode Current on page 6. The return current for a common-mode circuit is typically carried on a reference conductor or ground plane. The voltage on the two (or more) conductors carrying the common-mode current is the same with respect to the reference conductor and is referred to as the common-mode voltage.

Common-mode currents are almost always unintentional and often arise due to imperfections or "imbalance" in differential circuits; particularly when the return current for a differential circuit finds an unintended (and often longer) return path from the load back to the source as shown in Figure 1.5 Common-Mode Current from Leakage in Single-Ended Differential Circuit on page 7 and Figure 1.6 Common-Mode Current from Leakage in Balanced Differential Circuit on page 7. Current flowing in this unintended return path leaves a net non-zero current on the conductors that were intended to carry only a differential current. This non-zero net current is, effectively, a common-mode current that is superimposed on the differential-mode current carried on these conductors.

Figure 1.2. Single-Ended Differential Current

Figure 1.3. Balanced Differential Current

Figure 1.4. Common-Mode Current

Figure 1.5. Common-Mode Current from Leakage in Single-Ended Differential Circuit

Figure 1.6. Common-Mode Current from Leakage in Balanced Differential Circuit

## 1.3 Magnetic and Electric Fields, Near and Far Fields, Wave Impedance, Loop and Electric Dipole Radiators, and Antenna Reciprocity

M fields are created by moving charges (current). E fields are created by changing voltages on a conductor. Both Electric and Magnetic fields exhibit "near field" characteristics that are different from their "far field" characteristics. Energy is stored in the near field E and/or M field, while energy is radiated in the far field as an electromagnetic (EM) wave. The EM field has both electric and magnetic properties. The near field is sometimes referred to as the "inductive field" and the far field as the "radiative field". The boundary for near field vs. far field effects is often given as a distance of  $\lambda/2\pi$  from the center of a current loop, where  $\lambda$  is the dominant wavelength emitted by the source ( $\lambda = c/f$ , where c is the speed of light, and f is frequency). That's a distance of around 795 km for 60 Hz, 477 m for 100 kHz, or 0.477 m for 1 GHz.

All conductors that carry electrical signals will generate both M and E fields, but circuits carrying differential-mode currents tend to generate near fields that have more magnetic field strength than electric, while common-mode currents tend to generate stronger electric than magnetic near fields. The "wave impedance" of a field is the ratio of the electric field strength to that of the magnetic field strength.

Differential-mode circuits act as loop antennas, or magnetic dipoles. For loop radiators like these, the M field is dominant in the near field. The M field strength is proportional to current and to loop area, and inversely proportional to distance cubed. The E field strength in the near field is proportional to current, loop area and frequency, and inversely proportional to distance squared. The near field wave impedance is then proportional to distance and inversely proportional to wavelength. So the wave impedance of this predominantly magnetic field is lower near the source and increases with distance, approaching the intrinsic impedance of free space ( $\eta 0 = 120^*\pi = 377\Omega$ ) as the transition into EM wave radiation occurs in the far field.

Conductors carrying common-mode currents act more like electric dipole antennas. For an electric dipole radiator, the E field is dominant in the near field. The strength of the E field is proportional to current, total loop length, and wavelength, and inversely proportional to distance cubed. The M field strength is proportional to current and total loop length, and inversely proportional to distance squared. The near field wave impedance is then proportional to wavelength and inversely proportional to distance. The wave impedance of the predominantly electrical field in this case is higher near the source and decreases with distance, and it also approaches the intrinsic impedance of free space as it transitions to an EM wave in the far field.

The principle of reciprocity in antenna theory suggests that the characteristics an antenna has as a transmitter, such as directivity and efficiency, apply equally to that antenna when acting as a receiver. This means differential-mode circuits, which can act as efficient current-loop transmitters of low wave-impedance M fields, will also act as efficient receivers of such magnetic fields. Similarly, circuits with common-mode currents, which can act as efficient transmitters of high wave-impedance E fields are likely to be good E field receivers. In general, low impedance circuits tend to be more susceptible to interference/coupling from magnetic fields, while high impedance circuits tend to me more susceptible to electric fields.

Coupling of magnetic fields, such as those generated by loop radiators, is often referred to as "magnetic induction" or "inductive coupling". The effect of inductive coupling from the M field of a source conductor onto a victim conductor is an unwanted (noise) voltage induced in the victim. The coupling can be modelled as a mutual inductance, M, with a value that depends on factors such as the current loop areas of the source and victim circuits, and the distance between them. The voltage induced in the victim circuit is then:

$$v = M \frac{di}{dt}$$

where *di/dt* is the rate of change of current in the source loop

Coupling of E fields, such as those generated by common-mode currents, is often referred to as "electric induction" or "capacitive coupling". The effect of capacitive coupling from the E field of a source conductor to a victim conductor is an unwanted (noise) current induced in the victim. The coupling can be modelled as a "mutual capacitance", C, with a value that depends on factors such as the areas of the source and victim conductors, and the distance between them. The current induced in the victim circuit is then:

$$i = C \frac{dv}{dt}$$

where *dv/dt* is the rate of change of voltage on the source conductor

The voltage that results from this induced current will depend on the impedance from the victim conductor to ground.

#### 1.4 General Guidelines for Minimizing Radiated and Conducted Emissions

Note that radiated emissions and conducted emissions are closely related; high frequency energy on any conductor will generate electric, magnetic and electromagnetic fields that can directly result in radiated emissions. If the conductor exits the system as cabling, the high frequency energy carried on the conductor can directly result in conducted emissions as well. Coupling of the electric fields, magnetic fields, and/or electromagnetic fields of the conductor onto other victim conductors within the equipment can result in radiated and/or conducted emissions from the victim conductor.

In general, limiting the frequency content of switching signals to the extent that is practical will help reduce both radiated and conducted emissions. Also, employing techniques to minimize coupling of electric fields and magnetic fields between conductors in the equipment will help reduce both radiated and conducted emissions. Although both differential-mode and common-mode currents will radiate and potentially couple onto victim conductors, it is often the unintentional common-mode currents that contribute most to emissions.

Radiation from differential current-loop circuits can be well controlled by minimizing the area of the current loop. It is important make sure the current return path from the receiver to source is uninterrupted and follows the outgoing path from source to receiver as closely as possible. In the single-ended differential circuit depicted in Figure 1.2 Single-Ended Differential Current on page 6, current is supplied to the driver from the supply, VS. The return current path from the receiver to the driver is ground. The current loop from ground back to VS is completed through the supply, which can be a relatively long loop. This loop is shortened for higher frequency current components by the local supply decoupling capacitance at the driver, so high-quality, low-inductance decoupling is critical to minimizing current loop length and controlling radiated emissions.

Coupling from differential current-loop circuits can be controlled by the following:

- · Minimizing the current loop area of both potential source and victim circuits.

- When common-mode currents result from imbalance in differential circuits, the unintended return path may be long, resulting in a large E field antenna area. Even small unintentional common-mode currents can radiate a relatively large amount of energy.

- Energy from this unintended common-mode source can also readily couple onto nearby high-impedance conductors, which in turn, will radiate energy. If the victim conductors are large and/or long, the coupling and radiation will be higher. When the victims are cables entering/exiting the equipment, the resulting radiation can be particularly problematic.

- · Maximizing the distance between potential source and victim circuits.

- Coupling of the E field resulting from common-mode currents can be reduced by increasing distance between potential source and victim conductors.

- Use of grounded conductive shielding between source and victim can also be effective in reducing E field coupling.

- Minimizing di/dt in potential source circuits

- Generation of unintentional common-mode currents can be minimized by maximizing the balance between the send and receive

paths in differential circuits. Careful attention to matching of the send and receive current paths is important. Limiting *di/dt* can

also help, as parasitic capacitances in the differential circuits can cause greater imbalance for higher frequency components of

the differential signal.

- *di/dt* is minimized by limiting the switching frequencies of signaling and by limiting driver slew rate and drive strength.

Radiated and conducted emissions from cables or conductors carrying common-mode currents can often be reduced by the use of common-mode chokes and/or EMI filters. EMI filters may also be employed to improve the equipment's immunity to conducted emissions from other connected equipment. Passive EMI filters are typically constructed using various arrangements of resistors, capacitor, and inductors or beads. Common topologies include L, C, RC, LC, Pi-section, and T-section filters. More specific discussion of these techniques as applied to circuits employing galvanic isolation will be presented in the following sections of this guide.

## 2. Radiated and Conducted Emission Standards

There are many EMC standards that specify test methods and limits for radio frequency emissions (also referred to as "disturbances") from electronic equipment. Standards may be developed and/or published by individual countries, international standards organizations, or private organizations or consortiums such as automobile manufacturers. Separate standards often exist for different types of equipment, and further classification may be made according to the equipment's intended operating environment (residential or non-residential) or according to the desired EMC performance level. Emissions standards will generally specify the antenna type and distance used for radiated emissions measurements, the coupling mechanism used for conducted emissions measurements, the detector type and resolution bandwidth to be used, the frequency band(s) to be measured, and the associated pass/fail limits.

Limits for radiated emissions are specified in terms of electrical field strength in dBmV/m, and measurements are typically made using a Biconical, log periodic, or broadband antenna, and a spectrum analyzer. EMC standards typically require measurements with the antenna in both vertical and horizontal orientation, and the EUT is typically rotated to determine the orientation with the highest emission levels. The EMC standards generally specify the length of the EUTs power and signal cabling that must be exposed during the measurements.

Conducted emissions standards are generally most concerned with emissions conducted onto the equipment's power mains connections, because the mains network can act as an efficient transmitting antenna, allowing RF energy conduced from the equipment to then radiate from the mains network into the surrounding environment. Some standards also specify limits for signal lines. Conducted emissions are measured using a Line Impedance Stabilization Network, or "LISN". The LISN is connected between the equipment under test (EUT) and the mains network, and provides a port for connection of the EMI receiver to make measurements. The LISN prevents any radio frequency noise that might be present on the mains from coupling into the measurement, and provides a controlled impedance which converts conducted emission currents from the equipment into a voltage for measurement. Different standards may specify different LISN impedances to represent the environment in which equipment will be operated.

Emission levels are typically measured using a spectrum analyzer with a specified resolution bandwidth and detector type, which may be a peak detector, a quasi-peak detector, and/or an average detector. The peak detector measures the peak energy within the specified resolution bandwidth at each measurement frequency. The quasi-peak detector measurement is effectively weighed by the repetition rate of energy in the band, and is slower than the peak measurement.

The following sections provide a brief overview of some of the more commonly used emissions standards.

#### 2.1 IEC CISPR EMC Standards

Because the requirements for many countries are similar, many countries have now adopted, or accept testing to, the EMC standards published by the "Comité International Spécial des Perturbations Radioélectriques" (CISPR), which translates to "International Special Committee on Radio Interference". The CISPR is a part of the International Electrotechnical Commission (IEC). The IEC/CISPR standards for EMC are organized as "Basic Standards", "Generic Standards", "Product Standards", and "Guidance Documents" (Guidance Documents do not include specific compliance testing requirements).

The IEC/CISPR Basic Standards provide general rules for EMC assessment of all products, and serve as reference documents for the CISPR Generic Standards and Product Standards. The Basic Standards do not include prescribed limits. Examples of IEC/CISPR Basic Standards include:

- CISPR 16-1-2: Specification for radio disturbance and immunity measuring apparatus and methods Part 1-2: Radio disturbance and immunity measuring apparatus Coupling devices for conducted disturbance measurements

- · CISPR-16-2-1: Conducted disturbance measurements

- · CISPR-16-2-3: Radiated disturbance measurements

- · CISPR-16-2-4: Immunity measurements

- CISPR-16-4-2: Uncertainty in EMC measurements

- IEC 61000-4-20: Testing and measurement techniques Emission and immunity testing in transverse electromagnetic (TEM) waveguides

- · IEC 61000-4-20: Testing and measurement techniques Reverberation chamber test methods

- IEC 61000-4-20: Testing and measurement techniques Radiated emissions and immunity measurements in fully anechoic rooms (FARs)

The IEC/CISPR Generic Standards specify minimum EMC requirements related to a particular environment, including limits applicable to all products or systems operated in this environment for which there are no specific product/system EMC standards. Examples of IEC/CISPR Generic Standards include:

- · IEC 61000-6-3: Generic standards Emission standard for residential, commercial and light-industrial environments

- · IEC 61000-6-4: Generic standards Emission standard for industrial environments

- · IEC 61000-6-1: Generic standards Immunity for residential, commercial, and light-industrial environments

- · IEC 61000-6-2: Generic standards Immunity for industrial environments

The IEC/CISPR Product Standards define requirements, test procedures, and limits for particular products, systems, or installations. Examples of IEC/CISPR Product Standards include:

- CISPR 11: Industrial, scientific, and medical equipment Radio-frequency disturbance characteristics Limits and methods of measurement

- CISPR 12: Vehicles, boats, and internal combustion engines Radio disturbance characteristics Limits and methods of measurement for the protection of off-board receivers

- CISPR 25: Vehicles, boats, and internal combustion engines Radio disturbance characteristics Limits and methods of measurement for the protection of on-board receivers

- CISPR 32: EMC of multimedia equipment emission requirements

- IEC 61131-2: Industrial-process measurement and control Programmable controllers Part 2: Equipment requirements and tests

- IEC 61326-1: Electrical equipment for measurement, control, and laboratory use EMC requirements Part 1: General requirements

The IEC CISPR standards are often adopted by standards bodies such as the European Committee for Electrotechnical Standardization (CENELEC). For example, IEC CISPR 32: Electromagnetic Compatibility of Multimedia Equipment – Emission Requirements has been adopted by CENELEC as the "European Norm" EN 55032: Electromagnetic compatibility of multimedia equipment - Emission Requirements.

#### 2.2 IEC CISPR 25

CISPR25 addresses radio disturbance characteristics for vehicles, boats, and internal combustion engines. The limits specified in CISPR25 are intended to protect receivers in the vehicle from disturbances produced by components and circuits within the same vehicle. This standard defines test methods and limits for radiated disturbances from the complete vehicle, as well as for conducted and radiated disturbances from components or modules measured independently from the vehicle. Performance limits are given for five different performance "classes", with class 5 being the most stringent. The performance class is agreed upon between the "purchaser and the supplier" and documented in the test plan. The measurement methods and limits for a complete vehicle, which may or may not be connected to mains power, are given in Clause 5, and measurement methods and limits for components or modules are in given in Clause 6. Annex E defines artificial networks for measurement of conducted emissions, and Annex I specifies test methods for shielded power supply systems for high voltages in electric and hybrid vehicles.

CISPR 25 radiated disturbance measurements are made in an absorber-lined shielded enclosure (ALSE). Measurements are made in the frequency range of 150 kHz to 2.5 GHz. This range is divided into discrete bands associated with various services/bands that may be interrupted by the radiated emissions; for example, there are separate limits specified for the FM band at 76 to 108 MHz, for the TV Band I at 41 to 88 MHz, and for the VHF band at 68 to 87 MHz. Spectrum analyzer resolution bandwidths and minimum scan times vary with measurement frequency (service/band) and are specified separately for peak detection, quasi-peak detection, and average detection, with separate limits specified for each detection method.

Radiated disturbances from the complete vehicle are measured using the same type of antenna supplied with the vehicle, or specified antenna types if no antenna is supplied. For tests done with the vehicle charging, the cables are connected through "Artificial Networks" (ANs), which function similarly to the LISNs mentioned earlier. AC power mains are connected to the vehicle through a 50  $\mu$ H/50  $\Omega$  Artificial Mains Networks (AMNs) with 50  $\Omega$  terminators connected to the AMN measurement ports. DC power mains are connected through 5  $\mu$ H/50  $\Omega$  High Voltage Artificial Networks (HV-ANs). Communication lines, if present, are connected to the vehicle through Asymmetric Artificial Networks (AANs).

When testing components and modules, each positive power supply lead is connected to the EUT through a 5  $\mu$ H AN. An AN is also required on the power return line if it is longer than 200 mm. The measuring ports of ANs not connected to measuring equipment are terminated with 50  $\Omega$ .

Conducted disturbance test procedures and limits for components and modules are given for two different measurement methods: the "voltage method" and "current probe method". The voltage method makes use of the measurement port on the AN, and measurements are made over a frequency range of 150 kHz to 88 MHz. The current probe method places a current probe (see CISPR 16-1-2) around the complete wiring harness, and measurements are made with the current probe positioned at 50 mm and at 750 mm from the EUT. Measurements are made over a frequency range of 150 kHz to 245 MHz for the current probe method.

Radiated disturbances from components and modules may be measured in an ALSE using linearly polarized electric field antennas with a 50  $\Omega$  output impedance. For measurements from 150 kHz to 30 MHz, the vertical polarization is used. For measurements from 30 MHz to 2.5 GHz, both vertical and horizontal polarizations are required. Power is connected to the EUT through ANs. The EUT is operated under typical loading and under other conditions to ensure that the maximum emission state is measured.

Information regarding radiated emissions measurements for components/modules using the TEM cell method is provided in Annex F, and information regarding the Stripline method is given in Annex G. Note that both Annex F and Annex G are "informative" rather than "normative" parts of the standard.

#### 2.3 IEC CISPR 32

CISPR 32 specifies emission requirements for multimedia equipment. CISPR 32 supersedes the widely referenced CISPR 22: Information technology equipment – Radio disturbance characteristics – Limits and methods of measurement, as well as CISPR 13: Sound and television broadcast receivers and associated equipment – Radio disturbance characteristics – Limits and methods of measurement. CISPR 32 differentiates between two classes of equipment, Class A and Class B, and specifies limits for conducted and radiated emissions for each class. Equipment that is used in a residential environment must meet the more stringent Class B limits. Equipment not intended for residential use can use the more relaxed Class A limits. Class A equipment must provide a warning that it may cause radio interference if used in a residential environment.

Radiated emissions are measured from 30 MHz to an upper frequency limit of up to 6 GHz, depending on highest internal oscillator frequency used in the equipment. For example, emissions from equipment with a maximum internal frequency of 500 MHz are measured from 30 MHz to 2 GHz, while equipment with an internal frequency of over 1 GHz must be measured from 30 MHz to 6 GHz. Measurements at frequencies up to 1 GHz can be made in an either an Open Area Test Site (OATS), a Semi Anechoic Chamber (SAC), or a Fully Anechoic Room (FAR), at a distance of either 3 m or 10 m, using a quasi-peak detector with 120 kHz bandwidth. Measurements at frequencies above 1 GHz are made in a Free Space Open Area Test Site (FSOATS), at a distance of 3 m, using either an average detector with 1 MHz bandwidth, or a peak detector with 1 MHz bandwidth. Limits are given for Class A and for Class B equipment for each of these measurement scenarios. In addition, separate radiated emissions requirements are given for FM receivers (which are measured from 30 MHz to 1 GHz) and for outdoor units of home satellite receiving systems (which are measured from 30 MHz to 1 GHz).

Conducted emissions from ac mains power ports of Class A and Class B equipment are measured over the frequency range of 150 kHz to 30 MHz using an Artificial Mains Network (AMN) for coupling. Limits are given for the quasi-peak detector with 9 kHz bandwidth, and for the Average detector with 9 kHz bandwidth.

Asymmetric mode (common-mode) conducted emissions are measured for wired network ports, optical fiber ports, and antenna ports of Class A and Class B equipment. Asymmetric mode measurements are made over the frequency range of 150 kHz to 30 MHz using an Asymmetric Artificial Network (AAN), a current probe, or a Capacitive Voltage Probe (CVP) and current probe. Limits are given for both the quasi-peak detector with 9 kHz bandwidth, and for the average detector with 9 kHz bandwidth.

In addition, conducted differential voltage emissions are measured over a frequency range of 30 MHz to 150 MHz for TV broadcast receiver tuner ports, RF modulator output ports, and FM broadcast receiver tuner ports of Class B equipment. Coupling is accomplished using "Matching and combining networks for measurements into 75  $\Omega$ ", and the limits are specified in dB ( $\mu$ V) at 75  $\Omega$ . A quasi-peak detector with bandwidth of 120 kHz is used for frequencies below 1 GHz, and a peak detector with 1 MHz bandwidth is used for frequencies above 1 GHz.

#### 2.4 FCC Title 47, Part 15, Subpart B

In the United States, the "FCC Part 15" is a widely referenced EMC standard. The US Federal Government maintains a set of rules called the Code of Federal Regulations (CFR). Title 47 of the CFR is named "Telecommunication" and Chapter I of Title 47 is maintained by the Federal Communications Commission. "Part 15" of Chapter I addresses "Radio Frequency Devices", and Subpart B of Part 15 addresses "Unintentional Radiators" (unintentional radio frequency emissions).

Conducted emissions from the EUT onto the public utility power lines are coupled using a 50  $\mu$ H/50  $\Omega$  LISN. Measurements are made over a frequency range of 150 kHz to 30 MHz, and limits are given for quasi-peak and for average detectors.

In general, radiated emissions from unintentional radiators are measured from 30 MHz (or the lowest frequency used inside the EUT if that's above 30 MHz) to an upper limit of up to 40 GHz, depending on the highest frequency used inside the EUT). For example, emissions from equipment with a maximum internal frequency of 10 MHz are measured up to 1 GHz, while equipment with an internal frequency of over 10 GHz must be measured up to 40 GHz. Radiated emission levels for frequencies up to 1 GHz are measured using a quasi-peak detector, unless specified otherwise. For frequencies above 1 GHz, an average detector with a minimum resolution bandwidth of 1 MHz is used.

Note that radiated emissions for Class A devices are measured at 10 m from the EUT, while Class B devices are measured at 3 m. The field strength limits are higher for the Class B equipment than for Class A, but because these measurements are made at a shorter distance, the Class B limits are actually more stringent than those of Class A. In general, the conducted and radiated emission limits specified in CISPR 32 and FCC Part 15 are within a few dB of each other.

## 3. Isolated Systems and Electromagnetic Compatibility (EMC)

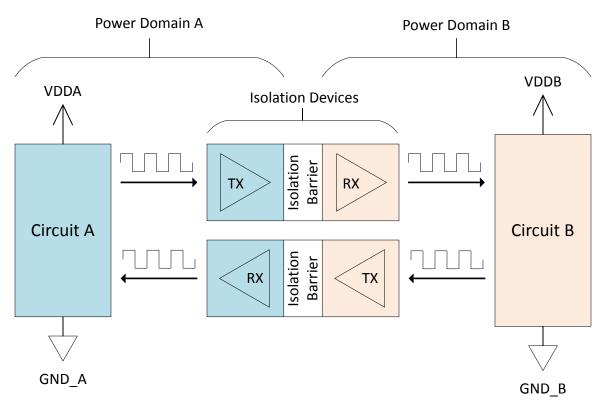

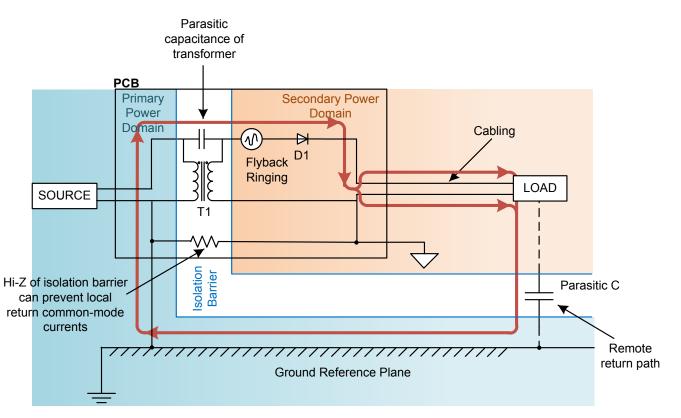

Galvanic isolation devices allow communication between two power domains of a system, while preventing currents from passing between them. Signals are passed between Circuit A and Circuit B using isolation devices, or isolators, as shown in Figure 3.1 Isolated Circuits and Power Domains on page 14. The isolators themselves include circuitry that resides in each power domain.

Figure 3.1. Isolated Circuits and Power Domains

Galvanic isolation can be employed in electrical systems for a number of different reasons. Isolation can allow robust communications between circuits that operate in different power domains and different potentials. Isolation can be employed to isolate a more sensitive circuit from noise that may exist in the ground and/or supply systems of another circuit. Isolation is also often used to provide protection for circuits, equipment, and/or human operators on the low-voltage circuit side of the barrier from high voltages and/or currents that may be present on the other side of the barrier. Isolation is required by safety standards for many types of electrical systems and equipment. Isolators are components that maintain the safety aspects of the isolation barrier, while allowing signaling across it.

While galvanic isolation can provide many benefits in a system, it can also create challenges with respect to EMC. Isolation between circuits on the A side and the B side of the barrier effectively makes all circuitry on the B side high-impedance with respect to the A side circuits. This makes circuits on the B side much more susceptible to coupling from E fields generated on the A side. The return path for currents induced through capacitive coupling into B side circuits will generally be high-impedance parasitic capacitance paths, making the resulting induced voltages large. Large conductors on the B side will be particularly effective as receiving antennas for coupling, and also as transmitting antennas that radiate into the environment. Cables entering or exiting the B side circuits will also be very effective radiators. And, of course, the same holds true for fields generated by circuits on the B side coupling into circuits on the A side.

## 4. Silicon Labs Isolators Are Designed to Minimize Radiated Emissions

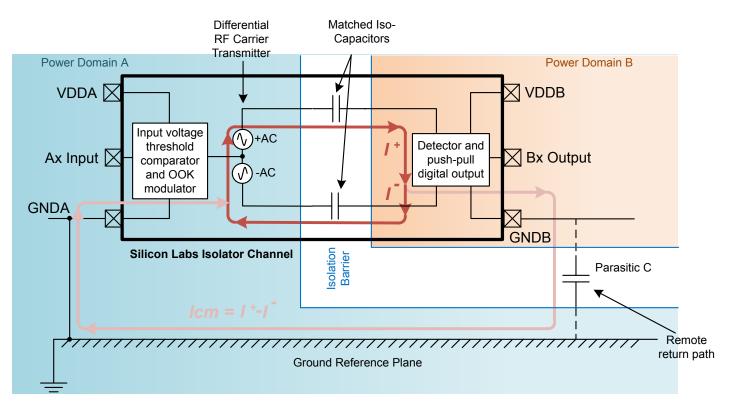

Figure 4.1 Simplified Block Diagram of Silicon Labs Isolation Channel on page 15 shows a simplified block diagram of a Silicon Labs isolator channel. Power domain A has a digital input controlling a radio frequency (RF) carrier transmitter which is coupled to Power domain B's detector and push-pull digital output through high-voltage SiO2 isolation capacitors. At first glance, it appears that the RF transmitter would become a common-mode noise generator. However, differential signaling is used. So despite the current from RF carrier crossing the isolation barrier, it has an equal, well-defined path back to its source. This makes the RF carrier transmitter behave as a differential current noise source. The isolation channels are designed to be well-balanced and they have a very small loop area wholly contained within the integrated circuit (IC) itself to minimize their contribution as a radiated emissions source. Only a small portion of the carrier could appear as a common-mode noise source due to any remaining mismatch in the loop.

Figure 4.1. Simplified Block Diagram of Silicon Labs Isolation Channel

Silicon Labs does not specify the carrier frequency of the RF transmitter used in the digital channels. Its nominal carrier frequency varies somewhat from product to product, however its carrier frequency resides squarely in the UHF band, around 500 MHz. For multichannel isolators, the carrier frequencies in adjacent channels are slightly offset from one another. This spreads the peak of any detectable energy in the radiated emissions when adjacent channels are simultaneously transmitting.

## 5. Choosing the Best Silicon Labs Isolator Option to Reduce Emissions for a Given RF Transmitter Duty Cycle

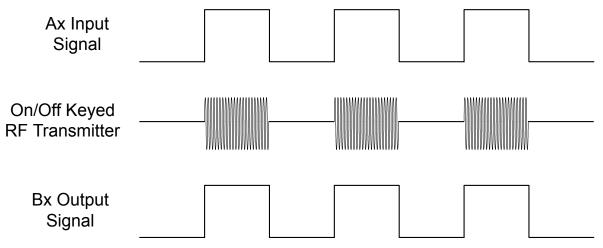

To ensure that the output always follows the input, Silicon Labs' isolators use an on/off keying (OOK) modulation technique. With OOK modulation, the RF transmitter is only active during one of two logic states as shown in Figure 5.1 OOK Modulation of RF Transmitter on page 16. How often the transmitter is active is dictated by the duty cycle characteristics of the digital signal it is transmitting across the isolation barrier.

Figure 5.1. OOK Modulation of RF Transmitter

If the signal's behavior is known and its duty cycle can be predicted, then selecting the correct Silicon Labs isolator ordering option can minimize the overall on-time of the RF transmitter and thus reduce emissions from the isolator itself. This has two benefits: 1) it reduces the overall time the RF transmitter could act as a potential noise source, and 2) it reduces the operating power consumption of the transmitting side of the isolator.

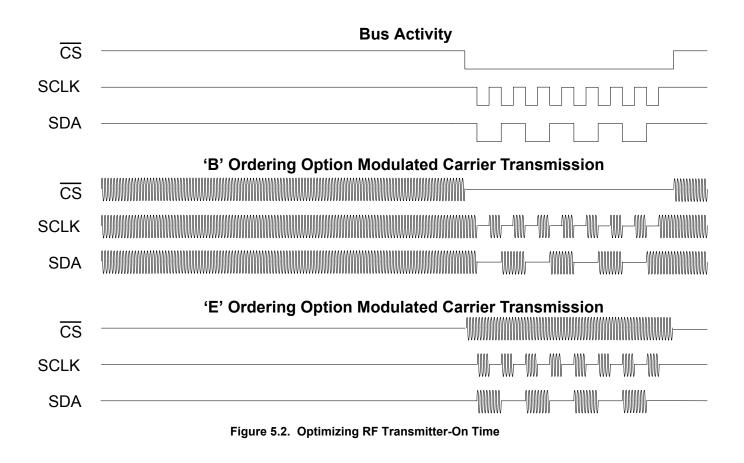

For example, the Si86xx multichannel digital isolator might only be needed for an isolated serial bus application that is only exercised a fraction of the time. The idle state of its pins will determine the overall time each signal's RF transmitter is on. For protocols with clock and data pins idle state low, chose part numbers that start with Si86xxB as logic low is their default idle state. For protocols with clock and data pins idle state is high, chose part numbers that start with Si86xxE. Figure 5.2 Optimizing RF Transmitter-On Time on page 17 shows how choosing the right part number can reduce the on time of the RF transmitter for a Type 3 SPI bus.

AN1131: Design Guide for Reducing Radiated and Conducted Emissions in Isolated Systems Using Silicon Labs' Isolators Choosing the Best Silicon Labs Isolator Option to Reduce Emissions for a Given RF Transmitter Duty Cycle

## 6. Techniques for Reducing Emissions from Differential-Mode Currents

Since Silicon Labs' isolation channel is already designed to minimize the radiated emissions from the RF transmitter, the PCB layout techniques available to reduce any remaining noise can be described as best practices common to all PCBs that contain digital integrated circuits. In general, it's best to use multilayer PCBs to take advantage of their numerous emissions reducing techniques not available in a lower cost 1 or 2 layer board designs. Moreover, it is recommended to provide the best decoupling by choosing a quality by-pass capacitor and placing it as close as possible to the IC supply pins for the highest effectiveness.

One way to describe the purpose of a local bypass capacitor is that it holds charge that can quickly provide current as needed to the IC's supply pin during load transients caused by the IC's normal switching operation. In this way, the local bypass capacitor extends the ability of a remote power supply to quickly react to changing loads as to minimize the voltage ripple that would normally occur on the supply. The presence of ac ripple in the supply path will inject energy into nearby circuits as either differential-mode or common-mode noise. If the alternating currents can be directed back to the local ground near its source through a local bypass capacitor, they can be treated as a differential-mode current noise source. To minimize radiated emissions, the capacitor's connection to the supply pin and ground must be low-inductance and as short as possible to create a very small loop area for the alternating currents to exist.

#### 6.1 Selecting Proper Bypass Capacitors

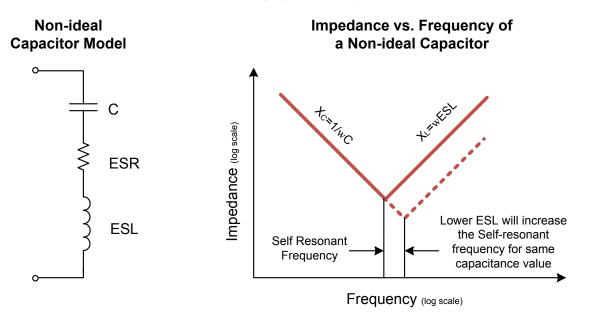

The impedance of an ideal capacitor decreases as frequency increases. This allows the capacitor to direct alternating currents to the local ground. But with a real-world capacitor, effective series resistance (ESR) and, especially, effective series inductance (ESL) limits how high of a frequency the bypass capacitor can be effective. Figure 6.1 Impedance vs. Frequency for a Non-ideal Capacitor on page 18 shows a simplified electrical model of a capacitor and the impedance vs. Frequency characteristic curve. At frequencies above self-resonance, a capacitor behaves as an inductor, thus failing to provide a low inductance return path for noise allowing it to propagate further in the circuit. This decreases its effectiveness in reducing higher frequency radiated emissions.

Figure 6.1. Impedance vs. Frequency for a Non-ideal Capacitor

Many IC vendors will specify using  $0.1\mu$ F surface mount ceramic capacitors as local bypass capacitors. There is nothing particularly special about the value of  $0.1\mu$ F. It has become somewhat of an industry norm as it is a good combination of available storage of charge for switching demands yet available in a small enough package to enable a tight layout. Smaller packages are generally preferable as they have lower ESL, thus extending the high frequency performance of the capacitor. Generally speaking, the same capacitor in built in a small package such as 0402 and 0603 will have lower ESL than constructed in a 0805 or 1206 package as ESL is a primarily a function of distance between the capacitor ends. Another option to reduce a capacitor's ESL is to choose one in reverse geometry construction. For example, a  $0.1\mu$ F in a 0306 package may have a self-resonant frequency twice that of a similar  $0.1\mu$ F 0603 capacitor.

#### 6.2 Choosing the Proper Bypass Capacitor Placement

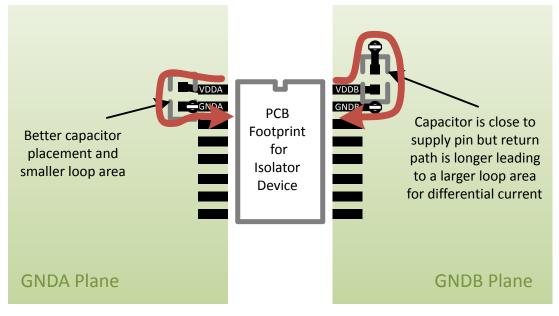

Just as minimizing a capacitor's ESL is improves the effectiveness of bypass capacitors, it is equally important to reduce the series inductance in traces and vias that connect the capacitor to the supply and ground pins of the isolator IC. Series inductance in PCB traces is a function of length- so use short, wide traces to the bypass capacitor. As shown in Figure 6.2 Minimize Loop Area with Optimum Bypass Capacitor Placement on page 19, the bypass capacitors for the supply pins on sides A and B of an isolator should be placed as closely to the supply pin as possible with the ground connection rotated towards the most direct path to the local ground pin. Figure 6.2 Minimize Loop Area with Optimum Bypass Capacitor Placement on page 19 illustrates both an optimized and non-optimized placement of bypass capacitors for the same isolator. The end system should seek to optimize both caps placement for their end system.

Figure 6.2. Minimize Loop Area with Optimum Bypass Capacitor Placement

#### 6.3 Adding Embedded Bypass Capacitor Structures for Multilayer PCBs

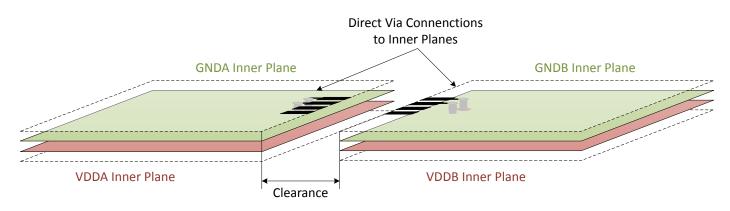

One can also consider using embedded capacitor structures in multilayer PCBs to increase the effectiveness of the bypass capacitors. This can be accomplished by creating power and ground planes for each power domain on the inner layers of a four layer PCB shown in Figure 6.3 Embedded PCB Capacitor to Improve Supply Bypassing on page 20. As shown, the planes make a parallel plate capacitor of the PCB itself and its capacitance is given by the equation below.

$$C = K \times E_0 \times \frac{A}{D}$$

Where K = relative permittivity of the dielectric (approximately 4.4 for FR4)

$E_0 = 8.854 \times 10^{-12}$ , the permittivity of a vacuum in F/m

A = area of overlap of inner power and ground layers in  $m^2$

D = distance between the layers in m

#### Equation 6.1. Capacitance of a PCB Inner Plane Capacitor

If this technique is used, one should connect supply and ground leads directly to these planes using through-hole vias as shown in Figure 6.3 Embedded PCB Capacitor to Improve Supply Bypassing on page 20. This gives each side's supply pin of the isolator a high-quality (low-inductance), high-frequency distributed capacitance.

Figure 6.3. Embedded PCB Capacitor to Improve Supply Bypassing

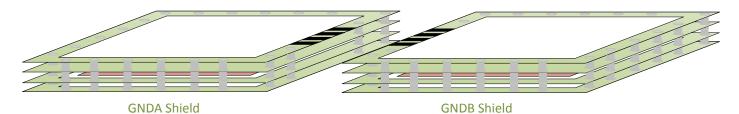

Moreover, note that extending the solid planes to the edge of the PCB creates a dipole that can allow noise to radiate from the sides of the PCB. It is common practice to create a ground shield around power planes that stitches every layer together as shown in the Figure 6.4 Ground Stitching Shields Reduce Emissions from PCB Edges on page 20.

Figure 6.4. Ground Stitching Shields Reduce Emissions from PCB Edges

#### 6.4 Terminating Transmission Lines

The use of ground planes is also essential for creating uniform transmission lines for propagating digital signals. Switching digital signals create differential-mode currents and for a current that propagates in one direction down a trace, there must be a return current. Inner ground planes provide a uniform, low-resistance and low-inductance return path for these currents to their source. Fortunately, in 4-layer PCB design, the distance between a trace on a surface layer to an internal ground plane is often just 10 to 12mils, minimizing the loop area created by the trace and its return path. Always ensure the ground plane returns for signal traces do not have voids and are continuous under the trace. If the return current must find a different way back to the source, it creates a larger loop area and more opportunity to cause emissions.

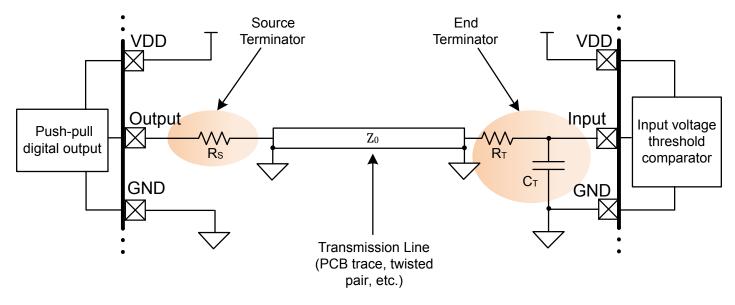

Minimizing the loop area of a trace and its return path are critical to reducing emissions. However, when traces are unterminated, ringing can result from the high *dv/dt* edge rates of digital signals and create radiated emissions. There are two common ways to reduce ringing. One is to add series resistors near the digital outputs of the IC to 'source' terminate the line. Typically, these are chosen to be around the same value as the characteristic impedance of the trace. The other method is to place a series resistor and a shunt capacitor at the end of trace to "end terminate" the line. Again, choose the resistor to match the characteristic impedance of the trace. The capacitor will set a corner frequency, so ensure a value is chosen to allow the frequency of interest to pass to the load. Figure 6.5 Source and End Terminations on page 21 shows the two locations for terminating a trace between ICs.

Figure 6.5. Source and End Terminations

## 7. Techniques for Reducing Emissions from Common-Mode Currents

Galvanic isolation can be extremely effective for providing human safety, improving noise immunity between circuits, signal level translation, and more. However, galvanic isolation can also have the side effect of increasing common-mode (E field) coupling between the isolated circuits. The resulting coupled common-mode signals can cause additional emissions as they take unintended paths back to their source. The loop area resulting from these unintended return paths can be quite large depending on cable length and distance between conductors and a reference ground plane. Whereas differential-mode noise is primarily a function of di/dt, common-mode noise is a function of dv/dt. In many applications, it is not practical to reduce di/dt without changing to the basic operation of the circuit. However, in switch mode power supplies, there are ways to reduce di/dt by adding a filter or clamp known as a snubber circuit.

Other methods that can be used to reduce emissions include shielding connected cable harnesses, moving conductors closer to a reference ground plane, placing safety capacitors between the power domains, or placing common-mode chokes in the suspected path of the common-mode currents. This design guide will focus on the addition of safety capacitors and common-mode chokes, which can be added to the same circuit board that contains the isolators.

#### 7.1 Adding Capacitance Between Power Domains

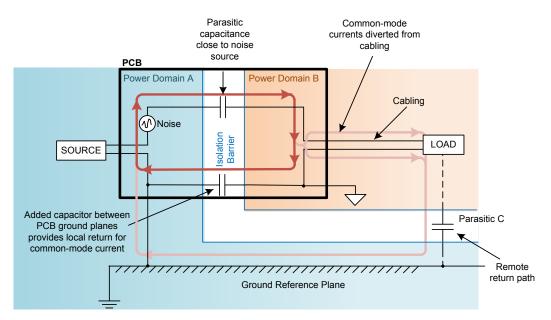

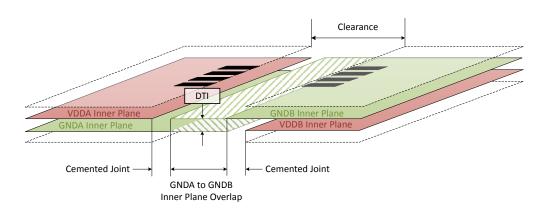

Adding a capacitor between the two power domains near the isolator provides a local return path for common-mode currents that can be much shorter than the parasitic paths these currents may otherwise take. This effect is depicted in Figure 7.1 Capacitive Coupling between Power Domains on page 23.

Figure 7.1. Capacitive Coupling between Power Domains

Galvanic isolation is maintained with this additional capacitive coupling between power domains, as capacitors block dc, or steady state, current. But there are performance effects to consider. If the capacitor bridges line to earth ground of an ac power system, then adding a capacitor will cause current leakage. Standards will dictate how much leakage between line and ground is allowable with IEC 60601 for medical devices being the most stringent. It specifies a maximum leakage to earth ground currents for some medical devices to be no greater than 10 µA.

Additional capacitance also degrades the ability to isolate switching noise to one power domain. Digital isolators are commonly used to transmit and receive signals from a quiet power domain to noisy one. A perfect example is using split power domains to isolate high voltage, high-current switching transients of a switch-mode power supply (SMPS) from the low voltage logic controller. By employing multiple power domains, the noise generated by the high power switching is isolated from the rest of the system that may include the sensitive logic. Silicon Labs isolators have a very low side-to-side capacitance (typically 1 to 2 pF) so they don't provide much coupling for the noise to propagate throughout the system. Placing a capacitor in parallel with the isolator will increase noise coupling proportion-al to the value of the capacitance.

International safety standards often specify test methods and limits for leakage currents. Increasing the capacitance across the isolation barrier may increase the ac leakage current that crosses the barrier. Depending on the system requirements, adding capacitance could solve a radiated emissions problem yet create a leakage problem. For this reason, it is recommended to use just enough additional capacitance to meet the desired radiated emissions profile.

There are two ways to add capacitance across the isolation barrier. One is to use a safety capacitor and the other is to build a capacitor using inner layers of the PCB. Safety capacitors are denoted as either X or Y depending on the location used. In ac power distribution, X locations are between line to line or line to neutral and Y locations are between line and earth. The subclass number that immediately follows the X or Y indicates the voltage rating per IEC 60384-14. Most isolated systems will require Y1 or Y2 safety capacitors. These have working voltages of =<500VAC or <300VAC respectively and peak impulse voltage ratings of 8 kV and 5 kV respectively. The designer should choose a safety capacitor with ratings to match or exceed the isolator's voltage rating as required for their end system.

Y1 and Y2 capacitors are commercially available in values from 5pF to 10nF. As with any capacitor, there is parasitic inductance to consider and this inductance limits the frequencies at which the capacitor is useful for minimizing radiated emissions from commonmode currents. As such, safety capacitors are most effective at filtering harmonics (<10s of MHz) from an isolated SMPS.

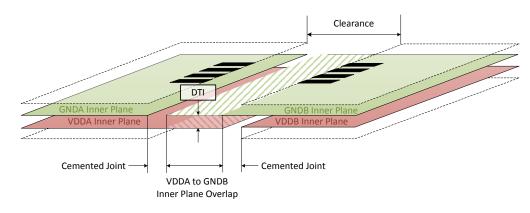

To provide a return path for even higher frequencies, a high-quality, distributed capacitance can be created by overlapping solid power and for ground planes of isolated power domains as shown in Figure 7.2 PCB Capacitor across the Isolation Barrier: VDDA to GNDB on page 24 and Figure 7.3 PCB Capacitor across the Isolation Barrier: GNDA to GNDB on page 24. Note that in this second case, the PCB stack-up changes between power domains allowing the GNDA and GNDB planes to overlap. This is the same technique as described to improve bypassing of supplies. However, now the capacitance created is the overlap of one inner plane from each side of the isolation barrier. Examining Equation 1 shows there are physical limitations to how much capacitance can be added. Each square centimeter of overlap with inner plane spacing of 1mm yields about 4pF of capacitance. AN1131: Design Guide for Reducing Radiated and Conducted Emissions in Isolated Systems Using Silicon Labs' Isolators Techniques for Reducing Emissions from Common-Mode Currents

Figure 7.2. PCB Capacitor across the Isolation Barrier: VDDA to GNDB

Figure 7.2 PCB Capacitor across the Isolation Barrier: VDDA to GNDB on page 24

Figure 7.3. PCB Capacitor across the Isolation Barrier: GNDA to GNDB

When choosing between adding a safety capacitor and designing a capacitor in the PCB structure, consider the dielectric strength and reliability of the FR4 material and PCB manufacturing process. The advantage of the commercially available safety capacitors is that they are constructed, tested and certified to standards much like the isolators that also bridge the isolation barrier. Nevertheless, FR4 material is low cost yet has a relatively high dielectric strength, approximately 20 kV/mm and most IEC specifications including IEC 60950 and IEC 61010 only require 0.4 mm of distance through insulation (DTI) with cemented joints to be rated Basic/Supplemental or Reinforced. If the design chooses to use the PCB cap structure method, they will want to consider how the PCB insulation changes over temperature or lifetime as the insulation rating is now dependent on construction materials and geometry for compliance. Moreover, testing and an accelerated life stress may be prudent to ensure the PCB remains compliant. Designers will also want to consider using a DTI spacing greater than the minimum 0.4mm for better insulation performance and lifetime margin.

#### 7.2 Using Common-Mode Chokes to Reduce Emissions

When common-mode currents couple into long conductors or cabling that can act as an effective radiating antenna, high levels of radiated emissions can result. Common-mode chokes can often be used to attenuate the common-mode signals on these paths while allowing differential signals to pass relatively unaffected. A common-mode choke is constructed with two windings on the same core such that when current through them is in the opposite direction, the magnetic flux generated in the core cancels enabling the choke to behave like wires, providing no additional impedance. But currents in the same direction will be presented with a large impedance due to the magnetic flux in the core summing. As currents return to their source in the path of least inductance, common-mode chokes are effective at blocking these currents from propagating through the system. Figure 7.4 Adding a Common-Mode Choke to Block Common-Mode Currents on page 25 is the same circuit presented in Figure 7.1 Capacitive Coupling between Power Domains on page 23 but it adds a common-mode choke before the cables that connect the load.

Figure 7.4. Adding a Common-Mode Choke to Block Common-Mode Currents

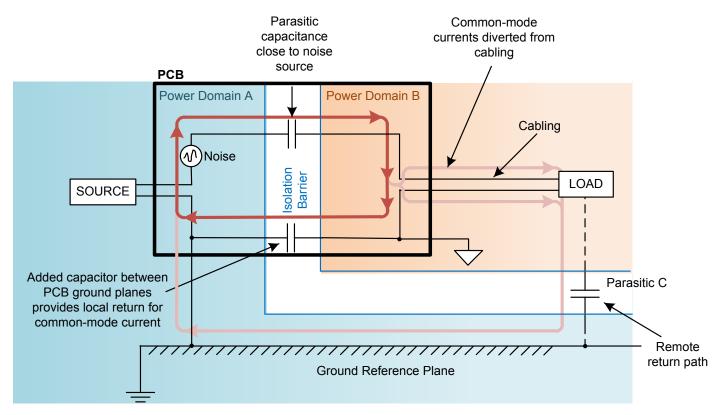

Just as there are parasitic elements such as ESL found in real-world capacitors that reduce their effectiveness as bypass capacitors, there are parasitic elements that limits the effectiveness of common-mode chokes. An ideal common-mode choke will present no impedance to differential signals and infinite impedance to common-mode signals. Figure 7.5 Impedance vs. Frequency for a Non-Ideal Common-Mode Choke on page 26 shows the impedance vs. frequency characteristic curves of a non-ideal common-mode choke for both differential-mode currents and common-mode currents. At frequencies above self-resonance, a common-mode choke behaves as a capacitor, thus failing to provide a block to prevent the currents propagating through the system. There is also a non-ideal curve for the impedance presented to differential-mode currents. As frequency increases, the parasitic inductance seen by the differential signals will present an increasing impedance until it reaches its self-resonance. This frequency is usually much higher than the self-resonant frequency of the common-mode impedance.

Figure 7.5. Impedance vs. Frequency for a Non-Ideal Common-Mode Choke

When choosing a common-mode choke, choose one that has a self-resonant frequency higher than the frequency of the commonmode noise that is desired to be blocked. If the common-mode choke is used to eliminate common-mode noise on high-speed differential signals, ensure that the differential-mode impedance is low enough to allow the signals to pass. Too much series inductance will attenuate and distort the desired signals.

### 8. Controlling Emissions in Designs using Digital Isolators with Integrated DC-DC Controllers

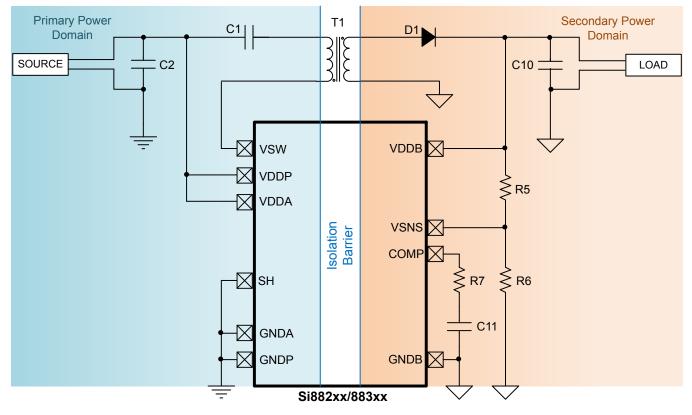

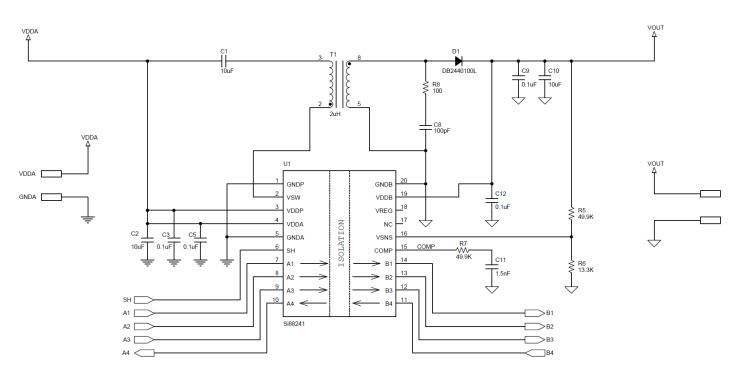

The Si882xx/3xx isolators combine either two or four digital data isolation channels with a dc-dc controller to provide an isolated power supply. The output of the dc-dc converter is used to power the isolated side of the digital channels as well as other circuitry that may reside in that power domain. The controller integrates power switches and isolated voltage feedback regulation. To complete the dc-dc converter, an external flyback transformer and several discrete passive components are needed as shown in Figure 8.1 Si882xx/3xx DC-DC Circuit on page 27. The dc-dc circuit topology is known as an asymmetric half bridge flyback and its theory of operation and component selection guide is found in Silicon Labs AN892.

The flyback nature of this converter topology is prone to producing ringing in the secondary, which can become a common-mode noise source and lead to increased emissions. This section of the design guide examines the potential noise sources with this dc-dc converter and suggests methods to reduce the emissions caused by them. Section 9. Case Study 1: CISPR 25 Radiated Emissions for an Si88241 Design and section 10. Case Study 2: CISPR 25 Conducted Emissions for an Si88241 Design illustrate improvements realized in radiated emissions and in conducted emissions, respectively, for Si88241 designs.

Figure 8.1. Si882xx/3xx DC-DC Circuit

#### 8.1 Primary-Side Loop Currents

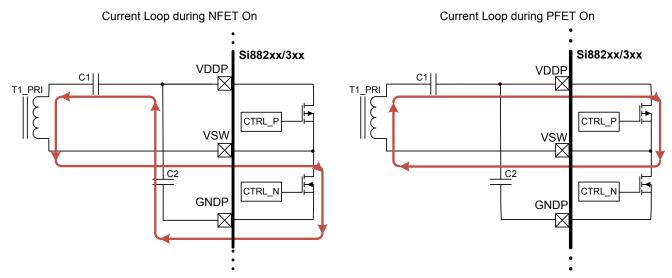

Figure 8.2 Primary-Side Loop Current Paths on page 28 shows the path of the current flow in the primary loop during the two switching conditions of the asymmetric half-bridge flyback. In each condition, the current flow has a well-defined path and is classified as a differential current.

Figure 8.2. Primary-Side Loop Current Paths

To minimize emissions from this type of circuit, the designer should minimize the area of the the current loops depicted above. Components C1, C2, and T1 should be placed close to pins 1-3 of the Si882xx/3xx. Also, consider routing traces on both top and bottom layers of the board so that the VSW currents are run directly beneath thus minimizing the loop area. Note that wide, low-inductive traces are preferred and they should use large through vias to connect them. Moreover, consider voiding any power or ground plane around the VSW node to reduce coupling to the primary side power or ground nodes.

Additionally note that the asymmetric half-bridge converter differs from a traditional flyback dc-dc converter topology as there is no large voltage impressed on the power transistors during the off switching cycle. The topology limits the voltage stress to no more than the source voltage so a primary side snubber is not needed to protect the switch. C1 and the primary winding of T1 do create a tank circuit during the time when the PFET is turned on and NFET is off. Therefore, it may be tempting to add a damping resistor between the transformer and the VSW to reduce the ringing from this tank circuit, but even a small amount of resistance will interfere with this converter's operation.

#### 8.2 Secondary-side Loop Currents

Figure 8.3 Secondary-Side Loop Current Paths on page 28 shows the current flow in the secondary loop during operation. When the primary PFET is on and NFET is off, current will flow from the secondary winding, through D1 and it will charge C10. When the primary NFET is on and the PFET is off, current will no longer flow from the T1 secondary winding. The load will be supplied by C10.

Figure 8.3. Secondary-Side Loop Current Paths

In each case, the currents present in the secondary have clearly defined paths, and the way to reduce their contribution to emissions is to minimize the loop area of these paths. It is recommended to use ground planes for returns. Since the T1\_SEC node will be switching, to reduce its coupling to the local ground, consider voiding the ground plane beneath it.

AN1131: Design Guide for Reducing Radiated and Conducted Emissions in Isolated Systems Using Silicon Labs' Isolators Controlling Emissions in Designs using Digital Isolators with Integrated DC-DC Controllers

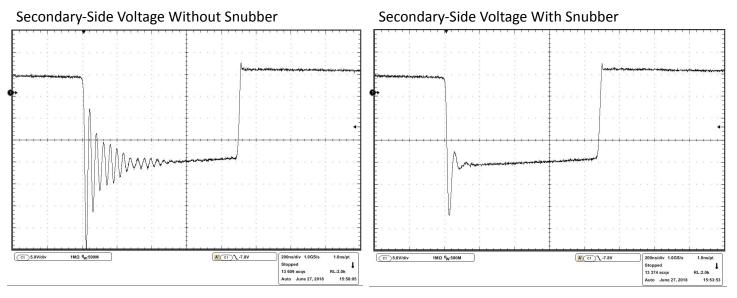

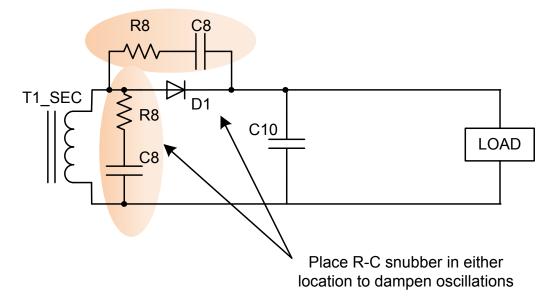

#### 8.3 Using Secondary-Side Snubber Circuit to Reduce Emissions Due to Ringing

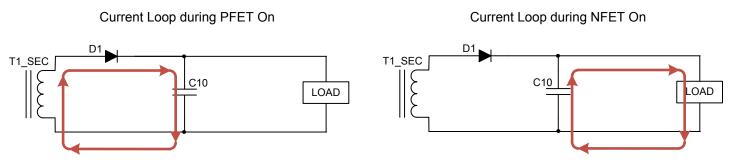

As the voltage changes polarity in the secondary winding, D1 goes from forward conducting to reverse biased and the current is blocked. Inductors will create a voltage spike when current through them changes quickly. This voltage transient, when applied to the tank circuit created by the secondary winding's inductance leakage and the parasitic capacitance present at that node, results in voltage overshoot and ringing at T1\_SEC – D1 node. Figure 8.4 Secondary-Side Ringing With and Without Snubber on page 29 shows the natural ringing (approximately 30 MHz) present at T1\_SEC – D1 node during operation without a snubber circuit installed.

Figure 8.4. Secondary-Side Ringing With and Without Snubber

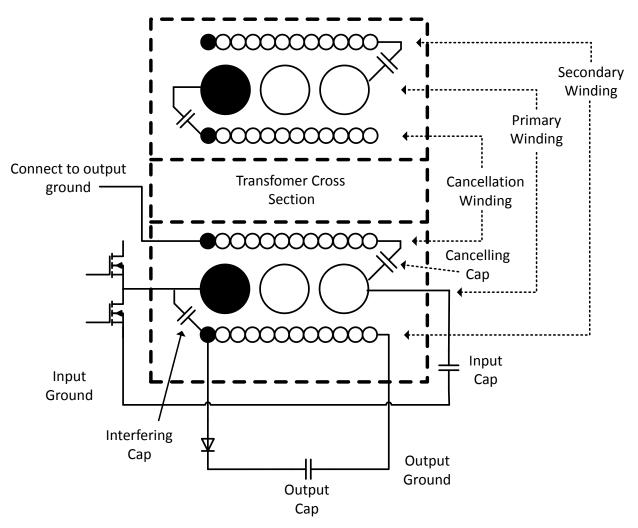

D1 must be rated to withstand the amplitude of the overshoot associated with this ringing as it is an applied reverse bias. But this ringing also becomes a common-mode noise source when applied to the unavoidable, across-the-isolation-barrier, parasitic capacitance of the transformer. A simplified model of the resulting common-mode current is shown in Figure 8.5 Common-Mode Current from Flyback Ringing in Secondary-Side Circuit on page 29.

Figure 8.5. Common-Mode Current from Flyback Ringing in Secondary-Side Circuit

As mentioned, for a common-mode noise source, the methods available to reduce the emissions resulting from ringing in the secondary are: reduce dv/dt of the noise, place a capacitor between the primary and secondary power domains for local return of common-mode current, or place a common-mode choke in series with the conductors that run to the load to create an impedance to common-mode currents.

To reduce the amplitude of the ringing in this circuit, a series R-C network, also known as an R-C snubber, can be placed across the secondary of the T1 or across the blocking diode D1 as shown in Figure 8.6 R-C Snubber Options for Secondary-Side Ringing on page 30. During the two steady state conditions shown in Figure 8.3 Secondary-Side Loop Current Paths on page 28, Secondary-Side Loop Current Paths, no current will flow through the R-C. But during switching and oscillating, the capacitor will allow current to flow through the resistor and will dampen the tank circuit created by the leakage inductance of the secondary winding applied to the parasitic capacitance at the T1\_SEC-D1 node.

The values of  $100\Omega$  and 100pF were chosen for the secondary snubber in the Si88xxxISO reference design and placed in parallel with the secondary winding. This network provided a good compromise between the snubber's damping capabilities and its dissipated power. The resistor value was chosen to match the impedance of the resonance. To increase the damping, the designer can increase the value of the capacitor. However, note that the tradeoff is in efficiency, and that the power dissipated in the R-C snubber can be expressed as

Where C<sub>SNUBBER</sub> = capacitor value of the snubber

V = 18V, approximate reverse bias on D1 during switching

f<sub>sw</sub> = 250kHz, approximate switching frequency of the dc-dc

**Power Dissipated in Snubber Resistor**

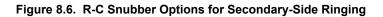

## 9. Case Study 1: CISPR 25 Radiated Emissions for an Si88241 Design

To demonstrate the effectiveness of the recommendations presented in this guide with respect to reducing radiated emissions, the radiated emissions from two Si88241 PCBs were measured to the CISPR 25 emission specification standard. Since the Si88241 bridges two separate power domains, the test procedure from Appendix I of the CISPR 25 was applied. The first PCB was the two-layer, costoptimized Si88xxISO customer evaluation board (EVB). The second emissions optimized PCB was designed and built with the exact the same circuit, but it included some of the layout techniques discussed in this application note for attenuating radiated emissions. In both designs, the secondary snubber remained unchanged from the evaluation board's 100 ohm + 100 pF, but the emissions optimized board included these features:

- Reduced primary and secondary current loops' area.

- Four-layer PCB with solid VDD and ground planes to enhance the effective supply bypassing.

- Inner plane overlap between the A-side GND and B-side VDD that added 19pF of additional capacitance.

- PCB edge ground rings.

This data was taken by Professional Testing Inc., in Round Rock Texas. Figure 9.1 Photograph of CISPR 25, Appendix I Test Setup on page 31 shows the test setup.

Figure 9.1. Photograph of CISPR 25, Appendix I Test Setup

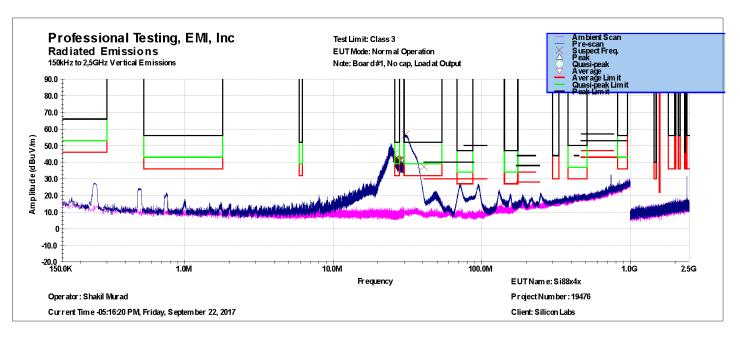

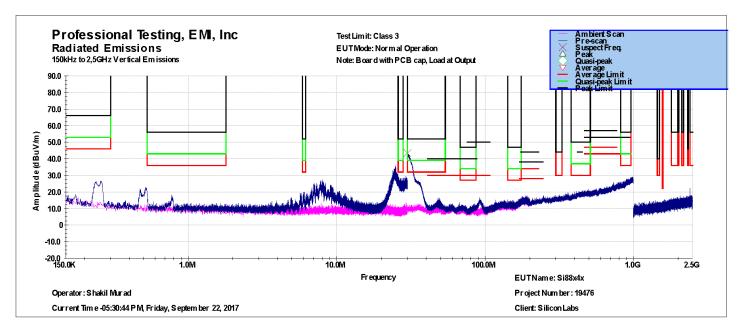

Figure 9.2 Emissions Profile of Two-Layer, Customer EVB on page 32 and Figure 9.3 Emissions Profile of Four-Layer, Optimized Layout PCB on page 32 show the measured emissions from the customer EVB and from the emissions optimized PCB, respectively. The two-layer, un-optimized board fails Class 3 profile limits at around 30MHz by 5dBuV/m. This is the same frequency of the observed secondary-side ringing as shown in Figure 8.4 Secondary-Side Ringing With and Without Snubber on page 29, Secondary-Side Ringing without any Snubber Installed. The four-layer, optimized board passes the Class 3 limits with 13dB improvement at this frequency band, providing 8dB of margin. Further reduction of emissions could be accomplished by adding an Y2-capacitor across the isolation barrier and/or including a common-mode choke in series with the cables, though these methods were not needed to meet the target profile.

Figure 9.2. Emissions Profile of Two-Layer, Customer EVB

Figure 9.3. Emissions Profile of Four-Layer, Optimized Layout PCB

## 10. Case Study 2: CISPR 25 Conducted Emissions for an Si88241 Design

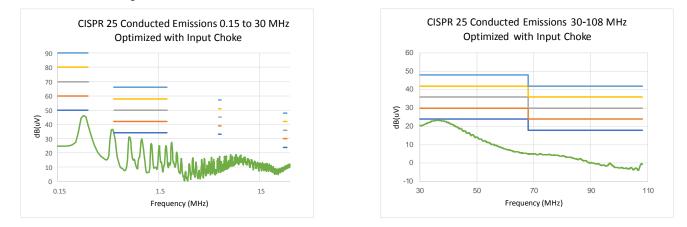

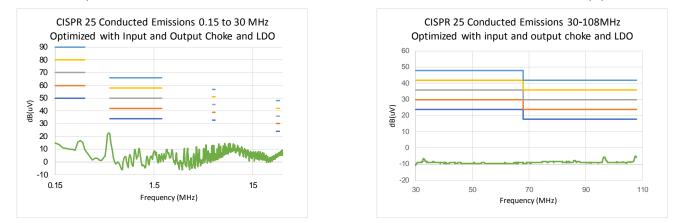

This case study demonstrates the effectiveness of the techniques presented in this paper with respect to reducing conducted emissions. CISPR 25 places limits on average, quasi-peak, and peak conducted emissions in various frequency bands for various equipment classes. For simplicity, this study focuses on average emissions in the range of 150 kHz to 30 MHz, measured with a resolution bandwidth of 9 kHz, and in the range of 30 MHz to 108 MHz, measured with a resolution bandwidth of 120 kHz.

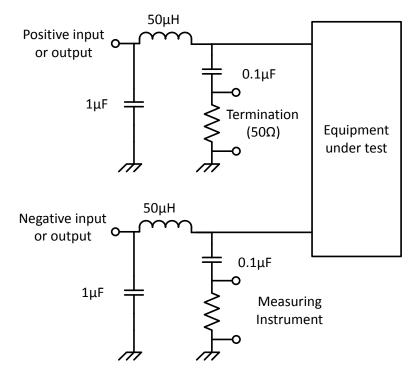

For power input to a dc to dc converter or power output from a dc to dc converter, CISPR 25 conducted emissions are measured using a 50 µH Artificial Mains Network (AN) or Line Impedance Stabilization Network (LISN).

Figure 10.1. LISN for Power Port Measurements

The same type of LISN is used on all input or output power wires. The measuring port on each LISN must be terminated with 50  $\Omega$ , which can be the input impedance of the measurement instrument or a resistive terminator, as shown in the figure above.

Conducted emissions can also occur on signal wires. For differentially routed signals (twisted pairs), conducted emissions result from either a common mode component of the signal or from a voltage on a local ground which couples to both signal wires and then becomes a common mode voltage for the signal.

In this section, we focus on the conducted emissions caused by the Si88241 dc-dc converter with the measurement equipment connected to the output side ground. Note that these CISPR 25 conducted emission measurements are single-ended, so both common-mode and differential ac signals on the output port will be included in the measurement. This section focuses on causes of, and reduction of, common-mode conducted emissions. However, take care to minimize the contribution of differential signals. For example, be sure there is adequate input filtering to limit ripple on the supply input side.

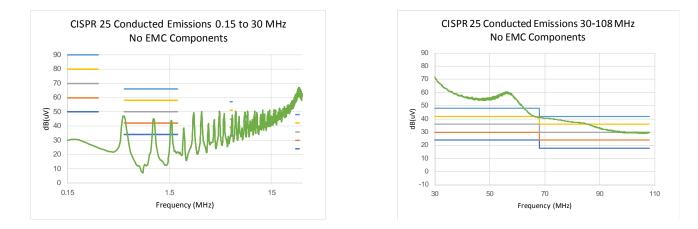

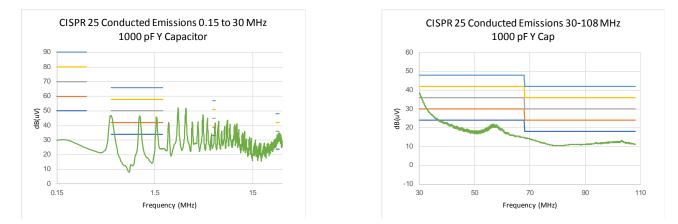

#### 10.1 Conducted Emissions Measurements without any Added EMC Components

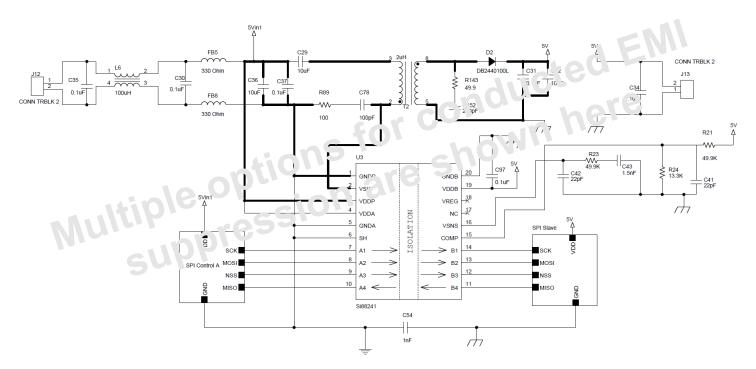

The basic dc-dc converter circuit of the Si88241 for 5 V input and 5 V output without additional EMC components is shown in the figure below:

Figure 10.2. Si88241 Circuit 5 V Input and 5 V Ouput