### APPROVED BY AICTE NEW DELHI, AFFILIATED TO VTU, BELGAUM

# DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

# ANALOG ELECTRONICS LABORATORY LAB MANUAL – 15ECL37 III-SEMESTER 2016-2017

Prepared by: Reviewed by: Approved by:

Pavan V S Kavitha M V Dr. A.A. Powly Thomas

Assistant Professor Head of the Department Principal Dept. of ECE Dept. of CSE GCEM

GCEM GCEM

81/1, 182/1, Hoodi Village, Sonnenahalli, K.R. Puram, Bengaluru, Karnataka-560048.

# **CONTENTS**

| S.No | Title               | Page No |

|------|---------------------|---------|

|      |                     |         |

| 1.   | Syllabus            | ii      |

| 2.   | Course objective    | iii     |

| 3.   | Course outcome      | iii     |

| 4.   | Do's & Don'ts       | iv      |

| 5.   | List of experiments | V       |

| 6.   | Viva questions      | 47-48   |

| 7.   | Appendix-1          | 49-52   |

#### **SYLLABUS**

- Design and set up the following rectifiers with and without filters and to determine ripple factor and rectifier efficiency: Full Wave Rectifier (b) Bridge Rectifier

- 2. Conduct experiment to test diode clipping (single/double ended) and clamping circuits (positive/negative).

- 3. Conduct an experiment on Series Voltage Regulator using Zener diode and power transistor to determine line and load regulation characteristics.

- 4. Realize BJT Darlington Emitter follower with and without bootstrapping and determine the gain, input and output impedances.

- 5. Design and set up the BJT common emitter amplifier using voltage divider bias with and without feedback and determine the gain bandwidth product from its frequency response.

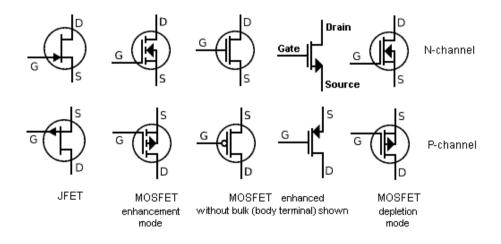

- 6. Plot the transfer and drain characteristics of a JFET and calculate its drain resistance, mutual conductance and amplification factor.

- 7. Design, setup and plot the frequency response of Common Source JFET/MOSFET amplifier and obtain the bandwidth.

- 8. Plot the transfer and drain characteristics of n-channel MOSFET and calculate its parameters, namely; drain resistance, mutual conductance and amplification factor.

- 9. Set-up and study the working of complementary symmetry class B push pull power amplifier and calculate the efficiency.

- 10.Design and set-up the RC-Phase shift Oscillator using FET, and calculate the frequency of output waveform.

- 11.Design and set-up the following tuned oscillator circuits using BJT, and determine the frequency of oscillation.

- a) Hartley Oscillator (b) Colpitts Oscillator

- 12.Design and set-up the crystal oscillator and determine the frequency of oscillation.

# **Course objectives:**

This laboratory course enables students to get practical experience in design, assembly, testing and evaluation of

- Rectifiers and Voltage Regulators.

- BJT characteristics and Amplifiers.

- JFET Characteristics and Amplifiers.

- MOSFET Characteristics and Amplifiers.

- Power Amplifiers.

- RC-Phase shift, Hartley, Colpitts and Crystal Oscillators

### Course outcomes:

Through this course, the students:

- Acquire a basic knowledge in solid state electronics including diodes, MOSFET, BJT, and operational amplifier.

- Develop the ability to analyze and design analog electronic circuits using discrete components.

- Observe the amplitude and frequency responses of common amplification circuits.

- Design, construct, and take measurement of various analog circuits to compare experimental results in the laboratory with theoretical analysis.

# **LAB INSTRUCTIONS**

# Do's

- Ensure your presence five minutes before the commencement of the lab.

- Attend all the lab sessions without fail.

- Come well prepared for every lab session.

- Complete and Bring the Lab records regularly.

- Ensure the proper polarity of cables before connecting the kits.

- Ensure the checking of the circuit of circuit connections before turning ON the circuit.

- Tuck in your shirts and not to play with instruments laid on the bench.

- Wearing loose garments inside the lab is strictly prohibited.

- You have to wear shoes compulsorily.

- Keep the space around you clear for others.

### Don'ts

- Don't bring the Cell phone and food items to Lab.

- Don't switch ON voltage supplies after making circuit connections in the absence of the teacher.

- Don't rotate the Knobs unnecessarily.

# LIST OF EXPERIMENTS

| SI No | Title                              | Page No |

|-------|------------------------------------|---------|

| 1     | Rectifiers                         | 1       |

| 2     | Clippers and Clampers              | 7       |

| 3     | Zener Diode                        | 20      |

| 4     | BJT Amplifiers                     | 23      |

| 5     | BJT Darlington Emitter Follower    | 27      |

| 6     | Hartley and Colpitts oscillator    | 31      |

| 7     | Crystal Oscillator                 | 38      |

| 8     | Class B push -Pull amplifier       | 41      |

| 9     | JFET Characteristics               | 43      |

| 10    | JFET Common Source Characteristics | 47      |

# **Experiment No: 1**

# DATE:

# **FULL WAVE RECTIFIER**

#### AIM:

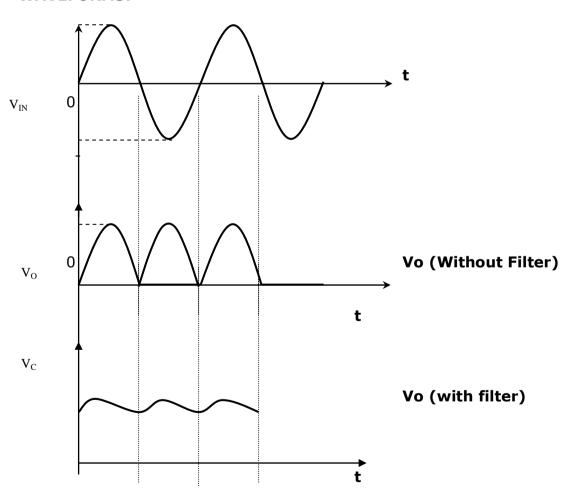

To study the full wave rectifier and to calculate ripple factor and efficiency and Regulation with filter and without filter.

### **COMPONENTS REQUIRED:**

| SI. No. | Components Details                              | Specification                 | Qty        |  |

|---------|-------------------------------------------------|-------------------------------|------------|--|

| 1.      | Diodes                                          | BY127                         | 2 Nos.     |  |

| 2.      | Capacitor                                       | 0.1μ <i>f</i> , 470μ <i>f</i> | Each 1 No. |  |

| 3.      | Power Resistance Board                          |                               | 1 No.      |  |

| 4.      | Step down Transformer                           | 12 V                          | 1 No.      |  |

| 5.      | CRO, Multimeter, Milliammeter, Connecting Board |                               |            |  |

#### THEORY:

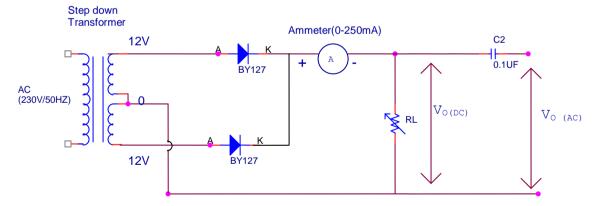

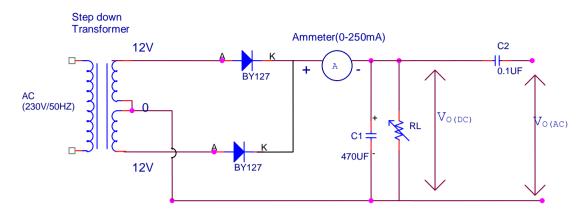

The center tapped full wave rectifier circuit is similar to a half wave rectifier circuit, using two diodes and a center tapped transformer. Both the input half cycles are converted into unidirectional pulsating DC.

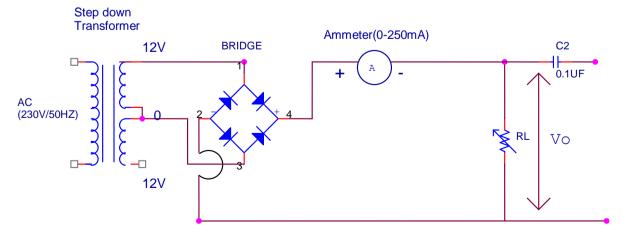

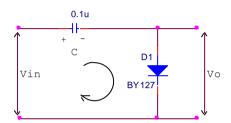

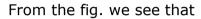

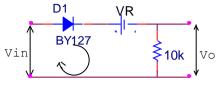

#### **CIRCUIT DIAGRAM:**

### **FULL WAVE RECTIFIER WITHOUT FILTER CAPACITOR**

### **FULL WAVE RECTIFIER WITH FILTER CAPACITOR**

#### **DESIGN:**

#### Vin rms = 12V

Vin m =

$$\sqrt{2}$$

Vin rms = 16.97V

$$V_{O\ DC} = 2Vm/\pi = 10.8V$$

Given

$$V_{O\ DC} = 10V$$

$$I_{O\ DC} = 100mA$$

$$R_L = V_{O\ DC} / I_{O\ DC} = 100\Omega$$

# Ripple = $r = Vo \ rms / V_{O \ DC} = 0.48$

Design for the filter capacitor

Ripple =

$$1/(4\sqrt{3} \text{ f C R}_L)$$

Given

$$r = .06$$

$$C = 1/(4\sqrt{3} f r R_L)$$

$$R_L = 100\Omega$$

$$f = 50Hz$$

#### = 470UF

Efficiency

$$\eta = PDC / PAC \Rightarrow (I^2_{DC} * R_L) / [(Irms)^2 * (R_L + R_F)]$$

**Regulation** % Regulation =

$$\frac{V_{NL} - V_{FL}}{V_{FL}} \times 100$$

#### **PROCEDURE:**

- 1. Connections are made as shown in the circuit diagram

- 2. Switch on the AC power supply

- 3. Observe the wave form on CRO across the load resistor and measure the o/p amplitude and frequency.

- 4. Note down  $R_{L},\ I_{DC,}\ V_{ODC}$  , Vinac, Voac  $\ \ in$  the tabular column for different load resistances.

- 5. Calculate the ripple and efficiency and regulation for each load resistance.

- 6. Repeat the above procedure with filter capacitor.

#### **TABULAR COLUMN:**

| SI.<br>No. | R <sub>L</sub> | $\mathbf{I}_{DC}$ | <b>V</b> <sub>0</sub> (DC) | V <sub>IN</sub> (AC) | V <sub>O</sub> (AC) | Ripple | Efficiency | Regulation |

|------------|----------------|-------------------|----------------------------|----------------------|---------------------|--------|------------|------------|

|            |                |                   |                            |                      |                     |        |            |            |

|            |                |                   |                            |                      |                     |        |            |            |

|            |                |                   |                            |                      |                     |        |            |            |

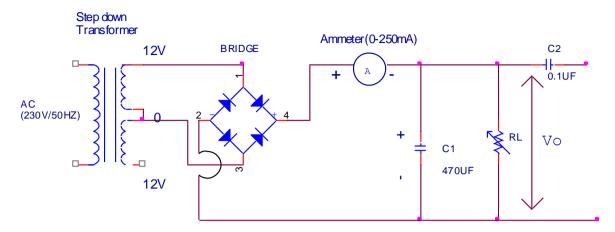

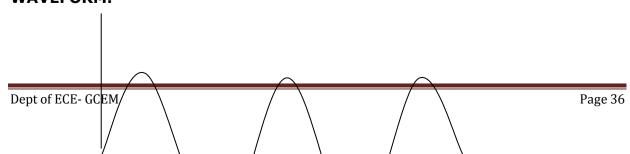

### **WAVEFORMS:**

# Experiment No: 1b DATE:

# **BRIDGE RECTIFIER**

#### AIM:

To study the bridge rectifier and to calculate ripple factor and efficiency and regulation with filter and without filter.

### **COMPONENTS REQUIRED:**

| SI. No. | Components Details                              | Specification                 | Qty        |  |

|---------|-------------------------------------------------|-------------------------------|------------|--|

| 1.      | Diodes                                          | BY127                         | 4 Nos.     |  |

| 2.      | Capacitor                                       | 0.1μ <i>f</i> , 470μ <i>f</i> | Each 1 No. |  |

| 3.      | Power Resistance Board                          |                               | 1 No.      |  |

| 4.      | Step down Transformer                           | 12 V                          | 1 No.      |  |

| 5.      | CRO, Multimeter, Milliammeter, Connecting Board |                               |            |  |

#### THEORY:

The bridge rectifier circuit is essentially a full wave rectifier circuit, using four diodes, forming the four arms of an electrical bridge. To one diagonal of the bridge, the ac voltage is applied through a transformer and the rectified dc voltage is taken from the other diagonal of the bridge. The main advantage of this circuit is that it does not require a center tap on the secondary winding of the transformer; ac voltage can be directly applied to the bridge.

The bridge rectifier circuit is mainly used as a power rectifier circuit for converting ac power to dc power, and a rectifying system in rectifier type ac meters, such as ac voltmeter in which the ac voltage under measurement is first converted into dc and measured with conventional meter.

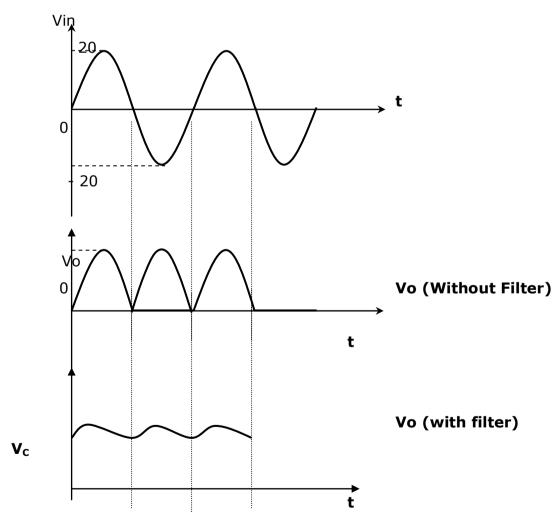

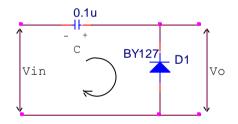

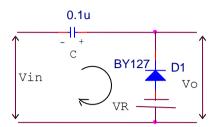

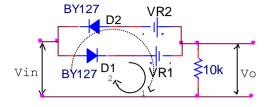

#### **CIRCUIT DIAGRAM:**

#### **BRIDGE RECTIFIER WITHOUT FILTER CAPACITOR**

#### BRIDGE RECTIFIER WITH FILTER CAPACITOR

#### **DESIGN:**

$$Vin rms = 12V$$

Vin m =

$$\sqrt{2}$$

Vin rms = 16.97V

$$V_{O\ DC} = 2Vm/\pi = 10.8V$$

Given

$$V_{ODC} = 10V$$

$$I_{O DC} = 100 mA$$

$$R_L = V_{ODC} / I_{ODC} = 100\Omega$$

# Ripple = $r = Vo rms / V_{ODC} = 0.48$

Design for the filter capacitor

Ripple =

$$1/(4\sqrt{3} \text{ f C R}_{L})$$

### Given r = .06

$$C = 1/(4\sqrt{3} f r R_L)$$

$$R_L = 100\Omega$$

$$f = 50Hz$$

#### = 470UF

### **Efficiency**

$$\eta = PDC/PAC$$

=

$$(I_{DC}^2 * R_L) / [(Irms)^2 * (R_L + R_F)]$$

$$\textit{Regulation} \qquad \text{\% Regulation = } \frac{V_{\mathit{NL}} - V_{\mathit{FL}}}{V_{\mathit{FL}}} \mathbf{X} 100$$

### **PROCEDURE:**

- 1. Connections are made as shown in the circuit diagram

- 2. Switch on the AC power supply

- 3. Observe the wave form on CRO across the load resistor and measure the o/p amplitude and frequency.

- 4. Note down  $R_{L}\text{, }I_{DC,\text{ }}V_{ODC\text{ },\text{ }}$  Vinac, Voac  $% P_{C}\text{, }$  in the tabular column for different load resistances.

- 5. Calculate the ripple factor, efficiency and regulation for each load resistance.

- 6. Repeat the above procedure with filter capacitor.

#### **TABULAR COLUMN:**

| SI.<br>No. | R <sub>L</sub> | I <sub>DC</sub> | V <sub>O</sub> (DC) | V <sub>IN</sub> | V <sub>O</sub> (AC) | Ripple | Efficiency | Regulation |

|------------|----------------|-----------------|---------------------|-----------------|---------------------|--------|------------|------------|

|            |                |                 |                     |                 |                     |        |            |            |

|            |                |                 |                     |                 |                     |        |            |            |

|            |                |                 |                     |                 |                     |        |            |            |

### **WAVEFORMS:**

# Experiment No: 2a DATE:

# **CLAMPING CIRCUITS**

#### AIM:

Design a clamping circuit for the given output.

### **COMPONENTS REQUIRED:**

| SI. No. | Components Details                                          | Specification | Qty  |

|---------|-------------------------------------------------------------|---------------|------|

| 1.      | Diodes                                                      | BY127         | 1 No |

| 2.      | Capacitors                                                  | 0.1 μF        | 1 No |

|         | Signal generator, Cathode F<br>Probes, Dual Power Supply, C |               |      |

#### THEORY:

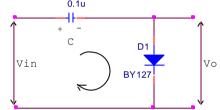

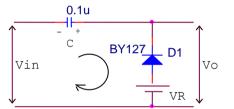

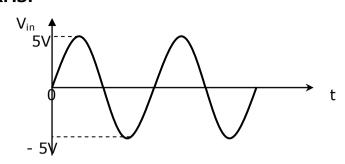

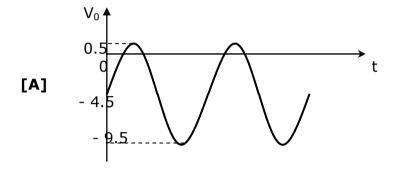

A clamper is one, which provides a D.C shift to the input signal. The D.C shift can be positive or negative. The clamper with positive D.C shift is called positive clamper and clamper with negative shift is called negative clamper. Consider a clamper circuit shown below.

In the positive half cycle as the diode is forward biased the capacitor charges to the value  $\left(V_{IN}-V_{D}\right)$  with the polarity as shown in the figure. In the negative half cycle the diode is reverse biased. Hence the output is  $V_{O}=V_{IN}-V_{C}$ .

Initially let us assume that the capacitor has charged to  $\left(V_{IN}-V_{D}\right)$  i.e. (5-0.5)=4.5V

Then in the positive half cycle diode is forward biased and applying KVL to the loop,

In the negative half cycle

When

$$V_{in} = -5V$$

$V_0 = -5 - 4.5 = -9.5V$

The output shifts between 0.5V and - 9.5V.Here the output has shifted down by 4.5V

The peak to peak voltage at the output of a clamper is the same as that of the input.

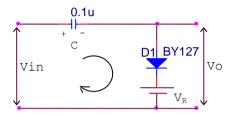

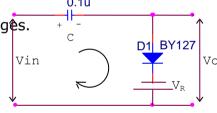

### **CIRCUIT DIAGRAM AND DESIGN:**

Given

$$V_{in} = 10V (p-p)$$

# A] In the positive half cycle:

Diode is forward biased.

Applying KVL to loop 1

$$V_{in} - V_C - V_D = 0$$

$$V_C = V_{in} - V_D$$

$$= 5 - 0.5 \Rightarrow 4.5V$$

$$\begin{split} &V_{in} - V_C - V_0 = 0 \\ &V_0 = V_{in} - V_C \\ &When \ V_{in} = 0 \qquad V_0 = -4.5V \\ &When \ V_{in} = 5V \quad V_0 = \ 0.5V \\ &When \ V_{in} = -5V \quad V_0 = -9.5V \end{split}$$

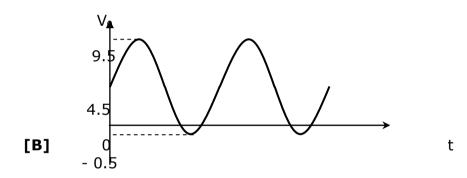

# B]In the negative half cycle:

Diode is forward biased

Applying KVL to loop 1

$$V_{in} + V_C + V_D = 0$$

$V_C = -(V_{in} + V_D)$

$V_C = -(-5 + 0.5)$

$= 4.5V$

# In the positive half cycle:

Diode is reverse biased.

Apply KVL to the loop

$$V_{in} + V_C - V_0 = 0$$

$$V_0 = V_{in} + V_C$$

When

$$V_{in} = 0$$

$V_0 = 4.5V$

When

$$V_{in} = 5V$$

$V_0 = 5 + 4.5 = 9.5V$

When

$$V_{in} = -5V$$

$V_0 = -0.5V$

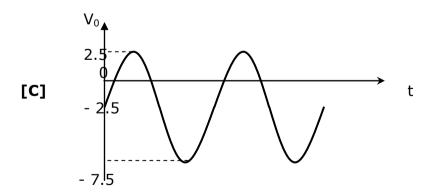

# C] Assume $V_R = 2V$

# In the positive half cycle:

Diode is forward biased.

Apply KVL to loop 1

$$V_{in} - V_C - V_D - V_R = 0$$

$$V_C = V_{in} - V_D - V_R$$

$$= 5 - 0.5 - 2$$

$$= 2.5V$$

# In the negative half cycle:

Diode is reverse biased

$$V_{in} - V_C - V_0 = 0$$

$$V_0 = V_{in} - V_C$$

When

$$V_{in} = 0V$$

$V_0 = -2.5V$

When

$$V_{in} = 5V$$

$V_0 = 2.5V$

When

$$V_{in} = -5V$$

$V_0 = -7.5V$

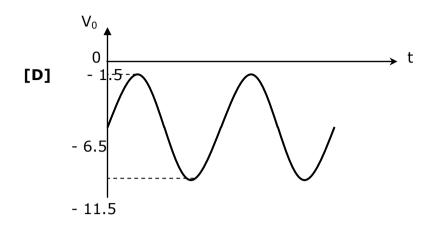

# D] Assume $V_R = 2V$

# In the positive half cycle:

Diode is forward biased and the capacitor charges.

Apply KVL to loop 1

$$V_{in} - V_C - V_D + V_R = 0$$

$V_C = V_{in} - V_D + V_R$

$= 5 - 0.5 + 2$

$= 6.5V$

# In the negative half cycle:

$$V_{in} - V_C - V_0 = 0$$

$$V_0 = V_{in} - V_C$$

When

$$V_{in} = 0V$$

$V_0 = -6.5V$

When

$$V_{in} = 5V$$

$V_0 = -1.5V$

When

$$V_{in} = -5V$$

$V_0 = -11.5V$

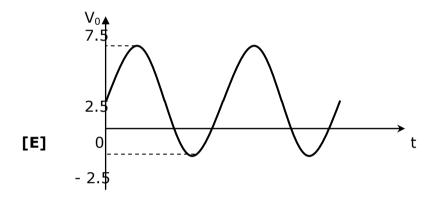

# ElIn the negative half cycle:

Assume  $V_R = 2V$

Diode is forward biased and capacitor charges.

Apply KVL to the loop1

$$V_{in} + V_C + V_D + V_R = 0$$

$$V_C = - (V_{in} + V_R + V_D)$$

$$= - (-5 + 0.5 + 2)$$

$$= 2.5V$$

$$V_{in} + V_C - V_0 = 0$$

$$V_0 = V_{in} + V_C$$

When

$$V_{in} = 0$$

$$V_0 = 2.5V$$

When

$$V_{in} = 5V$$

$$V_0 = 7.5V$$

When

$$Vin = -5V$$

$V0 = -2.5V$

$$V0 = -2.5V$$

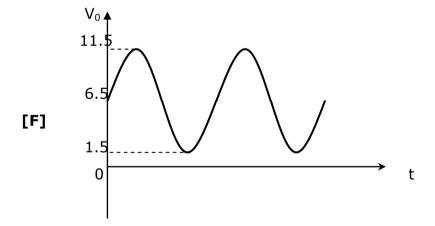

# F] VR = 2V

# In the negative half cycle:

Diode is forward biased and capacitor charges.

Apply KVL to loop 1

$$V_{in} + V_C + V_D - V_R = 0$$

$$V_C = - (V_{in} + V_D - V_R)$$

$$= - (-5 + 0.5 - 2)$$

$$= 6.5V$$

From the circuit we see that,

$$V_{in} + V_{C} - V_{0} = 0$$

$$V_0 = V_{in} - V_C$$

When

$$V_{in} = 0V$$

$$V_0 = 6.5V$$

When

$$V_{in} = 5V$$

$$V_0 = 11.5V$$

When

$$V_{in} = -5V$$

$V_0 = 1.5V$

$$V_0 = 1.5 V$$

- 1. Rig up the circuit as shown in the circuit diagram.

- 2. Give a sinusoidal input of 10V peak to peak

- 3. Check and verify the output.

# **WAVEFORMS:**

# **RESULT:**

Experiment No: 2b DATE:

# **CLIPPING CIRCUITS**

#### AIM:

Design a clipping circuit for the given values.

# **COMPONENTS REQUIRED:**

| SI. No. | c. Components Details Specification |       | Qty  |

|---------|-------------------------------------|-------|------|

| 1.      | Diodes                              | BY127 | 1 No |

| 2.      | Resistors                           | 10 ΚΩ | 1 No |

#### THEORY:

The process by which the shape of a signal is changed by passing the signal through a network consisting of linear elements is called linear wave shaping. Most commonly used wave shaping circuit is clipper. Clipping circuits are those, which cut off the unwanted portion of the waveform or signal without distorting the remaining part of the signal. There are two types of clippers namely parallel and series. A series clipper is one in which the diode is connected in series with the load and a parallel clipper is one in which the diode is connected in parallel with the load.

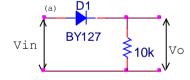

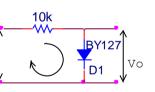

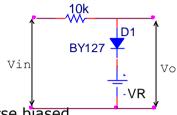

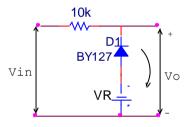

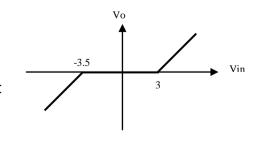

#### **CIRCUIT DIAGRAM AND DESIGN:**

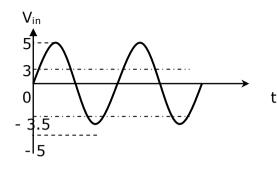

Assume  $V_{in} = 10V$  (Peak to Peak)

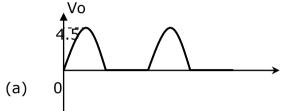

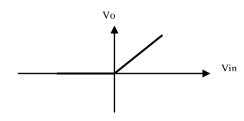

(a) Consider the circuit in fig. 1

In the  $\boldsymbol{positive}$   $\boldsymbol{half}$   $\boldsymbol{cycle}$  D is forward biased

$$\therefore$$

V<sub>0</sub> = V<sub>in</sub> - 0.5 = 5 - 0.5 = 4.5 (0.5V is the diode drop)

In the **negative half cycle** D is reverse biased

$$V_0 = 0$$

V

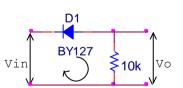

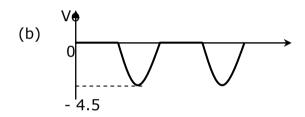

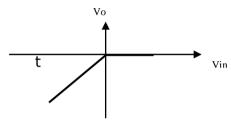

(b) Consider the circuit in fig. 2

In the **positive half cycle** D is reverse biased

$$V_0 = 0$$

In the  $\boldsymbol{negative}$   $\boldsymbol{half}$   $\boldsymbol{cycle}$  D is forward biased

Applying KVL to the loop

$$\therefore V_{in} + V_D - V_0 = 0$$

$$V_0 = V_{in} + V_D = -5 + 0.5 = -4.5V$$

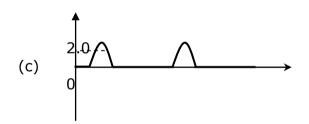

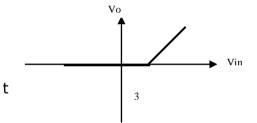

(c) Consider the circuit in fig. 3

Given  $V_R = 2.5V$

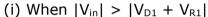

# In the positive half cycle

(i) When  $|V_{in}| > |V_D + V_R|$ , D is forward biased

Applying KVL, we get  $V_{in} = V_D + V_R + V_0$   $V_0 = V_{in} - V_D - V_R$   $V_0 = 5 - 0.5 - 2.5$

$$V_0 = 2V$$

(ii) When  $|Vin| < |V_D + V_R|$ , D is reverse biased  $V_0 = 0V$

In the negative half cycle, D is reverse biased

$$V_0 = 0V$$

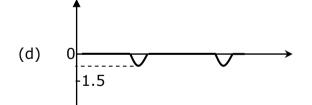

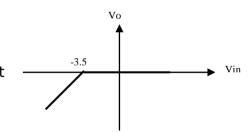

(d) Consider the circuit in fig. 4

Assume  $V_R = 3V$

In the **positive half cycle**, D is reverse biased

$$V0 = 0V$$

# In the negative half cycle

(i) When  $|V_{in}| > |V_D + V_R|$ , D is forward biased

Applying KVL, we get

$$V_{in} = -V_D - V_R + V_0$$

$V_0 = V_{in} + V_D + V_R$

$V_0 = -5 + 0.5 + 3$

$$V_0 = -1.5V$$

(ii) When  $|V_D + V_R|$ , D is reverse biased  $V_0 = 0V$

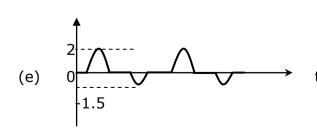

(e) Consider the circuit in fig. 5

Assume  $V_{R1} = 2.5V$  and  $V_{R2} = 3V$

In the **positive half cycle**,  $D_2$  is reverse biased

(i) When  $|V_{in}| > |V_{D1} + V_{R1}|$ ,  $D_1$  is forward biased

Applying KVL, we get

$$V_{in} = V_{D1} + V_{R1} + V_0$$

$$V_0 = V_{in} - V_{D1} - V_{R1}$$

$$V_0 = 5 - 0.5 - 2.5$$

$$V_0 = 2V$$

(ii) When  $|V_{D1} + V_{R1}|$ ,  $D_1$  is reverse biased  $V_0 = 0V$

# In the negative half cycle

(i) When  $|V_{in}| > |V_{D2} + V_{R2}|$ ,  $D_2$  is forward biased

Applying KVL, we get

$$V_{in} = -V_D - V_R + V_0$$

$$V_0 = V_{in} + V_{D2} + V_{R2}$$

$$V_0 = -5 + 0.5 + 3$$

$$V_0 = -1.5V$$

(ii) When  $|Vin < |V_{D2} + V_{R2}|$ , D2 is reverse biased

$$V_0 = 0V$$

(f) Consider the circuit in fig. 6

During the **positive half cycle**, D is forward biased

$$V_0 = V_D = 0.5V$$

During **negative half cycle**, D is reverse biasedvin

$$V_0 = V_{in}$$

Dept of ECE- GCEM

(g) Consider the circuit in fig. 7

During positive half cycle,

D is reverse biased

$$V_0 = V_{in}$$

During negative half cycle,

D is forward biased

$$V_0 = -V_D = -0.5V$$

(h) Consider the circuit in fig. 8

During positive half cycle

(i) When  $|V_{in}| > |V_D + V_R|$ ,

D is forward biased

$$V_0 = V_D + V_R = 0.5 + 2.5$$

$$V_0 = 3V$$

10k

(ii) When  $|V_{in}| < |V_D + V_R|$ , D is reverse biased

$$V_0 = V_{in}$$

During negative half cycle, D is reverse biased

$$V_0 = V_{in}$$

(i)Consider the circuit in fig. 9

Assume

$$V_R = 2.5V$$

During positive half cycle,

D is reverse biased

$$V_0 = V_{in}$$

During negative half cycle

(i) When  $|V_{in}| > |V_D + V_R|$ ,

D is forward biased

$$V_0 = -V_D - V_R = -0.5 - 2.5$$

$$V_0 = -3V$$

(ii) When  $|V_{in}| < |V_D + V_R|$ ,

D is reverse biased

$$V_0 = V_{in}$$

During negative half cycle, D is reverse biased

$$V_0 = V_{in}$$

(i) Consider the circuit in fig. 10

Assume

$$V_{R1} = V_{R2} = 2.5V$$

During positive half cycle,  $D_2$  is reverse biased.

(i) When  $|V_{in}| > |V_{D1} + V_{R1}|$ ,  $D_1$  is forward biased

$$V_0 = V_{D1} + V_{R1} = 0.5 + 2.5$$

$$V_0 = 3V$$

(ii) When  $|V_{in}| < |V_{D1} + V_{R1}|$ ,

$$\mathsf{D}_1$$

is reverse biased

$$V_0 = V_{in}$$

During negative half cycle,

D<sub>1</sub> is reverse biased

Vin

10k

D1

BY127 7

VR1

Applying KVL to the loop, we get

$$V_0 = -V_{D2} - V_{R2} = -0.5 - 2.5$$

$$V_0 = -3V$$

- (ii) When  $|V_{in}| < |V_{D2} + V_{R2}|$ ,  $D_2$  is reverse biased  $V_0 = V_{in}$

- (k) Consider the circuit in fig. 11

Assume

$$V_{R1} = 3.5V$$

and  $V_{R2} = 2V$

During positive half cycle

D<sub>1</sub> is forward biased and

D2 is reverse biased

D2

BY127

Vo

Vo

$$V_0 = V_{D1} + V_{R1} = 0.5 + 3.5 = 4 V$$

(ii) When  $|V_{in}| < |V_{R2} - V_{D2}|$

D<sub>1</sub> is reverse biased and

D<sub>2</sub> is forward biased

$$V_0 = -V_{D2} + V_{R2} = -0.5 + 2 \Rightarrow 1.5V$$

During negative half cycle,

D1 is reverse biased and D2 is forward biased

$$V_0 = -V_{D2} + V_{R2} = -0.5 + 2 \Rightarrow V_0 = 1.5V$$

#### **PROCEDURE:**

- 1. Rig up the circuit as shown in the fig.

- 2. Give a sinusoidal input of 10V peak to peak.

- 3. Check the output at the output terminal.

- 4. To plot the transfer characteristics, connect channel 1 of the CRO to the output and channel 2 to the input and press the XY knob

- 5. Adjust the grounds of both the channels to the centre.

- 6. Measure the designed values.

Dept of ECE-GCEM

t

# **WAVEFORMS:**

# **RESULT:**

# Shunt Clipper

Experiment: 03 DATE:

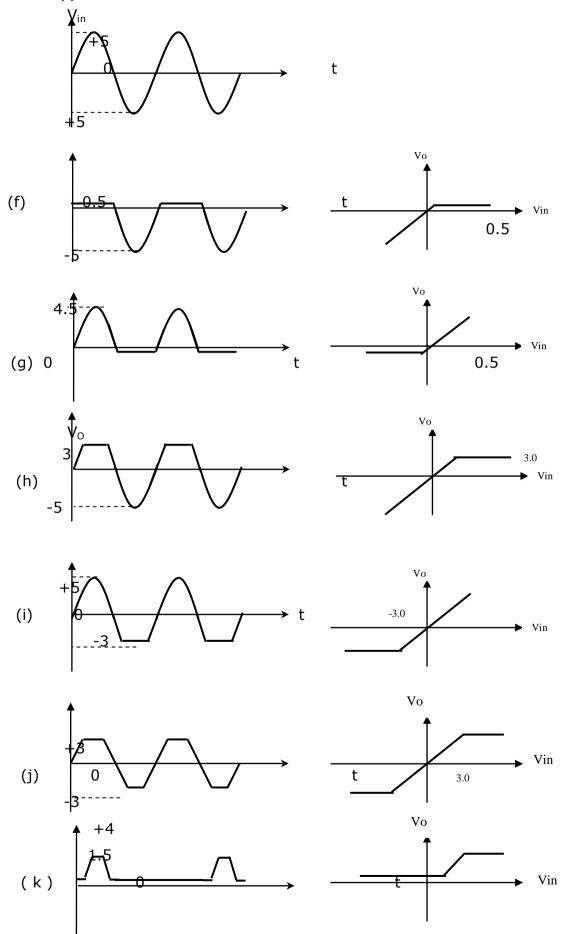

# **ZENER DIODE**

### AIM:

To study zener diode as voltage regulator, To calculate % line regulation, To calculate % load regulation.

**APPARATUS:** Zener diode, Resistors, Power supply, Multi meter.

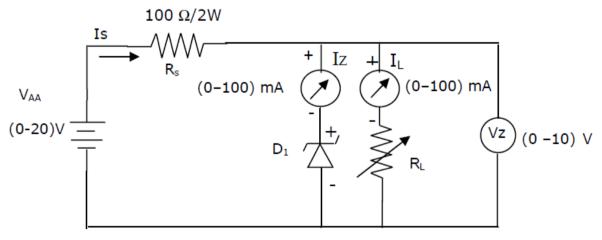

#### **CIRCUIT DIAGRAM:**

Line Regulation: Zener Regulator

Load Regulation: Zener Regulator

#### **THEORY:**

Zener diode is a P-N junction diode specially designed to operate in the reverse biased mode. It is acting as normal diode while forward biasing. It has a particular voltage known as break down voltage, at which the diode break downs while reverse biased. In the case of normal diodes the diode damages at the break down voltage. But Zener diode is specially designed to operate in the reverse breakdown region.

The basic principle of Zener diode is the Zener breakdown. When a diode is heavily doped, it's depletion region will be narrow. When a high reverse voltage is applied across the junction, there will be very strong electric field at the junction. And the electron hole pair generation takes place. Thus heavy current flows. This is known as Zener break down.

So a Zener diode, in a forward biased condition acts as a normal diode. In reverse biased mode, after the break down of junction current through diode increases sharply. But the voltage across it remains constant. This principle is used in voltage regulator using Zener diodes The figure shows the zener voltage regulator, it consists of a current limiting resistor RS connected in series with the input voltage Vs and zener diode is connected in parallel with the load RL in reverse biased condition. The output voltage is always selected with a breakdown voltage Vz of the diode.

**Regulation with a varying input voltage (line regulation):** It is defined as the change in regulated voltage with respect to variation in line voltage. It is denoted by 'LR'. In this, input voltage varies but load resistance remains constant hence, the load current remains constant. As the input voltage increases, form equation (3) Is also varies accordingly. Therefore, zener current Iz will increase. The extra voltage is dropped across the Rs. Since, increased Iz will still have a constant Vz and Vz is equal to Vout.

The output voltage will remain constant. If there is decrease in Vin, Iz decreases as load current remains constant and voltage drop across Rs is reduced. But even though Iz may change, Vz remains constant hence, output voltage remains constant.

Regulation with the varying load (load regulation): It is defined as change in load voltage with respect to variations in load current. To calculate this regulation, input voltage is constant and output voltage varies due to change in the load resistance value. Consider output voltage is increased due to increasing in the load current. The left side of the equation (4) is constant as input voltage Vin, IS and Rs is constant. Then as load current changes, the zener current Iz will also change but in opposite way such that the sum of Iz and IL will remain constant. Thus, the load current increases, the zener current decreases and sum remain constant. Form reverse bias characteristics even Iz changes, Vz remains same hence, and output voltage remains fairly constant.

#### **PROCEDURE:-**

#### A) Line Regulation:

- 1. Make the connections as shown in figure below.

- 2. Keep load resistance fixed value; vary DC input voltage from 5V to 15V.

- 3. Note down output voltage as a load voltage with high line voltage 'VHL' and as a load

Voltage with low line voltage 'VLL'.

4. Using formula, % Line Regulation = (VHL-VLL)/ VNOM x100, where VNOM = the nominal

load voltage under the typical operating conditions. For ex. VNOM =  $9.5 \pm 4.5 \text{ V}$

### **B) Load Regulation:**

- 1. For finding load regulation, make connections as shown in figure below.

- 2. Keep input voltage constant say 10V, vary load resistance value.

- 3. Note down no load voltage 'VNL' for maximum load resistance value and full load

- voltage 'VFL' for minimum load resistance value.

- 4. Calculate load regulation using, % load regulation = (VNL-VFL)/ VFL x100.

#### **Calculations:**

```

% Line Regulation = (VHL-VLL) / VNOM x100 = ---- \% % voltage regulation = (VNL-VFL)/VFLx100 = ---\%

```

#### **RESULT:**

Experiment No: 4

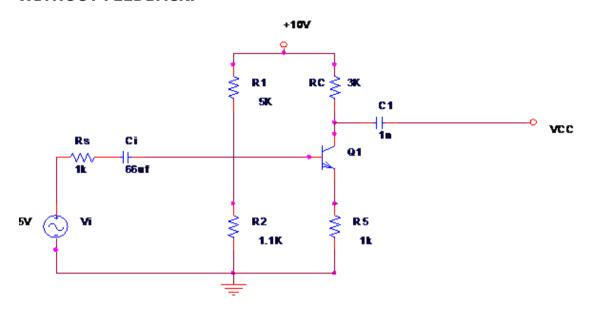

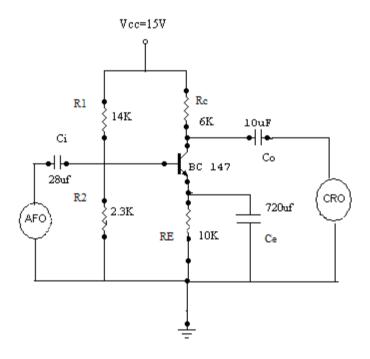

# **BJT AMPLIFIER**

#### AIM:

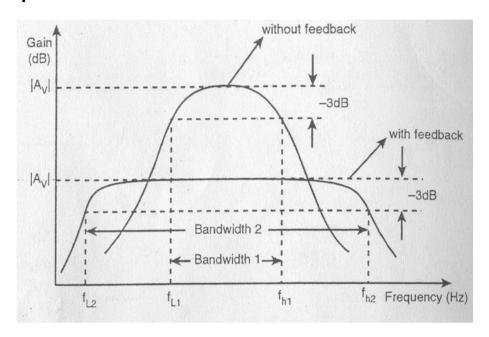

Design and set up the BJT common emitter amplifier using voltage divider bias with and without feedback and determine the gain bandwidth product from its frequency response.

**APPARATUS REQUIRED:**

| SI.No | APPARATUS    | RANGE                             | QUANTITY |

|-------|--------------|-----------------------------------|----------|

| 1     | AFO          | (0-1)MHz                          | 1        |

| 2     | CRO          | (0-20)MHz                         | 1        |

| 3     | Resistors    | 1.5ΚΩ,6ΚΏ,2ΚΩ,<br>14kΩ,2.3ΚΩ,10ΚΩ | Each one |

| 4     | Power supply | (0-30V)                           | 1        |

| 5     | Transistors  | BC 107                            | 1        |

| 6     | Capacitors   | 28pF, 10pF,720pF                  | 1        |

#### THEORY:

Negative feedback in general increases the bandwidth of the transfer function stabilized by the specific type of feedback used in a circuit. In Voltage shunt feedback amplifier, consider a common emitter stage with a resistance R' connected from collector to base. This is a case of voltage shunt feedback and we expect the bandwidth of the Trans resistance to be improved due to the feedback through R'. The voltage source is represented by its Norton's equivalent current source Is=Vs/Rs.

#### Design:

Given specifications:

VCC= 10V, IC=1.2mA, AV= 30, fI = 1 kHz, S=2, hFE= 150,  $\beta$ =0.4

The feedback factor,  $\beta = -1/RF = +1/0.4 = 2.5K'\Omega$

#### (i) To calculate RC:

The voltage gain is given by,

AV= -hfe (RC|| RF) / hie

$h ie = \beta re$

re = 26mV / IE = 26mV / 1.2mA = 21.6

hie =  $150 \times 21.6 = 3.2K$

Apply KVL to output loop,

VCC= IC RC + VCE+ IE RE ---- (1)

Where VE = IE RE (IC = IE)

VE= VCC / 10= 1V

Therefore RE=  $1/1.2x10-3=0.8K=1K'\Omega$

VCE= VCC/2= 5V

From equation (1), RC= 3 K $\Omega$

#### (ii) To calculate R1&R2:

S=1+(RB/RE)

$RB = (S-1) RE = R1 \mid\mid R2 = 1K\Omega$

RB= R 1R2 / R1+ R2----- (2)

VB = VBE + VE = 0.7 + 1 = 1.7V

VB= VCC R2 / R1+ R2 ----- (3)

Solving equation (2) & (3),

$R1 = 5 \text{ K'}\Omega \text{ & } R2 = 1.1 \text{K'}\Omega$

DATE:

# **CIRCUIT DIAGRAM**

# **WITHOUT FEEDBACK:**

# WITH FEEDBACK:

#### **PROCEDURE:**

- 1. Connect the circuit as per the circuit diagram.

- 2. Set VCC = 10V; set input voltage using audio frequency oscillator.

- 3. By varying audio frequency oscillator take down output frequency oscillator voltage for difference in frequency.

- 4. Calculate the gain in dB

- 5. Plot gain Vs frequency curve in semi-log sheet.

- 6. Connect the circuit as per the circuit diagram.

- 7. Set VCC = 10V; set input voltage using audio frequency oscillator.

- 8. By varying audio frequency oscillator take down output frequency oscillator voltage for difference in frequency.

- 9. Calculate the gain in dB

- 10. Plot gain Vs frequency curve in semi-log sheet.

- 11. Compare this response with respect to the amplifier without feedback.

#### **TABULATION:**

(With or without feedback)

| FREQUENCY | OUTPUT<br>VO(V) | Vin(V) | Gain = 20log(Vo/Vin) dB |

|-----------|-----------------|--------|-------------------------|

|           |                 |        |                         |

|           |                 |        |                         |

|           |                 |        |                         |

|           |                 |        |                         |

|           |                 |        |                         |

|           |                 |        |                         |

#### (iii) To calculate Resistance:

Output resistance is given by, RO= RC || RF RO= 1.3K' $\Omega$  input impedance is given by, Ri = (RB|| RF) || hie = 0.6K' $\Omega$  Trans-resistance is given by, Rm= -hfe (RB|| RF)( RC || RF) / (RB|| RF)+ hie

AC parameter with feedback network:

### (i) Input Impedance:

Rif = Ri /D (where D=  $1+\beta$  Rm)

Therefore D = 25

$Rm = 0.06K'\Omega$ .

Rif= 24

Input coupling capacitor is given by,

Xci = Rif / 10 = 2.4 (since XCi << Rif)

$Ci = 1/2\pi fXCi = 66\mu f$

#### (ii) Output impedance:

ROf = RO/D = 52

Output coupling capacitor:

XCO = Rof / 10 = 5.2

$CO = 1/2nfXCO = 30\mu f$

# (iii) Emitter capacitor:

XCE << R'E = R'/10  $R'E = RE|| \{( hie +RB) / (1+hfe)\}$  XCE = 2.7Therefore  $CE = 58\mu f$ .

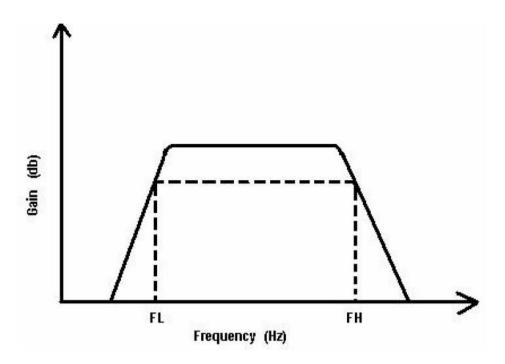

# **Model Graph:**

# **RESULT:**

# **Experiment No: 5**

# DATE:

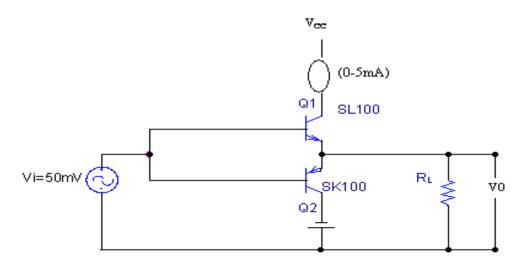

# **BJT DARLINGTON EMITTER FOLLOWER**

#### AIM:

To design and test a Darlington emitter follower circuit with and without boot strapping and determine the gain, input and output impedance.

### **COMPONENTS REQUIRED:**

| SI. No. | Components<br>Details               | Specification                     | Qty       |

|---------|-------------------------------------|-----------------------------------|-----------|

| 1.      | Transistor                          | SL100                             | 2 Nos.    |

| 2.      | Capacitors                          | 10 μ <i>f</i>                     | 1 No      |

| ۷.      | Capacitors                          | 0.47μ <i>f</i>                    | 2 Nos.    |

| 3.      | Resistors                           | 1 MΩ, 2.2 MΩ, 1.5 KΩ, 10 KΩ, 47KΩ | Each 1 No |

|         | DC Supply, CRO<br>AC millivoltmeter | with Probe, Signal generator,     |           |

#### **THEORY:**

Normally transistors are used as amplifiers. But there are some applications in which, matching of impedance is required between two circuits without any gain or attenuation. In such applications emitter followers are used. Emitter followers have large input impedance and small output impedance. Darlington emitter follower has two transistors connected in cascade such that the emitter of first transistor is connected to the base of second transistor. The voltage gain of the darlington emitter follower is close to unity. The major drawback of this circuit is that the second transistor amplifies leakage current of the first transistor and overall leakage current becomes high. The output is observed at the emitter terminal of the second transistor. Hence it is called an emitter follower.

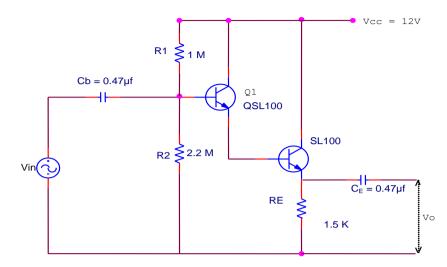

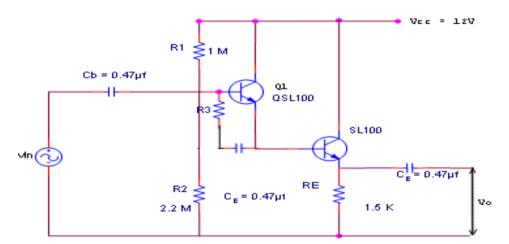

### **CIRCUIT DIAGRAM:**

# **Darlington emitter follower without bootstrapping**

# **Darlington emitter follower with bootstrapping**

### **DESIGN:**

Given

$$I_C = 4mA$$

,  $V_{CC} = 12V$ ,  $V_{BE} = 0.6V$ ,  $\beta_1 = \beta_2 = 100$

### To find R<sub>E</sub>:

Applying KVL to the output loop of the second transistor, we get

$$V_{CC} = V_{CE} + V_{RE}$$

Therefore

$$V_{RE} = V_{CC} - V_{CE} = 12 - 6$$

Therefore  $V_{RE} = 6V$

$$W.K.T R_E = V_{RE} / I_{E2}$$

Here

$$I_{E2} = I_{C2}$$

Therefore  $R_E = 6 / 4 \times 10^{-3}$

$$R_E = 1.5k\Omega$$

### To find R<sub>1</sub> & R<sub>2</sub>:

From the circuit we have

$$V_A = V_{BE1} + V_{BE2} + V_{RE}$$

= 0.6 + 0.6 + 6 = 7.2V

W.K.T.

$$I_C = \beta IB$$

Therefore  $I_B = (4 \times 10^{-3})/100 = 40 \mu A$

Let  $10I_B$  be the current through  $R_1$  and  $9I_B$  be the current through  $R_2$ .

From the fig. we see that

$$R_1 = (V_{CC} - V_A) / 10I_B$$

Therefore  $R_1 = 12K\Omega$

From the fig.  $R_2 = V_A / 9I_B$

Therefore  $R_2 = 20 \text{ K}\Omega \approx 22\text{K}\Omega$

W.K.T.

$$C_C = 10 / X_{RE} = 10 / (2.\pi.f.R_E)$$

Assume f = 50Hz

Therefore

$$C_c = 21.2 \mu F \approx 47 \mu F$$

W.K.T.

$$C_b = 10 / X_{RB} = 10 / (2.\pi.f.R_B)$$

where  $R_B = R_1 || R_2 = 7.5k\Omega$

Therefore  $C_b = 4.2 \mu F \approx 4.7 \mu F$

Chose  $R_3 = 10 \text{ K}\Omega$ ,  $C_B = 10 \mu f$  for bootstrapping

#### **PROCEDURE:**

- 1. Rig up the circuit as shown in the fig.

- 2. Check the circuit for biasing, i.e. check  $V_{CE}$ ,  $V_{CC}$  and  $V_{RE}$ .

- 3. Give a sinusoidal input signal of 1KHz from a signal generator.

- 4. Set the input signal to a value such that the output doesn't get clipped.

- 5. For different frequencies of the input signal, read the output on the voltmeter and verify that the gain is 1.

- 6. To measure input impedance, connect a resistor of  $47k\Omega$  in series with the signal generator.

- 7. Measure the voltage at the input point ( $V_S$ ) and at the point after the resistor ( $V_{IN}$ ).

Ι

- 8. Current through the resistor is given by the expression  $= (V_S V_{IN}) / 47K$ .

- 9. Input impedance is given by  $Z_{IN} = V_{IN} / 47 K$

- 10.To measure output impedance, connect a DRB in parallel with the output.

- 11. Adjust all the knobs of the DRB to maximum.

- 12.Start reducing the resistance in the DRB from a large value until the output reduces to half.

- 13. The resistance in the DRB is the output impedance.

# **TABULAR COLUMN:**

$V_{IN} = \underline{\hspace{1cm}}$  constant

| Frequency<br>(Hz) | V <sub>0</sub> (V) | Av | A <sub>v</sub> (dB) |

|-------------------|--------------------|----|---------------------|

|                   |                    |    |                     |

|                   |                    |    |                     |

|                   |                    |    |                     |

|                   |                    |    |                     |

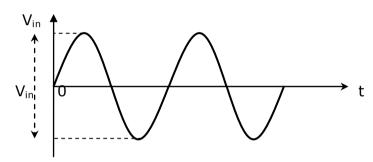

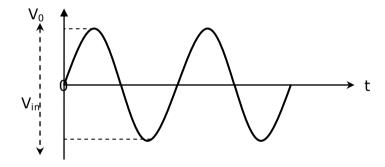

### **WAVEFORM:**

# **RESULT:**

# **Experiment No: 6**

# DATE:

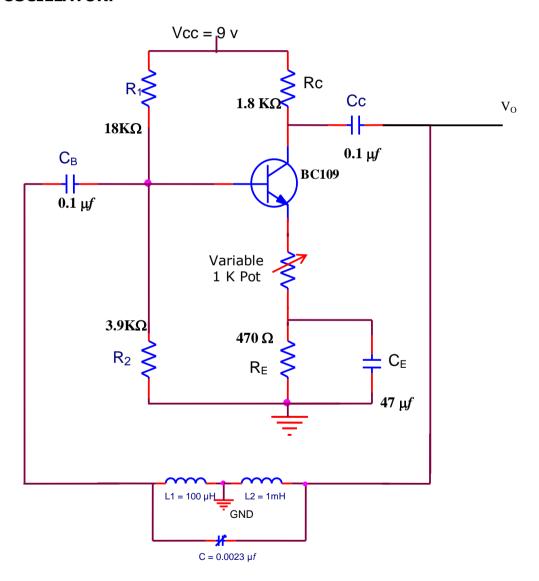

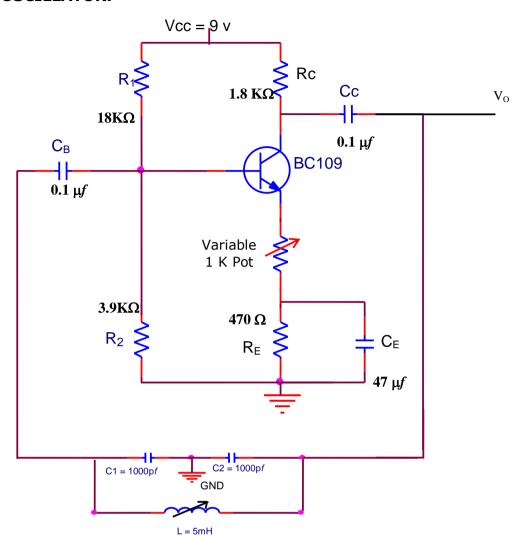

# **HARTLEY OSCILLATOR / COLPITT'S OSCILLATOR**

### AIM:

Design and set-up the following tuned oscillator circuits using BJT, and determine the frequency of oscillation.

## **COMPONENTS REQUIRED:**

| SI. No. | Components<br>Details | Specification                                               | Qty       |

|---------|-----------------------|-------------------------------------------------------------|-----------|

| 1.      | Transistor            | SL100                                                       | 1 No      |

| 2.      | Capacitors            | 0.1 μf, 1000 pf                                             | 2 No      |

|         |                       | 47μ <i>f</i> , 0.0023 μ <i>f</i>                            | Each 1 No |

| 3.      | Resistors             | 22Κ $\Omega$ , 4.7Κ $\Omega$ , 1.2Κ $\Omega$ , 330 $\Omega$ |           |

|         |                       | 1 K Pot                                                     | Each 1 No |

| 4.      | Inductors             | 100 μH, 1mH, 5mH                                            | Each 1 No |

|         | DC Supply, CRO with F |                                                             |           |

## **THEORY:**

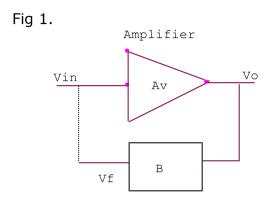

Oscillators are devices, which generate oscillations. The frequency of oscillations depends on the feedback network. Feedback may be of two types namely positive and negative. In positive feedback, the feedback signal is applied in phase with the input signal thus increasing it. In negative feedback, the feedback signal is applied out of phase with the input thus reducing it. The feedback used in oscillators is positive feedback. The oscillators work on the principle of Barkhausen criteria. This states that for sustained oscillations

- i) Loop gain  $Av\beta$  must be equal to 1.

- ii) The phase shift around the loop must be 0 deg of 360 deg.

Here Av is the gain of the amplifier and  $\beta$  is the attenuation of the feedback network. Consider the feedback network shown in the fig (1) below. Assume an amplifier with input signal Vin. The output signal Vo will be 180 deg out of phase with Vin. So to get an in phase output, the feedback network provides 180-deg phase shift. Therefore the output Vf from the feedback network can be made in phase and equal in amplitude to Vin and Vin can be removed. Even then the oscillations continue. Practical oscillations do not need any input signal to start oscillations. They are self-starting due to thermally produced noise in resistors and other components. Only one frequency (fo) of noise satisfies, Barkhausen

criteria and the circuit oscillates with that frequency. The magnitude of fo keeps on increasing each time it goes around the loop. The amplification of fo is limited by circuit's own non-linearities. Therefore to start oscillations  $Av\beta > 1$  and to sustain it, the loop gain  $Av\beta = 1$ .

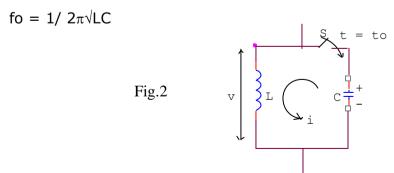

The feedback network used here consists of L and C. Consider the circuit shown below fig 2. This circuit consists of L and C in parallel. The capacitor stores energy in its electric field whenever there is voltage across it and the inductor stores energy in its magnetic field whenever there is current through it. Initially let us assume that the capacitor has charged to V volts. When S is closed c=0. When S is closed at  $t=t_0$ , capacitor starts charging through the inductor. Thus a voltage gets built up across the inductor due to the change in current through it. If the capacitor was changed with the polarity as shown in the fig 2 the current starts flowing from the positive plate of the capacitor to the negativ4 plate of the capacitor. As shown the voltage across the capacitor reduces during the discharge time v reduces and I increases. At time t1 v will be 0 and I will be maximum as c is fully discharged, the capacitor charges like sinusoidal oscillations. Thus the circuit oscillates with the frequency

The Hartley oscillator consists of two inductors and a capacitor and Colpitts oscillator consists of two capacitors and an inductor.

The resonant frequency fo for Hartley oscillator is

fo =1/

$$2\pi$$

$\sqrt{L_{eq}C}$  -----where  $L_{eq}$  = L1 + L2.

The resonant frequency fo for Colpitts oscillator is

fo = 1/

$$2\pi\sqrt{LC_{eq}}$$

-----where  $C_{eq}$  = C1C2/(C1 + C2)

## **CIRCUIT DIAGRAM:**

## **HARTLEY OSCILLATOR:**

## **COLPITTS OSCILLATOR:**

## **DESIGN:**

Given VCC = 9V, IC = 2mA,

$$\beta$$

= 50

$$\textbf{R}_{\textbf{E}} \colon$$

W.K.T.  $V_{\text{RE}} = V_{\text{CC}} /$   $10$  = 9 /  $10$  = 0.9V ------for biasing

$$I_{\text{E}} \approx I_{\text{C}} = 2 \text{ mA}$$

From the fig. We see that,

$$I_E R_E = V_{RE}$$

$$R_E = 0.9 / (2 \times 10^{-3}) = 450 \Omega$$

Therefore  $R_E \approx 470\Omega$

**R<sub>c</sub>:**  $V_{CE} = V_{CC} / 2 = 4.5V$  ----- for Q point to be in active region.

Applying KVL to output loop

$$V_{CC} - I_C R_C - V_{CE} - V_{RE} = 0$$

$$9 - 2 \times 10^{-3} R_C - 4.5 - 0.9 = 0$$

Therefore  $R_c = 1.8k\Omega$

R<sub>1</sub> & R<sub>2</sub>: From biasing circuit

$$V_B = V_{BE} + V_{RE}$$

= 0.7 + 0.9

$V_B = 1.6V$

Assume 10  $I_B$  flows through  $R_1$  and 9  $I_B$  flows through  $R_2$ .

W.K.T.

$$I_C = \beta I_B$$

$$2 \times 10^{-3} = 50 I_{B}$$

Therefore  $I_B = 40 \mu A$

From the fig. we see that,

$$R_1 = V_{CC} - V_B / 10 I_B = 9 - 1.6 / (10 \times 40 \times 10^{-6}) = 18.5 k\Omega$$

Therefore  $R1 \approx 18k\Omega$

$$R_2 = V_B / 9I_B = 1.6 / (9 \times 40 \times 10^{-6}) = 4.44k\Omega$$

Therefore  $R_2 \approx 3.9 k\Omega$

$$C_{E}$$

,  $C_{C}$ ,  $C_{B}$ : Let  $C_{B} = C_{C} = 0.1 \mu F$

$$X_{CE} = RE/10$$

Therefore  $f = 10 / (2\pi C_E R_E)$

Let f = 100Hz and W.K.T  $R_{\text{E}}$  = 470 $\Omega$

Therefore  $C_E = 10 / 2\pi f.R_E = 34\mu F$

Therefore  $C_E \approx 47 \mu F$ .

### **HARTLEY OSCILLATOR:**

Attenuation  $\beta = Vf/Vo = IX_{L1}/IX_{L2} = X_{L1}/X_{L2} = 2\pi \text{ foL}1/2\pi\text{foL}2 = L1/L2$

For sustained oscillations  $Av\beta = 1$  -----  $Av = 1/\beta = L2/L1$

For oscillations to start  $Av\beta > 1$  -----Av > L2/L1

#### **COLPITTS OSCILLATOR:**

Attenuation  $\beta = Vf / Vo = IX_{C1}/IX_{C2} = X_{C1}/ X_{C2} = (1/ 2\pi foC1)/(1/2\pi foC2) = C1/C2$

For sustained oscillations  $Av\beta = 1$  ----- Av = C1/C2

For oscillations to start  $Av\beta > 1$ -----Av > C1/C2

## **DESIGN OF TANK CIRCUIT**

Assume = fo = 100 KHz

### HARTLEY OSCILLATOR

$$f_o = 1/(2\pi \sqrt{L_{eq}C})$$

-----where  $L_{eq} = L1 + L2$ .

Assume L1 =  $100 \mu H$ , L2 = 1 mH

- $\therefore$  L<sub>EO</sub> =

- $f_0 = 1/(2\pi \sqrt{2*10^{-3}})$

- $\therefore$  C = 0.0023 µf (Decade capacitance box)

## **COLPITTS OSCILLATOR**

$$f_{\rm O} = 1/(2\pi\sqrt{\rm LC_{eq}})$$

-----where  $C_{\rm eq} = ({\rm C1C2})/({\rm C1} + {\rm C2})$

Assume C1 = C2 = 1000 pF

- ∴ Cea =

- $f_0 = 1/2\pi\sqrt{L * .05*10 6}$

$\therefore$  L = 5 mH (Use decade inductance box)

#### **PROCEDURE:**

- 1. Rig up the circuit as shown in the circuit diagram.

- 2. Before connecting the feedback network, check the circuit for biasing conditions i.e. check  $V_{\text{CE}}$ , and  $V_{\text{RE}}$ .

- 3. After connecting the feedback network. Check the output.

- 4. Check for the sinusoidal waveform at output. Note down the frequency of the output waveform and check for any deviation from the designed value of the frequency.

- 5. To get a sinusoidal waveform adjust  $1K\Omega$  potentiometer.

- 6. DCB/DIB can be varied to vary the frequency of the output waveform.

## **TABULAR COLUMN**

| HARTLEY OSCILLATOR |            |  |  |  |  |  |

|--------------------|------------|--|--|--|--|--|

| SL NO              | SL NO C fo |  |  |  |  |  |

|                    |            |  |  |  |  |  |

| COLPITTS OSCILLATOR |            |  |  |  |  |  |

|---------------------|------------|--|--|--|--|--|

| SL NO               | SL NO L fo |  |  |  |  |  |

|                     |            |  |  |  |  |  |

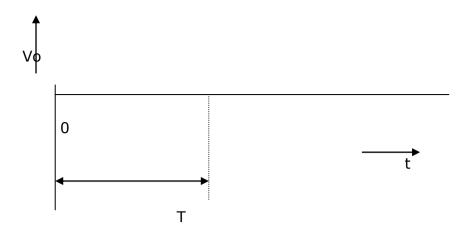

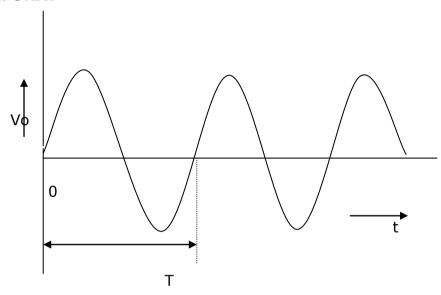

## **WAVEFORM:**

$\therefore$  frequency fo = 1/T

# **RESULT:**

Experiment No: 7 DATE:

# **CRYSTAL OSCILLATOR**

# AIM:

To design a crystal oscillator to oscillate at the specified crystal frequency.

# **COMPONENTS REQUIRED:**

| SI. No. | <b>Components Details</b>                                         | Specification    | Qty        |

|---------|-------------------------------------------------------------------|------------------|------------|

| 1.      | Transistor                                                        | SL100            | 1 No       |

| 2       | Canacitara                                                        | 0.1 μ <i>f</i>   | 2 No       |

| 2.      | Capacitors                                                        | 47μ <i>f</i>     | 1 No       |

| 3.      | Resistors $22K\Omega$ , $4.7K\Omega$ , $1.2K\Omega$ , $330\Omega$ |                  | Each 1 No  |

|         |                                                                   | 1 K Pot          | Lacii i No |

| 4.      | Crystal                                                           | 2 MHz or 1.8 MHz | 1 No       |

|         | DC Supply, CRO with Pro                                           |                  |            |

## **CIRCUIT DIAGRAM:**

## **DESIGN:**

Given VCC = 9V, IC = 2mA,

$$\beta$$

= 50

$$R_E$$

: W.K.T.  $V_{RE} = V_{CC} / 10 = 9 / 10 = 0.9V$  ------for biasing

$$I_E \approx I_C = 2 \text{ mA}$$

From the fig. We see that,

$$I_E R_E = V_{RE}$$

$$R_E = 0.9 / (2 \times 10^{-3}) = 450 \Omega$$

Therefore  $R_E \approx 470\Omega$

**R<sub>c</sub>:**  $V_{CE} = V_{CC}/2 = 4.5V$  ----- for Q point to be in active region.

Applying KVL to output loop

$$V_{CC} - I_C R_C - V_{CE} - V_{RE} = 0$$

$$9 - 2 \times 10^{-3} R_C - 4.5 - 0.9 = 0$$

Therefore  $R_c = 1.8k\Omega$

R<sub>1</sub> & R<sub>2</sub>: From biasing circuit

$$V_B = V_{BE} + V_{RE}$$

$$= 0.7 + 0.9$$

$$V_B = 1.6V$$

Assume 10  $I_B$  flows through  $R_1$  and 9  $I_B$  flows through  $R_2$ .

W.K.T.

$$I_C = \beta I_B$$

$$2 \times 10^{-3} = 50 I_{R}$$

Therefore  $I_B = 40 \mu A$

From the fig. we see that,

$$R_1 = V_{CC} - V_B / 10 I_B = 9 - 1.6 / (10 \times 40 \times 10^{-6}) = 18.5 k\Omega$$

Therefore  $R1 \approx 18k\Omega$

$R_2 = V_B / 9I_B = 1.6 / (9 \times 40 \times 10^{-6}) = 4.44k\Omega$

Therefore  $R_2 \approx 3.9 k\Omega$

$C_{E}$ ,  $C_{C}$ ,  $C_{B}$ : Let  $C_{B} = C_{C} = 0.1 \mu F$

$$X_{CE} = RE/10$$

Therefore  $f = 10 / (2\pi C_E R_E)$

Let f = 100Hz and W.K.T  $R_E$  = 470 $\Omega$

Therefore  $C_E = 10 / 2\pi f.R_E = 34\mu F$

Therefore  $C_E \approx 47 \mu F$ .

Dept of ECE- GCEM

## **PROCEDURE:**

- 1. Rig up the circuit as shown in the circuit diagram.

- 2. Before connecting the feedback network, check the circuit for biasing conditions i.e. check  $V_{CE}$ , and  $V_{RE}$ .

- 3. After connecting the feedback network. Check the output.

- 4. Check for the sinusoidal waveform at output. Note down the frequency of the output waveform and check for any deviation from the designed value of the frequency.

- 5. To get a sinusoidal waveform adjust  $1K\Omega$  potentiometer.

### **WAVEFORM:**

$\therefore$  frequency fo = 1/T

## **RESULT:**

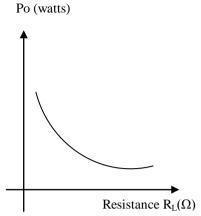

# **Experiment No:8**

# DATE:

# COMPLEMENTRY SYMMETRY CLASS-B PUSH PULL POWER AMPLIFIER

### Aim:

Set-up and study the working of complementary symmetry class B push pull power amplifier and calculate the efficiency.

# **COMPONENTS REQUIRED:**

| SI. No. | Components<br>Details               | Specification                 | Qty    |

|---------|-------------------------------------|-------------------------------|--------|

| 1       | Transistor                          | SL100                         | 1 No.  |

| 1.      | Hansistoi                           | SK100                         | 1 No.  |

| 2.      | Diode                               | BY127                         | 2 Nos. |

| 2       | Canacitara                          | 47 μ <i>f</i>                 | 2 Nos. |

| 3.      | Capacitors                          | 470 μ <i>f</i>                | 1 No.  |

| 4       | Desistans                           | 220Ω                          | 2 No   |

| 4.      | Resistors                           | DRB                           | 1 No   |

|         | DC Supply, CRO<br>AC millivoltmeter | with Probe, Signal generator, |        |

**Theory:** In class B operation, to obtain output for the full cycle of signal, it is necessary to use two transistors and have each conduct on opposite half cycle, the combined operation providing a full cycle of output signal. Since one part of the circuit pushes the signal high during one half cycle and the other part pulls the signal low during the other half cycle, the circuit is referred to as a push pull circuit.

## Circuit diagram:

### **DESIGN:**

Given Vcc =2.5V;  $R_L$ = 10  $\Omega$ ;  $I_{DC}$  = 3mA

# To Find R<sub>1</sub> & R<sub>2</sub>:

Applying KVL at the input circuit; We get; Vcc = 2VR1 + 1.4 Therefore;  $VR_1 = 0.55V$ ;  $VR_1 = I_{DC}R_1 = 0.55V$ ;  $R1 = 183\Omega$ . Choose;  $R_1 = R_2 = 220\Omega$ .

## To Find Ci:

Input coupling capacitor is given by, Xci >Zieff/10 >1.1K/10 Xci >  $1/2\pi$ fCi ;Ci > $28\mu$ F; Choose **Ci = 47\muF**

## To Find C<sub>o</sub>:

Output coupling capacitor is given by, Xco = 10 Xco > 1/2 $\pi$ fCo Co > 318 $\mu$ F; Choose; Co = 470 $\mu$ F Po<sub>ac</sub>=Vo²/8R $_{L}$  Pi<sub>dc</sub>=V $_{cc}I_{dc}$  Calculate circuit efficiency,  $\eta$  = Po (ac)/Pi(dc) = ( $\pi$ /4)Vo/Vcc = ?

#### **Procedure:**

- 1. Connect the circuit as per the circuit diagram.

- 2. Set  $V_I = 3V$ , using the signal generator.

- 3. Keeping the input voltage constant, vary the load resistor and note down the readings of the ammeter and peak to peak output voltage.

- 4. Calculate  $P_{DC}$ ,  $P_{AC}$  and % efficiency  $\eta$ .

- 5. Draw the plot of resistance versus output power.

### **Tabulation**

Vi = -----

| $R_L(\Omega)$ | V <sub>0</sub> (v) | I <sub>DC</sub> (mA) | P <sub>AC</sub> | $P_{DC}$ | % η |

|---------------|--------------------|----------------------|-----------------|----------|-----|

|               |                    |                      |                 |          |     |

|               |                    |                      |                 |          |     |

|               |                    |                      |                 |          |     |

|               |                    |                      |                 |          |     |

|               |                    |                      |                 |          |     |

|               |                    |                      |                 |          |     |

|               |                    |                      |                 |          |     |

#### **RESULT:**

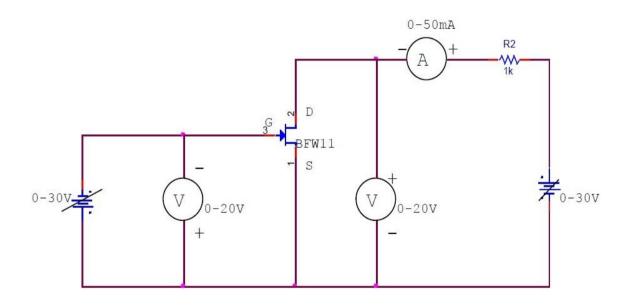

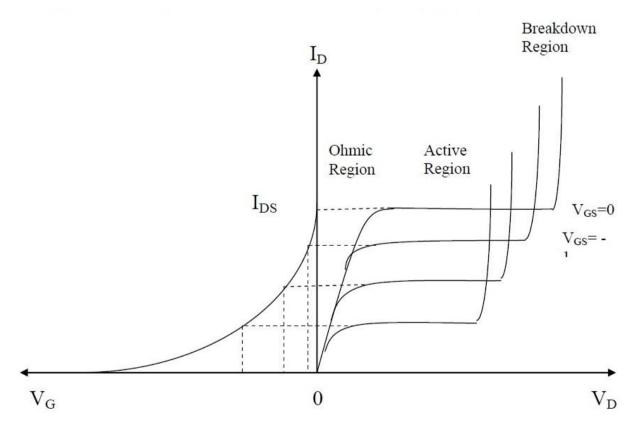

# **Experiment No:9**

# DATE:

# **JFET CHARACTERISTICS**

**AIM**: Plot the transfer and drain characteristics of a JFET and calculate its drain resistance, mutual conductance and amplification factor.

## **EQUIPMENT REQUIRED:**

- 1 Regulated Power Supply 0-30V

- 2 Voltmeter 0-20V

- 3 Ammeter 0-50mA

- 4 Bread Board

- 5 JFET.

### CIRCUIT DIAGRAM:

## **SPECIFICATIONS:**

For **JFET BFW11**: -

Gate Source Voltage VGS = - 30V Forward Gain Current IGF = 10 mA

Maximum Power Dissipation PD = 300 mW.

## **THEORY:**

A FET is a three terminal device, having the characteristics of high input impedance and less noise, the gate to source junction of the FET always reverse biased. In response to small applied voltage from drain to source, the n-type bar acts as sample resistor, and the drain current increases linearly with  $\mathbf{v}$ ds.with increase in Id the ohmic voltage drop between the and the channel region reverse biases the junction and the conducting position of the channel begins to remain

constant. The Vds at this instant is called "pinch of voltage". If the gate to source voltage (Vgs)is applied in the direction to provide additional reverse bias, the pinch off voltage is decreased.

In amplifier applications, the FET is always used in the region beyond the pinch off.

$Fds = Idss (1-Vgs/Vp)^2.$

## **PROCEDURE:**

#### **DRAIN CHARACTERISTICS**

- 1. Make the connections as per circuit diagram.

- 2. Keep VGS = 0V by varying VGG.

- 3. Varying VDD gradually, note down both drain current ID and drain to source voltage (VDS).

- 4. Step Size is not fixed because of non linear curve and vary the X-axis variable (i.e. if

- 5. Output variation is more, decrease input step size and vice versa).

- 6. Repeat above procedure (step 3) for VGS = -1V.

## **TRANSFER CHARACTERISTICS:**

- 1. Keep VDS = 2V by varying VDD.

- 2. Varying VGG gradually from 0 5V, note down both drain current (ID) and gate to source

- 3. Voltage (VGS).

- 4. Step Size is not fixed because of non linear curve and vary the X-axis variable (i.e. if

- 5. Output variation is more, decrease input step size and vice versa).

- 6. Repeat above procedure (step 2) for VDS = 4V.

## **OBSERVATIONS:**

## **DRAIN CHARACTERISTICS:**

| VGS(   | V)=0    | VGS(V)= -1 |        |  |  |

|--------|---------|------------|--------|--|--|

| VDS(V) | ID (mA) | VDS(V)     | ID(mA) |  |  |

|        |         |            |        |  |  |

|        |         |            |        |  |  |

|        |         |            |        |  |  |

|        |         |            |        |  |  |

|        |         |            |        |  |  |

|        |         |            |        |  |  |

|        |         |            |        |  |  |

|        |         |            |        |  |  |

|        |         |            |        |  |  |

|        |         |            |        |  |  |

# **TRANSFER CHARACTERISTICS:**

| VDS(   | V)= 1   | VDS(V)= 3 |        |  |  |

|--------|---------|-----------|--------|--|--|

| VGS(V) | ID (mA) | VGS(V)    | ID(mA) |  |  |

|        |         |           |        |  |  |

|        |         |           |        |  |  |

|        |         |           |        |  |  |

|        |         |           |        |  |  |

|        |         |           |        |  |  |

|        |         |           |        |  |  |

|        |         |           |        |  |  |

|        |         |           |        |  |  |

|        |         |           |        |  |  |

|        |         |           |        |  |  |

# **MODEL GRAPH:**

# **Transfer Characteristics**

# **Drain Characteristics**

## **CALCULATIONS:**

- 1. **Drain resistance rd** =  $\Delta VDS/\Delta ID$ =

- 2. Trans conductance gm =  $\Delta ID/\Delta VGS$ =

- 3. Amplification factor  $\mu$ = rd ×gm=

## **RESULT:**

- 1. Drain Resistance (rd) =

- 2. Trans conductance (gm) =

- 3. Amplification factor  $(\mu) =$

# Experiment No: 10 DATE:

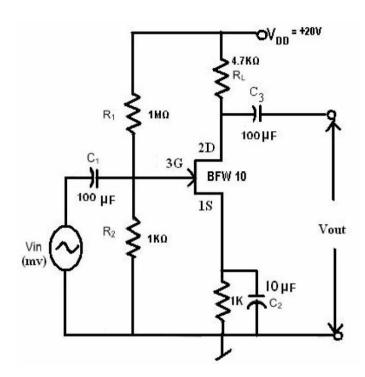

# JFET COMMON SOURCE CHARACTERISTICS

## AIM:

Design, setup and plot the frequency response of Common Source JFET/MOSFET amplifier and obtain the bandwidth.

## **EQUIPMENT REQUIRED:**

- 1 Regulated Power Supply 0-30V

- 2 Voltmeter 0-20V

- 3 Ammeter 0-50mA

- 4 Bread Board

5 JFET.

## **THEORY:**

The Common Source Amplifier is one of the three basic FET transistor amplifier configurations. In comparison to the BJT common-emitter amplifier, the FET amplifier has much higher input impedance, but a lower voltage gain. The Junction Field Effect Transistor (JFET) offers very high input impedance along with very low noise figures. It is very suitable for extremely low-level audio applications as in audio preamplifiers. The JFET is more expensive than conventional bipolar transistors but offers superior overall performance. Unlike bipolar transistors, current can flow through the drain and source in any direction equally. Often the drain and source can be reversed in a circuit with almost no effect on circuit operation.

The bias levels in amplifiers based on BJTs are often stabilized using the emitter degeneration technique; that is, a resistor is placed between the transistor's emitter and ground. The resistor creates negative feedback, which forces the quiescent collector current to remain at its design value regardless of changes in the transistor's parameters (such as  $\beta F$ ). A similar technique can be used to stabilize the biasing of FET amplifiers.

A common-source JFET amplifier in which a resistor RS has been added between the source and ground. In this circuit the gate has been connected to ground through the resistor RG; thus, the gate is held at ground potential (0 V). If the drain current ID begins to rise above its intended quiescent value, the voltage drop across RS will increase. Since the gate-source voltage VGS is the difference between the gate potential (fixed at 0 V) and the voltage across RS, a rise in the voltage across RS will cause VGS to drop, lowering ID back to its original value. The opposite chain of events occurs if ID begins to drop below its design value. It is a common practice in the design of circuits based on JFETs to tie the gate to ground potential via a large-valued resistor (typically around  $1M\Omega$ )

## **PROCEDURE:**

- 1. Make the connections as per circuit diagram.

- 2. Keep VGS = 0V by varying VGG.

- 3. Varying VDD gradually, note down both drain current ID and drain to source voltage (VDS).

- 4. Step Size is not fixed because of non linear curve and vary the X-axis variable (i.e. if

- 5. Output variation is more, decrease input step size and vice versa).

- 6. Repeat above procedure (step 3) for VGS = -1V.

# **CIRCUIT DIAGRAM:**

## **TABULAR COLUMN:**

|       | Input                     | Input             | Output                    | Gain (db) |

|-------|---------------------------|-------------------|---------------------------|-----------|

| SI No | Voltage (V <sub>i</sub> ) | Frequency         | Voltage (V <sub>0</sub> ) |           |

|       |                           | (f <sub>i</sub> ) |                           |           |

|       |                           |                   |                           |           |

|       |                           |                   |                           |           |

|       |                           |                   |                           |           |

|       |                           |                   |                           |           |

|       |                           |                   |                           |           |

|       |                           |                   |                           |           |

|       |                           |                   |                           |           |

# **GAIN VS FREQUENCY CURVE:**

# **RESULT:**

$F_H =$

$F_L =$

Gain (db) =

# **VIVA – QUESTIONS**

- 1. What are Semiconductors? Give examples?

- 2. What are the types of Semiconductor?

- 3. What is Intrinsic Semiconductor?

- 4. What is Extrinsic Semiconductor?

- 5. What are the types of Extrinsic Semiconductor?

- 6. What is P-type Semiconductor?

- 7. What are break down diodes or zener diodes

- 8. What is break down? What are its types?

- 9. What is zener breakdown4. What is avalanche break down?

- 10. What are the PIVs of three different filters

- 11. What are the advantages of bridge rectifier over center-taped full wave rectifier?

- 12. Define transformer utilization factor? What is the TUF for HWR and full wave center taped and bridge rectifier?

- 13. Why the CE configuration is commonly used for the amplifier circuits?

- 14. Why the Ib vs Vbe plots move outwards for higher values of Vce in Ce input characteristics?

- 15. What are the different types of clipping circuits?

- 16. Explain the different types of clipping circuits.

# **APPENDIX**

## Pin Identification of Transistors

1. Bipolar Junction Transistor (BJT) Transistors

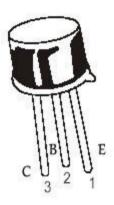

Transistors may be NPN or PNP which are available in Plastic casing or Metal Can package. In plastic casing,

one side of the transistor is Flat which is the front side and the pins are arranged serially. To identify the pins, keep the front flat side facing you and count the pins as one, two etc. In most NPN transistors it will be 1 (Collector), 2 (Base) and 3 (Emitter). Thus CBE. But in PNP transistors, the condition will be just reversed. That is EBC.

In Metal can types, the pins are arranged circularly. Just see a Tab in the rim. In NPN type, the pin close to the Tab is Emitter, the opposite one ,the Collector and the middle one, base. In PNP type the pins are reversed. Pin close to the Tab is Collector.

But this is not a standard pin configuration. The pin arrangement may vary in some transistors. So to get an idea, the following table will help you

| Transistor         | Туре | Pins 1 2 3 | Transistor       | Туре | Pins 1 2 3 |

|--------------------|------|------------|------------------|------|------------|

| BC546,547,548,549  | NPN  | CBE        | 2N 2222A,2N 3904 | PNP  | EBC        |

| 550, BC 337,AC 187 |      |            |                  |      |            |

| TIP 120,121,122    | NPN  | BCE        | TIP 125,126,127  | PNP  | EBC        |

| BD139              | NPN  | ECB        | BD140            | PNP  | ECB        |

| BF494,495          | NPN  | CEB        | MPSA 92,42,44    | PNP  | EBC        |

| C2570              | NPN  | BEC        | BC636            | PNP  | BCE        |

| C1730              | NPN  | ECB        | SK/CK/BEL100P    | PNP  | EBC        |

| BD677              | NPN  | BCE        | AC188            | PNP  | EBC        |

| D882 / 2SD882      | NPN  | ECB        | BC557            | PNP  | EBC        |

| D313/MJE 13005     | NPN  | BCE        | BC558            | PNP  | EBC        |

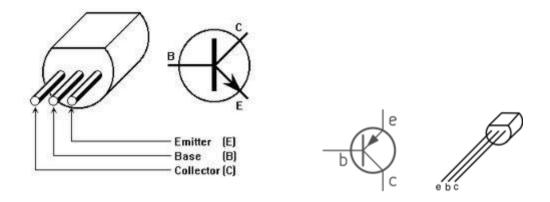

# 2. Field Effect Transistor (FET)

To identify a Field Effect Transistor, one should keep the curved portion facing him/her and start counting in anti clockwise direction. The 1<sup>st</sup> one is the source, then the gate and then the drain.

### 3. MOSFET - Metal Oxide Semiconductor Field Effect Transistor

Usually in some cases the pins of MOSFET are accordingly labeled as G, S and D denoting Gate, Source and Drain. In some cases, it is recommended to consult the datasheet of the MOSFET. Normally making the flat side faced towards you, the pins are labeled as S, G, D starting from left to right.