# FR FAMILY 32-BIT MICROCONTROLLER MB91460

# A/D CONVERTER

APPLICATION NOTE

# **Revision History**

| Date       | Issue                  |

|------------|------------------------|

| 2008-04-23 | V1.0, First draft, HPi |

This document contains 27 pages.

# Warranty and Disclaimer

To the maximum extent permitted by applicable law, Fujitsu Microelectronics Europe GmbH restricts its warranties and its liability for **all products delivered free of charge** (eg. software include or header files, application examples, target boards, evaluation boards, engineering samples of IC's etc.), its performance and any consequential damages, on the use of the Product in accordance with (i) the terms of the License Agreement and the Sale and Purchase Agreement under which agreements the Product has been delivered, (ii) the technical descriptions and (iii) all accompanying written materials. In addition, to the maximum extent permitted by applicable law, Fujitsu Microelectronics Europe GmbH disclaims all warranties and liabilities for the performance of the Product and any consequential damages in cases of unauthorised decompiling and/or reverse engineering and/or disassembling. **Note, all these products are intended and must only be used in an evaluation laboratory environment**.

- 1. Fujitsu Microelectronics Europe GmbH warrants that the Product will perform substantially in accordance with the accompanying written materials for a period of 90 days form the date of receipt by the customer. Concerning the hardware components of the Product, Fujitsu Microelectronics Europe GmbH warrants that the Product will be free from defects in material and workmanship under use and service as specified in the accompanying written materials for a duration of 1 year from the date of receipt by the customer.

- 2. Should a Product turn out to be defect, Fujitsu Microelectronics Europe GmbH's entire liability and the customer's exclusive remedy shall be, at Fujitsu Microelectronics Europe GmbH's sole discretion, either return of the purchase price and the license fee, or replacement of the Product or parts thereof, if the Product is returned to Fujitsu Microelectronics Europe GmbH in original packing and without further defects resulting from the customer's use or the transport. However, this warranty is excluded if the defect has resulted from an accident not attributable to Fujitsu Microelectronics Europe GmbH, or abuse or misapplication attributable to the customer or any other third party not relating to Fujitsu Microelectronics Europe GmbH.

- 3. To the maximum extent permitted by applicable law Fujitsu Microelectronics Europe GmbH disclaims all other warranties, whether expressed or implied, in particular, but not limited to, warranties of merchantability and fitness for a particular purpose for which the Product is not designated.

- 4. To the maximum extent permitted by applicable law, Fujitsu Microelectronics Europe GmbH's and its suppliers' liability is restricted to intention and gross negligence.

#### NO LIABILITY FOR CONSEQUENTIAL DAMAGES

To the maximum extent permitted by applicable law, in no event shall Fujitsu Microelectronics Europe GmbH and its suppliers be liable for any damages whatsoever (including but without limitation, consequential and/or indirect damages for personal injury, assets of substantial value, loss of profits, interruption of business operation, loss of information, or any other monetary or pecuniary loss) arising from the use of the Product.

Should one of the above stipulations be or become invalid and/or unenforceable, the remaining stipulations shall stay in full effect

# Contents

| R | REVISION HISTORY2 |                                                                           |     |  |  |  |  |  |  |

|---|-------------------|---------------------------------------------------------------------------|-----|--|--|--|--|--|--|

| w | ARRA              | ANTY AND DISCLAIMER                                                       | 3   |  |  |  |  |  |  |

| С | CONTENTS          |                                                                           |     |  |  |  |  |  |  |

| 1 | INTRODUCTION      |                                                                           |     |  |  |  |  |  |  |

|   | 1.1               | Key Features                                                              | . 6 |  |  |  |  |  |  |

| 2 | THE               | ANALOGUE/DIGITAL CONVERTER                                                | 7   |  |  |  |  |  |  |

|   | 2.1               | Block Diagram                                                             | 7   |  |  |  |  |  |  |

|   | 2.2               | Registers                                                                 | . 8 |  |  |  |  |  |  |

|   |                   | 2.2.1 Control Status Register (ADCS1)                                     | . 8 |  |  |  |  |  |  |

|   |                   | 2.2.2 Control Status Register (ADCS0)                                     | . 8 |  |  |  |  |  |  |

|   |                   | 2.2.3 Date Register (ADCR1, ADCR0)                                        | . 9 |  |  |  |  |  |  |

|   |                   | 2.2.4 Sampling timer and setting register (ADCT1, ADCT0)                  | . 9 |  |  |  |  |  |  |

|   |                   | 2.2.4.1 Sampling/Conversion Time                                          | . 9 |  |  |  |  |  |  |

|   |                   | 2.2.5 A/D Channel Setting Register (ADSCH, ADECH)                         | 10  |  |  |  |  |  |  |

|   |                   | 2.2.5.1 Start/Stop Channels                                               | 10  |  |  |  |  |  |  |

|   |                   | 2.2.6 Analog Input Enable Register (ADER0 – ADERn)                        | 11  |  |  |  |  |  |  |

| 3 | POW               | VER SUPPLY OF A/D CONVERTER                                               | 12  |  |  |  |  |  |  |

|   | 3.1               | Power consumption                                                         | 12  |  |  |  |  |  |  |

|   | 3.2               | Noise consideration                                                       | 12  |  |  |  |  |  |  |

| 4 | ANA               | LOGUE INPUT AND RELATED EXTERNAL CIRCUITS                                 | 14  |  |  |  |  |  |  |

|   | 4.1               | External circuits for analogue input                                      | 14  |  |  |  |  |  |  |

|   | 4.2               | Input Leakage current consideration                                       | 15  |  |  |  |  |  |  |

| 5 | SAM               | IPLING TIME CONSIDERATION                                                 | 17  |  |  |  |  |  |  |

| 6 | LAT               | CH-UP RELATED TO AV <sub>cc</sub> /V <sub>cc</sub> AND LARGE INPUT SIGNAL | 19  |  |  |  |  |  |  |

|   | 6.1               | $AV_{CC} > V_{CC}$                                                        | 19  |  |  |  |  |  |  |

|   | 6.2               | AV <sub>CC</sub> < V <sub>CC</sub>                                        | 19  |  |  |  |  |  |  |

|   | 6.3               | $U_{AIN} > AV_{CC} \text{ or } V_{CC}$                                    | 20  |  |  |  |  |  |  |

|   | 6.4               | Conclusion                                                                | 20  |  |  |  |  |  |  |

| 7 | INPU              | JT IMPEDANCE                                                              | 21  |  |  |  |  |  |  |

|   | 7.1               | Recharging and discharging the Sampling capacitor                         | 21  |  |  |  |  |  |  |

| 8 | ADC               | EXAMPLE                                                                   | 23  |  |  |  |  |  |  |

|   | 8.1               | ADC with interrupts                                                       | 23  |  |  |  |  |  |  |

|   |                   |                                                                           |     |  |  |  |  |  |  |

| 9 A | ADDITIONAL INFORMATION | 25 |

|-----|------------------------|----|

| LIS | T OF FIGURES           | 26 |

| LIS | T OF TABLES            | 27 |

# 1 Introduction

This application note describes the functionality of the Analog/Digital Converter (ADC) and gives some examples.

## 1.1 Key Features

- Minimum conversion time per Channel: 3 µs

- RC type successive approximation conversion with sample & hold circuit

- 8-bit or 10-bit conversion resolution

- Sequential channel conversion, once (Single Mode), continuous (Continuous Mode) and converts one channel, stops and waits for the next activation (Stop Mode)

- Interrupt generation after conversion selectable

- Interrupt can trigger DMA to transfer conversion result to memory

- Triggered by software, external Pin (ATG) or Timer

# 2 The Analogue/Digital Converter

THE BASIC FUNCTIONALITY OF THE ANALOGUE/DIGITAL CONVERTER

## 2.1 Block Diagram

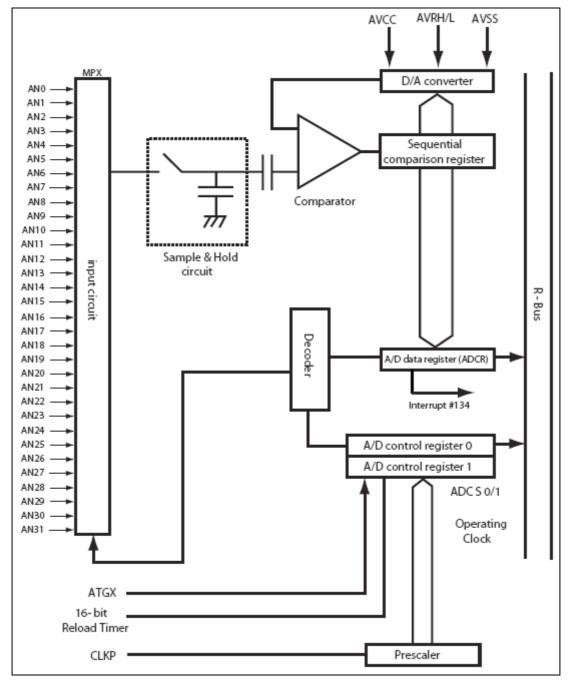

Figure 2-1 shows the internal block diagram of the ADC.

Figure 2-1: ADC Block Diagram

# 2.2 Registers

# 2.2.1 Control Status Register (ADCS1)

This register controls the A/D converter and indicates its status.

| Bit<br>No. | Name   | Explanation               | Initial<br>Value | Value | Operation                                               |

|------------|--------|---------------------------|------------------|-------|---------------------------------------------------------|

| 15         | BUSY*  | Busy Flag                 | 0                | 0     | Read: No A/D Conversion<br>Write: Force Conversion Stop |

| 15         | 0051   | and Stop*                 | 0                | 1     | Read: A/D Conversion ongoing<br>Write: No effect        |

| 14         | тып    | Interrupt                 | 0                | 0     | Read: No A/D Data<br>Write: Clear Flag                  |

| 14         | INT    | Flag                      | 0                | 1     | Read: A/D Data and Interrupt<br>Write: No effect        |

| 13         | INTE   | Interrupt                 | 0                | 0     | Interrupt disabled                                      |

| 10         | 11111  | enable                    | 0                | 1     | Interrupt, if A/D Data                                  |

| 12         | PAUS   | A/D<br>Converter<br>Pause | 0 -              | 0     | Read: No A/D Conversion Pause<br>Write: Clear Bit       |

| 12         |        |                           |                  | 1     | Read: Pause occurred<br>Write: No effect                |

|            |        |                           |                  | 0,0   | ADC Activation by Software                              |

| 11, 10     | STS1,0 | Start Source              | 0,0              | 0, 1  | ADC Activation by Software and ADTG Pin                 |

| 11, 10     | 5151,0 | Select                    | 0,0              | 1, 0  | ADC Activation by Software and Timer                    |

|            |        |                           |                  | 1, 1  | ADC Activation by Software, ADTG Pin, and Timer         |

| 9          | STRT   | Start                     | 0                | 0     | Always read; Write: no effect                           |

| 3          | DINI   | Conversion                | 0                | 1     | Start and Restart A/D Conversion                        |

| 8          | -      | Undefined                 | Х                | 0     | Reserved Bit , always write "0" to it                   |

Table 2-1: ADCS1

# 2.2.2 Control Status Register (ADCS0)

This register controls the A/D converter and indicates its status.

|     |        |             |       | 0, 0  | Single Mode 1; Reactivation during<br>Conversion allowed |

|-----|--------|-------------|-------|-------|----------------------------------------------------------|

|     |        |             |       | 0 1   | Single Mode 2; Reactivation during                       |

| 7,6 | MD1, 0 | Operation   | 0, 0  | 0, 1  | Conversion not allowed                                   |

| 7,0 | MD1, U | Mode Select | 0,0   | 1, 0  | Continuous Mode; Reactivation during                     |

|     |        |             |       | _, .  | Conversion not allowed                                   |

|     |        |             |       | 1, 1  | Stop Mode; Reactivation during                           |

|     |        |             |       | ⊥,⊥   | Conversion not allowed                                   |

| 5   | S10    | 10-Bit Mode | 0     | 0     | 10-Bit Conversion Mode                                   |

| 5   | 510    |             |       | 1     | 8-Bit Conversion Mode                                    |

|     |        |             |       |       | Current converted channel is shown                       |

| 4   |        | A/D         |       | Read  | during A/D converting (BUSY="1"). If                     |

|     | ACH4-  | converter   | 00000 | 1.044 | conversion is halt by forcibly stopping,                 |

| 0   | ACH0   | mode set    | ſ     |       | they show the stopped channel.                           |

|     |        |             |       | Write | No effect to these bits.                                 |

Table 2-2: ADCS0

\* These bits return "1" during Read-Modify-Write instruction.

## 2.2.3 Date Register (ADCR1, ADCR0)

These register stores digital value generated as a result of conversion. This register contains the last converted value and is rewritten every time the conversion ends.

| Bit No.      | Name   | Explanation | Value | Operation                         |

|--------------|--------|-------------|-------|-----------------------------------|

| 15<br><br>10 | -      | -           | 0     | These bits always return "0"      |

| 9            | D9<br> | Data Bits   | _     | These bits contain A/D data after |

| 0            | DO     | Duta Dito   |       | successful conversion             |

Table 2-3: ADCR1 & 2

2.2.4 Sampling timer and setting register (ADCT1, ADCT0)

These registers sets the sampling and conversion time

| Bit No.      | Name           | Explanation                | Initial Value           | Operation                                                                                                                                                              |

|--------------|----------------|----------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15<br><br>10 | СТ5<br><br>СТО | Comparison<br>Time Setting | 0,0,0,1,0,0             | Setting "000001" means one division<br>(=CLKP).<br>It's not allowed to set these bits<br>"000000"<br>Note : It's not allowed to set the<br>comparison time over 500 us |

| 9<br><br>0   | ST9<br><br>ST0 | Sampling<br>time           | 0,0,0,0,1,<br>0,1,1,0,0 | Sampling time = ST value * CLKP<br>cycle<br>Note: It's not allowed to set the<br>sampling time below 1.2 us when<br>AVCC is below 4.5 V.                               |

Table 2-4: ADCT1 & 2

## 2.2.4.1 Sampling/Conversion Time

The sampling time must be equal to or greater than 0.4  $\mu$ s. The Comparison time must be at least 0.6  $\mu$ s. Therefore an overall A/D conversion time could be 1  $\mu$ s, but this depends on the used peripheral clock.

Assume a peripheral clock of 16 MHz (62.5 ns cycle time). The sample cycle number then has at least to be 8 (0.5  $\mu$ s) and the conversion cycle number can be 10 (0.625  $\mu$ s). Therefore the overall A/D conversion time is 1.125  $\mu$ s.

All these settings are valid for  $4.5 \text{ V} \leq AV_{cc} \leq 5.5 \text{ V}$ . Please see the hardware manual for external impedance considerations.

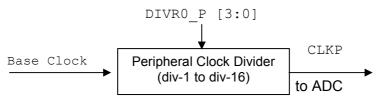

Please consider that the source clock frequency of the Reload Timer (CLKP) depends on the settings of the Clock Division setting register (DIVR0).

## 2.2.5 A/D Channel Setting Register (ADSCH, ADECH)

These registers specify the channels for the A/D converter to convert. Do not update these registers while the A/D converting is operating.

| Bit<br>No. | Name  | Explanation | Initial<br>Value | Value | Operation                             |

|------------|-------|-------------|------------------|-------|---------------------------------------|

| 15         |       |             |                  |       |                                       |

|            | -     | Undefined   | Х                | 0     | Reserved Bit , always write "0" to it |

| 13         |       |             |                  |       |                                       |

| 12         | ANS4  | Starting    |                  | 00000 | Start conversion from Channel 0       |

|            |       | Channel     | 0                |       |                                       |

| 8          | ANS0  | Setting     |                  | 11111 | Start conversion from Channel 31      |

| 7          |       |             |                  |       |                                       |

|            | -     | Undefined   | Х                | 0     | Reserved Bit , always write "0" to it |

| 5          |       |             |                  |       |                                       |

| 4          | ANE4  | Ending      |                  | 00000 | End conversion at Channel 0           |

|            |       | Channel     | 0                |       |                                       |

| 0          | ANE 0 | Setting     |                  | 11111 | End conversion at Channel 31          |

Table 2-5: ADSCH & ADECH

## 2.2.5.1 Start/Stop Channels

- Use start channel = end channel for conversion of only one channel.

- If start channel is greater then end channel, conversion starts form start channel to the highest available channel, then from channel 0 to the end channel.

## 2.2.6 Analog Input Enable Register (ADER0 – ADERn)

While a pin is used as analog input, corresponding bit in ADER register have to be set to 1. If a channel between the configured scanning limits is not configured as ADC input (the corresponding bit in this register is "0"), this channel is skipped during the scanning process.

The following table shows ADERH.

| Bit<br>No. | Name      | Explanation | Initial<br>Value | Value | Operation                |

|------------|-----------|-------------|------------------|-------|--------------------------|

| 31         | ADE31     | ADC Input   | 0                | 0     | Digital I/O Port enabled |

| 16         | <br>ADE16 | Selection   | 0                | 1     | Analog Input enabled     |

Table 2-6: ADERH

The following table shows ADERL.

| Bit<br>No. | Name     | Explanation | Initial<br>Value | Value | Operation                |

|------------|----------|-------------|------------------|-------|--------------------------|

| 15         | ADE15    | ADC Input   |                  | 0     | Digital I/O Port enabled |

| <br>0      | <br>ADE0 | Selection   | 0                | 1     | Analog Input enabled     |

Table 2-7: ADERL

# 3 Power supply of A/D converter

## ELECTRICAL POWER CONSIDERATIONS

#### 3.1 Power consumption

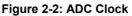

The power consumption ( $I_R$ ,  $I_A$ ) of the ADC increases in case a conversion is in progress (ADCS1\_BUSY = 1). While the ADC is halted (ADCS1\_BUSY = 0), only leakage current ( $I_{RH}$ ,  $I_{AH}$ ) flows. The following diagrams reflect this behaviour:

Figure 3-1: Power consumption and operating status of ADC

## Note:

Please refer to the datasheet in order to get the absolute values of  $I_R$ ,  $I_{RH}$ ,  $I_A$  and  $I_{AH}$ .

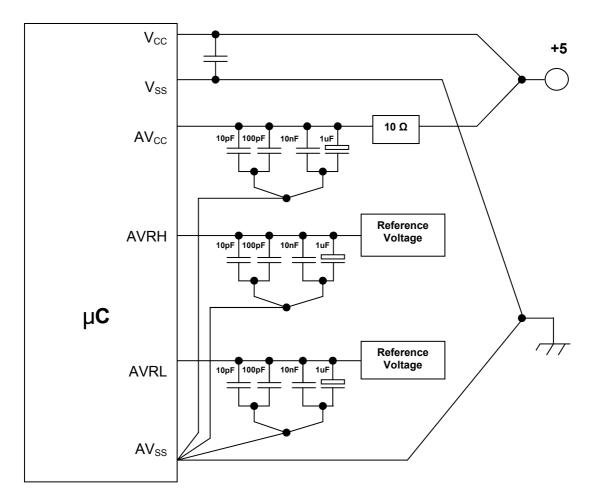

#### 3.2 Noise consideration

Fujitsu microcontroller has implemented an embedded 10-bit Successive Approximated Register (SAR) ADC. Due to the high resolution, the digital bit stream from the ADC output is sensitive to the environment noise. For example, 1LSB corresponds to only 4.9mV for  $U_{REF}$ =5V. Hence, the noise introduced from the external circuits must be considered and should be reduced to the minimum as possible.

The reference voltage  $U_{REF}$ , which is equal to AVRH-AVRL, is connected to the weighted capacitor array and the resistor array of the ADC. The noise coupled to AVR will not be rejected by ADC. This noise will be added to the  $U_{REF}$  directly, introducing an error with a ratio of  $U_{Noise}/U_{REF}$ . For example, to keep the error caused by this kind of noise below 0.1LSB, the noise level of  $U_{REF}$  must be kept within 0.49mV.

As a result, the pin AVRH and AVRL pins must be connected with low impedance. In practice often a simple low-pass RC-filter is used for noise reduction. In this case the reference voltage supply current (see datasheet) has to be taken into account when calculating the resistor of the filter, in order to minimize the voltage drop while converting. Normally two capacitors in parallel are recommended, one filtering low frequency noise, the other one filtering high frequency noise (( $10nF-1\mu F$ )||(10pF-100pF)). In most cases, this configuration suppresses the noise efficiently. If very high frequency noise appears in the environment, an additional noise filter such as a dedicated  $\pi$  mode RC filter might be useful.

The analogue power path AV<sub>CC</sub> supplies the internal voltage comparator and the analogue switches of the ADC, while the V<sub>CC</sub> path supplies all the digital parts in the microcontroller. Internal parasitic capacitors may couple noise from AV<sub>CC</sub> to the internal voltage comparator of the ADC. For this reason, also AV<sub>CC</sub> should not be connected directly to V<sub>CC</sub> but filter should be used, too. For more efficient noise filtering the same configuration as for AVRH is recommended.

# 4 Analogue input and related external circuits

# 4.1 External circuits for analogue input

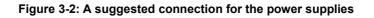

Figure 4-1: A typical external circuit for analogue input

To protect the analogue pins to suffer from an over-voltage, the so-called "clamping resistor" is usually added to the input pins. The minimum value of the resistor can be chosen as

$$R_{clamp} = U_{overvoltage} / I_{clamp}$$

Where, I<sub>clamp</sub> is the specified maximum clamp current in the data sheet.

For some applications, a large clamp resistor is sometimes unacceptable. As a compromise, an external clamping diode with low leakage current could be added between the input pin and  $AV_{CC}$  pin.

In some cases, the sensor has been biased with a voltage supply higher than the maximum allowed voltage for the microcontroller. For example, in the automotive applications, the sensors could be biased directly with the car battery, which exhibits a voltage of 12V/24V. A resistor divider consisting of  $R_1/R_2$  is commonly used to tail the sensor voltage signal "seen" on the pin down to the value which is equal or smaller than  $AV_{CC}/V_{CC}$  (see Figure 4-1).

The ratio between  $R_1$  and  $R_2$  should satisfy the following constrain:

$$\frac{R_1}{R_2} \ge \frac{U_{Signal}}{AV_{CC}} - 1$$

Other factor which influences the size dimension of  $R_1$ ,  $R_2$  and  $R_{clamp}$ , is related to current consumption budget and the input signal noise suppressing. The second factor will be discussed here with more detail. The signal from the sensors could be also noisy. The noise, which has a time constant smaller than the sampling time  $T_{sampling}$ , is transparent to the ADC, resulting distorted output. In this case, an additional dedicated bypass capacitor together with the clamping resistor or resistor divider, works as a low pass filter. A larger capacitor will lower the AC impedance and will be more effective at shunt away the noise signal. Generally, the time constant of this low pass filter ( $R_{clamp} + R_1 || R_2$ ) x  $C_{noise}$  should be chosen considerably larger than the sampling time (5 to 10 times larger with a rule of thumb).

However, at the same time this time constant should be also considerably smaller than the one of the sensor signal, depending on the applications. In this way, the analogue pin is able to follow the dynamic changes, which the ADC is being used to track. These, along with the

dimension of  $R_1/R_2$  or  $R_{clamp}$  must be considered when choosing the capacitor dimension to avoid rolling off any high frequency signal components of interest.

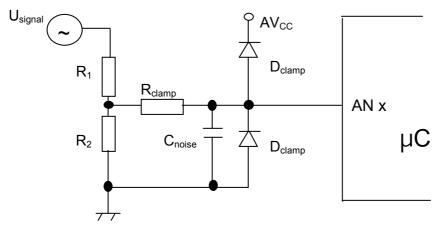

#### 4.2 Input Leakage current consideration

The analogue input pins show a small leakage current, whose maximum value is about  $3\mu A$  and ranged from  $3\mu A$  down to  $1\mu A$  depending on the temperature. The leakage current, which flows through the external resistor, introduces an undesired voltage drop. This error voltage is a function of the external resistor and the leakage current itself. The following example shows a dimension of the resistor with this factor taken into consideration. For the case of using a resistor divider to reduce the error due to leakage current, the size of R<sub>1</sub> || R<sub>2</sub> + R<sub>clamp</sub> should not be chosen too large and should be according to the following equation:

$$R_1 \parallel R_2 + R_{clamp} \le \frac{U_{LSB}}{I_{leakage}} \qquad \qquad \text{Note:} \\ U_{LSB} = U_{REF} / 1024$$

To keep the error smaller than one LSB for a leakage of  $3\mu A$ , the size of  $R_1 \parallel R_2 + R_{clamp}$  should be smaller than  $1.6k\Omega$ . As the leakage current drops down to  $1 \mu A$ , the value of R1  $\parallel$  R2 +  $R_{clamp}$  can be chosen as large as  $5k\Omega$ . This is considering  $U_{REF}$  of 5V.

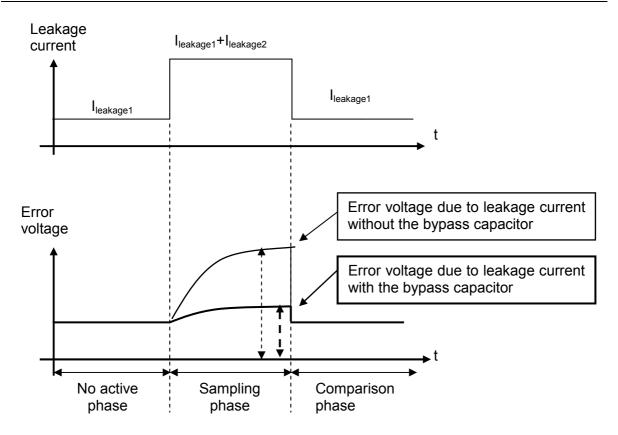

It is found in the test that the leakage current consists of two parts: one is due to the leakage current of the input ESD structure. Another leakage current appears only as the multiplexer is switched on during the sampling time, whose contribution is usually considerably larger than the one created from ESD structure. The second leakage current can be regarded as a noise during the sampling time by the bypass capacitor, which is commonly used to filter the noise from the sensor input. If this capacitor is large enough, it can absorb most of the second leakage current during the sampling time, eliminating its contribution to the error voltage.

Figure 4-2: Leakage current flowing to the analogue input pin

Figure 4-3: Reducing the leakage current with the bypass capacitor

To show the effect of the bypass capacitor on reducing the leakage current error, we take a sampling time of 5µs and a leakage current of 3µA as an example. If we want to keep the voltage drop due to the second leakage current small than 0.5 LSB, the minimum size of the bypass capacitor should be chosen as:

$$C = \frac{3\mu A \times 5\mu s}{4.9mV/2} \approx 6nF$$

# 5 Sampling time consideration

## SAMPLING TIME CONSIDERATION

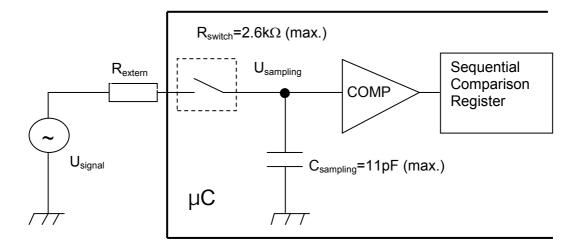

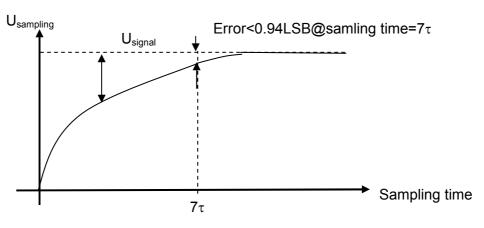

Fujitsu applies an embedded 10-bit successive approximation register ADC with an internal integrated sampling and hold stage. The signal will charge the sampling capacitor at first and then the voltage signal on the sampling capacitor will be evaluated by the 10-bit ADC successively. The time to charge the sampling capacitor to its final value equal to the signal level is a function of the sampling capacitor  $C_{\text{sampling}}$ , the external resistor and the internal switch on-resistor.

To reduce the error caused by the limited sampling time to an acceptable level, the sampling time should be chosen much larger than the time constant to charge the sampling capacitor. For example, if we choose a sampling time with a factor 7 of the RC constant, namely,  $7 \times (R_{extern} + R_{switch}) \times C_{sampling}$ . Then the error amounts to  $e^{-7} \times U_{REF}$ , corresponding  $0.94 \times U_{LSR}$  only.

For MB91467D Series, the on-resistor of the transmission gate amounts to  $2.6k\Omega$  and the sampling capacitor  $C_{\text{sampling}}$  equals to 11pF at AV<sub>CC</sub> = 5V. For an external resistor of  $2.25k\Omega$ , the sampling time should be chosen larger than  $7 \times (2.25k\Omega + 2.6k\Omega) \times 11pF = 0.37\mu s$  by using above thumb rule.

Figure 5-1: Block diagram for ADC in MB91F460D Series

Figure 5-2: Error related to sampling time

For the Fujitsu microcontroller the sampling time can be set by defining the register bit ST2 to ST0 of the ADC data register (ADCT). Please refer to the hardware manual.

# 6 Latch-up related to $AV_{CC}/V_{CC}$ and large input signal

## RECOMMENDATIONS TO PREVENT LATCH-UP

Latch-up conditions can permanently damage the device and must be avoided. It is up to the application to assign any precautions in order to avoid any latch-up condition.

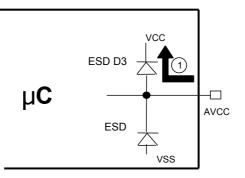

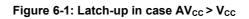

## 6.1 $AV_{CC} > V_{CC}$

Latch-up can happen if AV<sub>CC</sub> becomes larger than V<sub>CC</sub>. This might be related to the application cases that V<sub>CC</sub> is switched on later than AV<sub>CC</sub> or V<sub>CC</sub> is switched off earlier than AV<sub>CC</sub>. The ESD diode D3 becomes forward biased, introducing a possible latch-up.

## $6.2 \quad AV_{CC} < V_{CC}$

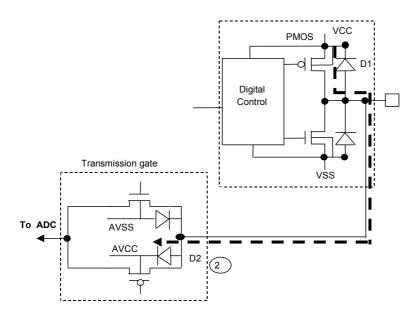

Figure 6-2: Latch-up in case AV<sub>cc</sub> < V<sub>cc</sub>

This case happens if the analogue pin is used as a digital output pin, the output level is "H", and at the same time,  $AV_{CC}$  is switched off. In this case, the PMOS in the output is on and

the parasitic diode D2 of the transmission gate within the analogue multiplex becomes forward biased. A quiescent current flows through PMOS and D2. In case that a latch-up does not happen, a reliable logic "1" should not be expected at the output, due to the load diode D2.

## 6.3 $U_{AIN} > AV_{CC} \text{ or } V_{CC}$

Figure 6-3: Problem in case  $U_{AIN} > AV_{CC}$  or  $V_{CC}$

If  $U_{AIN}$  becomes larger than  $V_{CC}$  or  $AV_{CC}$ , then the ESD diode D1 or D2 will be forward biased. A latch-up can happen. Even if a latch-up does not always happen in this case, the input signal, which exceeds  $V_{CC}$  or  $AV_{CC}$ , cannot be converted by the ADC properly.

## 6.4 Conclusion

It is strongly suggested that  $AV_{\text{CC}}$  and  $V_{\text{CC}}$  should be DC short circuit together to avoid any possible latch-up.

With the presence of  $AV_{CC}$  and  $V_{CC}$  voltage, an analogue input signal, which is smaller than  $AV_{CC}$  and  $V_{CC}$  can be always put on the analogue pins, independent on the MCU modes.

Latch-up conditions can permanently damage the device if the related specified currents are exceeded. So Latch-up conditions must be avoided under all circumstances. It is up to the application to assign any precautions in order to avoid any latch-up condition.

# 7 Input Impedance

## ADC BEHAVIOR ON HIGH INPUT IMPEDANCES

## 7.1 Recharging and discharging the Sampling capacitor

Because the ADC uses a sampling capacitor the input impedance must be set to a value below 15 k $\Omega$  to recharge or discharge this capacitor within the sampling time.

#### Example:

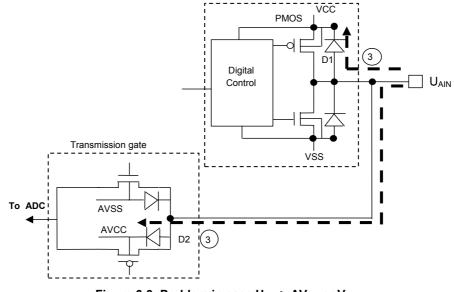

Assume an application uses two ADC inputs. At one pin there is a voltage of about Vcc and at the other pin Vss. The first conversion charges the internal capacitor to Vcc within the sample time (A). After this the conversion starts (B). At the second conversion the MUX switches to the other input and the capacitor is discharged to Vss (C). The second conversion starts (D). If the input impedance ( $Z_0$ ) is too high, a rest of charge will remain and a wrong conversion will result.

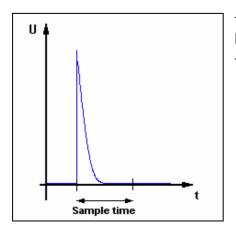

Figure 7-1: Current flow in the example

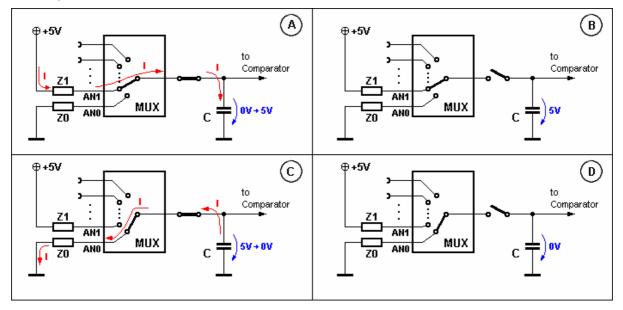

The left illustration shows the voltage glitch on AN0 if  $Z_0$  is low.

The glitch occurs, when the sampling switch is closed.

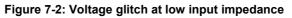

In this illustration the input impedance  $Z_0$  is too high. The sampling capacitor is not discharged within the sampling time and thus a wrong voltage is converted (red circle).

Figure 7-3: Voltage glitch at high input impedance

#### Note:

At high impedance input circuit, there will always be a glitch of about 0.5 Volts max even if the previous conversion was at 0 Volt. This results from the ADC internal architecture itself.

For the same reason discussed in this chapter an EMI capacitors for any analogue input pins should not exceed 1 nF.

# 8 ADC Example

EXAMPLES FOR THE ADC

## 8.1 ADC with interrupts

Main.c

```

/* THIS SAMPLE CODE IS PROVIDED AS IS AND IS SUBJECT TO ALTERATIONS. FUJITSU */

/* MICROELECTRONICS ACCEPTS NO RESPONSIBILITY OR LIABILITY FOR ANY ERRORS OR */

/* ELIGIBILITY FOR ANY PURPOSES.

*/

(C) Fujitsu Microelectronics Europe GmbH

1+

*/

/*_____

_ * /

void InitADC (void)

{

ADECH = 0 \times 01;

ADCS1 = 0xA2;

/* interrupt enabled, software trigger,

start conversion */

}

void main (void)

{

*/

___set_il(7);

/* allow all levels

*/

/* globally enable interrupts

*/

EI();

PFR16 = 0 \times 00;

DDR16 = 0xFF;

PDR16 = 0 \times 00;

/* init AD - converter

InitADC();

*/

/* waiting for interrupt (no operation) */

while(1)

__asm("\tnop");

}

interrupt void ISR ADC (void)

{

PDR16 = ADCR0; /* shows voltage on Port 0 ( LEDs )

*/

/* clear interrupt flag

ADCS1 = 0 \times A2;

*/

}

```

The above example demonstrates to configure ADC in the continuous mode with 8 bit conversion resolution with interrupts enabled. The maximum possible sampling and comparison time is used here. After every ADC interrupt the converted data is output to the LEDs connected to Port 16.

#### vectors.c

```

/* THIS SAMPLE CODE IS PROVIDED AS IS AND IS SUBJECT TO ALTERATIONS. FUJITSU */

/* MICROELECTRONICS ACCEPTS NO RESPONSIBILITY OR LIABILITY FOR ANY ERRORS OR */

/* ELIGIBILITY FOR ANY PURPOSES.

*/

*/

/*

(C) Fujitsu Microelectronics Europe GmbH

/*-----

_*/

void InitIrqLevels (void)

{

ICR59 = 30; /* Priority Level 30 for ADC */

. . .

}

/* ISR prototype */

__interrupt void ISR_ADC (void);

. . .

#pragma intvect ISR_ADC 134 /* ADC */

. . .

```

# 9 Additional Information

Information about FUJITSU Microcontrollers can be found on the following Internet page: <a href="http://mcu.emea.fujitsu.com/">http://mcu.emea.fujitsu.com/</a>

The software examples related to this application note is: 91460\_adc8-v10 91460\_adc\_r/t-v10 91460\_adc8\_dma-v14 91460\_ppg\_r/t\_adc\_dma-v10 91460\_adc8\_uart\_async-v13 91460\_adc10\_dma\_irq-v12 It can be found on the following Internet page: http://mcu.emea.fujitsu.com/mcu\_product/mcu\_all\_software.htm

# List of Figures

| Figure 2-1: ADC Block Diagram                                      | 7  |

|--------------------------------------------------------------------|----|

| Figure 2-2: ADC Clock                                              | 9  |

| Figure 3-1: Power consumption and operating status of ADC          | 12 |

| Figure 3-2: A suggested connection for the power supplies          | 13 |

| Figure 4-1: A typical external circuit for analogue input          | 14 |

| Figure 4-2: Leakage current flowing to the analogue input pin      | 15 |

| Figure 4-3: Reducing the leakage current with the bypass capacitor | 16 |

| Figure 5-1: Block diagram for ADC in MB91F460D Series              | 17 |

| Figure 5-2: Error related to sampling time                         | 18 |

| Figure 6-1: Latch-up in case AV <sub>CC</sub> > V <sub>CC</sub>    | 19 |

| Figure 6-2: Latch-up in case AV <sub>CC</sub> < V <sub>CC</sub>    | 19 |

| Figure 6-3: Problem in case $U_{AIN} > AV_{CC}$ or $V_{CC}$        | 20 |

| Figure 7-1: Current flow in the example                            | 21 |

| Figure 7-2: Voltage glitch at low input impedance                  | 21 |

| Figure 7-3: Voltage glitch at high input impedance                 | 22 |

# List of Tables

| Table 2-1: ADCS1         | 8  |

|--------------------------|----|

| Table 2-2: ADCS0         | 8  |

| Table 2-3: ADCR1 & 2     | 9  |

| Table 2-4: ADCT1 & 2     | 9  |

| Table 2-5: ADSCH & ADECH | 10 |

| Table 2-5: ADERH         | 11 |

| Table 2-6: ADERL         | 11 |