# ARM\* Instruction Set & Assembly Language

Web Sites:

http://www.heyrick.co.uk/assembler/

http://dec.bournemouth.ac.uk/staff/pknaggs/sysarch/ARMBook.pdf

http://www.arm.com/community/academy/university.html

Books (in addition to textbook):

Computers as Components by Wayne Wolf, Morgan Kaufman, 2000.

*The ARM RISC Chip – A Programmer's Guide* by A. van Someren & C. Atack, Addison-Wesley, 1994.

Jens Gregor, UTK CS Professor.

CS 160 ೮

\*Advanced RISC Machines

# Main Features [1]

- All instructions are 32 bits long

- Registers are 32 bits long

- Memory addresses are 32 bits long

- Memory is byte addressable

- Most instructions execute in a single cycle

- Every instruction can be conditionally executed

- Can be configured at power-up as either little or big endian

## ARM Instruction Set Overview & Registers

#### CS 160 灯

Ward 2

# Main Features [2]

#### A load/store architecture

- Data processing instructions act only on registers

- Three operand format

- Combined ALU and shifter for high speed bit manipulation

- Specific memory access instructions with powerful auto-indexing addressing modes

- 32 bit and 8 bit data types

- And also 16 bit data types on ARM Architecture v4

- Flexible multiple register load and store instructions

Ward 1

## **Processor Modes**

- The ARM has six execution modes

- User (unprivileged mode under which most tasks run)

- *FIQ* (entered when a high priority (fast) interrupt is raised)

- *IRQ* (entered when a low priority (normal) interrupt is raised)

- Supervisor (entered on reset and when a Software Interrupt instruction is executed)

- Abort (used to handle memory access violations)

- Undef (used to handle undefined instructions)

- ARM Architecture Version 4 adds a seventh mode

- System (privileged mode using the same registers as user mode)

```

CS 160 ೮

```

CS 160 💆

Ward 5

Ward 7

# **Register Organization**

#### General registers and Program Counter

| 10<br>11<br>12<br>13<br>14<br>15<br>15<br>16<br>17<br>18 | 10<br>11<br>12<br>13<br>14<br>15<br>15<br>16<br>17  | 10<br>11<br>12<br>13<br>14<br>15<br>15<br>16                                                                                            |

|----------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 12<br>13<br>14<br>15<br>16<br>17                         | 12<br>13<br>14<br>15<br>16                          | 12<br>13<br>14<br>15<br>15<br>16                                                                                                        |

| 13<br>14<br>15<br>16<br>17                               | 13<br>14<br>15<br>16                                | 13<br>14<br>15<br>16                                                                                                                    |

| r4<br>r5<br>r6<br>r7                                     | r4<br>r5<br>r6                                      | r4<br>r5<br>r6                                                                                                                          |

| 15<br>16<br>17                                           | <u> </u>                                            | <u> </u>                                                                                                                                |

| r6<br>17                                                 | ró                                                  | ró                                                                                                                                      |

| r7                                                       |                                                     |                                                                                                                                         |

|                                                          | rl                                                  |                                                                                                                                         |

| -8                                                       |                                                     | x7                                                                                                                                      |

| 10                                                       | 18                                                  | 18                                                                                                                                      |

| r9                                                       | 19                                                  | 19                                                                                                                                      |

| r10                                                      | r10                                                 | r10                                                                                                                                     |

| r11                                                      | r11                                                 | r11                                                                                                                                     |

| r12                                                      | r12                                                 | r12                                                                                                                                     |

| r13_abt                                                  | r13_im                                              | r13_unde                                                                                                                                |

| r14_abt                                                  | r14_irg                                             | r14_unde                                                                                                                                |

| r15 (pc)                                                 | r15 (pc)                                            | r15 (pc)                                                                                                                                |

|                                                          | r10<br>r11<br>r12<br>r13_abt<br>r14_abt<br>r15 (pc) | r10         r10           r11         r11           r12         r12           r13 sbt         r13 ing           r14 sbt         r14 ing |

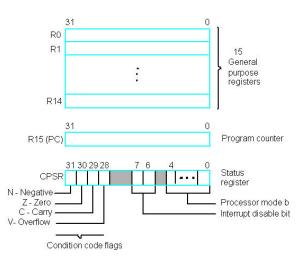

# Registers

- ARM has 37 registers in total, all of which are 32-bits long

- 1 dedicated program counter (PC)

- 1 dedicated current program status register (cpsr)

- 5 dedicated saved program status registers (spsr)

- 30 general purpose registers

- However, these are arranged into several banks, with the accessible bank being governed by the processor mode. Each mode can access

- a particular set of r0-r12 registers

- a particular r13 (the *stack pointer*) and r14 (*link register*)

- r15 (the program counter)

- cpsr (the *current program status register* or *status register*)

- and privileged modes can also access

- a particular spsr (saved program status register)

CS 160 ೮

Ward 6

## **User Mode Registers**

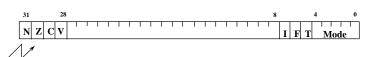

## Program Status Registers (CPSR, SPSRs)

Copies of the ALU status flags

#### Condition Code Flags

- N = Negative result from ALU flag

- Z = Zero result from ALU flag

- C = ALU operation Carried out

- V = ALU operation oVerflowed

#### Mode Bits

CS 160 🔰

M[4:0] define the processor mode

- Interrupt Disable bits

- I = 1, disables the IRQ

- F = 1, disables the FIQ

T Bit (Architecture v4T only)

- T = 0, processor in ARM state

- T = 1, Processor in thumb state

### **Accessing Registers**

- All instructions can access r0-r14 directly

- Most instructions also allow access of the PC

- Specific instructions allow access to cpsr

#### CS 160 ೮

CS 160 57

Ward 10

# Program Counter (r15)

- When the processor is executing in ARM state

- All instructions are 32 bits in length

- All instructions must be word aligned

- Addresses refers to byte (i.e., byte addressable)

- Therefore, the PC value is stored in bits [31:2] with bits [1:0] equal to zero (as instructions cannot be halfword or byte aligned)

- r14 used as the subroutine link register (Ir) and stores the return address when Branch with Link (BL) operations are performed through registers (place on stack in linked branch)

- Thus, to return from a linked branch using registers, contents of r14 must be placed in r15 (from stack).

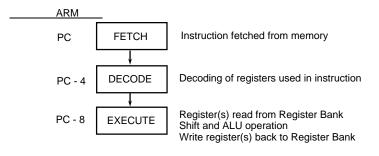

## **Instruction Pipeline**

• ARM uses a 3-stage pipeline in order to increase the speed of the flow of instructions to the processor

• The PC points to the instruction being fetched

Ward 9

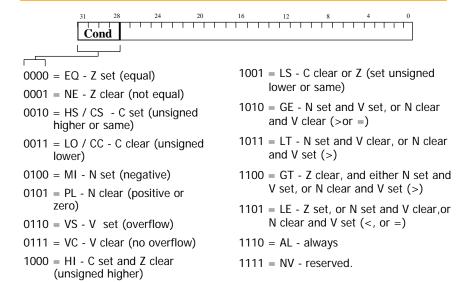

## **Conditional Execution**

- Most instruction sets only allow branches to be executed conditionally.

- However by reusing the condition evaluation hardware, ARM effectively increases number of instructions.

- All instructions contain a condition field which determines whether the CPU will execute them.

- Non-executed instructions soak up 1 cycle.

- Still have to complete cycle so as to allow fetching and decoding of following instructions.

- This removes the need for many branches, which stall the pipeline (3 cycles to refill).

- Allows very dense in-line code, without branches.

- The Time penalty of not executing several conditional instructions is frequently less than overhead of the branch or subroutine call that would otherwise be needed.

```

CS 160 灯

```

Ward 13

# Using and updating the Condition Field

- To execute an instruction conditionally, simply postfix it with the appropriate condition:

- For example an add instruction takes the form:

- ADD r0,r1,r2 ; r0 = r1 + r2 (ADDAL)

- To execute this only if the zero flag is set:

```

• ADDEQ r0,r1,r2 ; If zero flag set then...

; ... r0 = r1 + r2

```

- By default, data processing operations do not affect the condition flags (apart from the comparisons where this is the only effect). To cause the condition flags to be updated, the S bit of the instruction needs to be set by postfixing the instruction (and any condition code) with an "S".

- For example to add two numbers and set the condition flags:

```

• ADDS r0,r1,r2 ; r0 = r1 + r2

; ... and set flags

```

# **The Condition Field**

CS 160 圩

CS 160 57

Ward 14

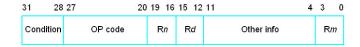

### **Instruction Formats and**

### **Addressing Modes**

#### Most instructions use the format

Conditional Execution Code - bits 28-31

Opcode – bits 20-27

2 or 3 Registers - bits 16-19, 12-15 & 0-3

Other information – bits 4-11 & maybe 0-3

#### CS 160 灯

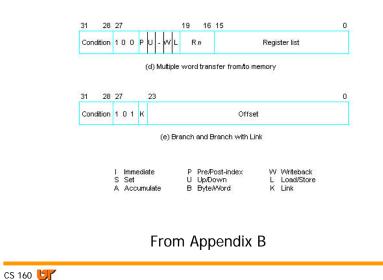

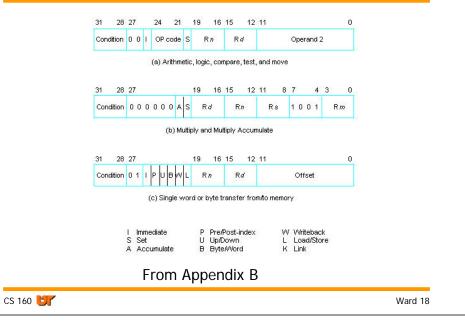

#### **ARM Instruction Encoding Formats** [2]

#### **ARM Instruction Encoding Formats** [1]

#### Addressing Modes [1]

|           | Name                 | Assembler syntax       | Addr essing function                 |

|-----------|----------------------|------------------------|--------------------------------------|

|           | With immediate offse | t.                     |                                      |

|           | Pre-inde xed         | [R n , #offset]        | EA = [R n] + offset                  |

|           | Pre-inde xed         |                        |                                      |

|           | with writeback       | [R n, #offset]!        | EA = [R n] + offset;                 |

|           |                      |                        | Rn← [Rn] + offset                    |

|           | Post-inde xed        | [R n], #offset         | EA = [R n];<br>Rn← [R n] + offset    |

|           |                      |                        |                                      |

|           | EA = effecti ve ad   | dress                  |                                      |

|           | offset = a signed r  | umber contained in the | instruction Between ±4095            |

| Examples: | Instru               | iction                 | Operation                            |

|           | LDR R                | 0,[R1,#12]             | R0 ← [[R1]+12]                       |

|           | STR R                | 0,[R1,#12]!            | & Loc([R1]+12]) ← R0<br>R1 ← [R1]+12 |

Ward 17

Ward 19

## Addressing Modes [2]

|          | Name                                                 | Assembler syntax                                      | Addr essing function                                      |            |

|----------|------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------|------------|

|          | With offset magnitude in                             | n Rm:                                                 |                                                           |            |

|          | Pre-inde xed                                         | [Rn,±Rm, shift]                                       | EA = [R n] ± [R m] shifted                                |            |

|          | Pre-inde xed<br>with writeback                       | [R n ,± R m , shift]!                                 | EA = [R n] ± [R m] shifted;<br>Rn ← [R n] ± [R m] shifted |            |

|          | Post-inde x ed                                       | [R n ], ± Rm , shift                                  | EA = [Rn];<br>Rn ← [Rn] ± [Rm] shifted                    |            |

|          | Relati ve<br>(Pre-inde xed with<br>immediate offset) | Location                                              | EA = Location<br>= [PC] + offset                          |            |

|          |                                                      | LSL for left shift or LSR<br>nsigned number specifyin |                                                           |            |

|          | ± Rm = the offset magnitude<br>contents of basere    |                                                       | added to or subtracted from the                           |            |

| LDR      | R0,[R1,R2,LSL#                                       | 2] R                                                  | 0 ← [[R1]+4*[R2]]                                         |            |

| STR      | R0,[R1],-R2,LSF                                      | × 2.                                                  | oc([R1]) ← R0<br>1 ← [R1] – [R2]/16                       | (truncated |

| CS 160 皆 | IT .                                                 |                                                       |                                                           | War        |

#### More on Load & Store

· Can Load & Store bytes rather than words

Use LDRB rather than LDR and STRB rather than STR.

- Loads & stores from 8 bits in low-order byte position

- Can Load to and Store from multiple registers

- Can only load and store multiple words (32 bits)

- Pre and post indexing with or without writeback modes are all available

- Mnemonic is LDM and STM and may have suffixes such as IA and FD (see next slide)

Example: STMFD R5!, {R0, R1, R2, R3}

Store R3 in [R5-4], R2 in [R5-8], R1 in [R5-12], R0 in [R5-16]

## More on Addressing Modes

• Do not have to specify an offset or shift

Examples: LDR R1,[R5] R1← [[R5]] STR R3,[R0,-R6] Loc([R0]-[R6]) ← R3

No Direct Addressing mode but assembler turns it into Relative addressing mode:

LDR R0,Address

offset  $\leftarrow$  [Address] - [PC] - 8 R0  $\leftarrow$  Loc([PC] + offset)

CS 160 ೮

Ward 22

#### **Multiple Word Transfers**

| Mnemonic<br>(Name)                                     | lnstru c<br>bits | tion | Operation<br>performed                                               |

|--------------------------------------------------------|------------------|------|----------------------------------------------------------------------|

| 10 10                                                  | PUI              |      |                                                                      |

| LDMIA/LDMFD<br>(Incrementafter/<br>Full descending)    | 01               | 1    | R <sub>bw</sub> ,,R <sub>bbh</sub> ← [[Rn]],[[Rn]+4],                |

| LDMIB/LDMED<br>(Increment before/<br>Empty descending) | 1 1              | 1    | $R_{bw}, \cdots, R_{bbh} \leftarrow [[Rn] + 4], [[Rn] + 8], \dots$   |

| LDMD A/LDMF A<br>(Decrementafter/<br>Full ascending)   | 0 0              | 1    | $R_{biph}, \ldots, R_{bw} \leftarrow [[Rn]], [[Rn] - 4], \ldots$     |

| LDMDB/LDMEA<br>(Decrementbefore/<br>Empty ascending)   | 1 0              | 1    | $R_{biph}, \dots, R_{bw} \leftarrow [[Rn] - 4], [[Rn] - 8], \dots$   |

| STMIA/STMEA<br>(Incrementafter/<br>Empty ascending)    | 01               | 0    | $[Rn], [Rn] + 4, \ldots \leftarrow [R_{bw}], \cdots, [R_{bbh}]$      |

| STMIB/STMF A<br>(Increment before/<br>Full ascending)  | 1 1 1            | 0    | $[Rn] + 4, [Rn] + 8, \ldots \leftarrow [R_{low}], \ldots, [R_{low}]$ |

| STMDA/STMED<br>(Decrementafter/<br>Empty descending)   | 0 0 1            | 0    | $[Rn], [Rn] - 4, \dots \leftarrow [R_{bloch}], \dots, [R_{low}]$     |

| STMDB/STMFD<br>(Decrementbefore/<br>Full descending)   | 101              | 0    | $[Rn] - 4, [Rn] - 8, \dots \leftarrow [R_{bbb}], \dots, [R_{bow}]$   |

CS 160 灯

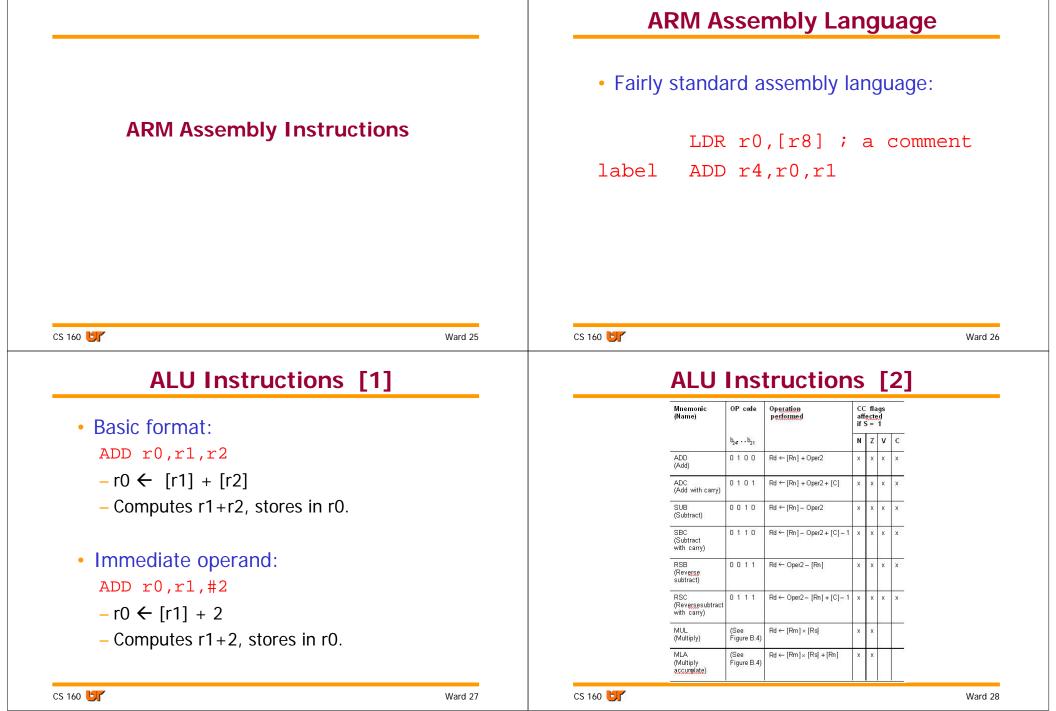

### ALU Instructions [3]

| Mnemonic<br>(Name)    | OP code                         | Operation<br>performed | CC flags<br>affected<br>if S = 1 |   |   |   |  |

|-----------------------|---------------------------------|------------------------|----------------------------------|---|---|---|--|

|                       | b <sub>24</sub> b <sub>21</sub> |                        | N                                | Z | v | С |  |

| AND<br>(Logical AND)  | 0000                            | Rd ← [Rn] ∧ Oper2      | х                                | х |   | X |  |

| ORR<br>(Logical OR)   | 1100                            | Rd ← [Rn] – Oper2      | x                                | x |   | x |  |

| EOR<br>(Exclusive-OR) | 0001                            | Rd ← [Rn] ∨ Oper2      | ×                                | x |   | x |  |

| BIC<br>(Bit clear)    | 1110                            | Rd ← [Rn] ∧ ¬Oper2     | x                                | х |   | x |  |

# **Comparison/Test Instructions**

| Mnemonic<br>(Name)                | OP code                         | Operation<br>performed | CC flags<br>affected<br>if S = 1 |   |   |   |

|-----------------------------------|---------------------------------|------------------------|----------------------------------|---|---|---|

|                                   | b <sub>24</sub> b <sub>21</sub> |                        | N                                | Z | v | C |

| CMP<br>(Compare)                  | 1010                            | [Rn] – Oper2           | x                                | x | x | х |

| CMN<br>(Compare <u>Negativ</u> e) | 1011                            | [Rn] + Oper2           | x                                | x | х | х |

| TST<br>(Bit test)                 | 1000                            | [Rn]  A Oper2          | x                                | x |   | х |

| TEQ<br>(Test equal)               | 1001                            | [Rn]⊕Oper2             | x                                | x |   | х |

• These instructions set only the NZCV bits of CPSR.

| CS 160 | ur | Ward 29 | CS 160 ೮ |

|--------|----|---------|----------|

### **Branching Instructions**

K=0 Branch (B) K=1 Branch with Link (BL); store return address in register R14

#### Examples:

- BEQ LOC1

- BNE LOC2

- BL ROUTINE

Ward 30

## **ARM Move Instructions**

| Mnemonic<br>(Name)      | OP code                         | Operation<br>performed | aff | : fla<br>ecte<br>S = | d |   |

|-------------------------|---------------------------------|------------------------|-----|----------------------|---|---|

|                         | b <sub>24</sub> b <sub>21</sub> |                        | N   | Z                    | ۷ | C |

| MOV<br>(Move)           | 1101                            | Rd ← Oper2             | x   | x                    |   | x |

| M∨N<br>(MoveComplement) | 1111                            | Rd ←¬ Oper2            | x   | x                    |   | x |

#### MOV r0,r1 ; sets r0 to r1

## **Load/Store Instructions**

- LDR, LDRB : load (word, byte)

- STR, STRB : store (word, byte)

- Addressing modes:

- register indirect : LDR r0,[r1]

- with second register : LDR r0, [r1, -r2]

- with constant : LDR r0, [r1, #4]

# ADR pseudo-op

#### ADR r1,F00

- Loads the 32-bit address FOO into r1

- Not an actual machine instruction •

- Assembler replaces with real machine • instructions to produce desired results

| 160 57                                                                                                                                                                                                                                                                                                                                                      | Ward 33 CS 160 5 | W |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---|

| ARM subroutine linkage                                                                                                                                                                                                                                                                                                                                      | e                |   |

| <ul> <li>Branch and link instruction:<br/>BL ROUTINE         <ul> <li>Copies current PC to r14.</li> </ul> </li> <li>Initial instructions in ROUTINE         <ul> <li>Save registers used in subroutine and r14 of (allows nested calls); for example:<br/>ROUTINE STMFD R13!,{r0,r1,r2,r14}</li> </ul> </li> <li>Final instructions in ROUTINE:</li> </ul> | on stack         |   |

| <ul> <li>Restore saved registers from stack and retraddress from stack to r15; for example:<br/>LBMFD R13!,{r0,r1,r2,r15}</li> </ul>                                                                                                                                                                                                                        |                  |   |

| <ul> <li>Nested and recursive calls handled prop<br/>with this process</li> </ul>                                                                                                                                                                                                                                                                           | perly            |   |