# **ARM Processors**

Lecture on Introduction to Embedded Systems

By

Harish V. Mekali

Assistant Professor, Dept. of ECE

BMSCE, Bangalore - 19

#### **Abstraction**

## **Embedded Systems**

**SOFTWARE**

**HARDWARE**

## **PROTOCOL**

#### **Abstraction**

## **System architecture**

## Microprocessor

- CPU is stand-alone, RAM,

ROM, I/O, timer are separate

- Designer can decide on the amount of ROM, RAM and I/O ports.

- Expansive

- Versatility

- General-purpose

## Microcontroller

- CPU, RAM, ROM, I/O and timer are all on a single chip

- Fix amount of on-chip ROM, RAM, I/O ports

- For applications in which cost, power and space are critical

- Not Expansive

- Single-purpose

#### **CPU** architecture

#### Comparison

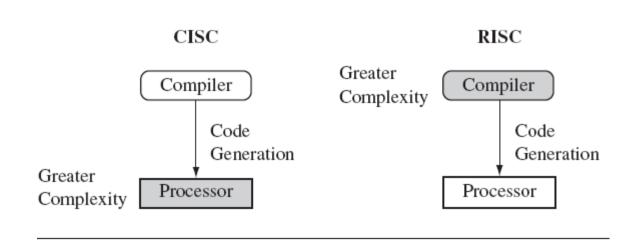

CISC RISC

Any instruction may reference memory Only load/store references memory

Many instructions & addressing modes Few instructions & addressing modes

Variable instruction formats Fixed instruction formats

Single register set Multiple register sets

Multi-clock cycle instructions Single-clock cycle instructions

Micro-program interprets instructions Hardware (FSM) executes instructions

Complexity is in the micro-program Complexity is in the compiler

Less to no pipelining Highly pipelined

Program code size small Program code size large

#### **CPU** architecture

### Memory architecture

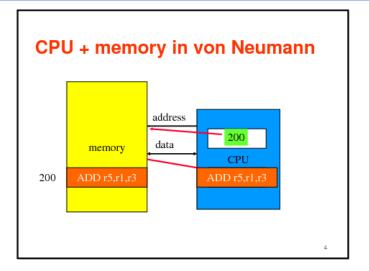

#### von Neumann Architecture

- · Memory holds data, instructions.

- Central processing unit (CPU) fetches instructions from memory.

- Separate CPU and memory distinguishes programmable computer.

- · CPU registers help out:

- · Program counter (PC),

- · Instruction register (IR),

- · General-purpose registers, etc.

.

#### von Neumann vs. Harvard

- von Neumann

- · Same memory holds data, instructions.

- A single set of address/data buses between CPU and memory

- Harvard

- Separate memories for data and instructions.

- Two sets of address/data buses between CPU and memory

data memory

data

PC

address

program memory

data

Harvard architecture

5

# Why ARM?

## **ARM Design Philosophy**

- Low power

- Small size

- High code density

- Low cost

- Easy debug

## **The ARM Processor Family**

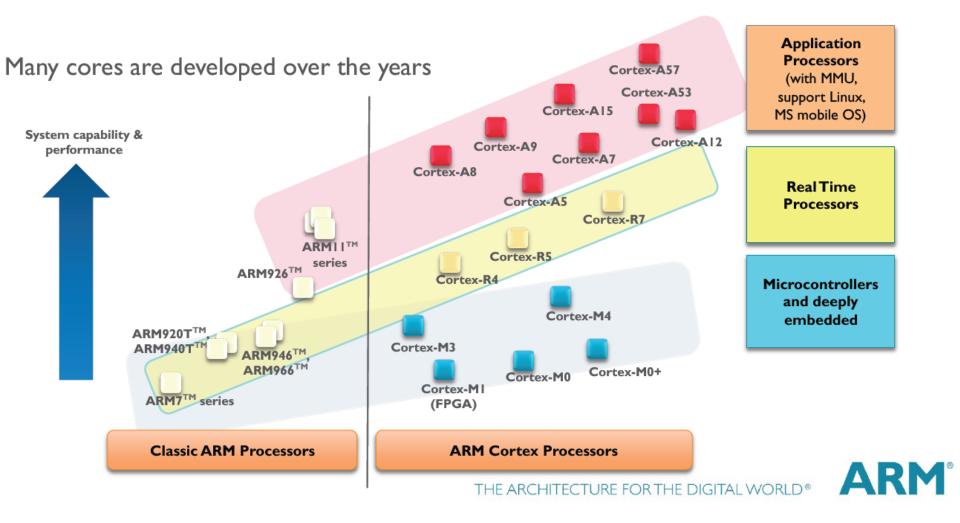

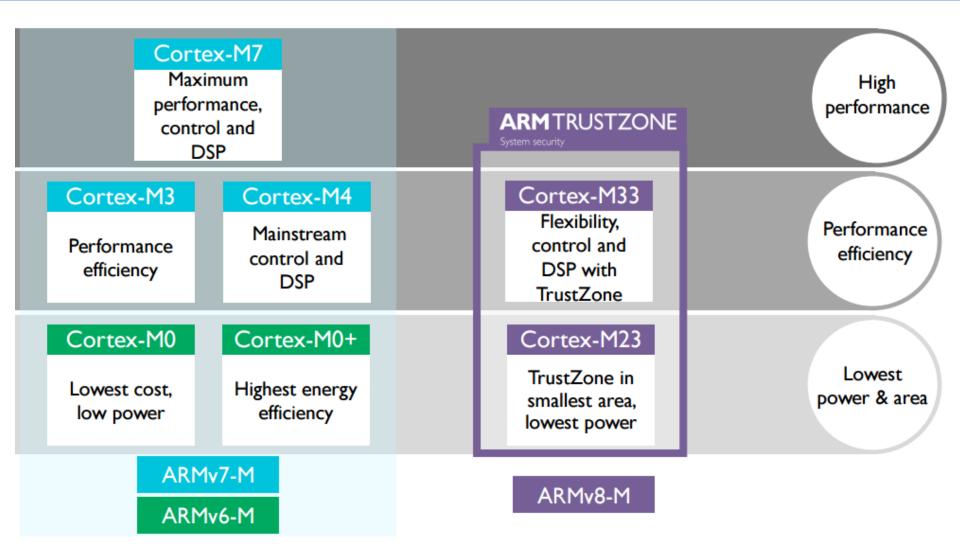

### **The ARM Processor Family**

## **Binary Upwards Compatibility**

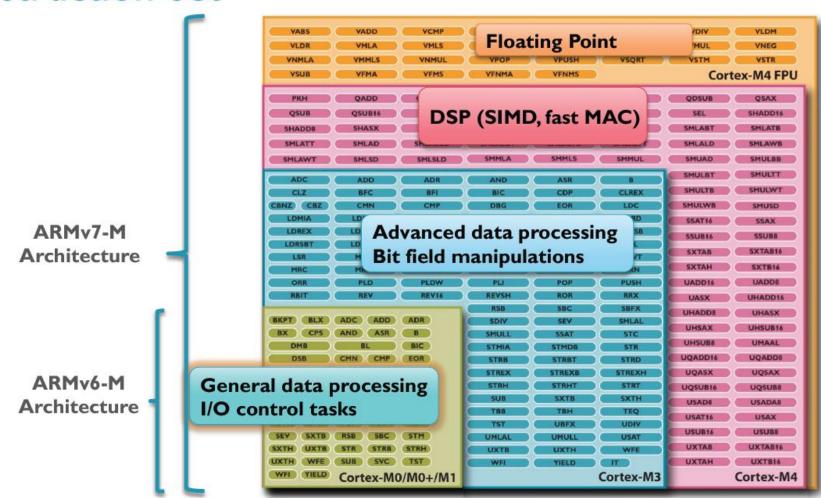

## Instruction Set

ARM University Program

The Architecture for the Digital World\* ARM

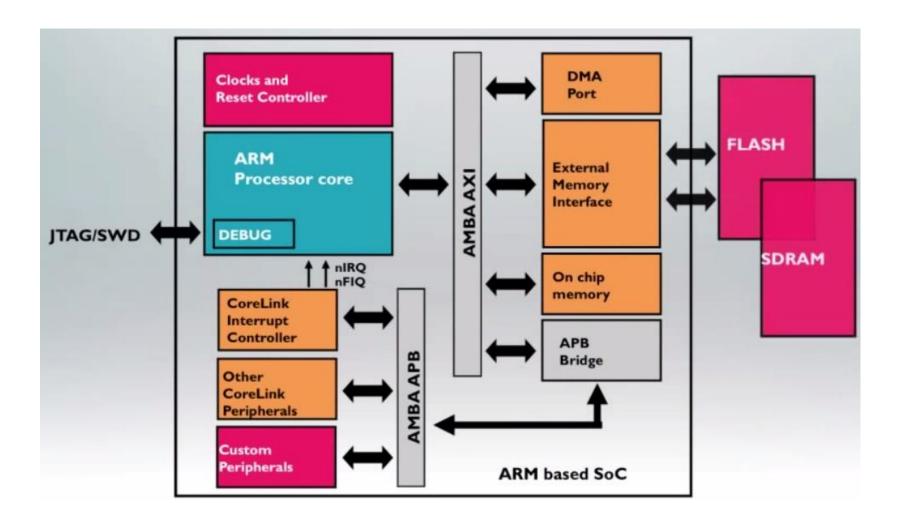

## **Inside ARM based System**

ARM University Program

The Architecture for the Digital World\* ARM\*

## **Inside ARM based System**

#### **AMBA**

AMBA ( Advanced Microcontroller Bus Architecture )

It is an open-standard, on-chip interconnect specification for the connection and management of functional blocks in system-on-a-chip (SoC) designs.

ASB (Advanced System Bus) : Simple bi-directional bus

APB (Advanced Peripheral Bus): Low speed peripheral bus

AHB (Advanced High speed Bus): Centralized multilayer bus

AHB multi : Multi master – multi slave

AHB lite : Single master – multi slave

Mostly ARM core is Bus master and Peripherals are slaves

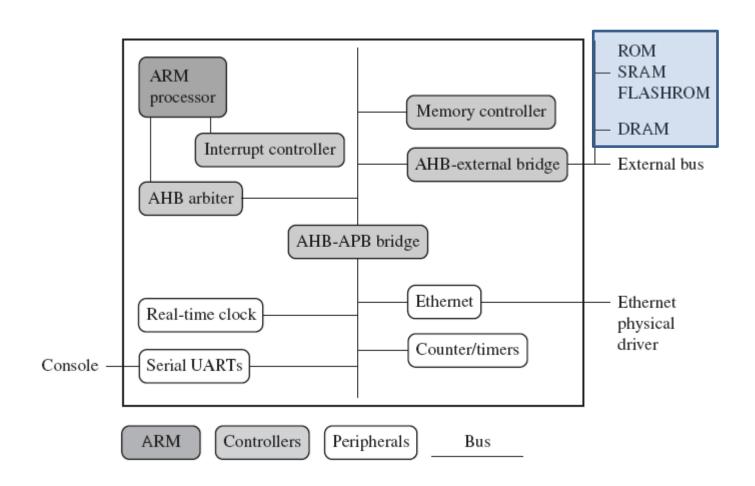

### **Peripherals**

- All peripherals are Memory mapped

- Controllers are special types of peripherals that govern the interfacing policies

- Interrupt controller

- Standard Interrupt control No Priority

- Vector Interrupt Control (VIC) Priority based

- Memory controller

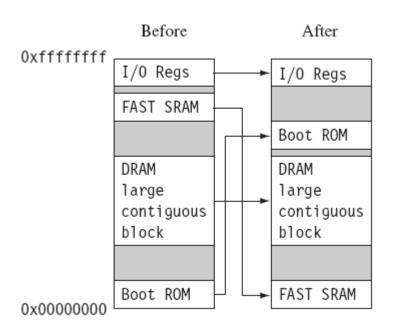

- Memory preparation

- Ex: DRAM requires to be configured for refresh rates and timing before it is accessed

- Memory management

- Memory protection

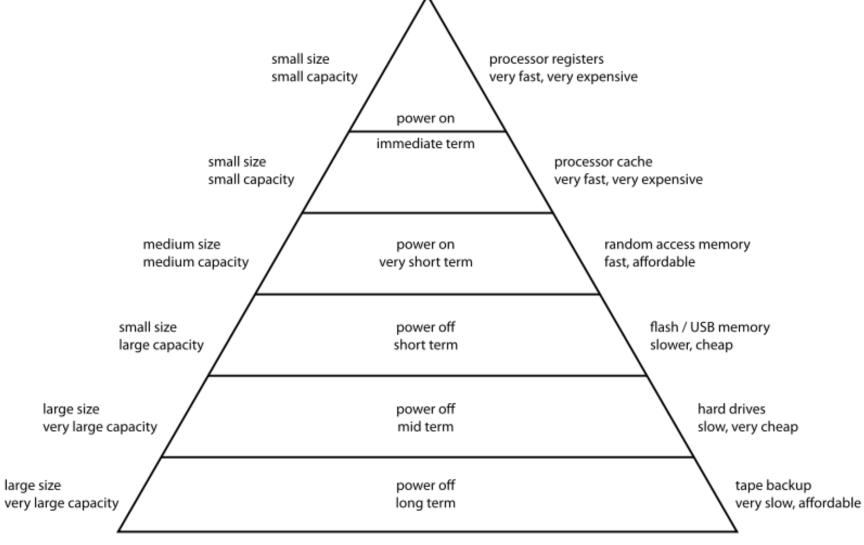

# Computer Memory Hierarchy

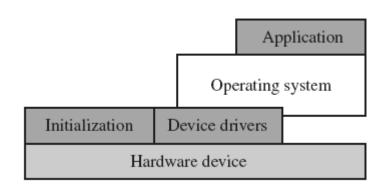

#### **Embedded Software**

#### Boot / initialization code

It runs on reset and does following basic tasks

- Initial hardware configuration like memory controllers and cache i.e., it prepares the hardware to satisfy the image to be booted

- Diagnostics: Fault detection and isolation

- Booting : Loading image and handing over the control to image by modifying the PC(Program Counter)

#### **Embedded Software**

#### Operating System

Organizes system resources like peripherals, memory and processors time

- Two main categories

- Real Time Operating Systems (RTOS)

- Hard real time

- Soft real time

- Platform Operating Systems

Manages large non real time applications

#### Applications

Code dedicated to handle a particular task

# Thank you

## Harish V. Mekali

hvm.ece@bmsce.ac.in

+91-9538765141

www.harishvmekli.blogspot.com

I acknowledge and appreciate ARM University Program(AUP) and ARM Embedded Systems pvt. Ltd. for their continuous support.

# References

#### Video lectures:

Mr. Chrish Shore, ARM Training Manager, UK

The ARM University Program, ARM Architecture Fundamentals

<a href="https://www.youtube.com/watch?v=7LqPJGnBPMM">https://www.youtube.com/watch?v=7LqPJGnBPMM</a>

2. Dr.Santanu Chaudhury, Dept. of Electrical Engineering, IIT Delhi Lecture - 5 ARM: ( <a href="https://www.youtube.com/watch?v=4VRtujwa\_b8">https://www.youtube.com/watch?v=4VRtujwa\_b8</a>)

#### Website:

3. <a href="http://infocenter.arm.com/help/index.jsp">http://infocenter.arm.com/help/index.jsp</a>

#### **Textbooks:**

- 1. ARM system developers guide, Andrew N Sloss, Dominic Symes and Chris Wright, Elsevier, Morgan Kaufman publishers, 2008.

- ARM System-on-Chip Architecture, Steve Furber, Second Edition, Pearson, 2015