The Thesis Entitled

# Asynchronous Design Methodology for an Efficient Implementation of Low Power ALU

Submitted in partial fulfillment of the requirements for the degree of

Master of Science in Computer Science and Engineering

by

G. Sundar

Under the guidance of

### Dr. Chitta Ranjan Mandal

Department of Computer Science & Engineering Indian Institute of Technology Kharagpur India July 2006

### Certificate

This is to certify that the dissertation entitled Asynchronous Design Methodology for an Efficient Implementation of Low Power ALU, submitted by G. Sundar, a student in the Department of Computer Science and Engineering, Indian Institute of Technology Kharagpur, India, for the award of the degree of Master of Science, is a record of an original work carried out by him under my supervision and guidance. This dissertation fulfills all requirements as per the regulations of this Institute and in my opinion has reached the standard needed for submission. Neither this dissertation nor any part of it has been submitted for any degree or any academic award elsewhere.

#### Dr. Chitta Ranjan Mandal

Department of Computer Science & Engineering Indian Institute of Technology Kharagpur West Bengal, India 721302

### Abstract

The power consumption becomes an important issue in circuit design technologies. The power dissipation in high-performance CMOS VLSI circuits like microprocessors is becoming an increasing problem. One reason for the high power dissipation is the almost universal design approach synchronous circuits, which imposes global synchrony across a chip. This is achieved by applying a common clock to all the functional units on a chip and has the undesirable side effect of causing those units to dissipate power whether or not they are doing useful work. The main objective of designing the asynchronous circuits will be there is no master clock, the reduction in silicon by following domino logic with dual-rail logic and thus ensures the power consumption in designing the circuits.

We present a design technique for implementing asynchronous ALUs with CMOS domino logic and delay insensitive dual rail fourphase logic. It ensures economy in silicon area and potentially for low power consumption. The design has been described and implemented to achieve high performance in comparison with the synchronous and available asynchronous designs. This implementation justifies the claimed performance through the SPICE simulation results.

**Keywords:** Integrated Circuits, Design Styles, Domino Logic, Delay insensitive, 4-phase dual-rail logic, Arithmetic and Logic Structures.

## Acknowledgement

This thesis would not have been a reality if my advisor Dr. C. R. Mandal hadn't given the best of moral support to me from the day I started my work here. His constant support coupled with his welltimed advices has helped me at every step of my work. I express my deep gratitude and indebtedness to him for giving me this golden opportunity.

I am particularly thankful to Prof. A. K. Majumdar, Prof. B. Majumdar, Prof. S. Ghosh, , Prof. I. Sengupta, Prof. B. D. Liu and Prof D. Sarkar for their constant encouragement and support. I would like to express my devout thanks to Dr. D. Samanta, who inspite of his busy schedule selflessly helped me throughout my project work.

I am also deeply indebted to Dr. Gunasekaran, the Registrar of the Institute and all my tamil friends for their constant help and encouragement throughout this period. I sincerely thank Dr. D. K. Nanda for his valuable support. Special thanks to Monalisaji and her family for the unstinted support by making me mentally tough enough to face and overcome difficult situations which came by.

I am grateful to Jayanto da, Anupam da, Prasenjit da and all the computer and Informatics Centre staff members for their help at times of need.

I am thankful to Ramesh, and my beloved sister Vijayakumari for their continuous inspiration and support throughout this period.

Last but not the least I express my gratitude to my mother and father for their sacrifice and patience in spite of many lost hours in their covetable association with me.

G. Sundar.

Dedicated to My beloved Parents

## Contents

| List of Figures vi |                |                                               | vi |  |

|--------------------|----------------|-----------------------------------------------|----|--|

| L                  | List of Tables |                                               |    |  |

| 1                  | Intr           | oduction                                      | 1  |  |

|                    | 1.1            | Motivation of the Work                        | 5  |  |

|                    | 1.2            | Brief Overview of our Work                    | 12 |  |

|                    | 1.3            | Organization of the Thesis                    | 13 |  |

| 2                  | C              | MOS Logics and Asynchronous Design            |    |  |

|                    | Μ              | ethodologies                                  | 15 |  |

|                    | 2.1            | Static CMOS                                   | 15 |  |

|                    | 2.2            | Dynamic CMOS                                  | 21 |  |

|                    | 2              | 2.2.1 Domino Logic                            | 27 |  |

|                    | 2              | 2.2.2 NORA Logic                              | 29 |  |

|                    | 2.3            | Handshake protocols                           | 31 |  |

|                    | 2              | 2.3.1 Bundled data protocols                  | 31 |  |

|                    | 2              | 2.3.2 4-phase dual rail protocol              | 33 |  |

|                    | 2              | 2.3.3 2-phase dual-rail protocol              | 36 |  |

|                    | 2.4            | Indication Principle and the Muller C-element | 36 |  |

|                    | 2.5            | Muller pipeline                               | 38 |  |

|                    | 2.6            | 4-phase dual-rail pipeline                    | 40 |  |

| 3                  | Arc            | hitecture and Implementation of ALU           | 42 |  |

|                    | 3.1            | Speed-independence basics                     | 42 |  |

|                    | 3.2            | Asynchronous circuits- a brief classification |    |  |

|                    |                | with delay                                    | 44 |  |

|                    | 3.3            | Isochronic forks                              | 46 |  |

| 3.4 Circuit relations with speed-independence    | 46 |

|--------------------------------------------------|----|

| 3.5 Building blocks of Asynchronous circuits     | 48 |

| 3.5.1 Latches                                    | 48 |

| 3.5.2 Function blocks                            | 48 |

| 3.5.3 Unconditional flow control                 | 49 |

| 3.5.4 Conditional flow control                   | 50 |

| 3.6 The 4-phase dual-rail implementation of      |    |

| basic components                                 | 50 |

| 3.7 Completion detection implementation with     |    |

| Muller C-elements                                | 52 |

| 3.8 Simple AND gate implementation with          |    |

| Muller C-element                                 | 53 |

| 3.9 Hybrid Adder Function                        | 55 |

| 3.10 4-phase dual-rail adder implementation      |    |

| with Muller C-elements                           | 56 |

| 3.11 4-phase dual-rail Dynamic CMOS Asynchronous |    |

| ALU Implementation                               | 58 |

|                                                  |    |

| 4. Performance Analysis and Simulation Results   | 61 |

| 4.1 Spice simulation tool                        | 61 |

| 4.2 Analysis of Logic operations                 | 62 |

| 4.3 Basic Addition Operation Analysis            | 65 |

| 5. Conclusions                                   | 72 |

| 5.1 Future Directions                            | 74 |

| 5.2 Publications/Communications out of this work | 75 |

# **List of Figures**

| 1.1  | Basic block diagram of an Asynchronous Circuit         | 5  |

|------|--------------------------------------------------------|----|

| 1.2  | (a) A synchronous circuit, (b) a synchronous circuit   |    |

|      | with clock drivers and clock gating, (c) an equivalent |    |

|      | asynchronous circuit, and (d) an abstract data-flow    |    |

|      | view of the asynchronous circuit.                      | 9  |

| 2.1  | CMOS inverter circuit                                  | 17 |

| 2.2  | CMOS inverter circuits in stages                       | 17 |

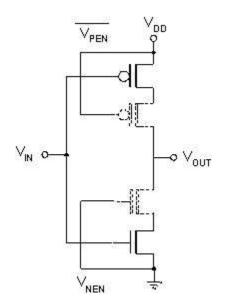

| 2.3  | CMOS tristate inverter                                 | 18 |

| 2.4  | Pseudo-NMOS logic                                      | 20 |

| 2.5  | Basic Structure of dynamic CMOS logic                  | 21 |

| 2.6  | Example for dynamic CMOS logic                         | 23 |

| 2.7  | Dynamic CMOS logic structure for minimum clock speed   | 25 |

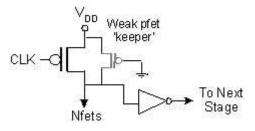

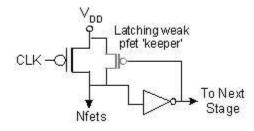

| 2.8  | Latching of weak PMOS in dynamic logic                 | 26 |

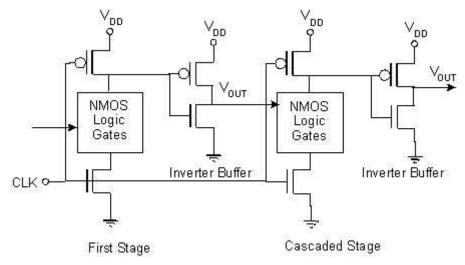

| 2.9  | Dynamic CMOS domino logic structure                    | 28 |

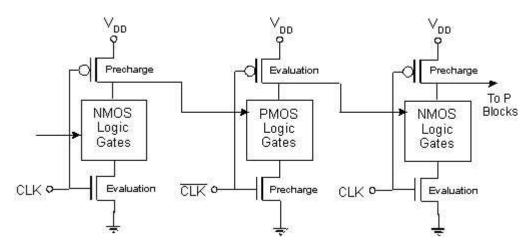

| 2.10 | Dynamic CMOS NORA logic structure                      | 29 |

| 2.11 | Clock skew representation                              | 30 |

| 2.12 | A bundled-data channel                                 | 31 |

| 2.13 | A 4-phase bundled-data protocol                        | 32 |

| 2.14 | A 2-phase bundled data protocol                        | 32 |

| 2.15 | The 4-phase dual-rail channel                          | 33 |

| 2.16 | The 4-phase dual-rail protocol handshaking             | 34 |

| 2.17 | Illustration of 4-phase dual-rail channel handshaking  | 35 |

| 2.18 | Illustration of 2-phase dual-rail protocol handshaking | 36 |

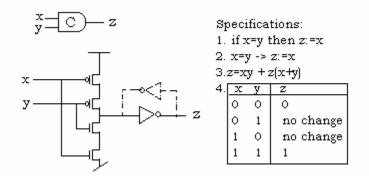

| 2.19 | OR gate                                                | 37 |

| 2.20 | Muller C-element symbol and implementation with        |    |

|      | Specification                                          | 38 |

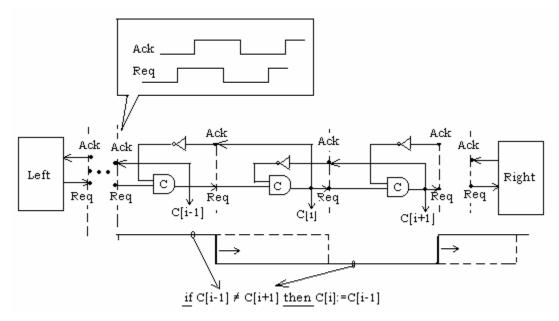

| 2.21 | Illustration of Muller pipeline                        | 39 |

| 2.22 | Simple 1-bit wide 3-stage 4-phase dual-rail pipeline   | 41 |

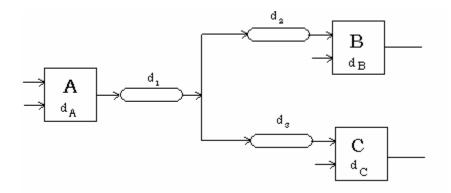

| Muller Model of a Muller pipeline stage with                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dummy gates modeling                                           | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A circuit part with gate and wired delays                      | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

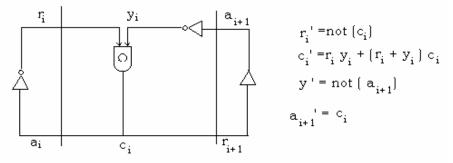

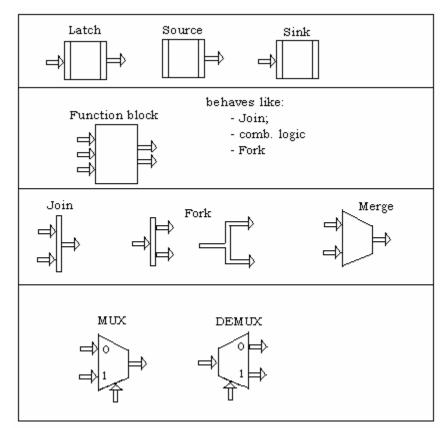

| Building blocks for asynchronous circuits                      | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

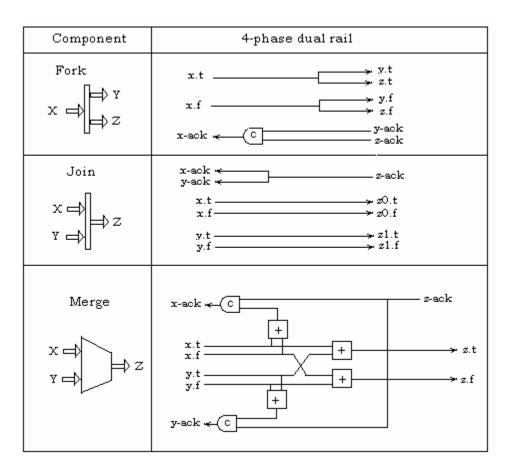

| The 4-phase dual-rail implementation of fundamental            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Components                                                     | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Implementation of N-bit latch with completion detection        | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

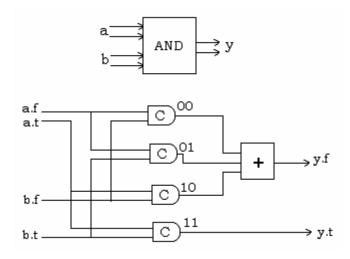

| Dual-rail implementation of AND gate with Muller               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| C-element                                                      | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

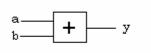

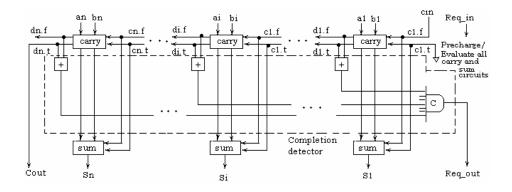

| N-bit Adder Block diagram dual-rail implementation             | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

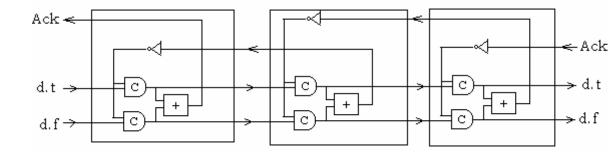

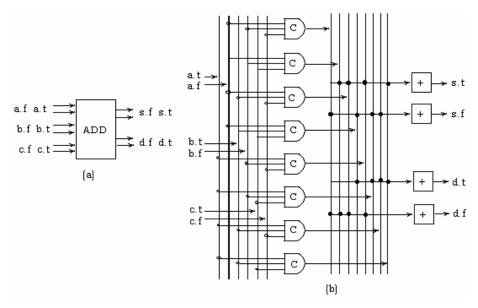

| 4-phase dual-rail adder (a) symbol (b) implementation          | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

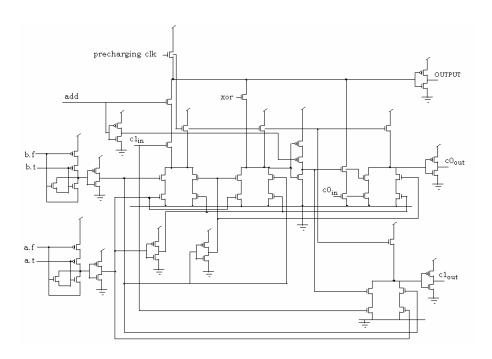

| Dynamic CMOS 4-phase dual-rail asynchronous ALU                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1-bit circuit                                                  | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

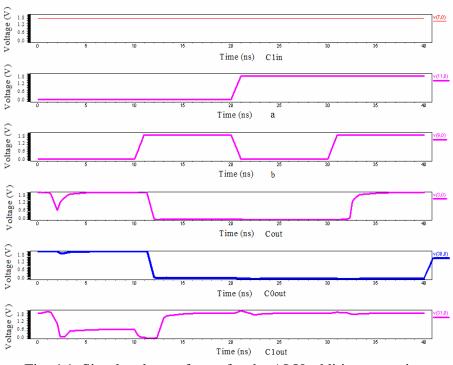

| Simulated waveforms for the ALU addition operation             | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

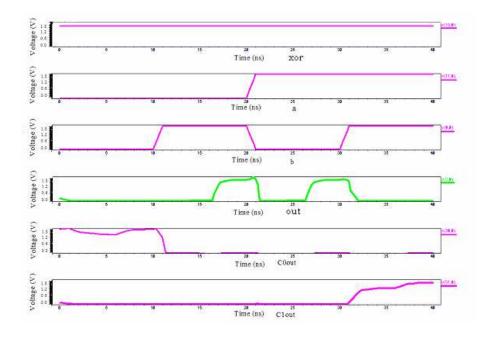

| Simulated waveforms for the X-OR operation                     | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

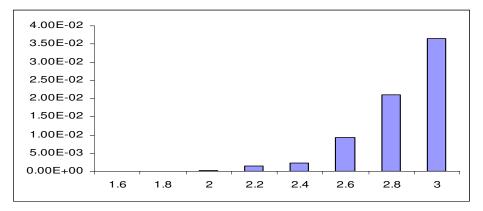

| Simulation Results for power consumption at                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Different VDD                                                  | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

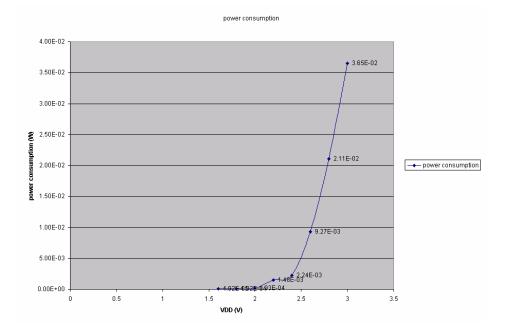

| $V_{\text{DD}}Vs$ Power consumption of ALU for Adder operation | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

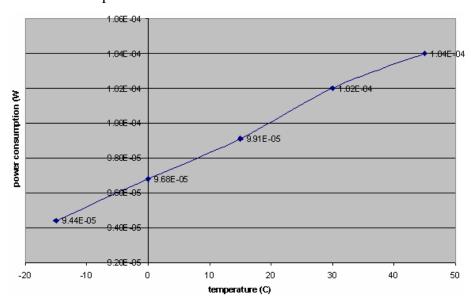

| Temperature Vs Power consumption of ALU for Adder              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Operation                                                      | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

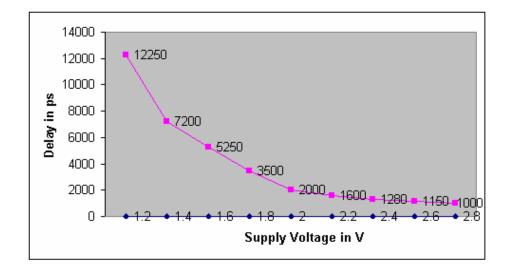

| Supply Voltages (VDD) Vs Delay performance for ALU             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Addition operation                                             | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                | <ul> <li>Dummy gates modeling</li> <li>A circuit part with gate and wired delays</li> <li>Building blocks for asynchronous circuits</li> <li>The 4-phase dual-rail implementation of fundamental</li> <li>Components</li> <li>Implementation of N-bit latch with completion detection</li> <li>Dual-rail implementation of AND gate with Muller</li> <li>C-element</li> <li>N-bit Adder Block diagram dual-rail implementation</li> <li>4-phase dual-rail adder (a) symbol (b) implementation</li> <li>Dynamic CMOS 4-phase dual-rail asynchronous ALU</li> <li>1-bit circuit</li> <li>Simulated waveforms for the ALU addition operation</li> <li>Simulated waveforms for the X-OR operation</li> <li>Simulation Results for power consumption at</li> <li>Different VDD</li> <li>VDD Vs Power consumption of ALU for Adder operation</li> <li>Temperature Vs Power consumption of ALU for Adder</li> <li>Operation</li> <li>Supply Voltages (VDD) Vs Delay performance for ALU</li> </ul> |

## List of Tables

| 2.1 | Truth table OR gate                                | 37 |

|-----|----------------------------------------------------|----|

| 3.1 | Truth table for AND gate implementation            | 54 |

| 3.2 | Truth table for 4-phase dual rail adder            | 57 |

| 3.3 | Functions available with the ALU                   | 60 |

| 4.1 | Input/output logic specification for addition by   |    |

|     | ALU                                                | 63 |

| 4.2 | Input/output logic specification for X-OR          |    |

|     | Operation by ALU                                   | 64 |

| 4.3 | Power consumption for addition operation at        |    |

|     | Different VDD                                      | 67 |

| 4.4 | Power consumption for adder operation at different |    |

|     | Temperatures                                       | 68 |

| 4.5 | Delay for addition operation with different supply |    |

|     | voltages VDD                                       | 69 |

| 4.6 | Simulation Results for ALU operation               | 70 |

| 4.6 | Performance Comparison with other published        |    |

|     | Works                                              | 71 |

### **Chapter 1**

### Introduction

The power consumption becomes an important issue in design technologies. The power dissipation in high-performance CMOS VLSI circuits like microprocessors is becoming an increasing problem. Even when battery power portability is not an issue the 20 or 30 Watt consumption of the latest high-end processors makes it difficult to keep the silicon at an acceptable operating temperature. At lower performance levels the designers of battery powered systems must make difficult trade-offs between the processing demands of, for example, hand-writing recognition software and the minimum acceptable battery life of their products. The process advances which have caused CMOS to progress from a low power technology to a high power technology show no signs of abating and, if new approaches are not developed, state-of-the-art performance in twelve years time will only be delivered at the cost of power dissipations one or two orders of magnitude higher than today's. While there are developments that alleviate this problem, such as the trend towards 3 volt (and later 2 volt) operation, these do not go far enough to remove the possibility that power dissipation might limit the performance that a chip can deliver.

One reason for the high power dissipation is the almost universal design approach, which imposes global synchrony across a chip. This is achieved by applying a common clock to all the functional units on a chip and has the undesirable side effect of causing those units to dissipate power whether or not they are doing useful work. There is no doubt that the synchronous approach to logic design has been very effective over the last two decades, and has enabled great advances to be made in the productivity of designers and their design tools and in the performance of machines. However there is now a resurgence opinion suggesting that it may be time to re-assess the merits of other design approaches. Higher speeds and larger chips are making the abstraction of global synchrony increasingly hard to sustain even on a single chip, with the power dissipation making this approach much less attractive. While it is possible to address power issue by gating clocks to individual units, this makes the clock skew problem much worse and is therefore needs for better solution.

The power consumption can be reduced by decreasing the supply voltage, load capacitance and frequency [1]. Several attempts are made to address this problem to reduce the switching activity of logic in redundant cycles [3] [21]. Xi et. a1 provides an optimization algorithm for buffer and device sizing under process variations [2]. Although it minimizes the skew, this methodology is limited when operating frequency is very high. On the other hand, Globally Asynchronous and Locally Synchronous (GALS) technique [10] [22] aims to eliminate the global clock, by partitioning the system into several synchronous blocks and communicating asynchronously among blocks. However, the global signaling protocol increases the total area-power penalty and affects performance of the system.

Asynchronous design approaches are therefore attracting renewed interest. New approaches to asynchronous designs are overcoming some of the difficulties, which had previously been impediments to cost-effective designs. Asynchronous designs tend naturally (in CMOS) to use power only when doing useful work and interfacing disciplines produce more modular designs with an inherent potential for component reuse[5].

In asynchronous systems, idle parts of the chip consume negligible power [9] [12]. This feature is particularly valuable for battery – powered equipment, but it can also cut the cost of larger systems by reducing the need for cooling fans and air-conditioning to prevent them from overheating. The amount of power saved depends on the machine's pattern of activity. Systems with parts that act only occasionally benefit more than systems that act continuously.

Most computers have components, such as the floating-point arithmetic unit, that often remain idle for long periods. Furthermore, systems produce less radio interferences than asynchronous synchronous machines do [39]. Because a clocked system uses a fixed rhythm, it broadcasts a strong radio signal at its operating frequency and at the harmonics of that frequency. Such signals can interface with cellular phones, televisions and aircraft navigation systems that operate at the same frequencies. Asynchronous systems lack a fixed rhythm, so they spread their radiated energy broadly across the radio spectrum, emitting less at any one frequency. Yet another benefit of asynchronous design is that it can be used to build bridges between clocked computers running at different speeds. Many computing clusters, for instance, link fast PCs with slower machines [33]. These clusters can tackle complex problems by dividing the computational tasks among the PCs. Finally, although asynchronous design can be challenging, it can also be wonderfully flexible. Because the circuits of an asynchronous system need not share a common rhythm, designers

have more freedom in choosing the system's parts and determining how they interact. Moreover, replacing any part with a faster version will improve the speed of the entire system. In contrast, increasing the speed of a clocked system usually requires upgrading every part. Several researchers propose asynchronous approaches to cope with performance and timing issue. Tang et. al. design a 16-bit asynchronous ALU with asynchronous pipeline architecture [4]. In this approach, simple handshake cells embedded in pipeline stages make the ALU run fast. However, large power has consumed by this design while waiting for the incoming data. In contrast, by using Galois Field arithmetic logic and reduced switching activity in the latches, work proposed in [5] achieved low power in an asynchronous ALU design. Since the improper rotate-wire concept of data buses, the time required for each multiplication operation becomes larger and it results in degradation of the performance.

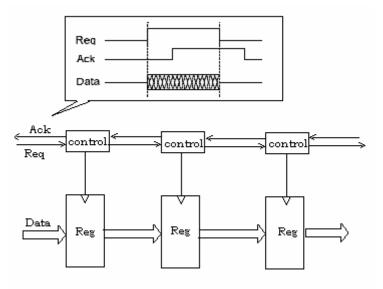

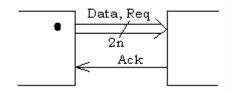

In reducing the time dependency of an asynchronous design of Quantum dot Cellular Automata (QCA), Hemani et al. [6] used GALS with delay-insensitive data encoding scheme. Here each gate has locally synchronized by corresponding clocking zone(s). Appropriate data forwarding and synchronization guaranteed at the gate-level that reduces the number of clocking zones and increases the circuit speed. Nevertheless, the overall timing of the circuit depends upon the layout. An asynchronous bundled-data pipeline for the matrix–vector multiplication core of discrete cosine transforms achieved 30% higher average throughput [16] based on a bit-partitioned carry-save multiplier. Due to its bulky control overhead, the controller drops its speed gain. These methods intend to improve the power consumption/performance of IC's using asynchronous methodology. The basic block structure of the asynchronous circuit is given in Fig.1.1. The data is processed to next step through register on demand of request signal. The next request signal issued only on acknowledge of the previous process completion. This way clock is eliminated by the acknowledge signal for each process of data.

Fig.1.1 Basic block diagram of an Asynchronous Circuit.

#### 1.1 Motivation of the work

Nowadays it is essential that each application instrument of the electronic industry should be compact, consume less power and less delay performance. Researches are continuing to reduce the above three parameters especially in battery operated computing devices. The sources of energy consumption on a CMOS chip can be classified as static and dynamic power dissipation [18] [19]. The dominant component of energy consumption in CMOS is dynamic power consumption caused by the actual effort of the circuit to switch. A first order approximation of the dynamic power consumption of CMOS circuitry [17] is given by the formula:

$$\mathbf{P} = \mathbf{C} * \mathbf{V}^2 * \mathbf{f}$$

where P is the power, C is the effective switch capacitance, V is the supply voltage, and f is the frequency of operation. The power dissipation arises from the charging and discharging of the circuit node capacitances found on the output of every logic gate. Every low-to-high logic transition in a digital circuit incurs a change of voltage, drawing energy from the power supply.

A designer at the technological and architectural level can try to minimize the variables in these equations to minimize the overall energy consumption. However, power minimization is often a complex process of trade-offs between speed, area, and power consumption [23]. This difficulty can be overcome by choosing the asynchronous design methodology where the dynamic power is almost avoided since there is no global clock. Also the transistors will be used at the time of demand only, which is unlikely with synchronous designs.

Most digital circuits designed and fabricated today are "synchronous". In essence, they are based on two fundamental assumptions that greatly simplify their design: (1) all signals are binary, and (2) all components share a common and discrete notion of time, as defined by a clock signal distributed throughout the circuit.

Asynchronous circuits are fundamentally different; they also assume binary signals but there is no common discrete time. Instead the circuits use handshaking between their components in order to perform the necessary synchronization, communication, and sequencing of operations. Expressed in ' synchronous terms' this results in a behaviour that similar to systematic fine-grain clock gating and local clocks that are not in phase and whose period is determined by actual circuit delays-registers are only clocked where and when needed [4].

The difference gives asynchronous circuits inherent properties that can be exploited to advantage in the areas listed and motivated below. Further its having the following advantages.

- 1. Lower power consumption, due to fine-grain clock gating and zero standby power consumption [11]

- High operating speed, since operating speed is determined by actual local latencies rather than global worst-case latency. [14]

[39]

- Less emission of electro-magnetic noise, the local clocks tend to tick at random points in time. [39] [42]

- 4. Robustness towards variations in supply voltage, temperature, and fabrication process parameters, since timing based on matched delay and it can be insensitive to circuit and wire delays[40].

- 5. Better composability and modularity, because of the simple handshake interfaces and the local timing [36].

- No clock distribution and clock skew problems, since there is no global signal that needs to be distributed with minimal phase skew across the circuit[37].

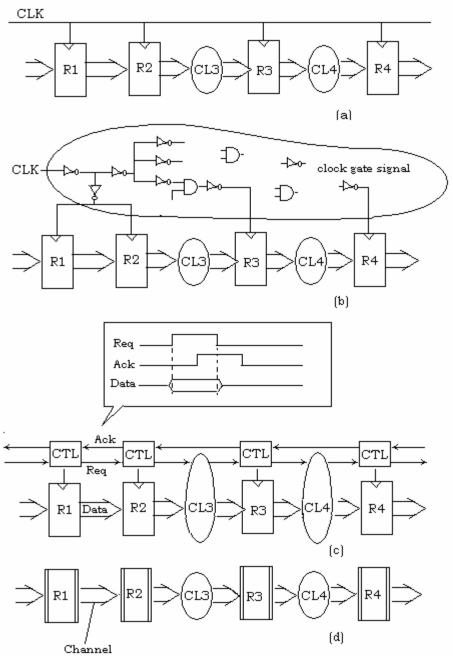

Fig 1.2(a) shows synchronous circuit. For simplicity the figure shows a pipeline, but intended to represent any synchronous circuit. When designing ASICs using hardware description languages and synthesis tools, designers focus mostly on tha data processing and assume the global clock. For example, a designer would express the fact that data clocked into register R3 is a function CL3 of the data clocked into R2 at the previous clock as the following assignment of variable: R3 : = CL3(R2). Figure 1.2(a) represents this high-level view with a universal clock.

When it comes to physical design, reality is different. Today's ASICs use a structure of clock buffers resulting in a large number of(possibly gated) clock signals as shown in Fig. 1.2(b). It is well known that it takes CAD tools and engineering effort to design the clock gating circuitry and to minimize and control the skew between the many different clock signals. In synchronous designs the problem of guaranteeing the two-sided timing constraints-the set up to hold time window around the clock edge-in a world that is dominated by wire delays is not an easy task. The buffer-insertion-and-resynthesis process that is used in current commercial CAD tools may not converge and, even if it does, it relies on delay models that are often questionable accuracy.

Fig. 1.2 (a) A synchronous circuit, (b) a synchronous circuit with clock drivers and clock gating, (c) an equivalent asynchronous circuit, and (d) an abstract data-flow view of the asynchronous circuit.

Asynchronous design provides an alternative solution to this limitation. In an asynchronous circuit the clock signal is replaced by some form of handshaking between neighbouring registers [4]; for example the simple request-acknowledge based handshake protocol shown in Fig. 1.2(c). In the second chapter we look an alternative handshake protocols and data encoding, but before departing into those implementation details it is useful to take a more abstract view as illustrated in figure 1.2(d).

- The data and handshake signals connecting one register to the next in Fig. 1.2(c) as a "handshake channel" or "link,"

- The data stored in the registers as tokens tagged with data values ( that may be changed along the way as tokens flow through combinational circuits), and

- The combinational circuits as being transparent to the handshaking between registers; a combinatorial circuit simply absorbs a token on each of its input links, performs its computation, and then emits a token on each of its output links.

Viewed this way, an asynchronous circuit is simply a static data-flow structure. Intuitively, correct operation requires that data token flowing in the circuit do not disappear, that one token does not overtake another, and that new tokens do not appear out of nowhere. A simple rule that can ensure this is the following [36]:

A register may input and store a new data token from its predecessor if its successor has input and stored the data token that the register was previously holding. [ The states of the predecessor and successor registers are signaled by the incoming request and acknowledge signals respectively.] Following this rule data is copied from one register to the next along the path through the circuit. In this process subsequent registers will often be holding copies of the same data value but the old duplicate data values will later be overwritten by new data values in a carefully ordered manner, and a handshake cycle on a link will always enclose the transfer of exactly one data-token. Understanding this "token flow game" crucial to the design of efficient circuits, and we will address these issues, extending the token-flow view to cover structures other than pipelines.

An important thing is that the "handshake-channel and data-token view" represents a very useful abstraction that is equivalent to the register transfer level (RTL) used in the design of synchronous circuits [47]. This data-flow abstraction, as we call it, separates the structure and function of the circuit from the implementation details of its components.

Another important consideration is that it is the handshaking between the registers that controls the flow of tokens, whereas the combinatorial circuit blocks must be fully transparent to this handshaking. Ensuring this transparency is not always trivial; it takes more than a traditional combinational circuit, so we will use the term "function block' to denote a combinational circuit whose input and output ports are handshake-channels or links. The synchronous circuit shown in Fig. 1.2(b) is "controlled" by clock pulses that are in phase with a periodic clock signal, whereas the asynchronous circuit in Fig. 1.2(c) is controlled by locally derived clock pulses are generated where and when needed. This tends to randomize the clock pulses over time, and is likely to result in less electromagnetic emission and a smoother supply current without the large di/dt spikes that characterize a synchronous circuit.

we consider an approach of asynchronous ALU design to reduce the transistors count, power consumption and delay. We propose the application of delay insensitive dual rail logic and bundled data bounded delay model in our design. Since the proposed approach will have the all advantages of asynchronous circuit earlier discussed will be very useful in power consumption and occupying less space with average delay in battery operated devices.

#### 1.2 Brief Overview of our Work

In the present work, we consider an approach of asynchronous ALU design to reduce the transistors count, power consumption and delay. We propose the application of delay insensitive dual rail logic and bundled data bounded delay model in our design. To achieve higher performance and lower power operation, we design the circuits with CMOS domino logic. The use of domino logic reduces the transistor count, parasitic capacitances and ensures glitch-free circuit. The Muller C-element and Four-Phase Dual Rail Protocol are used for the completion detection.

This design uses conventional CMOS domino logic since its implementation supports the glitch free circuit and the capacitance of its output node is separating by interval and load capacitance [2]. Also it ensures the lower power consumption by reducing the parasitic capacitances and transistor count. Asynchronous circuits are fundamentally different from the synchronous counterpart and use handshaking among components to perform the necessary synchronization, communication and sequencing of operations. The handshaking implementation may follow any one of these protocols, 4phase bundled data, 2 –phase bundled data or 4-phase dual rail. In all protocols, Muller pipeline is used. The 4-phase dual rail has designed to combine encoding of data and request. We apply it in our circuit, because 4- phase dual rail protocol provides reliable synchronization, lower power consumption with simple and faster signal transition than 2-phase model [9].

The asynchronous ALU is implemented with 4-phase dual rail protocol and CMOS domino logic for single bit operation. The 32 bit ALU can be extended on concatenation of the same circuit with 32 blocks. The completion detection circuit detects each operation completion and sends back the necessary acknowledge signal. The power is consumed only at the time operation only, which is unique advantage of our asynchronous design than synchronous using master clock [43].

#### **1.3 Organization of the Thesis**

The design architecture and results are presented in the dissertation in the following five chapters.

- Chapter 1: Motivation and a brief overview of our work is presented.

- Chapter 2: Introduction to asynchronous design methodologies, designing the low power circuits and C-Muller pipelines.

- Chapter 3: We consider our work to design an efficient asynchronous VLSI architecture design of low power ALU with four-phase dual rail protocol.

- Chapter 4: In this chapter, simulation results through SPICE design tool are reported and compared with other published works.

- Chapter 5: Summary of the work and future scope to extend our work is given.

### Chapter 2

## CMOS logics and Asynchronous Design Methodologies

In this chapter, we are discussing about the fundamentals of CMOS logic design styles namely static and dynamic CMOS design followed by the Asynchronous design methodologies available in detail. Our proposed Asynchronous ALU circuit is following the dynamic domino CMOS logic and 4-phase dual-rail protocol among the different logic styles available. Also in the final part of this section, the base of any asynchronous circuit C-Muller element and its pipeline, the 4-phase dual rail pipeline follows that are discussed.

#### 2.1 Static CMOS

Although static CMOS logic is widely used for its high noise margins and relative ease of design, it is limited at running extremely high clock speeds. For applications requiring the fasted circuit speeds possible, dynamic CMOS logic has numerous advantages over static CMOS including not only higher speeds but also significantly reduced surface area. The advantages do not come without a cost however. Due to the nature of dynamic CMOS logic, undesired effects can occur within the circuit unless extra effort is put into the engineering design. Understanding the basic principles of Dynamic CMOS logic begins with first an understanding of the basic properties of MOSFET devices as well as the characteristics of static and pseudo-NMOS logic [23].

Due to the internal structure of MOSFET devices, an effective capacitance can be associated across all possible terminal

combinations of the gate, drain, source, and body. When charge is applied to these capacitances, the corresponding terminal voltage rises, and when the charge is removed, the terminal voltage decays just as if the terminal were modeled as a capacitor. Modeling the MOSFET terminals as capacitors is useful to explain the voltages and currents associated with the MOSFETs in a complex circuit. MOSFETs are characterized by the three modes of operation: Cutoff, Linear, and Saturated [27].

However, since current flows through the device for both the linear and saturated modes, it is useful to consider the MOSFET as ON in this conducting state or OFF when no current flows. For an NMOS, or n-channeled MOSFET, the device is only ON when the gate to source voltage, Vsg, is greater than the device threshold voltage, V<sub>T</sub>.

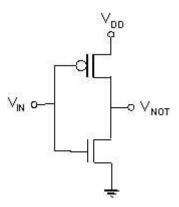

For a PMOS, or p-channeled MOSFET, the device is only ON when the source to gate voltage, VsG, is greater than the negative device threshold voltage, - VT. For the purposes of this analysis, the input to the gates of the MOSFETs will either be high or low, VDD or GND, respectively. Therefore, if the PMOS source is connected to VDD, the PMOS will only be ON if the gate voltage is low. Likewise, if the NMOS source is connected to GND, the NMOS will only be ON when the gate voltage is high. Observing how the NMOS and PMOS work in conjunction to form the CMOS inverter circuit, Fig. 2.1, is a useful example to understand how these devices might be used in more complex circuitry.

Fig.2.1 CMOS inverter circuit

When the input is low, the PMOS turns ON and the NMOS turns OFF. The output is simultaneously cut off from GND and charged high due to the 'pull-up' path to VDD through the PMOS. Conversely, when the input is high, the PMOS turns OFF and the NMOS turns ON resulting in a 'pull-down' path to GND while the connection to VDD is cutoff. When utilized in this fashion, the NMOS device is considered a 'pull-down' device, and the PMOS is considered a 'pull-up' device [23].

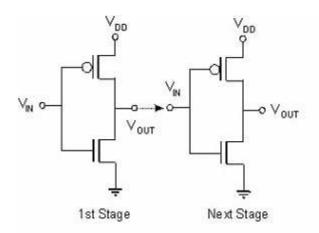

Fig.2.2 CMOS inverter Circuits in stages

By connecting the output of this circuit to the input of similar logic, the voltage and current characteristics can be determined by considering the capacitive effects associated with the input of this second stage. As shown in Fig. 2.2, a low input to the CMOS inverter charges the input of the second stage high due to the current from VDD flowing out of the first-stage PMOS. A high input to the inverter removes any charge at the input of the second stage through the NMOS of the first stage.

Fig.2.3 CMOS tristate inverter

The capacitive effects of the MOSFET terminals can also be used to store charge across the terminals temporarily. Consider the tristate inverter in Fig. 2.3. When VPEN and VNEN are low (note VPEN is inverted), Vout is disconnected from both VDD and GND leaving Vout floating. In this 'Z-state,' Vout must retain its previous voltage level. Ideally, any charge associated with the Z-state would remain across the terminals of the MOSFET indefinitely; however, due to parasitic charge leakage, an originally high voltage in the output Z-state will decay to zero with time. If the system were run at speeds higher than the time needed for the leakage current to cause a logic error, the characteristics of the output Z-state can be utilized to vastly increase circuit speeds. This is the essence of dynamic CMOS.

Although there are many positive reasons for using static CMOS logic, there are also numerous drawbacks. Static devices inherently have more components and clocked transistors than dynamic devices. A full latch for example in the traditional static configuration may require 66 transistors [21]. A dynamic configuration performing the same function may require only 36 transistors [21]. The number of transistors used to construct a flipflop is also significantly reduced by using dynamic logic as opposed to fully static logic. Reducing the total number of transistors not only allows the overall device to be significantly smaller, but also reduces the power requirements of the system [20].

Most of the disadvantages of using static CMOS, however, are associated with the use of PMOS. Caused in part because hole mobilities are significantly slower than electron mobilities, PMOS devices must be much larger than NMOS devices for the two to have the same ability to transport a fixed amount of charge during a fixed time interval. The larger surface area needed to form a PMOS device than an NMOS device is not only a detriment to the overall chip size, but also increases the capacitance associated to the PMOS device. The larger capacitance and slower carrier mobilities associated with PMOS cause a greater time delay for the PMOS to charge up the capacitor associated with the next logic stage. This increased time delay becomes a bottleneck when trying to design faster circuits. In standard CMOS logic, one PMOS device will always compliment an NMOS device. Altering this logic so that fewer PMOS devices are needed will vastly improve circuit performance.

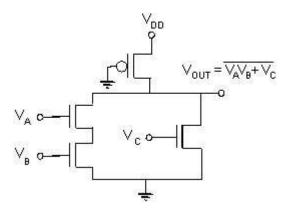

One method to decrease the number of PMOS devices in the circuit is to use what is called pseudo-NMOS logic. Instead of using one PMOS for every NMOS device, pseudo-NMOS logic utilizes only one PMOS device as a load to all other NMOS logic as shown in Fig.2.4.

Fig. 2.4 pseudo- NMOS logic

Since the voltage at the gate of the PMOS is always GND, the PMOS device is always ON. The output then of the pseudo-NMOS circuit is selectively discharged to GND through the NMOS logic block. Since the NMOS devices in the ON state forms a pull-down path to GND and the PMOS device is always ON, there will be times during circuit operation where a path is formed from VDD to GND. The pseudo-NMOS logic must be ratio sensitive so as to minimize the loss in power dissipation. In other words, the PMOS must be 'weak' or small so as to have less capacitance associated with the device. In this

configuration, the charge will be pulled up much more slowly by the PMOS than it can be discharged through the NMOS devices. In this way, a pull-down path to ground through the NMOS logic block should easily pull down the output. When no pull-down path to ground exists via the NMOS logic, the output is then pulled high through the PMOS load. Although pseudo-NMOS logic can be utilized to reduce the number of PMOS components in the system, not only does the static power dissipation serve as a detriment, but the speed of the circuit is limited by the time necessary for the weak PMOS to charge up the output node [27].

#### 2.2 Dynamic CMOS

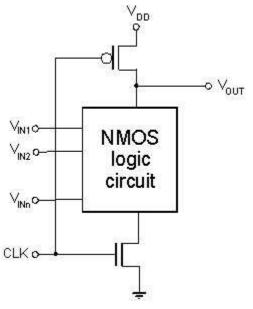

An alternative logic that reduces the number of PMOS devices while also solving most of the problems associated with pseudo-NMOS logic is dynamic CMOS. The basic structure of dynamic CMOS logic is shown in Fig. 2.5.

Fig. 2.5 Basic Structure of dynamic CMOS logic.

When the clock is low, the NMOS device is cut off while the PMOS is turned ON. This has the effect of disconnecting the output node from ground while simultaneously connecting the node to VDD. Since the input to the next stage is charged up through the PMOS transistor when the clock is low, this phase of the clock is known as the 'precharge' phase. When the clock is high however, the PMOS is cutoff and the bottom NMOS is turned ON, thereby disconnecting the output node from VDD and providing a possible pull-down path to ground through the bottom NMOS transistor. This part of the clock cycle is known as the 'evaluation' phase, and so the bottom NMOS is called the 'evaluation NMOS.' When the clock is in the evaluation phase, the output node will either be maintained at its previous logic level or discharged to GND. In other words, the output node may be selectively discharged through the NMOS logic structure depending upon whether or not a path to GND is formed due to inputs of the NMOS logic block [23]. If a path to ground is not formed during the evaluation phase, the output node will maintain its previous voltage level since no path exists from the output to VDD or GND for the charge to flow away.

As an example, the Pseudo-NMOS circuit shown in Fig. 2.4 can be made into a dynamic logic structure by adding an evaluation NMOS and connecting it to a clock with the PMOS as shown in Fig. 2.6.

Fig. 2.6 example for dynamic CMOS logic

During the precharge phase, the output is pulled high through the PMOS in the ON state. When the clock goes high in the evaluation stage, the output will be data-dependent. If the input signals A AND B are high OR if C is high, a path to ground through the evaluation NMOS will be formed and the output node will be pulled low. If these conditions are not met, then the output will remain high. Regardless of the resultant logic level of the output node at the end of the evaluation phase, the output node will be pulled high again when the clock goes low for the next precharge phase.

There are many advantages of using dynamic CMOS logic over static CMOS logic or Pseudo NMOS logic. The elimination of the complimentary PMOS transistors significantly reduces the transistor count needed to implement the various logic functions not only because the number of transistors is nearly half, but because the physical size of the PMOS transistors tend to be much larger than the size of an NMOS transistor. The switching speeds are also increased using the dynamic logic configuration since the speed bottleneck caused by the lengthier time the PMOS requires to pull-up the output node is eliminated. Since this node is already precharged high through the PMOS during the precharge phase, the output node needs only to be selectively discharged during the evaluation phase. Discharging the output node through the NMOS devices is significantly faster than the time needed to charge up the output node through the PMOS device [22].

Although increased speed over static or Pseudo NMOS logic is a significant achievement in the dynamic logic, there are several potential problems with the implementation of this design that need to be considered. Since the basic dynamic CMOS logic configuration causes the output node to be disconnected from VDD during the evaluation phase, even if the output is also disconnected from GND, the charge of the output node will begin to diminish due to the non-ideal effects of the system. Parasitic capacitances, for example, may leak the charge away from the output node and eventually cause a logic error [8]. Since there is, however, a finite time needed for the charge to erroneously escape, the use of faster the clock speeds will eliminate this kind of error. This implies however, that there is a minimum clock speed at which dynamic CMOS logic structures may be operated. It also eliminates the possibility to idle the basic dynamic CMOS logic circuit.

These drawbacks however, are not without a solution. In many cases, the specifications of the system do not require the circuit to ever idle or run at relatively slow clock speeds. In these cases, the fastest clock speed is desired, making the minimum clock speed of the dynamic

Fig. 2.7 Dynamic CMOS logic structure for minimum clock speed

logic configuration a non-issue [13]. In other cases, some of the static benefits can be introduced to the dynamic logic configuration with the addition of a 'weak'-PMOS device added between the output node and VDD as shown in Fig. 2.7. If the gate is connected to GND, this PMOS device will always be turned ON. Then, even in the evaluation phase, the output node will be connected in some capacity to VDD. This PMOS, the 'keeper,' has the effect of maintaining the output node charge even at slower clock speeds. The keeper transistor is designed to be weak enough so that a path to GND through the NMOS logic block during the evaluation phase will significantly overpower the effects of the keeper PMOS and easily pull the output node to GND. Although this configuration has advantages, it does introduce another PMOS device into each stage and also causes excess power dissipation due to possibility of the connection from VDD to GND through the NMOS devices and the PMOS keeper. When such a circumstance occurs, the NMOS and PMOS must 'fight' each other to pull-up or pull-down the output through VDD or GND respectively, and power is lost. For high-performance circuits, an alternative is clearly needed.

Fig. 2.8 Latching of weak PMOS in dynamic logic

The use of a keeper PMOS in dynamic logic could be further improved by connecting the gate of the keeper not to GND, but to the output node of the inverter stage as shown in Fig. 2.8. The keeper would now function as a latch cutting off whenever the output of the inverter is high. In this way, power dissipation is significantly reduced whenever a pull-down path to GND has been formed in the NMOS logic block since this would make the input to the inverter low and thus the output of the inverter high. When the output of the inverter is low however, as would be the case if no pull-down path to ground was formed in the NMOS logic block, the keeper PMOS would turn on and maintain the output high charge on the precharge node even at reduced clock speeds or an idle [17].

Other characteristics of dynamic CMOS logic that must be taken into consideration when designing dynamic logic are the problems that can occur when cascading the dynamic logic blocks [25]. Due to the finite pull down time of the NMOS logic block, during the very first portion of the evaluation phase, the output will always register an output high state for at least a brief moment in time before the output charge can be removed via the pull-down path to GND. This is considered a 'racing' problem since the logic is evaluated correctly only when the time to pull down the output node is faster than the time needed for the briefly high output caused by the precharge phase to propagate as an erroneous logic signal to the next stage. Since the output node of one dynamic CMOS logic block is connected to an input of the next dynamic CMOS stage, an output high state however brief could complete a pull-down path to GND in the following stage and erroneously cause a discharge in the output of this next stage. Since the charge on the output node cannot be recovered until the next precharge phase, the logic error would remain and propagate through the system. Dynamic CMOS logic blocks should therefore not be directly cascaded. Note that care must also be taken to insure that the input logic signals to the NMOS logic block are correct and stable for the complete duration of the evaluation stage or a similar logic error could occur [17].

#### 2.2.1 Domino Logic

The errors occurring due to cascaded dynamic logic blocks can be overcome by adding an inverter stage between the output of one stage and the input of another as in Fig. 2.9.

Fig. 2. 9 Dynamic CMOS domino logic structure

This inverter then would start out low at the very beginning of the evaluation phase. The output low state of the inverter would cutoff the NMOS logic gates in the next stage preventing any erroneous pulldown path. If a pull-down path is formed by the NMOS logic block of the first stage, the output of the inverter buffer would conditionally charge from low to high. Only if the inputs to the first stage NMOS logic block warrant a discharge of the output node would the output inverter make the low to high transition. When the output of this inverter buffer goes high, the following stage of NMOS logic would conditionally form a pull-down path to ground. In this way, the addition of the inverter buffer eliminates any logic errors caused by the finite pull-down time of the NMOS logic block. This kind of design is referred to as Domino Logic since the pull-down of one stage can conditionally cause the pull-down of succeeding stages and so on like falling dominoes [26].

The number of Domino logic stages that may be cascaded is limited only by the sum of the total pull-down times in all cascaded logic blocks, which must be contained within the evaluation clock phase. Drawbacks to this design are of course the addition of two additional components to each dynamic block. Extra design consideration must also be observed when using dynamic CMOS logic blocks in conjunction with static CMOS logic blocks. Since the final output to the Domino logic blocks is the inverted form of the original output due to the additional inverter buffer stage, only non-inverting logic may be used between the output and input of dynamic logic. That is, since the inverter must make only one conditional state change from logic low to high (not high to low) during the evaluation phase only an even number of static logic blocks may be used in between dynamic logic blocks [24].

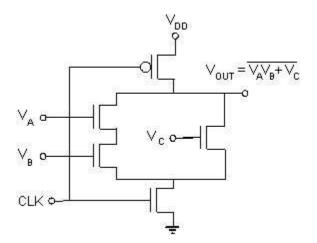

#### 2.2.2 NORA Logic

An alternative to Domino Logic is NORA or Domino-Zipper Logic. NORA stands for 'no-race,' indicating another method to eliminate the 'racing' problem of directly cascaded dynamic logic blocks. Fig. 2.10 depicts the basic structure of NORA logic which is characterized by alternating the MOSFETs in the logic block from PMOS to NMOS logic gates and so on. Note that the function of the clocked n- and p- FETs in the PMOS logic stage are reversed compared to the NMOS logic stage [23].

Fig. 2.10 Dynamic CMOS NORA logic structure

Although this structure eliminates the cascading problem, the excess use of PMOS in forming the logic gates reduces the maximum clocking speed and increases the surface area of the system. For this reason, it is preferable to use only the NMOS for the logic gates and leave the PMOS as precharge elements. Further design considerations for NORA logic are needed when combining the dynamic NORA blocks with static blocks. As observed with Domino Logic, the output may only be allowed to change from low to high once during the evaluation phase of the NMOS logic and visa-versa for the PMOS, so only an even number of static blocks may be used in between two of the dynamic blocks.

Fig. 2.11 clock skew representation

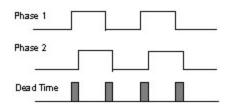

Another significant drawback to this configuration is the use of the two-phase clock. For a circuit operating at high speeds, the clock characteristics become increasingly important. The signals of both clock phases must be delivered at nearly the same instant for the circuit to operate correctly. Routing a one phase clock to the millions of circuit elements such that the delay is minimized is a challenging design issue in and of itself. Routing a second clock phase to a similar quantity of circuit elements such that the delay is minimized compared not only to itself, but to the first clock phase becomes a serious problem. The time delay between the first and second clock phase is known as clock skew. The presence of clock skew in a circuit reduces the maximum operation speed of that circuit, since the logic cannot be correctly evaluated during this delay time [8]. Clock skew, as shown in Fig. 2.11, can be eliminated by using only one clock phase.

### 2.3 Handshake Basics

In Fig 1.2(c) one particular handshake basic protocol has been explained, known as the 4-phase bundled-data protocol also called as return-to-zero handshake protocol [4]. The below sections explain the basic principles for designing the handshaking (asynchronous) circuits.

### 2.3.1 Principles of Bundled-data protocols

In bundled data protocols the data signals use normal Boolean levels to encode information and separate request and acknowledge wires are bundled with the data signals. In Fig. 2.12, a bundled data channel is shown in which data is bundled with request and acknowledge wires.

Fig.2.12 A bundled-data channel

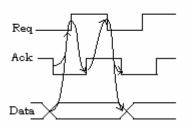

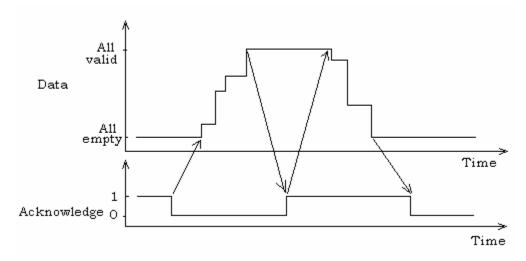

The 4-phase protocol is illustrated in Fig. 2.13. Here the request and acknowledge wires use normal Boolean levels to encode information, and the term 4-phase refers to the number of communication actions [4]:

Fig.2.13 A 4-phase bundled-data protocol

(1) the sender issues/sends Data and sets Req High,

(2) the receiver absorbs/receives the Data and sets Ack High,

(3) the sender responds by taking Req Low and

(4) the receiver acknowledges this by taking Ack Low.

The sender may initiate the next communication cycle once all above 4 phases are over.

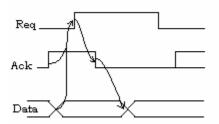

Fig.2.14 A 2-phase bundled data protocol.

The 2-phase bundled data protocol is shown in Fig. 2.14. The information on the request and acknowledge wires is now encoded as signal transitions on the wires and there is no difference between a 0 to 1 and a 1 to 0 transition, they both represent a "signal event". Ideally the 2-phase bundled-data protocol should lead to faster circuits than the 4-phase bundled-data protocol, but often the implementation of circuits responding to events is complex [54].

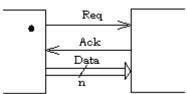

The term 'bundled data' hints at the timing relationship between the data signals, whereas the term 'single rail' hints at the use of one wire to carry one bit of data [58]. The protocols introduced above all assume that the sender is the activity party that initiates the data transfer over the channel. This is known as a push channel. The opposite, the receiver asking for new data, is also possible and is called a pull channel. In this case the directions of the request and acknowledge signals are reversed, and the validity of the data is indicated in the acknowledge signal going from the sender to receiver. In the abstract diagram, the active end of the channel is marked with a dot.

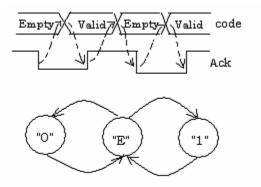

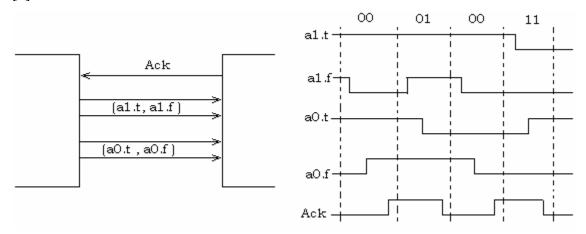

#### 2.3.2 4-phase dual-rail protocol

The 4-phase dual rail channel is shown in Fig.2.15.In this handshake protocol, it encodes the request signal into the data signal by using 2 wires per bit of information that is to be communicated. This 4-phase dual-rail protocol uses two request wires per bit of information a;

Fig.2.15 The 4-phase dual rail channel