#### **Behavioral Modeling using Verilog-A**

Dr. Vishal Saxena

Electrical and Computer Engineering Department Boise State University, Boise, ID

# Verilog-A

- VerilogA is the standard behavioral modeling language in Cadence Spectre environment

- Allows to simulate complex systems without transistor-level implementation

- Some of the functionality is similar to Matlab Simulink but more circuit oriented

- Can interchange VerilogA, Transistor-level and parasitic extracted circuit views for system-level simulation using the Hierarchy editor

- Powerful method for complex design verification

- Language construct is similar to digital Verilog RTL, but not quite the same

- Easy to pick up, but mastery comes with experience

- Can be used to model novel devices not covered by bsim

# Verilog-AMS

- Verilog-AMS is an extension of Verilog-A to include digital Verilog cosimulation functionality

- Works with the ams simulator instead of spectre

- Need to clearly define interfaces between analog and digital circuits

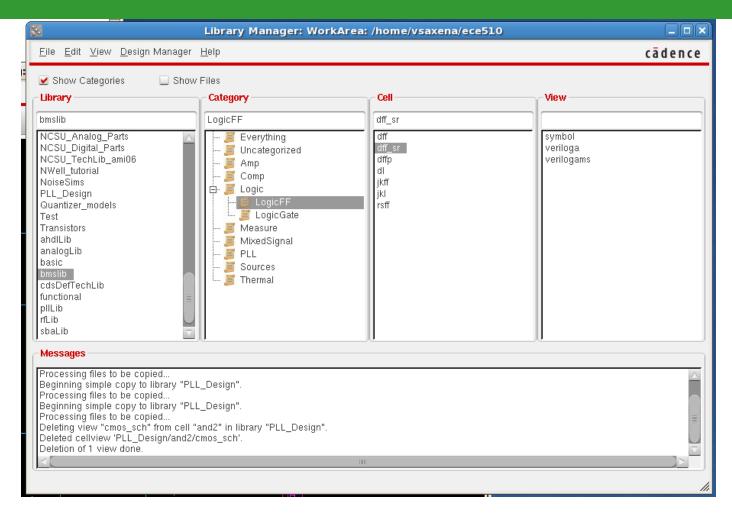

- □ bmslib and ahdlLib libs have *verilogams* views along with *veriloga*

- □ Don't worry about it for now....

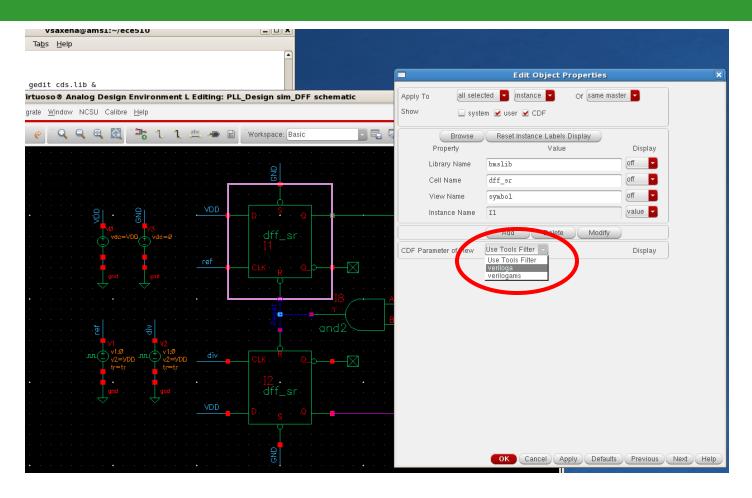

## Using Behavioral Cells

## Setting cell parameters

- Select: CDF parameter of View → veriloga

- Connect the Set pin to GND to disable it, Reset is asserted when high.

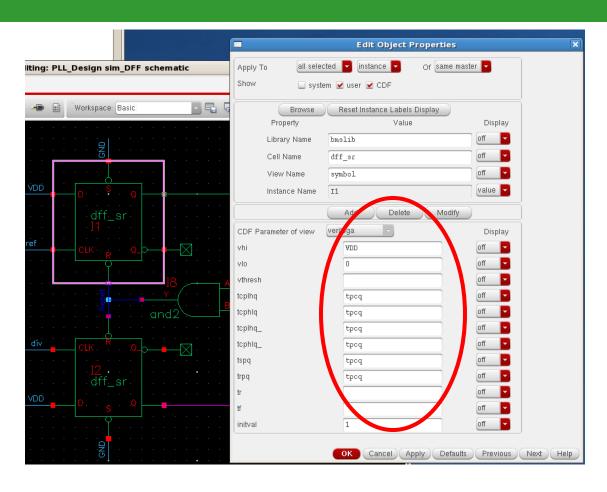

## Setting cell parameters

- Set desired model parameters such as voltages and delays

- $\Box$  Preferably use variables controlled from the ADE-L window (e.g.  $t_{pcq}$  here)

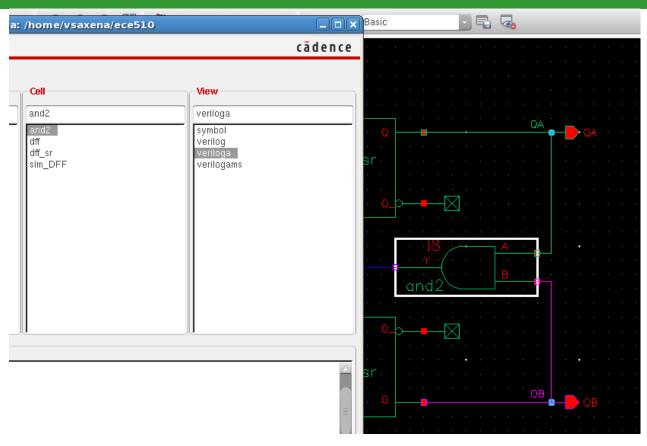

# Logic Cells

- $\square$  Make a local copy of the *bmslib*  $\rightarrow$  *and2 cell*

- Delete the cmos\_sch view as it interferes with the simulation

- Could also use cells from the ahdlLib library

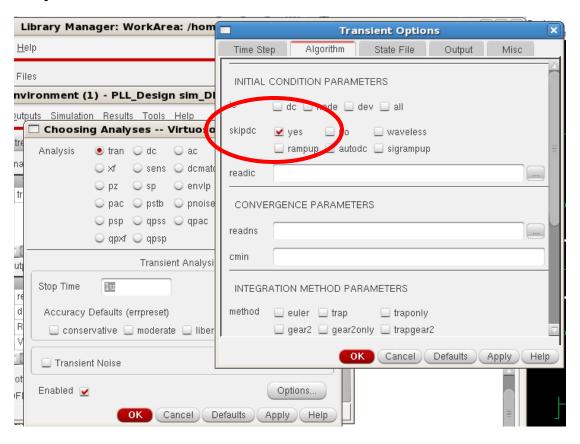

## Convergence Hints

- Since verilog-A models are idealized models they can cause convergence problems

- In a transient sim use the **skipdc** option if DC operating point convergence is not achieved by the simulator

#### Convergence Hints contd.

- Use initial conditions to help with convergence

- ADE L → Simulation → Convergence Aids → Initial Condition

- Can relax tolerances in the simulator options

- ADE L → Simulation → Options → Analog

- Use common-sense when using idealized elements and models...

- Turn on Spectre debug mode to help fix the problem

- Look into the convergence related help in the Spectre references (listed later)

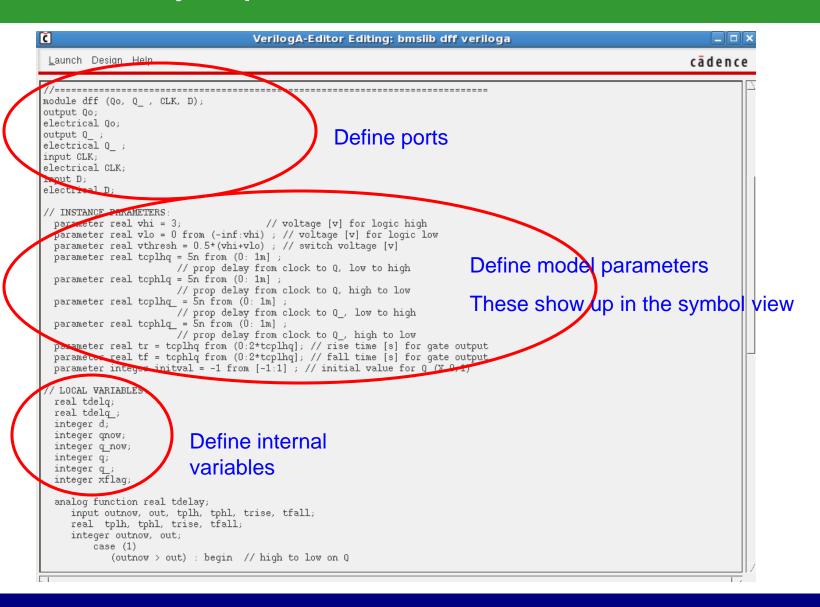

#### **Dff Code Synopsis**

## Dff Code Synopsis contd.

```

(outnow == out) :if (tdelay < 0.05*tr) tdelay = 0; // no change

endcase

endfunction

analog begin

@ (initial step) begin

if (thresh > vhi || vthresh < vlo) begin

$display

("%M: Inconsistent input threshold specification w/logic family.\n");

end

case (initval)

the model functionality

Initial step

1: begin q = 1; q = 0; end

0: begin q = 0; q = 1; end

-1: begin q = (V(\overline{D}) > vthresh); q = (V(\overline{D}) <= vthresh) end

default begin q = (V(D) > vthresh); q = (V(D) <= vth/esh); end

rflag = 1;

// initial time, input data is allowed

end

@ (cross(*(CLK) - vthresh, +1) ) xflaq = 1;

if ( lag) begin

xflaq = 0;

d = V(D) > vthresh;

qnow = q;

q now = q;

end

if (d) begin

Behavior

q = 0;

definitions

tdelq = tdelay(qnow, q, tcplhq, tcphlq, tr, tf);

tdelq = tdelay(q now, q , tcplhq , tcphlq , tr, tf

ir (!d) begin

q = 0:

cohlq, tr, tf);

cdelq = tdelay(q now, q , tcplhq , tcphiq , tr, tf);

♥(Qo) <+ transition( q ? vhi : vlo, tdelq, tr, tf);</pre>

Output transitions

V(Q )<+ transition( q ? vhi : vlo, tdelq , tr, tf);</pre>

endmodule

```

Main analog block defining

## How to get started using Verilog-A modeling

- Start with the available behavioral blocks with Spectre

- Don't create a fresh model from scratch unless you really need it

- Modify the existing ones

- Don't get bogged down with the code complexity of these professionally coded models

- Your custom behavioral codes can be really simple

- Once you start using verilogA, it will get easier.....

- Great skill to have for an analog designer!

- All circuit design these days is at system level

#### References and Online Resources

- Spectre reference libraries with behavioral cells

- bmslib and ahdlLib

- Must read: Cadence Whitepaper, "Creating Analog Behavioral Models"

- http://lumerink.com/courses/ECE614/Handouts/CDN\_Creating\_Analog\_Behavioral\_ Models.pdf

- Designers Guide Community Site

- http://www.designers-guide.org/

- Books

- *The Designer's Guide to Verilog-AMS* by Kenneth S. Kundert & Olaf Zinke, 2004.

- The Designer's Guide to SPICE and Spectre by Kenneth S. Kundert, 1995.

- ⊐ AMS CAD Wiki

- http://lumerink.com/cadwiki/doku.php

Happy Circuit Modeling with VerilogA!

#### References

- 1. Ken Kundert, "The Designer's Guide to Spice & Spectre," Boston, Kluwer, 1995.

- 2. Ken Kundert, "The Designer's Guide to Verilog-AMS, 2004.

- 3. Cadence Whitepaper: <u>Creating Analog Behavioral Models</u>

- 4. Designers Guide Community. [Online] <a href="http://www.designers-guide.org/">http://www.designers-guide.org/</a>

- 5. Virtuoso Spectre DesignerReference [Online]

- 6. http://lumerink.com\courses\ECE614\Handouts\Spectre Designer Reference.pdf

- 7. Virtuoso Spectre Circuit Simulator RF Analysis User Guide [Online]

- 8. <a href="http://www.seas.gwu.edu/~vlsi/ece218/SPRING/reference/manual\_cadence\_spectreRF.pdf">http://www.seas.gwu.edu/~vlsi/ece218/SPRING/reference/manual\_cadence\_spectreRF.pdf</a>

- 9. Information on linking Matlab and Spectre in Linux environment. [Online] <a href="http://www.lumerink.com/courses/ECE697A/docs/Cadence+Spectre+Matlab+Toolbox.pdf">http://www.lumerink.com/courses/ECE697A/docs/Cadence+Spectre+Matlab+Toolbox.pdf</a>

- 1. Verilog-AMS Language Reference Manual. [Online] <a href="http://www.eda.org/verilog-ams/htmlpages/lit.html">http://www.eda.org/verilog-ams/htmlpages/lit.html</a>