# BEOL Interconnect Innovations for Improving Performance

# Paul Besser, PhD

Formerly Senior Technology Director at Lam Research Currently Director of Emerging Technologies at ARM

### Acknowledgements

- Lam Research

- Hui-Jung Wu, Justin Jiang, Kaushik Chattopadhyay, Lee Brogan, Natalia Doubina, Nagraj Shankar, Cheng-Kai Li, and Larry Zhao

- imec

- Houman Zahedmanesh, Kristof Croes, Ivan Ciofi

- GLOBALFOUNDRIES

- Todd Ryan

- ARM

- Saurabh Sinha, Brian Cline, Greg Yeric

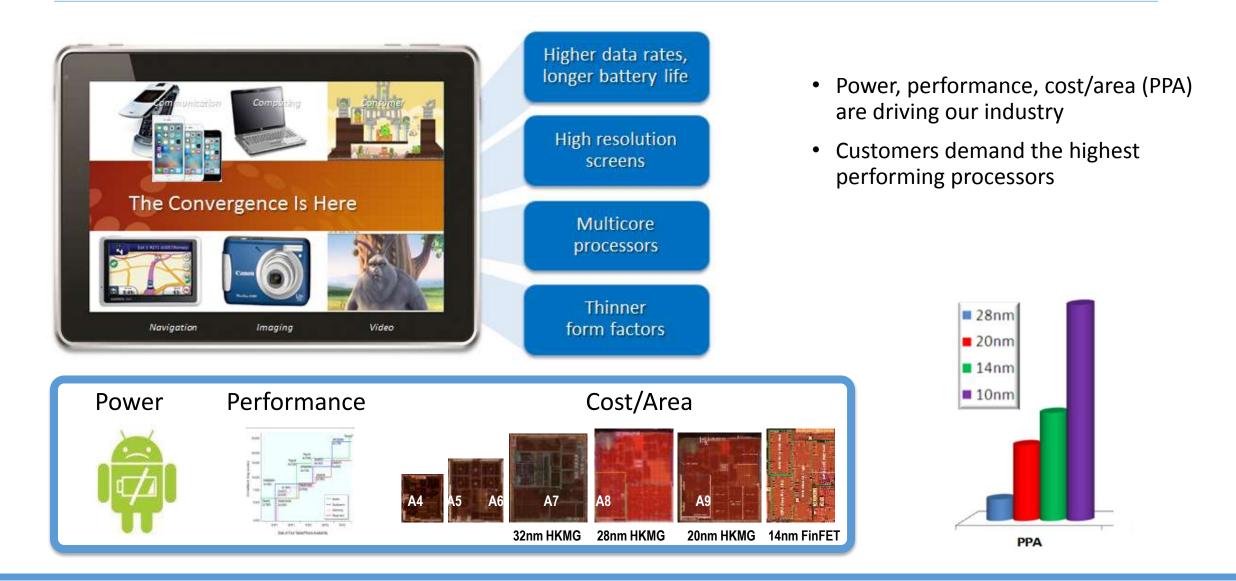

## Market Needs Drive Requirements and Technology Innovations

3

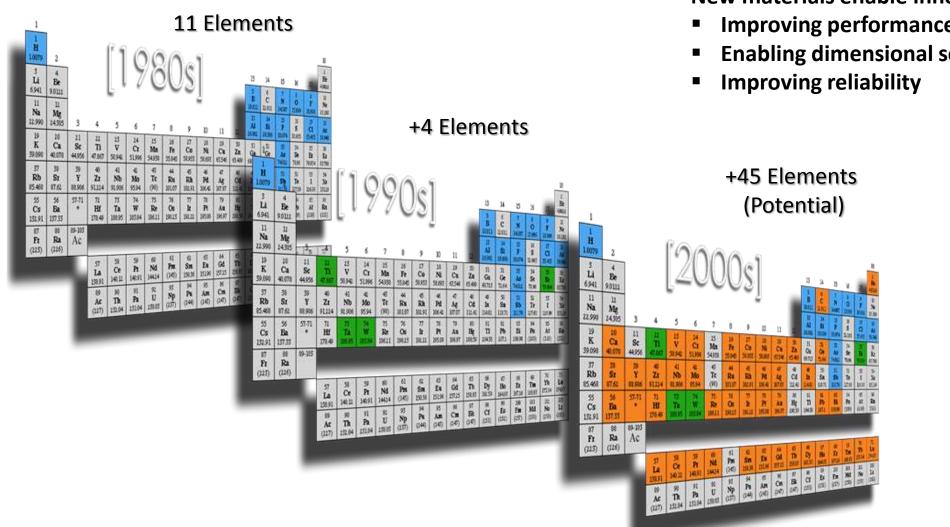

#### Innovations in Silicon Manufacturing

New materials enable innovation by

Improving performance,

4

Enabling dimensional scaling, and

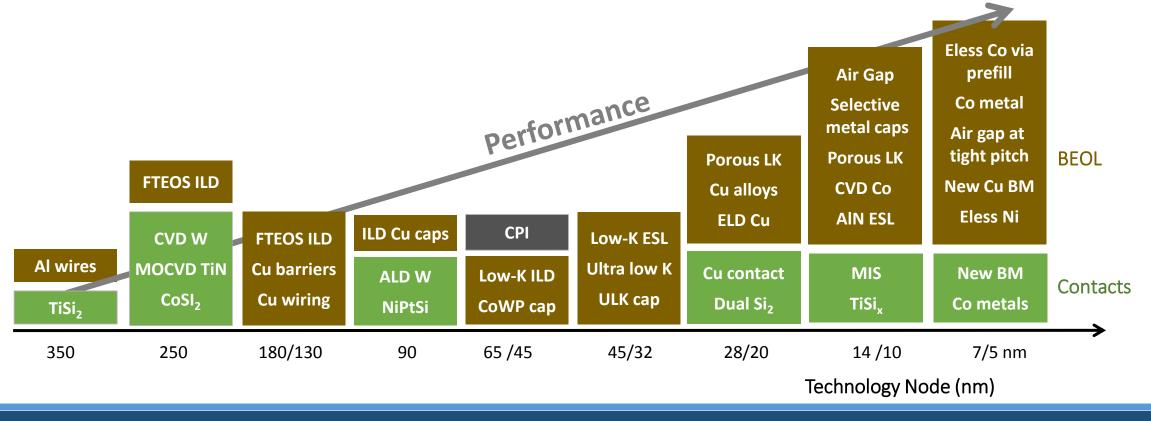

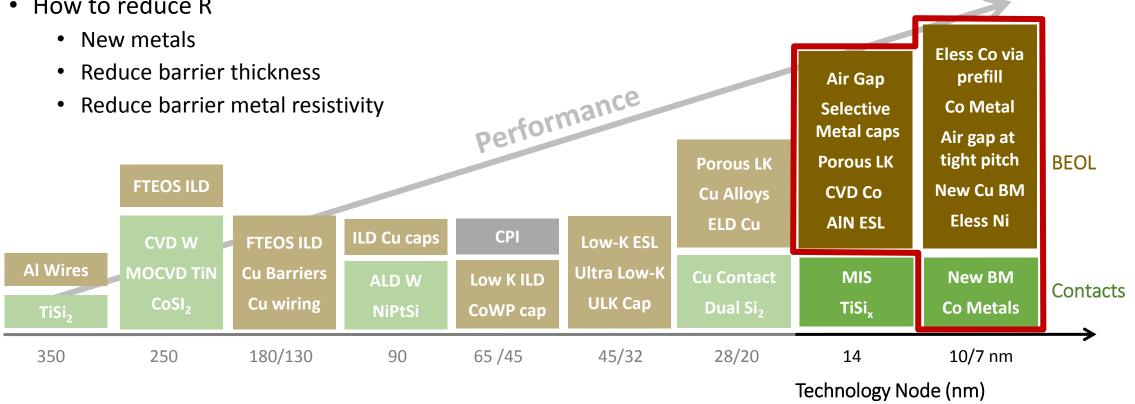

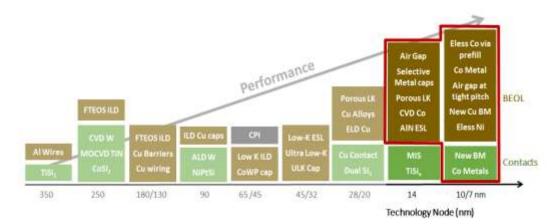

### MOL and BEOL Materials Innovations Roadmap

- Improving performance (data access speed, battery life, etc.) is much more than just shrinking the dimensions of the processor

- Novel materials innovations drive contact and BEOL RC improvement (reduction)

- RC Delay ∝ Resistance x Capacitance

### BEOL — How Important Are Resistance and Capacitance?

|           | Technology                                                       |       | 14nm       | 10nm | 7nm  | 5nm  |

|-----------|------------------------------------------------------------------|-------|------------|------|------|------|

|           | R <sub>CONTACT</sub> + EPI,<br>per side                          | Ω-µm  | <b>4</b> 6 | 56   | 67   | 78   |

| BEOL FEOL | R <sub>SPREADING</sub> +<br>R <sub>EXTENSION</sub> ,<br>Per side | Ω-µm  | 51         | 47   | 28   | 25   |

|           | CFEOL                                                            | aF/µm | 750        | 800  | 690  | 750  |

|           | Back end R                                                       | Ω/µm  | 27         | 72   | 173  | 400  |

| BE        | Back end C                                                       | aF/μm | 19.8       | 17.1 | 16.5 | 16.0 |

Greg Yeric, ARM (IEDM 2014)

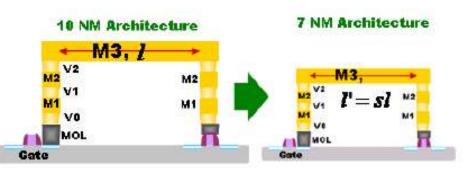

- Back-end interconnect resistance will dominate product performance at 5nm

- BEOL capacitance scaling slows, beyond 10nm

- Key issue at 5 nm: non-scaling parasitics

- Line Rs dominates but at 5 nm

- Via Rs will affect design

- More power is required when design adds a buffer to compensate for R

- Unidirectional patterning has made via Rs more critical since it requires routing changes; standard cell routes must go through multiple vias

6

James Hsueh-Chung Chen (IITC 2014)

## **BEOL RC Reduction Innovations for Future Generations**

- How to reduce C

- New lower K dielectrics, even dielectric replacement

- Air gaps

- Lower K FSL

- How to reduce R

#### RC Delay $\propto$ Resistance x Capacitance

7

# **Capacitance Reduction Opportunities**

### Challenges with Lowering Capacitance

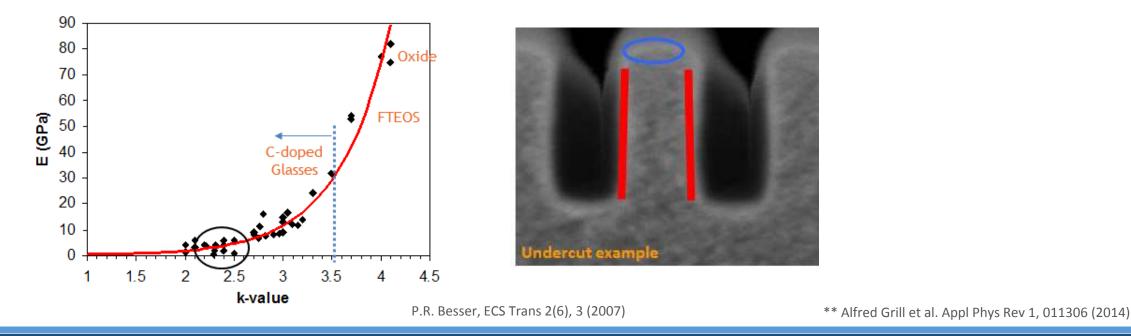

- Capacitance (C) can be reduced by lowering the dielectric constant (k) of the material, but at a cost!

- Dielectric constant is lowered by changing the chemical composition of the dielectric or by introducing porosity (pULK)\*\*

- $\downarrow$  k will  $\downarrow$  elastic modulus (E)  $\rightarrow$  reliability, integration, and packaging issues

- Process-induced damage to trench sidewall and top interface is a major integration challenge\*\*

- Higher K, moisture uptake, increased capacitance, TDDB failure

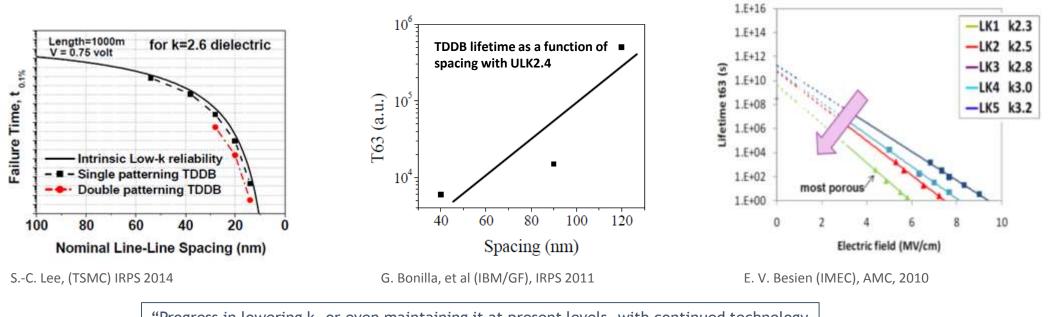

# **TDDB Lifetime and Interconnect Scaling**

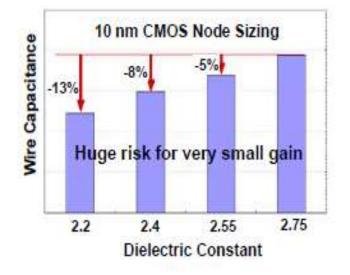

- Capacitance reduction by increasing porosity is high risk with little benefit

- TDDB is a critical hurdle for BEOL scaling, suffering an order of magnitude degradation for each generation @ ULK2.4

- Reducing ULK dielectric constant further degrades dielectric reliability

- Poor LER and misaligned vias can further degrade TDDB

10

#### New Dielectrics Can Help Reduce RC, but Have Challenges

- Porous low k were introduced as part of the 32/28 nm technology

- ↑ porosity ↓ k value, but dielectrics have ↑ process-induced damage and ↓ mechanical strength

- Damage ↑ the effective k and can erase the capacitance benefit

- As a result, at tight pitch interconnects, industry options are \*\*

- Higher K, non-porous, dense LK dielectrics (less susceptible to damage)

- Single precursor formulations (dense LK) with a lower K, and/or

- Low porosity ULK with higher C content

- Industry is spending much resource and has a huge risk exposure for a little gain in C

- Is there a better way?

Rama Divakaruni (IBM) SOI Technology Summit, Shanghai (2013)

\*\* E Todd Ryan et al, IITC-MAM (2015)

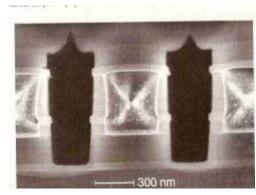

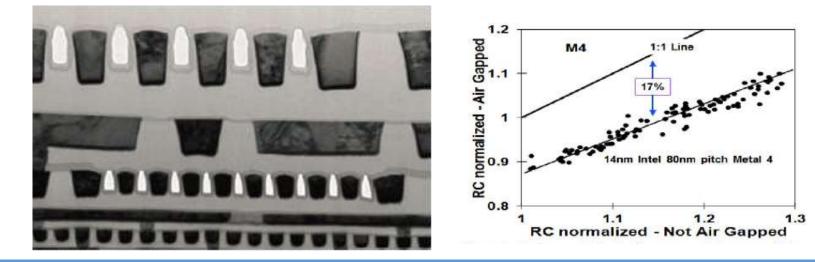

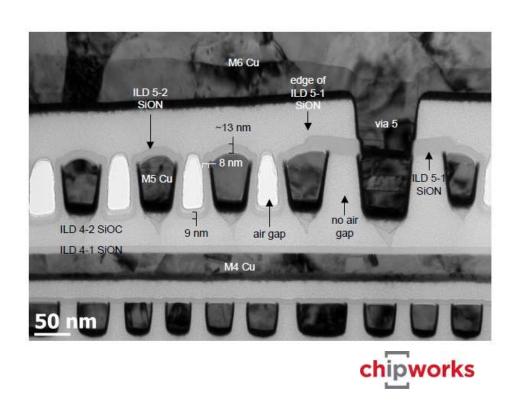

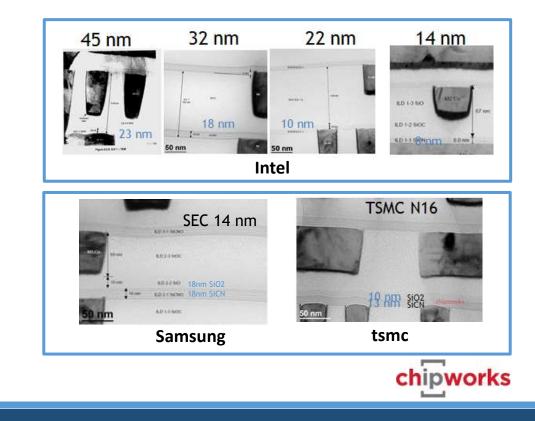

# Technology Elements of Air Gaps (AG) in Integrated Circuits

- Air gap insertion has been demonstrated to reduce capacitance and lower the effective dielectric constant

- Logic had AG >20 years ago: Al technology, pre-unlanded vias

- Memory AG in production for years: NAND BL-BL + WL-WL, DRAM BL-BL

- AG for capacitance reduction reemerging \*\*

- Implemented by Intel 14 nm in performance critical layers

- Two metal levels, with one level without air gap between AG layers

- Huge RC gain was realized 14 and 17% at 80 and 160nm pitch.

G Schindler et al., AMC (2006)

Fischer et al., IITC/MAM (2015)

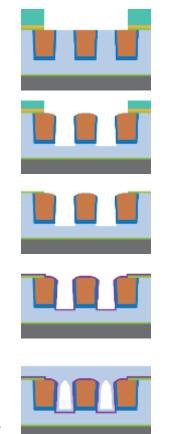

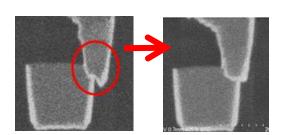

### Air Gap Structure and Integration Flow

- 1. Diffusion barrier open in select AG regions

- 2. Low-k etch process

- 3. Post-etch strip/clean

- 4. Conformal dielectric barrier deposition

- 5. Non-conformal low-k deposition to create AG

Every process step is critical for reliability, but conformal DB dep affects design

# Reliability Considerations: Short Lines are Integrated in Products!

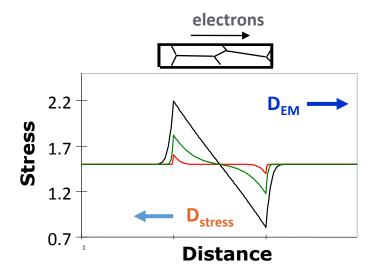

- Under normal electromigration (EM) testing,

- As atoms diffuse along the line length, compressive and tensile stresses develop at opposite ends of the line

- Line length:

- If the line is long, then a void develops in the line = failure

- If the line is short enough (< jL<sub>crit</sub>), there is a balance between electromigration- and stress-induced atomic diffusion

- Short-line effect:

- Short lines will never fail (< jL<sub>crit</sub> = Blech Length)

- Short-line effect will depend on dielectric material\*\*

Designers utilize and rely on short line effects in their designs for tight pitch interconnects; however, Blech Length is also considered at all metal layers, for deciding current density design rules

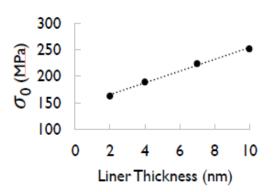

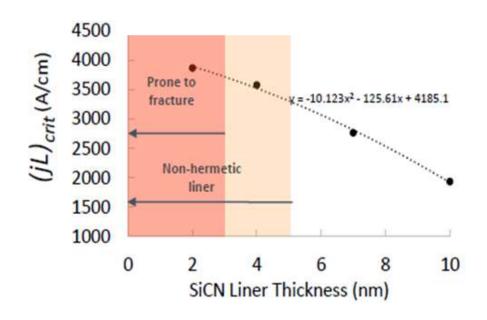

# Thickness of DB, Post Air Gap Formation, Affects Reliability

- Air gaps have to be designed into the chip

- Air gaps are selectively introduced, avoiding vias and placing air gaps at critical layers with high current densities for maximum benefit

- Process-oriented simulations reveal affect of Air Gaps on circuit design:

- As expected, the tensile stress in Cu lines increases linearly DB thickness

- JI<sub>crit</sub> (Blech Length) in an air-gapped interconnect depends on SiCN (DB) thickness and increasing the DB thickness degrades <sub>Jlcrit</sub>

- Airgapped interconnects with 5 nm conformal SiCN have a JI<sub>crit</sub> comparable to non-airgapped interconnects (with ULK 2.5 ILD)

- DB must be thick enough to be hermetic, but if too thick, JI<sub>crit</sub> will be degraded, affecting circuit design

Houman, Besser, Wilson and Croes, JAP 120, 095103 (2016)

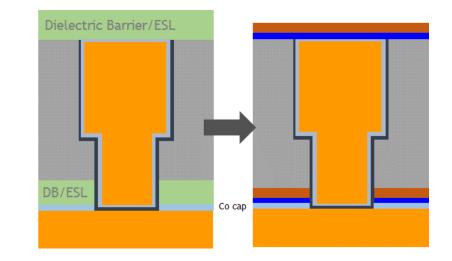

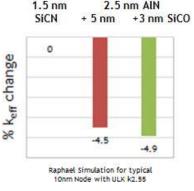

## Dielectric Barrier/Etch Stop Layer Requirements

- Requirements for dielectric barrier/ESL

- Cu diffusion barrier

- Hermetic barrier for moisture and O<sub>2</sub> Thicker Barrier

- High etch selectivity

- Excellent adhesion to metal and ULK

- High breakdown voltage and low leakage

- Low dielectric constant

- A combination of high etch selectivity ESL and thin hermetic Cu barrier enables DB scaling

- A high selectivity ESL can provide better control of unlanded via over etch and enable TiN wet removal with protected via bottom

- Replacing SiCN with AIN + SiCO is a offers a highly conformal stack with high etch selectivity, k<sub>eff</sub> reduction, and excellent diffusion barrier;

- film is hermetic at 3 nm thick.

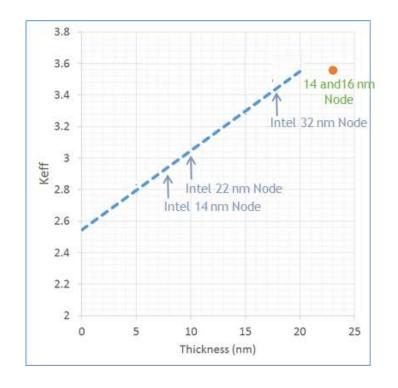

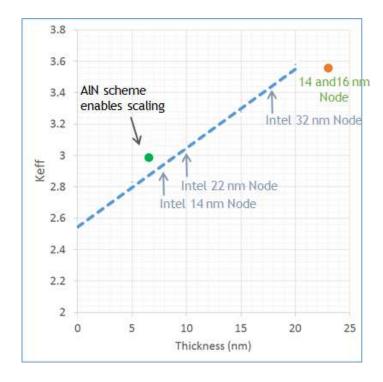

# Dielectric Barrier (DB)/Etch Stop Layer (ESL) Scaling to the Rescue

- Modelling suggest thinning or scaling the DB to 5 nm NDC thickness provides 7% k<sub>eff</sub> reduction, which is more than one generation of low k dielectric progress.

- Can DB/ESL continue to scale with all the DB/ESL requirements and increasing complex patterning?

## Dielectric Barrier (DB)/Etch Stop Layer (ESL) Scaling to the Rescue

- DB/ESL remains as the key process for capacitance reduction

- Co-optimization of etch and ESL is needed to enable robust via patterning and capacitance improvement

- Integrating AIN + SiCO stacks as a replacement for SiCN provides an integration advantage:

- Scaling enabled

- High etch selectivity

- Significant  $\mathbf{k}_{\text{eff}}$  reduction

- Excellent diffusion barrier

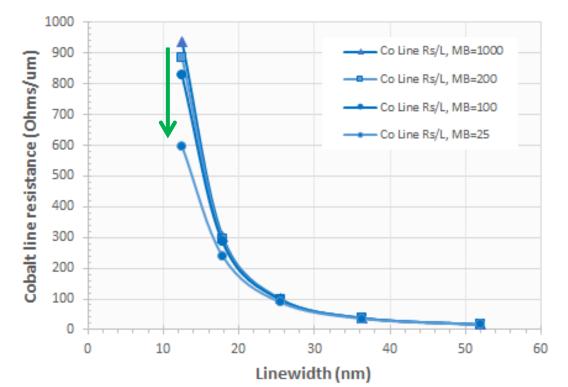

# **Resistance Reduction Opportunities**

How far can Cu extend? And what replaces Cu?

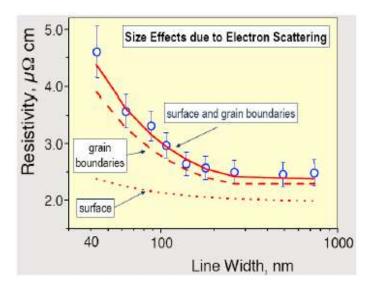

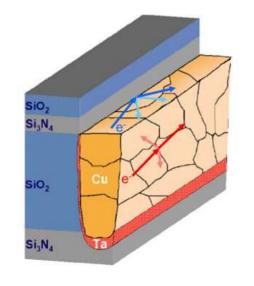

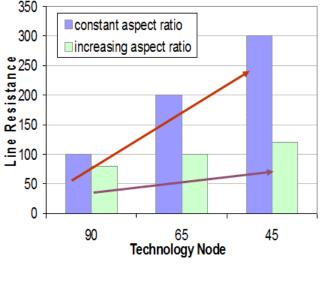

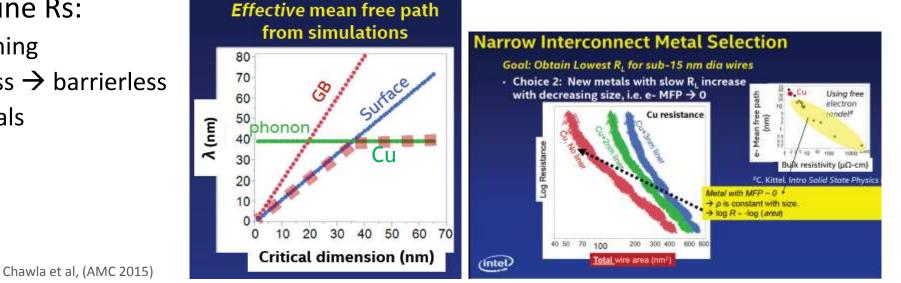

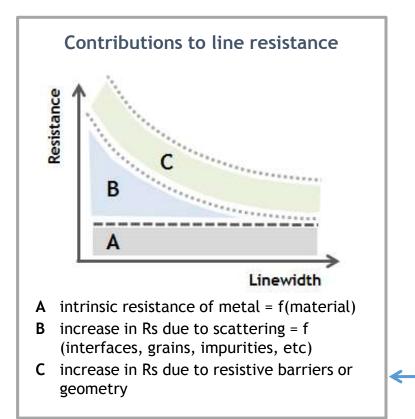

#### Understanding Copper Resistance Increase in Narrow Features

- Resistance increase with decreasing linewidth, due to scattering

- Electrons are scattered by grain boundaries, interfaces, surfaces, and defects (Cu electron mfp = 36 nm)

- Scattering events lead to Cu resistivity  $\uparrow$  with  $\downarrow$  linewidth

- How to compensate?

- Increase aspect ratio of the Cu line? Void-free fill is a challenge.

G. Schindler, Sematech workshop on Cu resistivity (2005)

P.R. Besser, ECS Trans 2(6), 3 (2007)

Paul Besser, NCCAVS Symposium in San Jose, CA

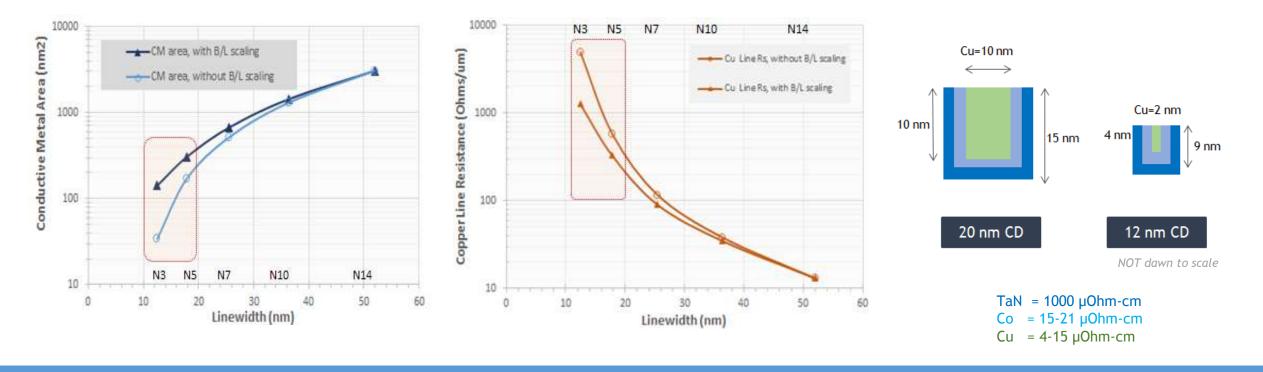

### Why Line Resistance Increases as Linewidth Decreases

- Cu extendibility is challenged by fill, barrier integrity, conductive metal area, and scattering; Cu current carrying cross-section i with i linewidth

- A calculation of conductive metal area and Cu line Rs as a function of linewidth reveals

- Barrier thicknesses has not scaled below 2.5 nm, but must scale for Cu to scale below 20 nm linewidth, and

- Area for conductive metal is small, leading to a high Rs in narrow features

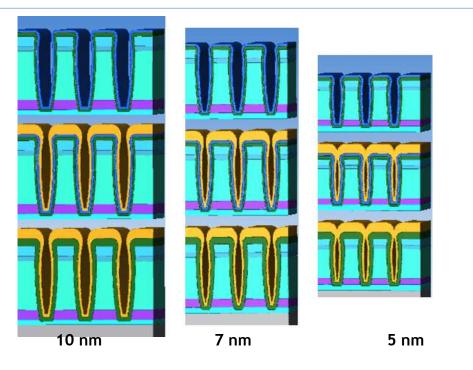

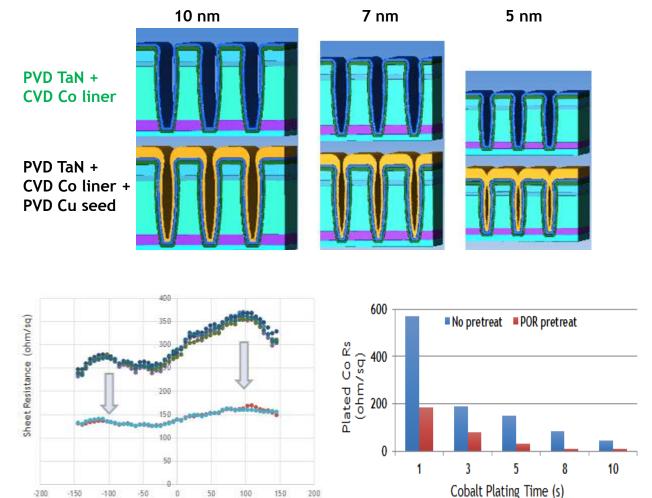

# BEOL Scaling Simulations: Cu can Extend to 7 nm, Maybe to 5 nm

PVD TaN barrier + CVD Co liner

PVD TaN barrier + CVD Co liner + PVD Cu seed

PVD TaN/Ta barrier + PVD Cu seed

- ► Coventor<sup>™</sup> simulations (to scale) reveal the challenge with extending PVD barrier/liner/seed: PVD overhang and can lead to voids in narrow features

- Cu extendibility is a function of design rules

- Cu seed extendibility to 5nm is questionable

- ▶ Migrating to PVD TaN/CVD liner (Co or Ru) is likely at 7 nm to enable extendibility of Cu

### At 10 and 7nm, Cu Extendibility is Possible

- Co liner provides an improvement for Cu scaling; however, only to 12 nm linewidth

- Scaling the liner thickness (with alternative liners) can extend Cu, but with a net resistance line

resistance increase

# What Is Beyond Cu?

#### Resistivity in Narrow Features (Intel, 2015)

- At the 5 nm node, not scaling the PVD liner thickness reduces the electrical area by a factor of 2 while increasing the Rs by an order of magnitude

- Based on modeling, resistivity in a 12 nm line (AR=1.5, 3 nm liner) is dominated by surface scattering:

- Surface scattering (54%), bulk resistivity/phonon(15%) and GB scattering (31%)

- Options to reduce line Rs:

- Subtractive patterning

- Scale liner thickness  $\rightarrow$  barrierless

- Smaller EMFP metals

### Another Perspective: EMFP and Resistivity

- In the case of thin wires and/or small grain sizes, the wire resistivity is proportional to the product of EMFP ( $\lambda$ ) and bulk resistivity ( $\rho_0$ ), for a fixed grain size distribution and linewidth

- With this metric, options to consider as Cu replacements are:

- Rh cost

- Ir cost

- Al cost and thermal excursion

- Co

- Ni options to consider...

- Ru

| Element    |    | Crystal structures | $\lambda_n$ (nm) | $\lambda \times \rho_0 (10^{-16} \Omega m^2)$ |  |

|------------|----|--------------------|------------------|-----------------------------------------------|--|

| Silver     | Ag | fcc                | 53.3             | 8.46                                          |  |

| Copper     | Cu | fcc                | 39.9             | 6.70                                          |  |

| Gold       | Au | fcc                | 37.7             | 8.35                                          |  |

| Aluminum   | Al | fcc                | 18.9             | 5.01                                          |  |

| Calcium    | Ca | fcc                | 35.4             | 11.9                                          |  |

| Beryllium  | Be | hcp                | 48.0/68.2        | 17.1/24.3                                     |  |

| Magnesium  | Mg | hcp                | 22.3/20.0        | 9.81/8.80                                     |  |

| Rhodium    | Rh | fcc                | 6.88             | 3.23                                          |  |

| Sodium     | Na | bcc                | 30.9             | 14.7                                          |  |

| Iridium    | Ir | fcc                | 7.09             | 3.69                                          |  |

| Tungsten   | W  | bcc                | 15.5             | 8.20                                          |  |

| Molybdenum | Mo | bcc                | 11.2             | 5.99                                          |  |

| Zinc       | Zn | hcp                | 17.4/13.7        | 10.3/8.1                                      |  |

| Cobalt     | Co | hcp                | 11.8/7.77        | 7.31/4.82                                     |  |

| Nickel     | Ni | fcc                | 5.87             | 4.07                                          |  |

| Potassium  | K  | bcc                | 31.5             | 22.7                                          |  |

| Cadmium    | Cd | hcp                | 16.8/15.1        | 12.6/11.3                                     |  |

| Ruthenium  | Ru | hcp                | 6.59/4.88        | 5.14/3.81                                     |  |

| Indium     | In | bet                | 8.65/8.16        | 7.62/7.18                                     |  |

| Osmium     | Os | hcp                | 7.20/4.87        | 6.41/4.33                                     |  |

D. Gall, JAP 119, 085101 (2016)

#### Metal Options: Choosing a Good Metal Conductor to Replace Cu

|                             | Cu       | Со                    | Ru         | Ni               |

|-----------------------------|----------|-----------------------|------------|------------------|

| Barrier/Liner Needed        | Barrier  | Thin liner            | Thin liner | TBD              |

| Bulk Resistivity            |          |                       |            |                  |

| EMFP (nm)                   | 39       | 6                     | 10         | 18               |

| Melting Point (°C)          | 1083     | 1495                  | 2250       | 1453             |

| Deposition processes        | ECD, PVD | ECD, ELD,<br>CVD, PVD | CVD, PVD   | PVD, CVD,<br>ELD |

| Gap Fill of Narrow Features |          |                       |            |                  |

| Cost                        |          |                       |            |                  |

Co exhibits short EMFP, high melting point, and can be deposited with various techniques at low cost

P.R. Besser, ECS Trans 2(6), 3 (2007)

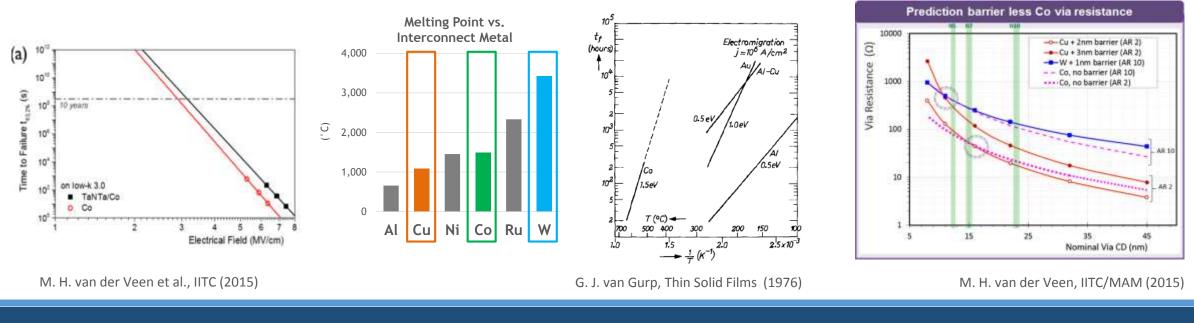

## Why Cobalt for Interconnects?

- Co is already integrated in IC processing as a liner and a cap layer

- The shorter mean free path of electrons in Co and the reduced requirement for a barrier reduce the resistivity disadvantage of Co (vs. Cu) in the 15-20 nm line dimension range

- Co electromigration (EM) is better than Cu, based on melting point and publications

- Electroplating allows bottom-up Co fill at a low cost, but CVD/PVD also fills features

Paul Besser, NCCAVS Symposium in San Jose, CA

• IMEC simulations suggest barrierless vias filled with Co have a resistance benefit for N7 and beyond

# Enabling Void-Free Metallization with Co Electrochemical Dep

15nm 53nm 14nm 124nm 16nm

- Co electroplating on CVD Co liner alleviates PVD Cu seed "pinch off"

- Co liner oxidizes when exposed to air and leads to resistivity increase and potential interfacial integrity degradation

- Pre-treatment of Co liner results in substantial conductivity increase and allows for improved nucleation of ECP Co film

- Temperature/time/chemistry can be used to control the sheet resistance drop and Co agglomeration

Hui-Jung Wu et al., Semicon West (2016)

Natalia Doubina et al., CSTIC 2016, Shanghai

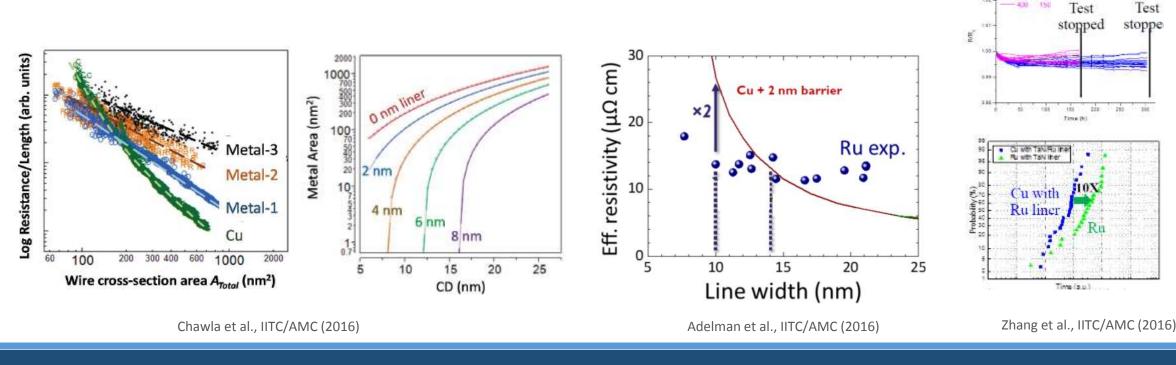

### Other Alternatives to Cu

- Resistance and Electromigration Performance of 6 nm Wires (Intel)

- Line Rs and EM were measured for 6 nm CD wires; interconnect performance was measured down to 60 nm<sup>2</sup> wire crosssectional area.

- Ruthenium is an option to replace Cu at 5nm (imec, GLOBALFOUNDRIES, IBM)

- Ru reflows at a low temperature; resistivity is 18 µΩ-cm at 7 nm LW is better than Cu (with a 2 nm barrier); via Rs was comparable to Cu; a thin adhesion layer is required (TiN), but TDDB and EM are good

- The challenges with Ru are cost, CMP, and immaturity

Resistance ratio vs stress time

i mAAum

T(°C)

#### How to Reduce Interconnect Rs Further?

• The solutions shown thus far are incremental improvements in via/line Rs: the industry needs still lower via and line Rs!

31

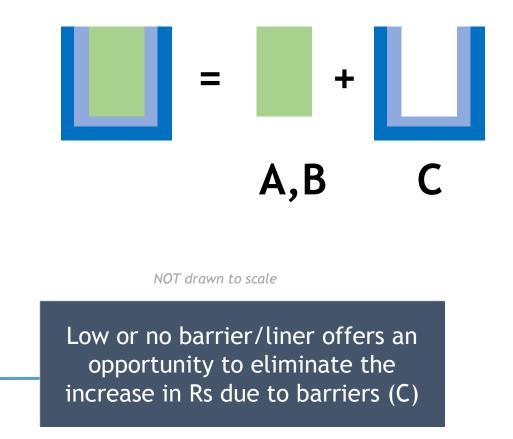

#### How to Reduce Interconnect Rs Further?

• The solutions shown thus far are incremental improvements in via/line Rs: the industry needs still lower via and line Rs!

#### • One option: directly platable, conductive liner

- Co-Ti (University of Tokyo). Resistivity is ~130  $\mu\Omega\text{-cm}$

- Co-Mo (Fudan University). Resistivity is 100-150  $\mu\Omega$ -cm

- Co-W (Tokyo University). Resistivity of CoW films (200 nm) with 10 and 20%W were 80 and 200 μΩ-cm. Adding Cp<sub>2</sub>WH<sub>2</sub> into source gas in an ALD cycle -> CoW alloy film with 5%W without including WO<sub>3</sub> or C reduced resistivity to 25 μΩ-cm (15 nm thick)

- Co-Si (Literature). Resistivity is10-40 μΩ-cm, depending on the phase of CoSix formed

32

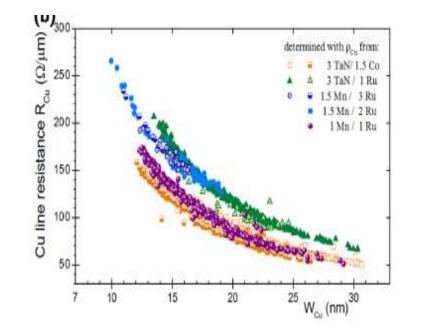

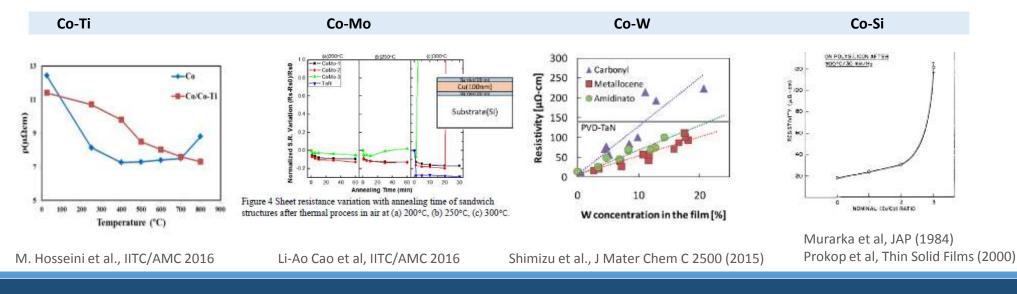

## Modelling of Barrier Resistivity Affects Line Resistance

#### Co Line Rs vs. linewidth

| Technology |       | 14nm | 10nm | 7nm  | 5nm  |

|------------|-------|------|------|------|------|

| Back end R | Ω/µm  | 27   | 72   | 173  | 400  |

| Back end C | aF/µm | 19.8 | 17.1 | 16.5 | 16.0 |

Greg Yeric, ARM (IEDM 2014)

Calculations of line resistance as a function of barrier resistivity (25 vs. 1000 µOhm-cm) reveal barrier line Rs reduces ~40% as a function of barrier resistance (at 12 nm linewidth)

#### **Barrier resistance matters**

Circuit performance simulations confirm a performance gain with conductive liner

#### Assumptions

- Co Line Rs based was measured to 18nm. Extrapolated to 12nm LW

- 70% linewidth scaling node to node

- aspect ratio is constant at 2

- Metal resistivity changes with linewidth (LW)

- Barrier thickness = constant at 2.5 nm

33

Barrier resistivity changes from 25-1000 μOhm-cm

Paul Besser, NCCAVS Symposium in San Jose, CA

# Summary

- Materials innovations drive performance improvements in the microelectronics industry, creating faster and smaller devices

- Leading-edge nodes are seeing an explosion of new innovations to drive BEOL RC reduction

- For capacitance (C)

- Capacitance scaling has slowed

- Dielectric barrier scaling (i.e. AIN + SiCO) offers the best opportunity to reduce capacitance

- For resistance (R)

- Line and via resistance are the dominant source of interconnect delay at 7 and 5 nm

- Cu line and via resistance are increasing with each technology node, due to electron scattering, but also due unidirectional patterning and a lack of barrier scaling

- Conductive liner/barriers offer promise to lower line and via resistance

- Co interconnects show great promise to replace Cu, either by

- Electroless Co via prefill or

- Co electroplating

# Thank you