# Bootstrap Circuitry Selection for Half-Bridge Configurations

Mamadou Diallo, High Power Drivers

#### **ABSTRACT**

Driving MOSFETs in half-bridge configurations present many challenges for designers. One of those challenges is generating bias for the high-side FET. A bootstrap circuit takes care of this issue when properly designed.

This document uses UCC27710, TI's 620V half-bridge gate driver with interlock to present the different components in a bootstrap circuit and how to properly select them in order to ensure predictable switching of the power FETs.

# Contents

| 1 | Introduction                                                                      | - 1 |

|---|-----------------------------------------------------------------------------------|-----|

| 2 | Basic Operation of Bootstrap Circuit                                              | 2   |

| 3 | Bootstrap Components Selection                                                    |     |

| 4 | Layout Considerations for Bootstrap Components                                    | 8   |

| 5 | Summary                                                                           | Ş   |

| 6 | References                                                                        | 9   |

|   | List of Figures                                                                   |     |

| 1 | Bootstrap Charging Path                                                           | 2   |

| 2 | Bootstrap Capacitor Discharging Path                                              | 2   |

| 3 | Reverse Recovery Losses due to Bootstrap Diode Reverse Recovery Time              | 4   |

| 4 | Reverse Recovery Losses due to Bootstrap Diode Reverse Recovery Time (Zoomed Out) | 5   |

| 5 | HB_HS Ringing Effects on Switch Node                                              | 6   |

| 6 | VDD/HB-HS Fast Ramp Up (R <sub>boot</sub> = 00hms)                                | 7   |

| 7 | VDD/HB-HS Fast Ramp Up (R <sub>boot</sub> = 2.20hms)                              | 8   |

| 8 | Layout Example using UCC27710                                                     | 8   |

#### **List of Tables**

#### 1 Introduction

When using half-bridge configurations, it is necessary to generate high-side bias to drive the gate of the high-side FET referenced to the switch node. One of the most popular and cost effective way for designers to do so is the use of a bootstrap circuit which consists of a capacitor, a diode, a resistor and a bypass capacitor.

This application report will explain how this circuit works, the key components of the bootstrap circuits and their impact in the gate drive. This app note will put emphasis on half-bridge gate drives using drivers with no built-in bootstrap diode, which gives designers flexibility and reduces power dissipation in the gate driver IC. Additionally, it will discuss the layout considerations for the different components of this circuit.

## 2 Basic Operation of Bootstrap Circuit

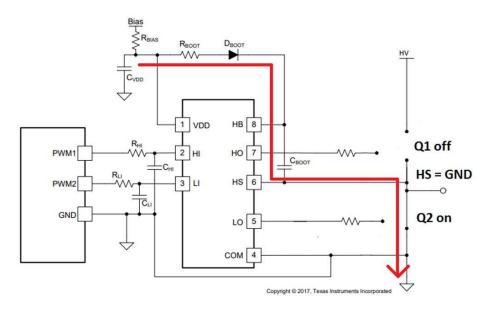

A bootstrap circuit is used in half-bridge configurations to supply bias to the high-side FET. Figure 1 shows the charging path of a bootstrap circuit in a simplified half-bridge configuration using UCC27710, TI's 620V half-bridge driver with interlock. When the low-side FET is on (high-side FET is off), the HS pin and the switch node are pulled to ground; the VDD bias supply, through the bypass capacitor, charges the bootstrap capacitor through the bootstrap diode and resistor.

Figure 1. Bootstrap Charging Path

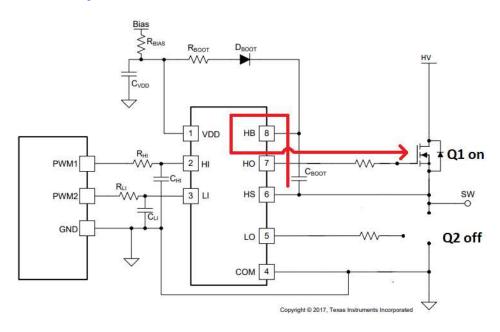

When the low-side FET is turned off and the high-side is on, the HS pin of the gate driver and the switch node are pulled to the high voltage bus HV; the bootstrap capacitor discharges some of the stored voltage (accumulated during the charging sequence) to the high-side FET through the HO and HS pins of the gate driver as shown in Figure 2.

Figure 2. Bootstrap Capacitor Discharging Path

## 3 Bootstrap Components Selection

This section discusses each component's role and its impact in the gate drive.

## 3.1 Bootstrap Capacitor

From a design perspective, this is the most important component because it provides a low impedance path to source the high peak currents to charge the high-side switch. As a general rule of thumb, this bootstrap capacitor should be sized to have enough energy to drive the gate of the high-side MOSFET without being depleted by more than 10%. This bootstrap cap should be at least 10 times greater than the gate capacitance of the high-side FET. The reason for that is to allow for capacitance shift from DC bias and temperature, and also skipped cycles that occur during load transients. The gate capacitance can be determined using Equation 1:

$$\begin{split} &C_g = \frac{Q_g}{V_{Q_{1g}}} \\ &\text{where } Q_g \text{: gate charge (MOSFET's datasheet)} \\ &V_{Q_{1g}} = V_{DD} - V_{BootDiode} \\ &\text{where } V_{BootDiode} \text{: forward voltage drop across the boot diode} \,. \end{split}$$

Once the gate charge determined, the minimum value for the bootstrap capacitor can be estimated using Equation 2:

$$C_{\text{boot}} \ge 10 \times C_{\text{g}}$$

(2)

Alternatively, a more detailed calculation of the minimum bootstrap capacitor value can be done using Equation 3:

$$\begin{split} &C_{boot} \geq \frac{Q_{total}}{\Delta \, V_{HB}} \\ &Q_{total} = Q_G + \, I_{HBS} \times \frac{D_{max}}{f_{sw}} + \frac{I_{HB}}{f_{sw}} \end{split}$$

where:

where:

- · Q<sub>G</sub> = Total MOSFET gate charge (MOSFET's datasheet)

- · I<sub>HBS</sub> = HB to VSS leakage current (gate driver's datasheet)

- $\cdot D_{max} = Maximum duty cycle$

- · I<sub>HB</sub> = HB Quiescent current (Gate driver's datasheet)

And

$$\Delta V_{HB} = V_{DD} - V_{DH} - V_{HBL}$$

where:

- $\cdot V_{DD} =$  Supply voltage of the gate driver IC

- · V<sub>DH</sub> = Bootstrap diode forward voltage drop (Bootstrap diode datasheet)

- · V<sub>HBL</sub> = HB UVLO falling threshold (Gate driver datasheet)

It is important to note that values below the minimum required bootstrap capacitor value could lead to activation of the driver's UVLO therefore prematurely turning off the high-side FET. On the flip side, higher values of the bootstrap capacitor lead to lower ripple voltage and longer reverse recovery time in some conditions (when initially charging the bootstrap cap or with a narrow bootstrap charging period) as well as higher peak current through the bootstrap diode. Equation 4 relates the bootstrap cap and the peak currents through the bootstrap diode.

$$I_{peak} = C_{boot} \times \frac{dv}{dt}$$

(4)

It is generally recommended to use low ESR and ESL surface mount multi-layer ceramic capacitors (MLCC) with good voltage ratings (2xVDD), temperature coefficients and capacitance tolerances.

(3)

## 3.2 VDD Bypass Capacitor

The charge to replenish the bootstrap capacitor must come from some larger bypass capacitor, usually the VDD bypass capacitor. As a rule of thumb, this bypass capacitor should be sized to be at least 10 times larger than the bootstrap capacitor so that it is not completely drained during the charging time of the bootstrap capacitor. This allows the bootstrap capacitor to be properly resplenished during the charging sequence. This 10x ratio results in 10% maximum ripple on the VDD capacitor in worst case conditions.

$$C_{VDD} \ge 10 \times C_{Boot}$$

(5)

# 3.3 External Bootstrap Diode

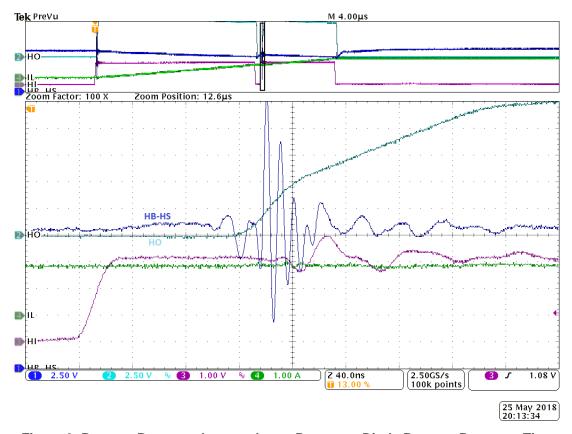

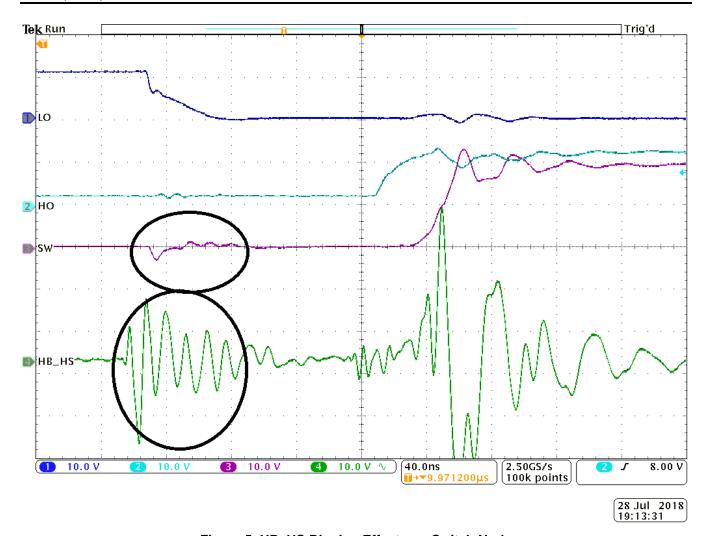

In order to minimize losses associated with the reverse recovery properties of the diode and ground noise bouncing, a fast recovery diode or Schottky diode with low forward voltage drop and low junction capacitance is recommended. Using Schottky diodes reduce the risk associated with charge supplied back to the gate driver supply from the bootstrap capacitor and minimize leakage current. Figure 3, shows the reverse recovery losses when using diodes with reverse recovery times on HB-HS(Ch1). We can observe large amount of over and undershoot on the HB-HS pin which can trigger the driver's UVLO and shutdown the gate driver.

When the HS pin (switch node) is pulled to a higher voltage, the diode must be able reverse bias fast enough to block any charges from the bootstrap capacitor to the VDD supply. This bootstrap diode should be carefully chosen such that it is capable of handling the peak transient currents during start-up; and such that its voltage rating is higher than the system DC-link voltage with enough margins.

Figure 3. Reverse Recovery Losses due to Bootstrap Diode Reverse Recovery Time

Figure 4 below shows a reverse recovery condition created (channel 1) by setting up the timing to specifically force the switch node high with the diode current flowing.

Figure 4. Reverse Recovery Losses due to Bootstrap Diode Reverse Recovery Time (Zoomed Out)

Figure 5 shows the effects of the losses on the HB-HS pin which can trigger the switch node and potentially damage the driver.

Figure 5. HB\_HS Ringing Effects on Switch Node

## 3.4 Bootstrap Resistor

The role of the bootstrap resistor is to limit the peak currents at the bootstrap diode during start-up, it should therefore be carefully selected as it introduces a time constant with the bootstrap capacitor given by Equation 6:

$$\tau = \frac{R_{\text{Boot}} \times C_{\text{Boot}}}{\text{Duty Cycle}}$$

(6)

This time constant occuring during the high-side off time explains the dependency on duty cycle. This duty cycle being constant, the bootstrap resistor and bootstrap capacitor should be tuned appropriately to achieve the desired start-up time. Increasing the bootstrap resistor values will increase the time constant leading to slower start-up time.

Additionally, the bootstrap resistor chosen must be able to withstand high power dissipation during the first charging sequence of the bootstrap capacitor. This energy can be estimated by Equation 7:

$$\frac{1}{2} \times C_{\text{boot}} \times V_{C_{\text{boot}}}^2 \tag{7}$$

This energy is dissipated during the charging time of the bootstrap capacitor and can be estimated using Equation 8:

$$E \cong 3 \times C_{boot} \times R_{boot}$$

(8)

This resistor is essential in limiting the peak currents through the bootstrap diode at start-up and limiting the dv/dt of HB-HS (high-side floating supply to the return high-side floating supply). The peak current through this resistor can be calculated using Equation 9:

$$I_{pk} = \frac{V_{DD} - V_{BootDiode}}{R_{boot}}$$

(9)

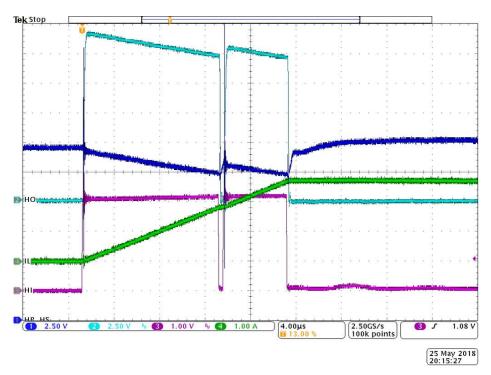

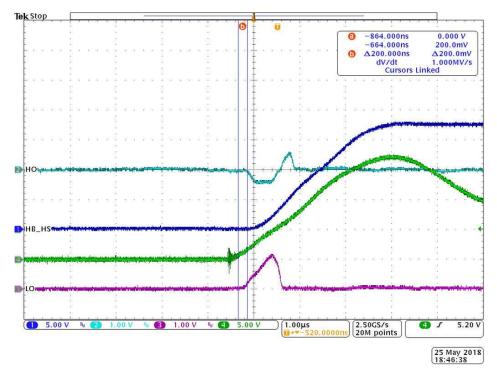

Figure 6 shows the fast ramp up on VDD (CH4) and HB-HS (CH1) when using a 0-Ohm resistor which leads to undesired change in voltage on LO(CH3) and HO(CH2).

Figure 6. VDD/HB-HS Fast Ramp Up (R<sub>boot</sub> = 00hms)

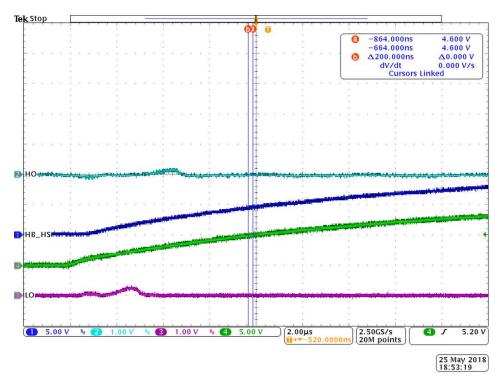

Figure 7 shows how using slightly higher resistor value ( $R_{boot} = 2.20$ hms) solve this issue. It is important to note that the bias rising rate observed in Figure 7 does not apply to all drivers.

Figure 7. VDD/HB-HS Fast Ramp Up ( $R_{boot} = 2.20$ hms)

# 4 Layout Considerations for Bootstrap Components

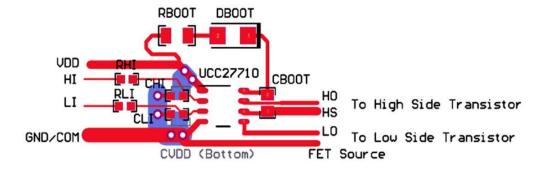

Once all bootstrap components appropriately selected, it is important to carefully place these components in order to minimize parasitic inductances and reduce high current trace length. This high current path includes the bootstrap capacitor, the bootstrap diode, the ground-referenced VDD bypass capacitor of the driver, and the low-side power switch. It is therefore important to reduce that path and keep that loop as small as possible. The bootstrap capacitor and bypass capacitor should be placed as closed as possible to the gate driver supply pins. Figure 8 below shows a good layout example using UCC27710 with all bootstrap components located near the gate driver IC minimizing any effects of parasitic inductances and reducing the high peak currents path of the bootstrap circuit. It is also important to separate high voltage power and low voltage signal traces.

Figure 8. Layout Example using UCC27710

www.ti.com Summary

## 5 Summary

This application report used UCC27710, TI's 600V family of half-bridge drivers to discuss the basic operation of a bootstrap circuit in a half-bridge configuration. It also discussed the role and importance of each bootstrap components required to generate bias for the high-side FET in half-bridge configurations. It showed a detailed calculation method as well as a general rule of thumb estimation for the bootstrap capacitor. Additionally, it discussed how to properly place these components on a PCB layout once all the components are appropriately selected.

#### 6 References

- UCC27710 Product Folder

- UCC27710 Datasheet

- UCC27710 Evaluation Module

- Half-bridge Driver Products

- Fundamentals of MOSFET and IGBT Gate Driver Circuits

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ("TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated