NEPP EEE Parts for Small Missions Workshop September 10-11, 2014

#### Candidate Cubesat Processors

#### Steven M. Guertin

Jet Propulsion Laboratory / California Institute of Technology

Pasadena, CA

This work was performed at the Jet Propulsion Laboratory, California Institute of Technology,

Under contract with the National Aeronautics and Space Administration (NASA)

This work was funded by the NASA Electronic Parts and Packaging Program (NEPP)

Copyright 2014 California Institute of Technology. Government Sponsorship is acknowledged.

#### Outline

- Motivation

- Microcontrollers Current Cubesat Devices

- Selection Efforts

- MSP430 SEE and TID

- PIC SEE and TID

- Microprocessors Expected Use Soon

- Selection

- Snapdragon Efforts

- Atom

## Key Issues

- Common paradigm of Cubesat processing

- Small

- Low Power

- Microcontroller-like

- A couple common processors/microcontrollers

- Looking forward

- We expect that processing desire will increase

- Instruments may become more computation intensive

- Primary processors may migrate for more computation

- Approach for improving mission assurance

- Determine mission assurance issues for current-generation microcontrollers/microprocessors—focus on SEL/gross SEE, and TID (Primarily LEO and GEO/GCR environments)

- Build repository of knowledge for devices for future use

#### **CUBESAT MICROCONTROLLERS**

## National Aeronautics and Space Administration Cubesat Controller Survey

- Reviewed many Cubesat system architectures

- Verified device ordering approach with Pumpkin they indicate orders are simple "no special procedures" quote and buy from places like Digikey

| CubeSat Provider | Processor              | Availability | Development |

|------------------|------------------------|--------------|-------------|

|                  |                        |              | Board       |

| Pumpkin          | TI MSP430F1612         | Yes          | Yes         |

|                  | TI MSP430F1611         | Yes          | Yes         |

|                  | TI MSP430F1618         | No           | No          |

|                  | Silicon Labs C8051F120 | Yes          | Yes         |

|                  | Microchip              | Yes          | Yes         |

|                  | PIC24FJ256GA110        |              |             |

|                  | Microchip              | Yes          | Yes         |

|                  | dsPIC33FJ256GP710      |              |             |

| Tyvak            | AT91SAM9G20 (ATMEL,    | Yes          | Yes         |

| (Intrepid)       | ARM9 Based)            |              |             |

| CubeSat Provider | Processor                       | Availability   | Development<br>Board |

|------------------|---------------------------------|----------------|----------------------|

| GOMspace         | AT91SAM7 series (ATMEL, Unknown |                | Unknown              |

| (NanoMind)       | ARM7 Based)                     |                |                      |

|                  | ATMEL ATMEGA1281                | Yes            | Unknown              |

| Gaussteam        | TI MSP430 series                | Yes            | Yes                  |

| (ABACUS)         |                                 |                |                      |

| ESL/ISIS         | ARM Cortex-M3 MCU               | Unknown        | Unknown              |

| (Cube Computer)  |                                 |                |                      |

| ISIS (OBC)       | AT91SAM9G20 (ATMEL,             | 20 (ATMEL, Yes |                      |

| 1                | ARM9 Based)                     |                |                      |

| Clyde Space      | Use Pumpkin CubeSat OBC         | Yes            | Yes                  |

To be presented by Steven M. Guertin at the

#### Microcontroller Selection

- Initial efforts

- Currently focusing on the PIC and MSP devices

- Database shows many missions use these

- Believed they may show some significant problems

- Relatively easy inside our flow for development

- Pushing to the AT91SAM9G20

- No data yet, but moving forward with test design and plan

- ARM-based in-line with Xilinx Zynq, and higher-end processors

- Follow-up

- Most likely the AT91SAM9G20 will be studied more in the future (i.e. no likely to finish this FY)

- Si Labs C8051

- At present, focus is on SEL and TID. SEE effort may increase

## National Aeronautics and Space Administration SEE Testing — MSP430

- Utilized MSP development kit

- Prepared by acid-etching and using a socket with the plastic over the DUT drilled out

- Primary test effort

- Performed SEL and limited SEE testing of MSP430F1612

- Cursory comparison to MSPF4301611 shows similar behavior

- Socket on the board limited angular study

- But SEL and SEU already observed so error in rates is in conservatism

MSP430F1612 positioned in the beam line at TAMU

## **National Aeronautics**

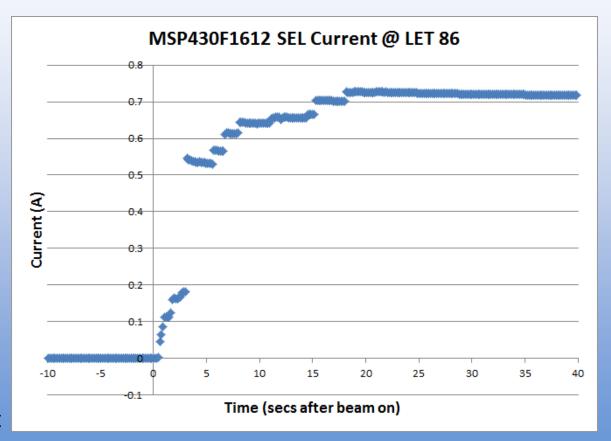

## and Space Administration SEL Results — MSP430

- **MSP** Devices **Experienced increased** current almost immediately after the beam was turned on.

- Nominal operating current is less than 1 mA

- Current "steps" observed, making signature messy

- Max current appears limited, but 100x or more of nominal...

- Device unprogrammable and not running after 1e6 – but run at right is 3e4/cm<sup>2</sup> w/no failure

Flux =  $^2$ e3/cm<sup>2</sup>-sec

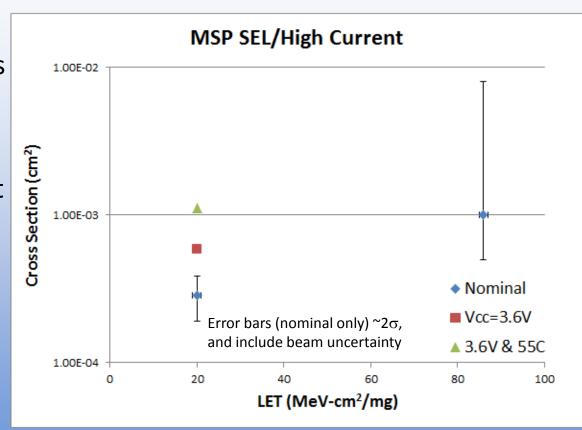

#### SEL Cross Section – MSP 430

- SEL behavior is common at tested LETs (20 and 86 MeVcm<sup>2</sup>/mg)

- 0.05 A threshold

- Not recovered by reset

- Cannot measure other event types

- Expect to have cross section ~1e-6cm² at LET 10

- ISS event rate estimated between 2e-5 and 4e-4/day

- ~10x higher for GCR

| LET (MeV-cm <sup>2</sup> /mg) | Condition | SBUs | ਰ (cm²/bit) |

|-------------------------------|-----------|------|-------------|

| 20                            | Nominal   | 66   | 4.2e-8      |

To be presented by Steven M. Guertin at the NASA Electronic Electr

## TID Testing of MSP 1611 & 1612

- Performed biased and unbiased testing

- Used JPL's high dose rate Co-60 room irradiator

- Between irradiation, tested with characterization programs:

- LED blinker

- Flash memory test program (provided in MSP development kit)

- Whetstone test program

- Test steps: 1, 2, 5, 10, and 20 krad(Si)

- Unbiased devices showed no degradation at 20 krad

- Some biased 1611 devices became unstable at 10 krad

- some devices failed to be reprogrammable at 20k, but instead seemed to be running the TID test program (LED blinking)

#### **SEE Testing - PIC**

- Used Explorer 16 board from Microchip

- Test Devices:

- PIC24FJ256GA110

- dsPIC33FJ256GP710

- Using on-board regulators

- Two test programs

- RAM write/read

- Flash read/dwell

Plug-In-Module

- PIC24

- dsPIC33

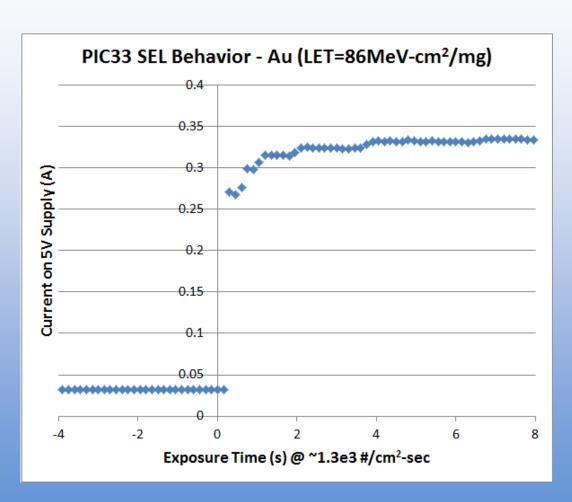

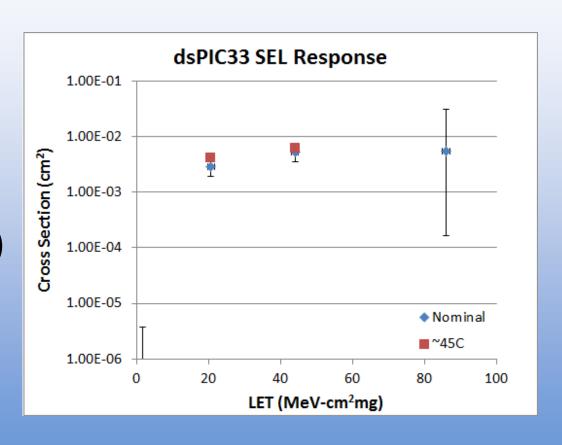

#### SEL Results – PIC33 Current

- 5V supply line increases current very quickly after beam on

- Not recovered by reset

- Similar "currentstep" behavior to MSP

- Maximum current appears to be small compared to SEL

- But still 10x increase

No evidence of damage after exposure to 1e7 #/cm<sup>2</sup>

#### **SEL Cross Section**

- Used 0.25 A as threshold for SEL

- When heated, the SEL current trips protection on the on-board regulation

- Both points (slightly) higher σ for high T

- ISS event rate estimated between 2e-4 and 4e-3/day

- ~10x higher for GCR

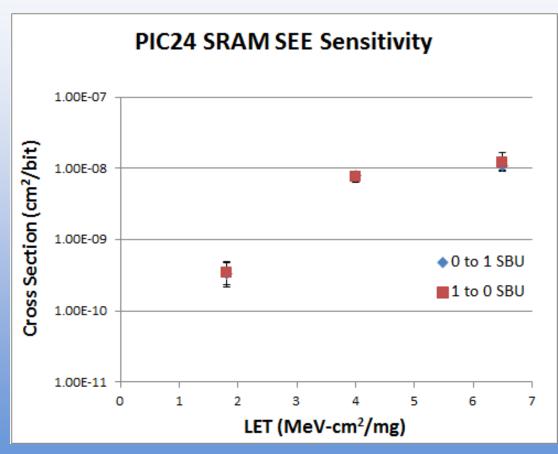

#### PIC SEE Results

- Low priority compared to SEL efforts

- Flash Results

- No upsets observed with 6e5 #/cm² ions at LET = 86

- Limiting per-bit cross section of ~6e-12 cm²/bit

- SRAM Results

- SEL behavior interfered at higher LETs

ARM9-based ISIS board

#### **NASA AMES Phonesat**

#### **CUBESAT MICROPROCESSORS**

#### Motivation

- Various Cubesats have flown with more capable processing

- Usually C&DH is 8 or 16-bit MCUs, the "ARMs" are actually reduced capability Thumb™ processors

- AAUSat-3, CANX-2 used a 32-bit ARM processor

- Phonesat ... flew ... phones (and newer iterations are flying more)

- Expect that as Cubesat programs continue, need for more processing will be important

- Key drivers same as for Cubesats in general

- Small, low power, cheap

- Generally accessible to low-budget environments (schools, R&D, etc.)

## Snapdragon/Atom Effort

- We focused on cell phone processors primary player is ARM, with Intel trying to get Atom into play

- Avoid issues with closed architecture i.e. not using Apple A6/A7/etc.

- Most common phone processor in high-end devices is Snapdragon, with Krait CPU (similar to ARM Cortex A15)

- We are currently looking at Snapdragon 600 and Snapdragon 800 (both TSMC 28 nm – low power)

- Prototyping equipment readily available

- Being used in the hobby space

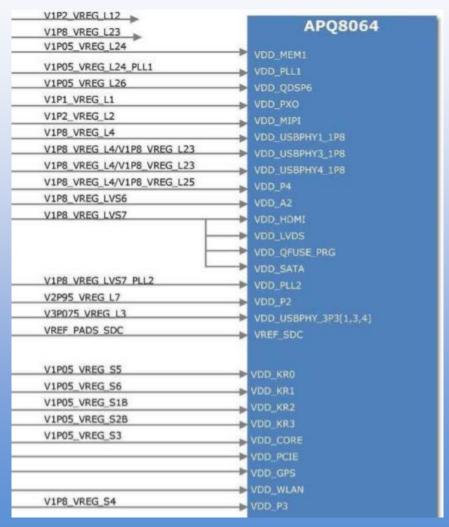

## SEL Test of Snapdragon

- Qualcomm makes a power support chip that provides the supplies required.

- We were unable to obtain the power scheme to be able to do this independently, and the test board did not provide direct access to all power lines

## SEL in APQ8064

- Thinned parts to 80 μm

- Tested at TAMU with 25 MeV/amu Kr

- $-60^{\circ}$  Tilt LET<sub>eff</sub> = 57 & 75 (at sensitive region)

- 3e7 exposure at LET 57, 4e7 exposure at LET 75

- Tested during booting of Android

- Almost all SEL runs resulted in a "rebooting in 5 seconds" but reboot never succeeded

- Reset worked in 9 out of 10 runs resulting in nominal operation (this rules out an SEL behavior).

- Board current @5.1V:

- At start of run 330-350 mA

- At end of run 160-500 mA (never above 350 for high exposure runs)

- No significant increase

## SEE Testing of Snapdragon

- Exposed IFC6410 board to Ar @ LET = 7 MeV-cm<sup>2</sup>/mg

- Test software was to monitor Android boot

- Observed through UART error output

- Provides information about boot behavior for first ~90 seconds

- Takes ~5 seconds after power up to be activated

- Provides interrupt/exception reporting

- Total exposure was 3e6 #/cm²

- No damage observed

- No evidence of high current modes (but LET was low)

- But system had a hard time, and crashed often

## National Aeronautics and Space A2 Error tration

- Capture of errors during boot

- LET=6.3, flux ~5e3

#/cm<sup>2</sup>

- Using Android boot

Unspecified Exception

Requires ~10-15 secs of boot to get reports

## **Unspecified Exception**

Usually fails to reach reportable status

```

42.0745301 Bluetooth: Tx timer expired

43.8143751 L2 Error detected!

43.8164191 L2ESR

= 0 \times 00010010

L2ESYNR0 = 0x6200080a

L2ESYNR1 = 0 \times 04a4977a

L2EARØ

= 0 \times 0002 c160

= 0x00000000

L2EAR1

CPU bitmap = 0x1

43.8363191 L2 data soft error, single-bit

43.840378] Kernel panic - not syncing: L2 single-bit error detected

43.846787] [<c0014918>] (unwind_backtrace+0x0/0x11c) from [<c07ba978>] (pani

+0x84/0x1d4>

43.855028] [<c07ba978>] <panic+0x84/0x1d4> from [<c007d7f4>] <msm_12_erp_irq

0x1fc/0x260>

43.863268] [<c007d7f4>] <msm_12_erp_irg+0x1fc/0x260> from [<c00d2844>] <hand

1 (handle_irg_event+0x3c/0x5c)

43.882862] [<c00d2a60>] (handle_irg_event+0x3c/0x5c) from [<c00d554c)] (hand

le_fasteoi_irq+0xdc/0x148)

eneric_handle_irq+0x30/0x44)

43.901785] [<c00d20a8>] (generic_handle_irg+0x30/0x44> from [<c000ee40>] (ha

idle_IRQ+0x7c/0xc0>

43.9105441 [<c000ee40>] (handle_IRQ+0x7c/0xc0> from [<c0008620>] (gic_handle,

irg+0x94/0x110>

43.919059] [<c0008620>] {gic_handle_irg+0x94/0x110> from [<c07c8cc0>] {__irg

suc+0x40/0x70)

43.9274531 Exception stack(0xc0d05e70 to 0xc0d05eb8)

43.9324881 5e60:

00000000 c0f3cd00 00000

ааа аааааааа

43.940668] 5e80: c0d04000 00000000 00000202 c0d05f28 00000012 fa00300c c0d43

43.948817] 5ea0: c0d4f080 c0d05eb8 c0087d3c c0087710 20000113 ffffffff

43.9554401 [<c07c8cc0>] <__irq_svc+0x40/0x70> from [<c0087710>] <__do_softir

43.963680] [<c0087710>] <__do_softirg+0x4c/0x248> from [<c0087d3c>] <irg_exi

+0x48/0xa0)

43.971860] [<c0087d3c>] (irg_exit+0x48/0xa0) from [<c000ee44>] (handle_IRQ+0

(80/0xc0)

irg+0x94/0x110>

43.988249] [<c0008620>] (gic_handle_irq+0x94/0x110) from [<c07c8cc0>] (__irq

43.9966421 Exception stack(0xc0d05f28 to 0xc0d05f70)

44.0016781 5f20:

00000000 00000000 00000001 00000003 00000

44.0098581 5f40: c0d65924 00000003 00000000 c0d65924 00000000 00000000 00000

44.018007] 5f60: c07c873c c005bf7c 60000013 fffffffff

44.0230731 [<c07c8cc0>] (__irg_svc+0x40/0x70) from [<c005bf7c>] (msm_cpuidle

_enter+0x70/0x78>

44.031680] [<c005bf7c>] <msm_cpuidle_enter+0x70/0x78> from [<c056911c>] <cpu

idle_enter+0x14/0x18>

44.040592] [<c056911c>] <cpuidle_enter+0x14/0x18> from [<c0569690>] <cpuidle

idle_call+0x1e0/0x3c0>

```

#### **Atom Test Devices**

- Two types of boards:

- MinnowBoard

- Conga board

- Conga boards

- Use E620 embedded Atom processors

- 45nm parts

- MinnowBoards

- Use E640 embedded Atom processors

- 45nm parts

- Hobbyist Boards

Strong community for hacking – will be helpful for test needs

#### Atom E620 Power

- Since we're using an eval board, we're stuck with how the power system is laid out.

- We would need at least 7

power supplies and have

to tap into the board

connections then get

the power sequence right.

- We decided for the current approach to monitor the power draw of the board.

| Signal<br>Name | Nominal Voltage | Description                                                                                                                        |

|----------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------|

| vcc            | 0.75 - 1.15 V   | Processor Core Supply Voltage. Power supply is required for processor cycles.                                                      |

| VNN            | 0.75 - 0.9875 V | North Cluster Logic and Graphics Supply Voltage                                                                                    |

| VCCP           | 1.05 V          | Needed for most bus accesses                                                                                                       |

| VCCF           | 1.05 V          | Can be connected to VCCP                                                                                                           |

| VCCPQ          | 1.05 V          | Can be connected to VCCP                                                                                                           |

| VCCPDDR        | 1.05 V          | DDR DLL and logic Supply Voltage. Required for memory bus accesses.<br>Requires a separate rail with noise isolation.              |

| VCCPA          | 1.05 V          | JTAG, C6 SRAM, Fuse Supply Voltage. Needs to be on in Active or<br>Standby. This rail is connected to the VCCP rail.               |

| VCCQ           | 1.05 V          | Connect to 1.05 V                                                                                                                  |

| LVD_VBG        | 1.25 V          | LVDS Band Gap Supply Voltage. Needed for LVDS display                                                                              |

| VCCA           | 1.5 V           | Core PLL, core thermal sensor and sensor                                                                                           |

| VCCA180        | 1.8 V           | LVDS Analog Supply Voltage. Needed for LVDS display. Requires a separate rail with noise isolation.                                |

| VCCD180        | 1.8 V           | LVDS I/O Supply Voltage. Needed for LVDS display.                                                                                  |

| VCC180SR       | AON             | DDR2 Self Refresh Supply Voltage. Powered during Active,<br>Standby, and Self-Refresh states.                                      |

| VCC180         | 1.8 V           | DDR2 I/O Supply Voltage. Required for memory bus accesses. Cannot be connected to VCC180SR during Standby or Self- Refresh states. |

| VCCD           | 1.05 V          | Core supply voltage                                                                                                                |

| VCCDSUS        | 1.05 V          | Core suspend rail                                                                                                                  |

| VCCP33         | 3.3 V           | Legacy I/O and SDVO supply voltage                                                                                                 |

| VCCP33SUS      | 3.3 V           | 3.3 V suspend power supply                                                                                                         |

| VCCPSUS        | 3.3 V           | RTC suspend well voltage supply                                                                                                    |

| VCC33RTC       | 3.3 V           | RTC well voltage supply                                                                                                            |

| VCCD_DPL       | 1.05 V          | DPLL dedicated supply                                                                                                              |

| VCCA_PEG       | 1.05 V          | Used by PCIe* and SDVO                                                                                                             |

| VCCSFR_EXP     | 1.8 V           | PCIe* superfilter regulator                                                                                                        |

| VCCSFRDPLL     | 1.8 V           | SDVO superfilter regulator                                                                                                         |

| VCCSFRHPLL     | 1.8 V           | HPLL superfilter regulator                                                                                                         |

| VCCQHPLL       | 1.05 V          | HPLL quiet supply                                                                                                                  |

| VCCFHV         | 1.05 V          | Can be connected to VCCP                                                                                                           |

| VMM            | 1.05 V          | Connect to 1.05 V                                                                                                                  |

#### SEL in Atom E620

- Thinned parts to 80 μm

- Tested at TAMU with 25 MeV/amu Kr

- $-60^{\circ}$  Tilt LET<sub>eff</sub> = 57 & 75 (at sensitive region)

- Tested at BIOS screen of Conga™ eval board

- Board current @12V:

- At start of run 650-700 mA

- At end of run 500-700 mA

- No significant increase

- Changes correlated to lockup and reboot

#### **BACKUP**

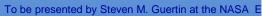

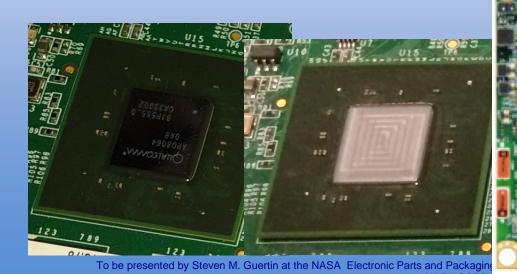

## A Packaging Example

We are finding some significant problems with some test boards, in terms of preparation for test...

## NASA

## A Packaging Example

We are finding some significant problems with some test boards, in terms of preparation for test...

# NASA

## Alternate Snapdragon Board

Another board design – IFC6410 is much easier to work with

We have established method to thin devices to enable testing with 25 MeV/amu cocktail at TAMU (~100 μm)

#### SEE Results – MSP430

- Tested MSP430F1612 for SRAM upsets

- Test program loads 2048 bytes with 0s or 1s (depending on pass number)

- Runs for general SEE observation used SEL protection, only LET 20 MeV-cm<sup>2</sup>/mg was tested

| LET (MeV-cm <sup>2</sup> /mg) | Condition | SBUs | ਰ (cm²/bit) |

|-------------------------------|-----------|------|-------------|

| 20                            | Nominal   | 66   | 4.2e-8      |

| 20                            | 3.6V      | 21   | 3.0e-8      |

| 20                            | 3.6V/55C  | 7    | 2.0e-8      |

Reduced cross section with Vcc expected; final row probably reflects low statistics as temperature should have no impact

#### SEFI in MSP430

- Observed 1 event where test program continued to operate but repeated error pattern observed.

- During runs without power-cycle (no SEL protection)

- Note observed asymmetry (~4:1) in 1 to 0 vs. 0 to 1 SBUs

- Passes writing all '1's resulted in:

- Oxfe observed in first 64 even addresses

- Went away after first few cycles

- SEFI turned into errors in all '0's passes:

- 0x01 observed in first 64 even addresses

- Continued through beam-induced reset

- Cross section for this event is about 1e-4cm<sup>2</sup> @ LET 20

- Also observed 1 reset event same cross section

#### Limitations of

#### Mobile/Cellphone Processor SEE Testing

- Test boards

- Packaging can be significant problem with preparation for heavy ions and TID

- Access to power generation and monitoring of current may be extremely limited

- Software/Operations

- These are complex SOCs

- We are targeting SOC test methods, but they may be too complex to evaluate without significant effort

## **Looking Forward**

- TID of PIC devices

- Testing of AT91SAM9G20

- Will try to work on this next year

- SEE Testing of Snapdragon 600 and Atom E620

- In the near future

- TID of Snapdragon and Atom

- Depending on potential benefit to users –

expected to easily meet most program needs

(>20krad)