2021 Edition

# **Chapter 10: Integrated Power Electronics**

For updates, visit <a href="http://eps.ieee.org/hir">http://eps.ieee.org/hir</a>

The HIR is devised and intended for technology assessment only and is without regard to any commercial considerations pertaining to individual products or equipment.

We acknowledge with gratitude the use of material and figures in this Roadmap that are excerpted from original sources. Figures and tables should be re-used only with the permission of the original source.

November 2021 Table of Contents

# Table of Contents

| Chapter 1: Heterogeneous Integration Roadmap:  Driving Force and Enabling Technology for Systems of the Future |    |

|----------------------------------------------------------------------------------------------------------------|----|

| Chapter 2: High Performance Computing and Data Centers                                                         |    |

| Chapter 3: Heterogeneous Integration for the Internet of Things (IoT)                                          |    |

| Chapter 4: Medical, Health and Wearables                                                                       |    |

| Chapter 5: Automotive                                                                                          |    |

| Chapter 6: Aerospace and Defense                                                                               |    |

| Chapter 7: Mobile                                                                                              |    |

| Chapter 8: Single Chip and Multi Chip Integration                                                              |    |

| Chapter 9: Integrated Photonics                                                                                |    |

| Chapter 10: Integrated Power Electronics                                                                       |    |

| Introduction                                                                                                   | 1  |

| Section I. Embedded Integrated Voltage Regulators                                                              | 7  |

| Section II: Power System-In-Package (SIP) Modules                                                              | 36 |

| Section III: Integrated High-Power Systems                                                                     | 83 |

| Section IV: Energy Harvesting                                                                                  | 7: |

| Chapter 11: MEMS and Sensor Integration                                                                        |    |

| Chapter 12: 5G, RF and Analog Mixed Signal                                                                     |    |

| Chapter 13: Co-Design for Heterogeneous Integration                                                            |    |

| Chapter 14: Modeling and Simulation                                                                            |    |

| Chapter 15: Materials and Emerging Research Materials                                                          |    |

| Chapter 16: Emerging Research Devices                                                                          |    |

| Chapter 17: Test Technology                                                                                    |    |

| Chapter 18: Supply Chain                                                                                       |    |

| Chapter 19: Cyber Security                                                                                     |    |

| Chapter 20: Thermal                                                                                            |    |

| Chapter 21: SiP and Module                                                                                     |    |

| Chapter 22: Interconnects for 2D and 3D Architectures                                                          |    |

| Chapter 23: Wafer-Level Packaging, Fan-in and Fan-out                                                          |    |

| Chapter 24: Reliability                                                                                        |    |

# **Chapter 10: Integrated Power Electronics**

#### Introduction

Although Power Electronics (PE) has far-reaching applications, the packaging technologies for PE circuits and systems are substantially common. This chapter focuses on the technologies for electronics packaging of the last few centimeters of electrical energy delivery to loads in high-performance computing, communications, mobile, automotive, industrial, medical and defense, with specific focus on System in Package (SiP) solutions that support loads and intellectual property (IP) blocks, such as CPU, GPU, FPGA, HBM and broader

Send corrections, comments and suggested updates to the TWG chair, using our HIR SmartSheet:

https://rebrand.ly/HIR-feedback

property (IP) blocks, such as CPU, GPU, FPGA, HBM and broader standalone loads in sensors, IoT and energy harvesting systems. As such, this Chapter is divided into four parts:

Section I. Embedded Integrated Voltage Regulators

- I.1. Summary

- I.2. Requirements

- I.3. Existing Solutions and Challenges

- I.4. Potential Solutions

- I.5. Required R&D

Section II: Power System-In-Package (SIP) Modules

- II.1. Power Module Topologies

- II.2. SIP Power Module Integration

- II.3. Potential Solutions and Required R&D

- II.4. Passive Components

- II.5. Roadmap

Section III: Integrated High-Power Systems

- III.1. Introduction

- III.2. Challenges in Circuit Architectures

- III.3. Challenges and Existing Solutions

- III.4. Power Module (High Voltage)

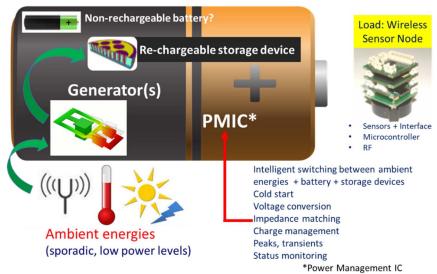

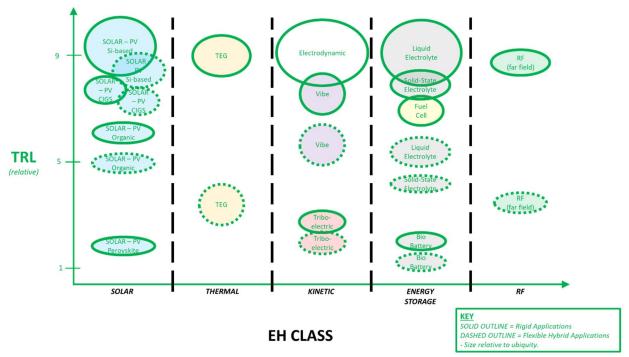

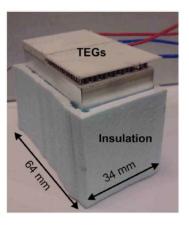

Section IV: Energy Harvesting

- IV.1. Introduction

- IV.2. Energy Harvester Related Integration Challenges

- IV.3. Power Management ICs (PMICs) for Energy Harvesting

- IV.4. Challenges and Solutions Roadmap

#### Contributors

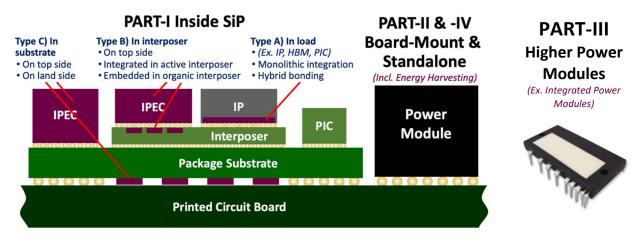

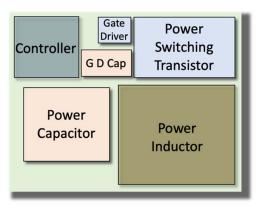

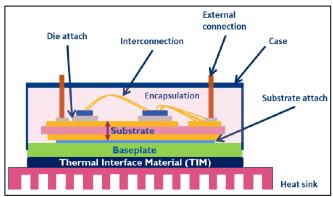

An Integrated Power Electronics Component (IPEC), as used in this chapter, is defined in Figure 1. The IPEC embodies the primary functions of power conditioning as represented by power switching semiconductors, passive capacitor and inductor energy storage elements, a semiconductor gate driver with associated capacitor, and a controller. The IPEC may be implemented in its entirety as a standalone system component as discussed in Sections II, III and IV, or partitioned with portions, such as the power switching and control, implemented within IPs while energy storage is implemented within lower-cost real estate, such as interposers, as discussed in Section I.

The identification of the existing electronics packaging technologies and future development needs build from Section I to Section III and, though there is substantial commonality among the packaging technology approaches, redundancy in discussions is limited. Therefore, it is recommended that the reader move sequentially from Section I to Section III. Section IV is an evolving topic and will be expanded in the next revision of the HIR with closer alignment to Section II. Also, Chapter 10 primarily focuses on ≤48V/100A power conditioning. However, the basic technologies are applicable to much higher power levels. A graphical description of the areas addressed by each Section is shown in Table 1. The highlighted "IPEC" is described below.

Figure 1. The "Integrated Power Electronics Component," IPEC, represents the electrical components and functions required for electronic conditioning of electrical energy delivered to the load(s). The IPECs may be partitioned and integrated in multiple ways within the System in Package, or be a standalone power electronic circuit for board-level power supply.

Heterogeneous Integration (HI) must be inclusive of power conditioning and delivery. While it is possible to supply power adjacent to one or more IP devices at the present time, such delivery will be impractical in the future to support the necessary speed and densities envisioned for heterogeneously integrated systems. Power delivery is one of the most critical elements that cross-cuts all application areas and clearly requires its own chapter in the roadmap. It is hoped that readers understand the PE packaging approaches, problems and technologies and can assimilate and morph solutions into their own IP packaging approaches to further deeper levels of integration.

Heterogeneous Integration also provides significant advantages to power electronics, as it permits integration of wide bandgap (WBG) power devices, e.g. GaN, with silicon control, logic, and memory devices, and with evolving passive devices. System-in-Package (SiP) and standalone power supply designers can use HI to address the primary challenges of power electronics: space, heat generation and electrical noise creation affecting communication, computation and sensor circuits. The challenges are divided into four categories: (1) reducing power converter size; (2) decreasing power path impedance; (3) delivering power efficiently; and (4) distributing clean, high-quality power at multiple voltages ranging from 48V to ≤1V to multiple levels of stacked packages. To reduce PE circuit size and path impedance, and achieve higher power processing densities, components need to be smaller and integrated closer together. Higher switching frequencies reduce component size and require closer location of components, which in turn reduces path impedance and radiated and coupled electrical noise. However, higher switching frequencies increase heating from increased power loss. Coupling the increased heating with densification greatly increases thermal densities and localized high-temperature regions. The densities are then limited by the practical worst-case junction temperatures of the semiconductors and longer-term reliability of packaging materials. The challenges are addressed in each Section of the Chapter specific to the packaging approaches addressed in that Section with the overarching focus on increasing frequency, reducing path impedance, increase efficiency and improve thermal management.

The reader is encouraged to contact any of the committee contributors to further discussions and answer questions. Also, please consider joining the committee to participate in the 2022 expansion and revision of this HIR Chapter by contacting Prof. Doug Hopkins, dchopkins@ncsu.edu, or Prof. Patrick McClusky mcclupa@umd.edu. Your input is greatly appreciated and needed.

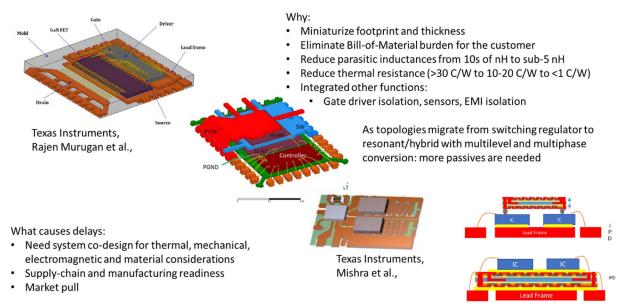

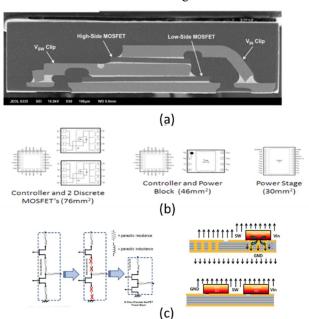

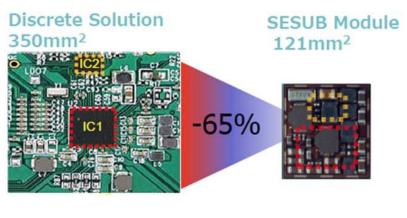

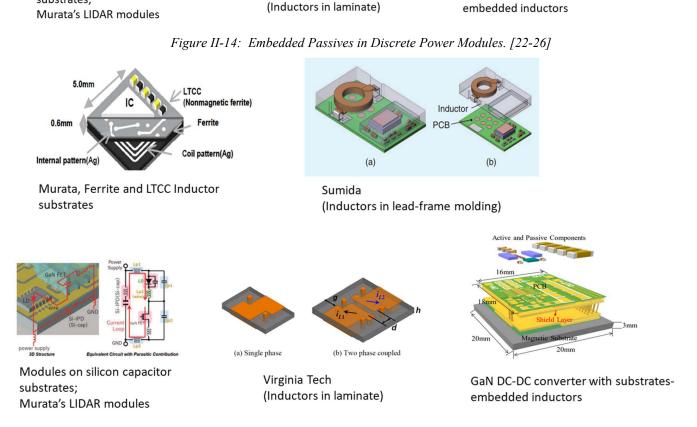

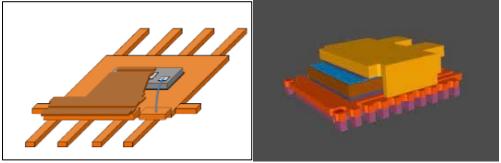

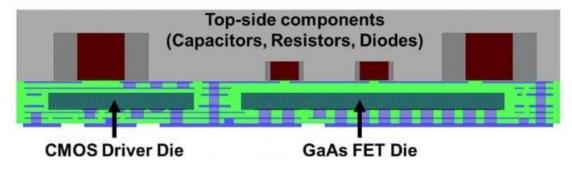

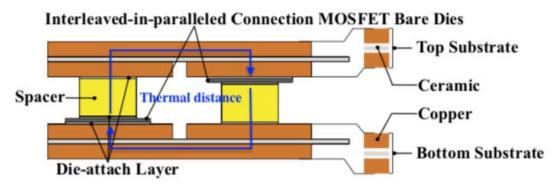

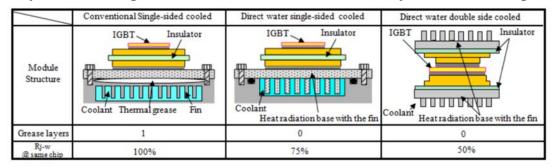

#### Topical Discussion #1 – 3D Heterogeneous Integration of Actives and Passives for Discrete Power Modules

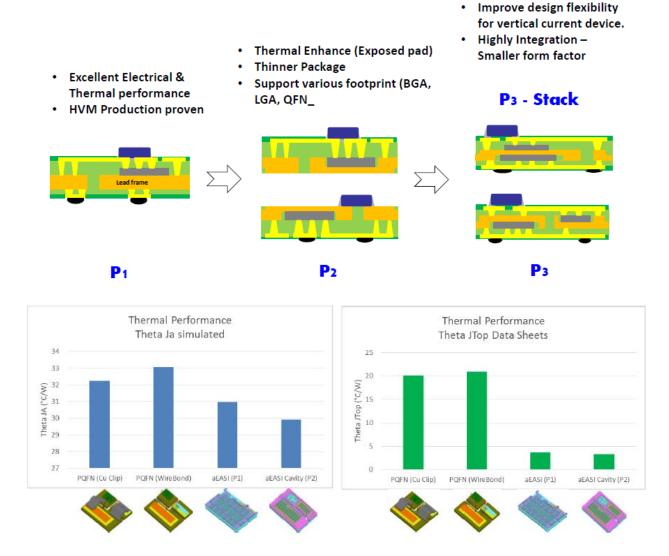

The power electronics community faces an escalating demand for efficient and integrated high-density power supplies for future computing needs. In order to meet this demand, power module technologies have made dramatic advances in the past decade, with advances in wide bandgap devices, innovative topologies, and more importantly with 3D power packaging technologies with advanced materials and process integration. Some of the advances include innovative multilevel and multiphase converter topologies with hybrid converters, high-density and thin passive components with higher efficiency at high frequencies, superior die-attach materials, thermal and thermomechanical reliability performance with high-Tg laminates, and high-power interconnects with innovative plated interconnects that can handle high currents. In spite of these advances, multiple challenges are foreseen in the future to meet the required targets of 1 W/mm³ for low-power (1-30 W) and 0.1 W/mm³ or >1000 W/in³ for higher power (30 – 300 W) at efficiencies of above 95% to minimize thermal management challenges. This requires advances on all fronts: Designs, Materials for Packaging, Passives, Heat Spreaders and Die-Attach amongst others.

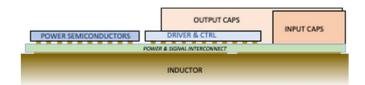

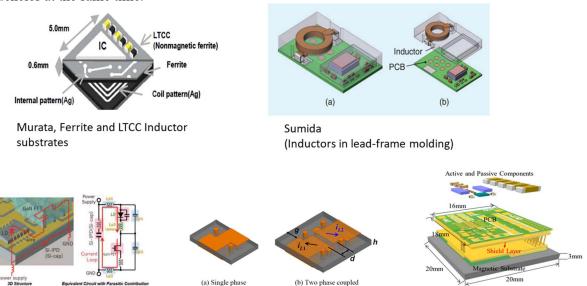

Need for thinner and vertically-integrated power delivery for efficient power supply is pushing the volumetric density and form-factors of future power modules. Higher switching frequency is critical for higher bandwidth, faster load transient response, and higher voltage scaling speed for better energy saving by dynamic voltage and frequency scaling. Higher current is required to meet the demand for higher functional integration. New topologies that can balance the voltage and current stresses while achieving higher switching speed and meeting the density, efficiency and electromagnetic compatibility with minimal EMI issues are required.

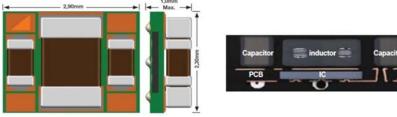

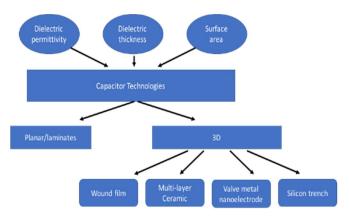

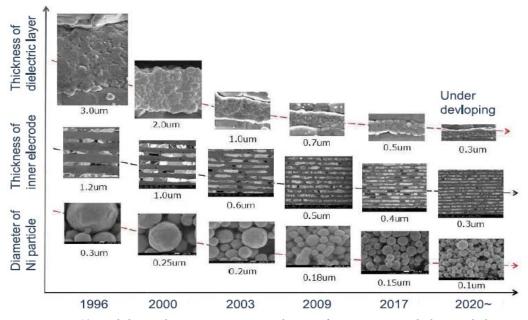

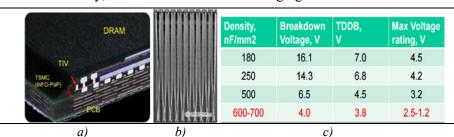

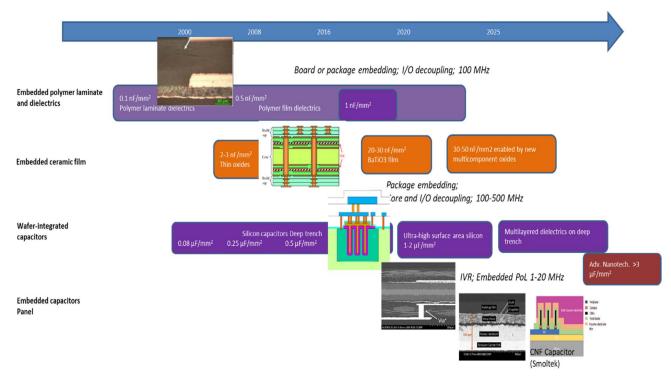

Surface assembly of passives is still the most common approach today in spite of its higher parasitics and lower volumetric efficiency and reliability challenges with solder interconnects. However, as the passives dominate the volume of the module, there is an increasing need to integrate passive component substrates. Both capacitors and inductors need to reach higher power-handling and efficiency in thinner form-factors for future power modules to meet the power density, size, weight and thickness targets. Because of their dominance in converter volume, passives may be used as the substrates themselves. Such examples to effectively utilize the substrate volume include the magnetic-embedded substrates and silicon trench capacitor substrate modules. Future magnetic materials are expected to deliver higher current/phase and higher frequencies with lower losses. Trench capacitors are becoming prevalent in replacing MLCCs because of their silicon scaling and integration advantages in spite of their limited volumetric densities with deep trench electrodes. Innovative nanoelectrodes will soon supersede trench capacitors in terms of performance.

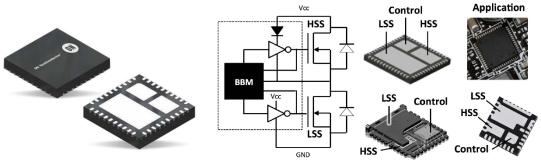

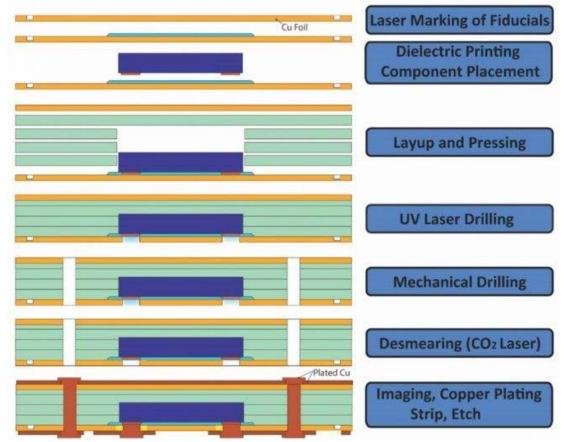

The prevalent approach for power modules is to embed active switches and controllers in a leadframe or laminate with embedding or direct-plated off-chip interconnects. In all the approaches, 3D components on package with innovative through-via copper interconnects and thinner components are the key. These include copper clip interconnects and plated through-laminate or through-mold vias. The package design challenge is to balance the often conflicting electrical, thermomechanical and thermal management requirements. For example, high currents dictate the use of large amounts of copper; however, such large copper induces tremendous thermomechanical stresses on the thinned WBG devices. The materials challenge is to ensure long-term reliability in a high-temperature environment for an extended period, given the large number of disparate materials and their interfaces required. This requires high-temperature polymer dielectrics as well as polymer laminates, and CTE-matched heat-spreaders that co-exist with devices for addressing the local hot-spots from WBG heat dissipation. Pressureless assembly of devices with superior die-attach materials will be another key requirement.

#### Topical Discussion #2 – Heterogeneous Integration of Embedded Integrated Voltage Regulators

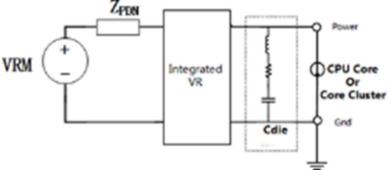

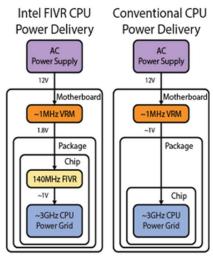

Fine-grain power management significantly improves energy efficiency (performance-per-watt) by up to 73%<sup>1,2</sup> by supplying the minimal voltage required at any given time to each load. It requires Integrated Voltage Regulators (IVRs) located in close proximity to the load to bypass the majority of the power distribution network (PDN) and associated impedance. Printed circuit board (PCB) mounted voltage regulators (VRs) cannot supply accurate voltages for fine-grain power management due to their high PDN impedance.<sup>3</sup> The way forward is PCB-mounted DC-DC converters that step down the system bus voltage to an intermediate voltage, which is then input to IVRs that perform voltage regulation.

The IVR challenges are to significantly reduce the interconnect resistance and parasitics between separately manufactured components (e.g., power transistors, gate drivers, controllers, capacitors and inductors), each made using their optimal manufacturing process, and to significantly reduce the z-dimension to enable integration in close proximity to the load. Monolithic integration cannot meet these IVR challenges.

Heterogeneous Integration (HI) refers to the integration of separately manufactured components into a higher-level assembly (System in Package – SiP) that, in the aggregate, provides enhanced functionality and improved operating characteristics.<sup>4</sup> A potential solution is for IVRs to employ two levels of HI to enhance functionality and improve operating characteristics:

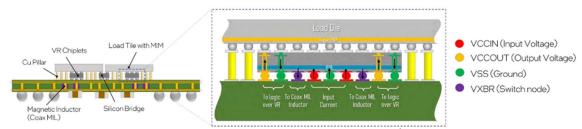

- 1) Disaggregate and tightly re-integrate separately manufactured components in an integrated power electronics component (IPEC) that provides multiple precisely regulated voltage outputs over a wide range (0.5-1.8V range) with increasing input voltage (3-5V),<sup>5</sup> current density (10-20A/mm²) and switching frequency (5-50MHz), with high reliability, low thermal resistance and low cost in an ultrathin z-dimension (100μm or less). Note: "IPEC" is synonymous with "VR chiplet," but does not have a chiplet standard interface.

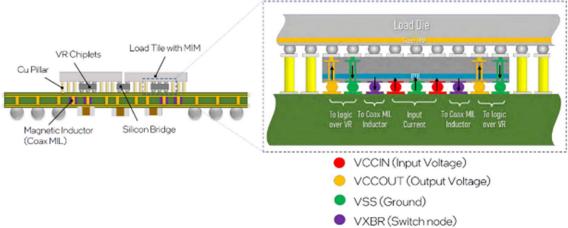

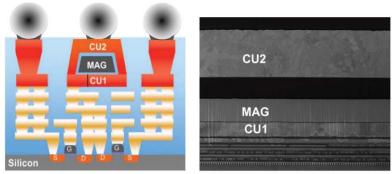

- 2) Integrate IPECs in SiPs immediately under the load die, as shown in Figure 2, similar to silicon bridges, to provide vertical current flow for each voltage rail to its load from the PCB through the package substrate to the load die, minimizing lateral current flow and associated parasitics and significantly improving the PDN and fine-grain power management. Capacitors may be integrated in the load die and/or in the IPEC. SuperMIM capacitors, comprised of thin layers of different high-k materials each of few Angstroms thick stacked in a repeating superlattice, provide a 5x increase in MIM capacitance. Inductors may be integrated into the IPEC or into the package substrate.<sup>6</sup>

Figure 2. IPEC integrated below the die<sup>6</sup>

Required R&D includes panel-level packaging (PLP) employing a portfolio of state-of-the-art heterogeneous integration technologies (e.g., pick-and-place, die bonding, micro-transfer printing, RDL, through-substrate vias, sort/test, etc.); Electronic Design Automation (EDA) tools and Process Design Kits (PDKs) for heterogeneous integration; optimization of separately manufactured components for IVRs, including power transistors, gate drivers, controllers, inductors and capacitors; integrating arrays of separately manufactured components in IPECs customized for advanced topologies; and stacking separately manufactured components.

#### References

- 1. V. De et al, <u>Fine-grain power management in manycore processor and System-on-Chip (SoC) designs, IEEE/ACM International Conference on Computer-Aided Design, 2015.</u>

- 2. <u>Power Management for Multicore Processors via Heterogeneous Voltage Regulation and Machine Learning</u>

Enabled Adaptation

- 3. P. Zou et al, <u>Powering 5G Era Computing Platforms the Road toward Integrated Power Delivery</u>, 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD), May 2019.

- 4. Heterogeneous Integration Roadmap, 2019 Edition, Chapter 1: HIR Overview and Executive Summary, page

- 5. K. Radhakrishnan et al, <u>Power Delivery for High Performance Microprocessors Challenges, Solutions and Future Trends,</u> IEEE Transactions on Components, Packaging and Manufacturing Technology, Volume 11, Issue 4, April 2021.

- 6. K. Radhakrishnan, <u>Power Delivery for Heterogeneous Systems</u>, Connecting Heterogeneous Systems Summit, September 2021.

### **Section I. Embedded Integrated Voltage Regulators**

Glossary of Terms

| BEOL             | Back End of Line                        | MIM              | Metal Insulator Metal                             |

|------------------|-----------------------------------------|------------------|---------------------------------------------------|

| BSPDN            | Back Side Power Distribution Network    | MOSFET           | Metal Oxide Semiconductor Field Effect Transistor |

| CoWoS-L          | Chip on Wafer on Substrate - LSI        | MTP              | Micro-Transfer Printing                           |

| CPU              | Central Processing Unit                 | PCB              | Printed Circuit Board                             |

| CZT              | Cobalt Zirconium Tantalum (CoZrTa)      | PCPU             | Power of CPU                                      |

| DBHi             | Direct Bonded Heterogeneous Integration | PDN              | Power Distribution Network                        |

| DC               | Direct Current                          | Pin              | Input Power                                       |

| DTC              | Deep Trench Capacitor                   | PLP              | Panel-Level Packaging                             |

| EMI              | Electro-Magnetic Interference           | PMIC             | Power Management Integrated Circuit               |

| EMIB             | Embedded Multi-chip Interconnect Bridge | P <sub>out</sub> | Output Power                                      |

| ESL              | Equivalent Series Inductance            | PSiP             | Power Supply in Package                           |

| ESR              | Equivalent Series Resistance            | PwrSoC           | Power System on Chip                              |

| FIVR             | Fully Integrated Voltage Regulator      | RDL              | Redistribution Layer                              |

| FPGA             | Field Programmable Gate Array           | $R_{mb}$         | Motherboard Resistance                            |

| FSPDN            | Front Side Power Distribution Network   | $R_{pkg}$        | Package Resistance                                |

| GaAs             | Gallium Arsenide                        | sFOCoS           | Stacking Fan-Out Chip on Substrate                |

| GaN              | Gallium Nitride                         | SiC              | Silicon Carbide                                   |

| GPU              | Graphics Processing Unit                | SiP              | System in Package                                 |

| HBM              | High Bandwidth Memory                   | SKU              | Stock Keeping Unit                                |

| HEMT             | High Electron Mobility Transistor       | SOC              | System on Chip                                    |

| HI               | Heterogeneous Integration               | VCCIN            | Input Voltage                                     |

| I <sub>out</sub> | Output Current                          | VCCOUT           | Output Voltage                                    |

| IPD              | Integrated Passive Device               | $V_{out}$        | Output Voltage                                    |

| IPEC             | Integrated Power Electronics Component  | VR               | Voltage Regulator                                 |

| IVR              | Integrated Voltage Regulator            | VRM              | Voltage Regulator Module                          |

| L/S              | Line / Space                            | VSS              | Ground                                            |

| LDO              | Low Drop-Out                            | VXBR             | Switch Node                                       |

#### I.1. SUMMARY

Fine-grained power management significantly improves energy efficiency (performance-per-watt) by up to 73%, 1,2 by supplying the minimal voltage required at any given time to each load. It requires Integrated Voltage Regulators (IVRs) located in close proximity to the load to bypass the majority of the power distribution network (PDN) and associated impedance. Printed circuit board (PCB) mounted voltage regulators (VRs) cannot supply accurate voltages for fine-grain power management due to their high PDN impedance. The way forward is PCB-mounted DC-DC converters that step down the system bus voltage to an intermediate voltage which is then input to IVRs that perform voltage regulation.

The IVR challenges are to significantly reduce the interconnect resistance and parasitics between separately manufactured components (e.g., power transistors, gate drivers, controllers, capacitors and inductors), each made using their optimal manufacturing process, and significantly reduce the z-dimension to enable integration in close proximity to the load. Monolithic integration cannot meet the IVR challenges.

The success of silicon integration at low power levels has been driven by the ability to integrate at competitive prices more complex systems than could be accomplished with discrete elements: multi-phase and distributed power conversion can be implemented with no significant added cost relative to single-phase converter architecture. Additionally, complex monitoring, protection, margining, etc., can be easily implemented when the whole system is contained in a single silicon device. Unfortunately, such capabilities do not easily extend to higher current/voltage levels, as silicon devices are limited by the process utilized, so that they cannot address the diverging requirements imposed by higher-power applications. Heterogeneous Integration (HI) enables the coexistence of differently optimized technology within an assembled unit, while still benefiting by reduced electrical distances, dense signal paths and high-current advanced interconnects, thus providing similar system-level benefits as are achieved by silicon integration.

Heterogeneous Integration (HI) refers to the integration of separately manufactured components into a higher-level assembly (System in Package – SiP) that, in the aggregate, provides enhanced functionality and improved

operating characteristics.<sup>4</sup> A potential solution is for IVRs to employ two levels of HI to enhance functionality and improve operating characteristics:

- Disaggregate and tightly integrate separately manufactured components in an integrated power electronics component (IPEC) that provides multiple precisely regulated voltage outputs over a wide range (0.5-1.8V range) with increasing input voltage (3-5V),<sup>5</sup> current density (10-20A/mm<sup>2</sup>) and switching frequency

- (5-50 MHz) and high reliability, low thermal resistance and low cost in an ultra-thin z-dimension  $(100 \mu m)$  or less). Note: "IPEC" is synonymous with "VR chiplet," but does not have a chiplet standard interface.

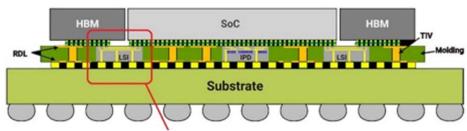

- Integrate IPECs in SiPs immediately under the load die (Figure 1), similar to silicon bridges, to provide vertical current flow for each voltage rail to its load from the PCB through the package substrate to the load die, minimizing lateral current flow and associated parasitics and significantly improving the PDN and fine-grain power management. Capacitors may be integrated in the load die. SuperMIM capacitors, comprised of thin layers of different high-k materials each of few Angstroms thick stacked in a repeating superlattice, provide a 5x increase in MIM capacitance. Inductors may be integrated in the package substrate.<sup>6</sup>

Figure I-1: IPEC integrate below die<sup>6</sup>

#### I.2. REQUIREMENTS

This section discusses the following requirements for IPECs:

- Modularity

- Fine-grain power management employing multiple buck regulators with fast transient response

- Low-impedance power distribution network (PDN)

- 0.5V to 1.8V output voltage

- 5-50MHz switching frequency

- 3-5V input voltage

- 10-20A/mm<sup>2</sup> output current density

- <100 μm thickness

- High system efficiency

- Ultra-low thermal resistance

- High reliability

- Cost effective: panel-level processing (PLP), high yield, known good die, modularity

Some of these requirements cannot be quantified in a "roadmap," because they must meet a "threshold" (i.e., be "good enough") which varies with application. For example, IVRs must have high reliability and be cost effective, but the specific reliability and cost targets are different for, say, mobile versus automotive applications. Similarly, IVRs must provide high efficiency, but specific efficiency targets depend upon the application whose goal is to maximize overall system energy efficiency (performance-per-watt) as opposed to IVR efficiency. Table 1 summarizes the IPEC requirements for IVRs. Over time the input voltage, switching frequency and output current density increases, the thickness decreases and output voltage range does not change much. In addition, as increasing numbers of phases are integrated in each IPEC, IPEC reliability improves and there's continuous improvement in reducing thermal resistance and cost.

Table I-1: IPEC Requirements for IVRs

| Matria                                      | Generation |         |        |         |  |

|---------------------------------------------|------------|---------|--------|---------|--|

| Metric                                      | 1          | 2       | 3      | 4       |  |

| Input voltage (V)                           | 3          | 3       | 5      | 5       |  |

| Switching Frequency (MHz)                   | 5 – 10     | 10 - 50 | 5 – 10 | 10 - 50 |  |

| Output current density (A/mm <sup>2</sup> ) | 10         | 20      | 10     | 20      |  |

| Output voltage (V)                          | 0.5 - 1.8  |         |        |         |  |

| Thickness (µm)                              | <100       |         |        |         |  |

PCB-mounted DC-DC converter requirements are discussed in Section II of this chapter. IPEC requirements for IVRs include the following:

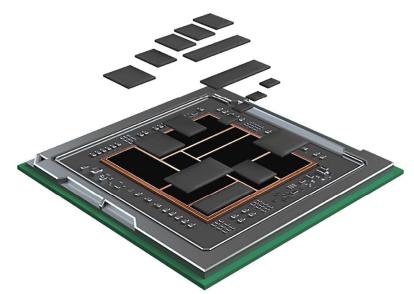

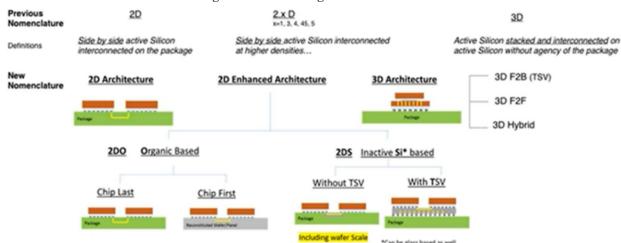

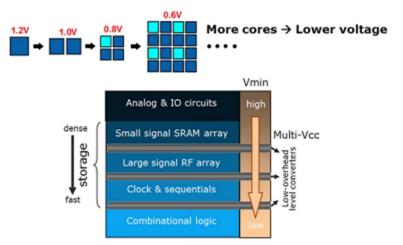

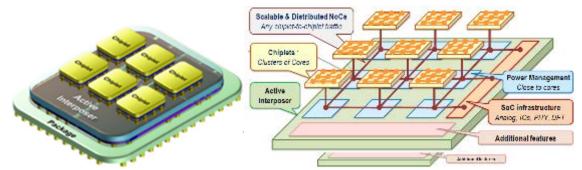

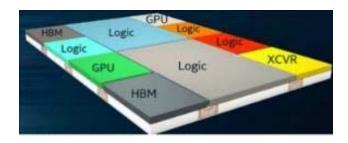

**Modularity**: IPECs are small, modular building blocks for integration in SiPs having multiple loads, each with different power delivery requirements. SiPs are increasingly disaggregated SoCs (Figure 2)<sup>7</sup> that integrate multiple CPU, FPGA, custom accelerator, cache, memory, I/O, networking and other "chiplets" (also knowns as "tiles" or "IP blocks"). The SiP power delivery requirements vary widely depending upon the application, which include high-performance computing and data centers, mobile, automotive, aerospace and defense, Internet of Things (IoT), and medical, health and wearables (discussed in other chapters in the Heterogeneous Integration Roadmap). The SiP body size ranges from <100mm² (10x10mm) to >10,000mm² (100x100mm); the number of load die range from 2 to >10; the number of voltage rails/phases range from <10 to >100; and the SiP current demand ranges from <10A to >1,000A. Similar to the general heterogeneous integration approach of re-using die, mix-and-matching them to build a family of different SiPs, the power delivery approach is to integrate a number of IPECs in different SiPs to meet specific current demand and voltage rail/phase count requirements and re-use IPECs in a wide range of SiPs for many different applications. IPECs may be readily integrated into a wide range of packaging technologies, including 2D, 2DO organic-based, 2DS inactive silicon or glass-based, and 3D architectures (Figure 4). Refer to Chapter 21 SiP and Module System Integration and Chapter 22 Interconnects for 2D and 3D Architectures of this Heterogeneous Integration Roadmap. The IPEC input voltage is 3-5V to meet applications which use both:

- 3-5V system buses, such as mobile and IoT

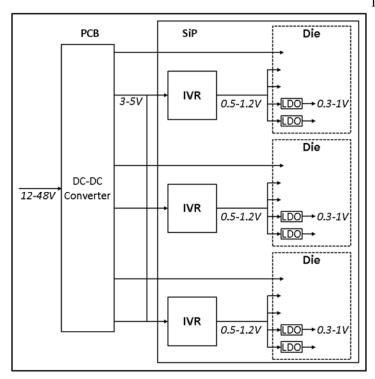

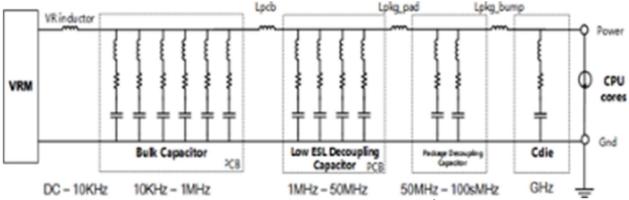

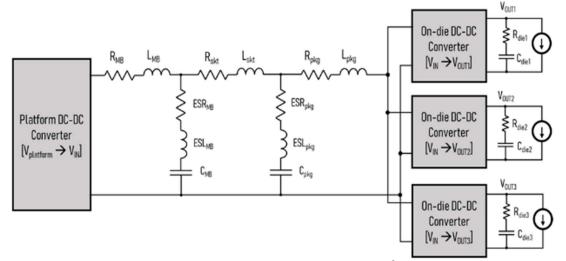

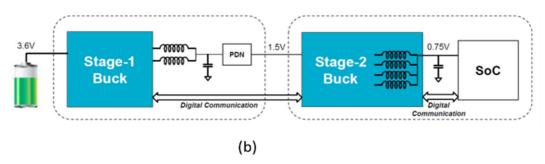

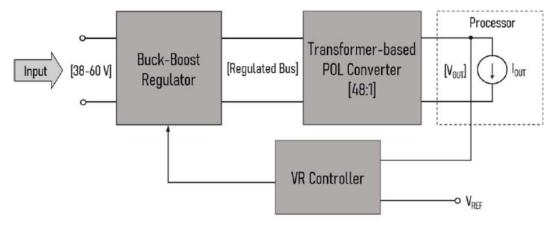

- Higher system bus voltages with multi-stage DC-DC conversion, since single-stage conversion is impractical with increasing input voltages and switching frequencies and decreasing output voltages. Multi-stage DC-DC conversion (Figure 3) uses one or more PCB-mounted DC-DC converters to step down a higher system bus voltage (12-48V) to an intermediate voltage (3-5V) input to the IVRs as discussed in Section II of this Chapter. The IVRs supply many 0.5-1.2V rails to the many loads in the SiP. For some rails, LDOs (low drop out linear regulators) integrated on the load die provide additional voltage regulation. The PCB-mounted DC-DC converter may still supply some rails directly to the load die. 10

Figure I-2: Disaggregated SoC<sup>7</sup>

Figure I-3: Multi-Stage DC-DC Conversion<sup>10</sup>

Figure I-4: Package Architectures<sup>8</sup>

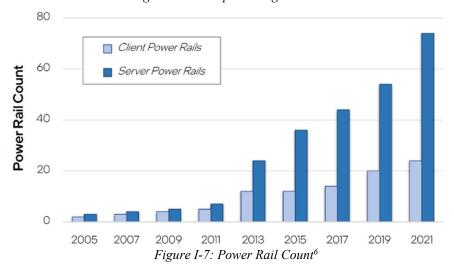

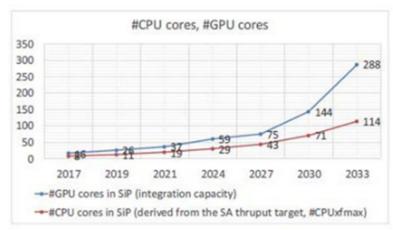

Fine-grain power management employing multiple buck regulators with fast transient response significantly improves energy efficiency by operating each load at its minimal voltage required at any given time. Load power dissipation is highly dependent on voltage, increasing more than quadratically with supply voltage when considering thermal degradation and leakage power in addition to dynamic power. For <10nm processes, power increases by 3% for every 10mV increase in supply voltage. Hence, precise voltage regulation is required because margins reduce the performance and power efficiency. Fast Dynamic Voltage Frequency Scaling (DVFS) changes the voltage and switching frequency individually for each load on the fly (Figure 5) in response to rapid changes in the workload or operating conditions (e.g., temperature and aging). DVFS varies the voltage between low levels to minimize power consumption during standby operation, to high levels to maximize performance during peak operation. DVFS requires many independent voltage regulators to supply multiple voltage domains with very accurate voltage levels, and fast transient response to multiple loads (Figure 6). The historical increase in power rail count (Figure 7) will continue with integration of an escalating number of cores (Figure 8). DVFS significantly increases the SiP performance and decreases its power consumption.

Adaptive Body Bias (ABB) is used to adjust the device body voltage to reduce leakage current. Whereas DVFS is effective to address dynamic power consumption, it is less effective in reducing leakage power; ABB is effective

in lowering leakage power consumption. ABB has been shown to reduce leakage current exponentially while DVFS reduces leakage linearly.<sup>15</sup> With ABB, a voltage is applied between the source or drain and the substrate to change the threshold voltage (Vth) of a transistor – forward-biasing to reduce Vth to provide a faster, leakier transistor, and reverse-biasing to increase Vth to provide a slower, less-leaky transistor. ABB can be applied to the whole chip or, with Fine-Grain Body Biasing (FGBB), can be applied separately to regions of a chip such as to each core on a multicore processor.<sup>16</sup>

Figure I-5: Fast Dynamic Voltage Scaling<sup>14</sup>

Figure I-6: Multiple Voltage Domains<sup>1</sup>

Figure I-8: IRDS projection of number of CPU and GPU core in an 80mm<sup>2</sup> area<sup>3</sup>

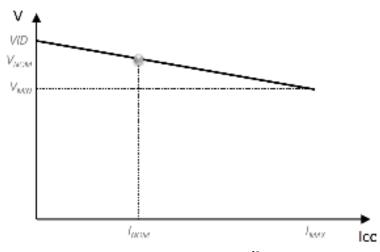

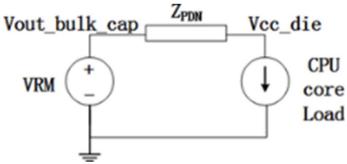

Low impedance power distribution network (PDN): Low-impedance PDNs are needed to supply loads with voltages within a tightly controlled operating range, and this need is escalating with advanced CMOS nodes having the operating voltage in close proximity to threshold voltage. For example, a 20mV variation is a much larger percent variation when the operating voltage is 500mV versus 900mV. 17 Load current consumption can change dramatically from cycle to cycle, and spikes in current draw cause the voltage to droop.<sup>3</sup> Voltage overshoots and undershoots must be minimized during load changes and input power supply fluctuations. A voltage that is too low can cause timing issues resulting in failure, and a voltage that is too high results in excessive power consumption and compromised reliability. There are penalties for adding generous guardbands.<sup>17</sup> The voltage regulator's bandwidth and the PDN's impedance<sup>18</sup> determine the amount of voltage droop in response to a load change. A steeper load line (Figure 9) results in significant power loss due to an operating voltage that is significantly higher than the minimum voltage required.<sup>19</sup> The PDN's impedance must be kept low across a wide range of frequencies by minimizing inductive, capacitive and resistive parasitics, and its voltage gradient across spatially distributed voltage domains must be minimized. In addition, routing losses in the path from the voltage regulator to the load must be minimized since they have a quadratic dependence on current. PCB-mounted VRs cannot supply accurate voltages for finegrain power management due to their high PDN impedance (Figure 10 and Figure 11), so the way forward is PCBmounted DC-DC converters that step down the system bus voltage to an intermediate voltage, which is then input to IVRs that perform voltage regulation and bypass the majority of the PDN impedance (Figure 12 and Figure 13). Since IVRs supply low voltage (<1V) and high current (10's to 100's of amps), the IVR-to-load PDN must have minimal series resistance and inductance.

Figure I-9: Load Line<sup>20</sup>

Figure I-10: High Impedance PDN Due to External VRM<sup>3</sup>

Figure I-11: PDN With External VRM<sup>3</sup>

Figure I-12: IVRs bypass PDN bottleneck<sup>3</sup>

Figure I-13: IVRs Supplement VRMs<sup>5</sup>

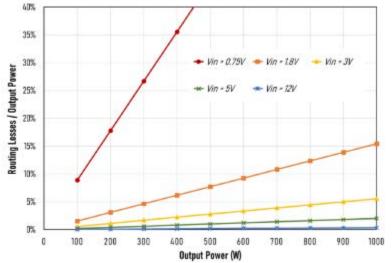

**Input voltage** in the 3-5V range<sup>5</sup> is needed to balance being low enough to support high switching frequency and high enough to reduce the PDN's routing loss for support of escalating output power (Figure 14) and reduce the

number of power/ground pins, which compete with I/O. Additional factors that determine the optimal IVR input voltage include the proximity of the first stage DC-DC converter to the IVR and whether the first stage is regulated versus unregulated and centralized versus distributed.<sup>21,22</sup>

Figure I-14: Routing Losses<sup>5</sup>

**Switching frequency** in the 5-50MHz<sup>5</sup> range is needed to balance being low enough to support low duty cycles (output voltage divided by input voltage) and high efficiency, and high enough to reduce the size of the inductors and capacitors and to increase the control loop bandwidth (which is approximately 10% of switching frequency), improving transient response. Low-bandwidth VRs require additional decoupling capacitors to make up for their slow response time.

**Output voltage range** in the 0.5V to 1.8V range is needed to support SiPs integrating a diversity of load die made using different process nodes and having different voltage requirements. Input voltages of 0.5V to 1.2V are typical for digital loads (the lower voltages to minimize power consumption during power-saving operating modes and the higher voltages to maximize performance during peak operating modes) and 1.2V to 1.8V for analog loads.

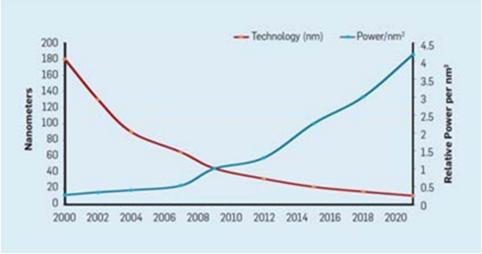

Output current density in the 10-20A/mm<sup>2</sup> range is needed to keep up with escalating SiP power density. The power density trend in the last decade (Figure 15) will continue with CMOS scaling to 5nm, 3nm, 2nm nodes and beyond and heterogeneously integrating many diverse die in large-area (>100x100mm) substrates. High-end SiPs will draw more than 1,000A in the near future, driving the need to achieve high current density for other IVR components.

Figure I-15: Transistor scaling and chip power density trend<sup>3</sup>

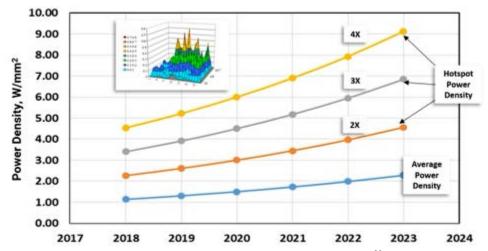

Ultra-low thermal resistance is needed to facilitate heat removal, which is a major challenge and limiting factor, since (i) IVRs share the SiP's limited thermal envelope with the load die, and (ii) IVRs having high current densities

are located in close proximity to loads having high power densities, which are forecasted to increase to >2W/mm<sup>2</sup> average with >9W/mm<sup>2</sup> hotspots (Figure 16).<sup>23</sup> IVRs must not exacerbate these hotspots and will require thick copper interconnects to minimize thermal resistance.

Figure I-16: Load Die's Power Density Trend<sup>23</sup>

High system efficiency is needed to maximize SiP performance-per-watt, which is the key performance metric, as opposed to maximizing the IVR efficiency. Counter-intuitively, IVR efficiency that is lower than PCB-mounted VR efficiency may be acceptable due to IVRs improving fine-grain power management and the PDN network. The voltage accuracy (i.e. minimized voltage variation) at the on-die power grid has far greater impact on energy efficiency than VR conversion efficiency,<sup>24</sup> and the reduction in PDN routing losses can be more than enough to offset the voltage regulator's conversion losses. For example, a 97% efficient first stage followed by an 88% efficient second stage voltage regulator (i.e., 85% combined efficiency) provides higher system efficiency than a single stage 90% voltage regulator (Table 2). In addition, SiP performance-per-watt can be increased with short-duration peak current operating modes for individual loads. Due to the short duration, IVR efficiency is not important during these peaks. (The challenges is maintaining high reliability during peak operation). Lastly, system energy proportionality (whereby energy consumption scales with workload) is important and requires multi-phase IVRs with phase shedding, whereby IVR phases are progressively turned on/off depending upon workload.

Table I-2: System Efficiency - Single Stage PDN vs. Dual Stage PDN<sup>5</sup>

| Parameter                                                               | Single<br>Stage PDN    | Dual Stage<br>PDN      |

|-------------------------------------------------------------------------|------------------------|------------------------|

| CPU Power (P <sub>CPU</sub> )                                           | 100 W                  | 100 W                  |

| Output Voltage (Vout)                                                   | 1 V                    | 1 V                    |

| Output Current (I <sub>OUT</sub> = P <sub>CPU</sub> /V <sub>OUT</sub> ) | 100 A                  | 100 A                  |

| VR2 Input Voltage (V <sub>1N2</sub> )                                   | 1 V                    | 3V                     |

| VR2 Efficiency (η <sub>2</sub> )                                        | 100%                   | 88%                    |

| VR2 Input Power ( $P_{IN2} = P_{CPU} / \eta_2$ )                        | 100 W                  | 113.6 W                |

| PDN Current ( $I_{PDN} = P_{IN2}/V_{IN2}$ or $I_{OUT}$ )                | 100 A                  | 37.9 A                 |

| Package Resistance (R <sub>PKG</sub> )                                  | $0.5~\mathrm{m}\Omega$ | $0.5~\mathrm{m}\Omega$ |

| Package Losses ( $P_{PKG} = I_{PDN}^2 \times R_{PKG}$ )                 | 5 W                    | $0.7~\mathrm{W}$       |

| MB Resistance (R <sub>MB</sub> )                                        | l mΩ                   | $1~\mathrm{m}\Omega$   |

| MB Losses $(P_{MB} = I_{PDN}^2 \times R_{MB})$                          | $10\mathrm{W}$         | 1.4 W                  |

| Routing Losses (P <sub>R</sub> P <sub>PKO</sub> + P <sub>MB</sub> )     | 15 W                   | 2.1 W                  |

| VR1 Output Power ( $P_{OUT1} = P_{1N2} + P_{R}$ )                       | 115                    | 115.7 W                |

| VR1 Efficiency (η <sub>1</sub> )                                        | 90%                    | 97%                    |

| VR1 Input Power $(P_{IN1} = P_{OUT1}/\eta_1)$                           | 127.8 W                | 119.3 W                |

| System Efficiency $(\eta_{sys} = P_{CPU}/P_{IN1})$                      | 78.3%                  | 83.8%                  |

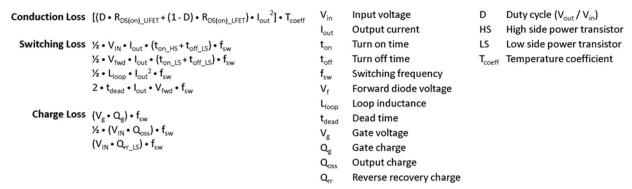

IVR power loss is due to conduction loss, switching loss and charge loss (Figure 17). The challenges for 3-5V input, high current density IVRs are to (i) minimize the conduction loss by minimizing the power transistor's on-

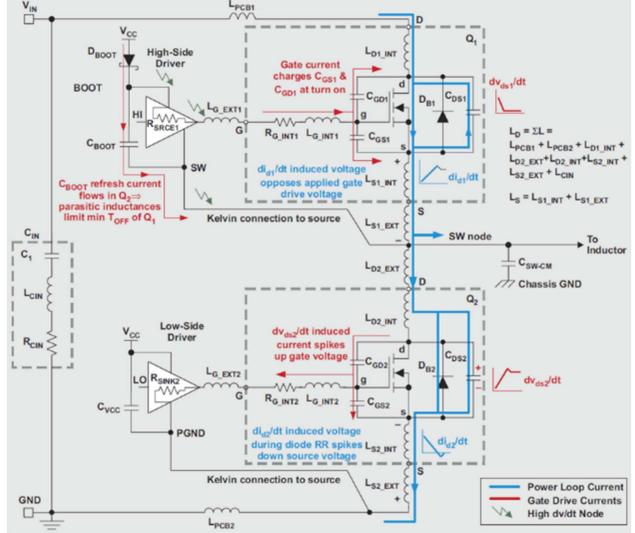

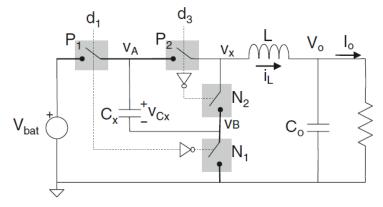

resistance and interconnect resistance, and (ii) minimize the switching loss by minimizing the parasitics in the gate drive and power loops (Figure 18)<sup>25</sup> to minimize the turn on/off time, dead time and loop inductance. The interconnects are a major limiter, because to achieve high efficiency along with high current density requires integrating in a minimal footprint (i) high current interconnects (VCCIN, VCCOUT, VSS, VXBR as shown in Figure 1), (ii) gate distribution with ultra-low parasitics, and (iii) control, protection and monitoring interconnects to each phase. Charge loss is moderate with 3-5V voltage input and moderate switching frequency but becomes substantial with increasing input voltage and switching frequency. The tradeoff is between minimizing conduction loss versus switching loss, since increasing the power transistors' gate periphery reduces its on-resistance (conduction loss) but increases its switching loss and vice versa.

Figure I-17: Buck Regulator Power Loss Equations

Figure I-18: Parasitics in Gate Drive and Power Loops<sup>25</sup>

**High reliability** is needed to ensure operation at all times in the safe operating area, which is typically well below the rated voltage, maximum allowable junction temperature and maximum allowable current density, and meet reliability standards, such as IPC-9592B: Requirements for Power Conversion Devices for the Computer and Telecommunications Industries. High reliability requires using proven materials and manufacturing processes and employing structures that minimize stresses and coefficient-of-thermal-expansion (CTE) mismatches. **Low cost** is necessary for IPECs to be used in a wide range of SiPs and applications and not limited to only high-performance applications that can afford price premiums. Low cost requires:

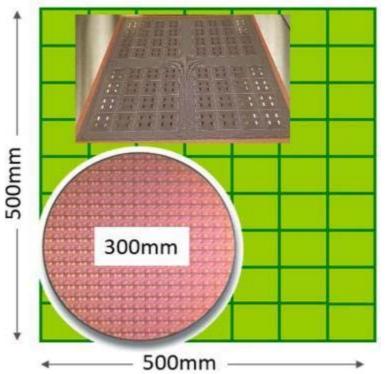

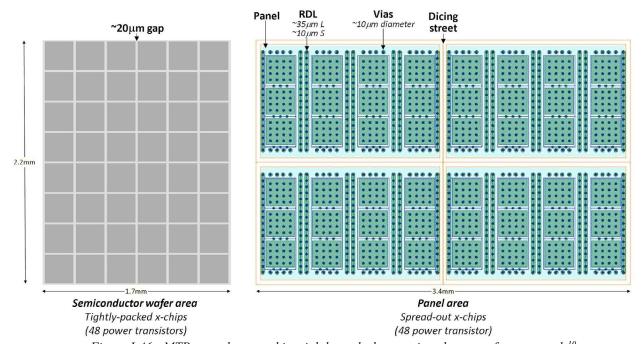

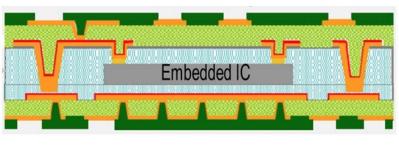

- Panel-level processing (PLP): Embedded Chip or Fan-Out are promising technologies to integrate the separately manufactured IVR components into an IPEC that can be mounted within the SiP. Manufacturing these IPECs on panels that have three-times the area of wafer-level processes (Figure 19)<sup>28</sup> and use inexpensive panel area rather than expensive semiconductor area for the high-current interconnects, are required to meet low costs. Historically, high-performance "compute" applications (e.g., CPUs, GPUs, FPGAs and HBMs) have been the market drivers for heterogeneous integration. These applications require very high interconnect density (to increase bandwidth, decrease latency and improve power efficiency) and ultra-fine (<1μm/1μm) line width/space (L/S) design rules. PLP challenges for the compute applications are (i) providing ultra-fine L/S and (ii) since each panel contains a large number of die, very high volumes are required to make the business case for PLP manufacturing facilities. In contrast to compute applications, IPECs require interconnects having much higher current density but lower interconnect density, so coarse (>10μm/10μm) L/S design rules are sufficient. IPECs are an attractive market driver for PLP since they do not require ultra-fine L/S and address large markets having very high volumes.

- **High yield:** Complex HI SiPs will require IPECs with multiple IVRs, each having multiple separately manufactured active and passive components. Utilization of multicomponent PLP to achieve low costs can only be successful with high IPEC module yields. Since a complex IPEC will have multiple bare chips as well as passive devices, these components must have intrinsically high yields prior to subsequent integration. In addition, the integration process must have high yields and must use mature, well-proven materials and manufacturing processes and relaxed design rules.

- Known good die: IPECs need to be tested and binned prior to integration in the SiP.

Figure I-19: Dimensional difference between 300mm wafer and 500x500mm panel<sup>28</sup>

**Ultra-thin z-dimension:** The IPEC must be thin ( $<100\mu m$ ) to facilitate integration in close proximity to the load die in a wide range of package architectures.

#### I.3. EXISTING SOLUTIONS AND CHALLENGES

Existing solutions and their challenges for meeting the requirements described above are:

Converter topology technologies include:

- Low-drop out (LDO) linear regulators, which are limited to regulating the output voltage close to the input voltage since their efficiency is proportional to output voltage divided by input voltage.

- Switched-capacitor converters, which use capacitors for energy storage, are well-suited for a fixed input to output voltage conversion ratio but suffer from low efficiency when the conversion ratio deviates from the optimal.

- Switched-inductor voltage regulators (buck converters),<sup>29</sup> which use inductors as the energy storage element, are widely used for regulating an output voltage that is much lower than the input voltage.

- Advanced topologies, including multi-level buck converters and hybrid and resonant switched-capacitor converters,<sup>30</sup> improve performance and reduce voltage requirements but require an increased number of power transistors, gate drivers and passive components.

**PCB-mounted VRs** have historically been used for the vast majority of today's VR applications, but they are inadequate for supplying accurate voltages for fine-grain power management<sup>3</sup> due to their high PDN impedance which adds tens of millivolts extra voltage guard band, limited number of power rails and slow transient response. PCB-mounted VRs, discussed in more detail in Section II, include the following:

- Discrete power components (i.e., power transistors, gate drivers, controllers, capacitors and inductors), each separately manufactured using their optimal manufacturing process, are mounted on the PCB. This solution is very low density due to the number of discrete components and low (<1MHz) switching frequency, resulting from high parasitics between the components and high switching loss, requiring bulky passive components.

- Power management integrated circuits (PMICs) monolithically integrate power transistors, gate drivers and controllers along with a host of application-specific power management functions. Their inductors and capacitors are mounted on the PCB. Given the conduction versus switching loss tradeoff, PMIC's switching frequency decreases (requiring bulky passive components) as their input voltage and/or output current increases. PMICs for smartphones typically support 2.8-5.5V input voltage with multiple phases and independent outputs, and they can support up to approximately a total 20A output current with <1MHz switching frequency or up to 10 MHz switching frequency with <1A output current. PMICs for up to 48V input support low output current at <1MHz.

- Integrated regulators (like PMICs) monolithically integrate power transistors, gate drivers and controllers, and their inductors and capacitors are assembled on the PCB. Since they target a wide range of applications, they (unlike PMICs) do not integrate application-specific power management functions. Given the conduction versus switching loss tradeoff, they support high output current at low switching frequency or vice versa.

- Power stages integrate separately manufactured power transistor and driver die in a package. Their

controller, inductors and capacitors are mounted on the PCB. High-current applications parallel

multiple power stages in a multi-phase buck converter. They are optimized to provide high output

current and high efficiency, so their switching frequency is typically less than 1MHz, requiring bulky

inductors and capacitors.

- Power Supply in Packages (PSiPs) integrate controller, power transistor, and gate driver die along with the inductors and some of the capacitors in a package (with additional capacitors mounted on the PCB). Existing PSiPs range from small packages which support low input voltage and output current to bulky packages which support higher input voltage and output current. PSiPs can be paralleled to support higher output current. Given the conduction versus switching loss tradeoff, they support high output current at low switching frequency or vice versa.

Challenges include simultaneously increasing both the switching frequency to 5-50MHz and current density to  $10\text{-}20\text{A/mm}^2$  while also significantly reducing the z-dimension to less than  $100\mu\text{m}$ . Incremental improvements in PCB-mounted VR technology cannot meet these challenges, so new disruptive technology is needed.

**Monolithic integration** technology is well-suited for low-voltage power components, such as controllers and capacitors, but poorly suited for integrating power components that require higher voltages and current densities. Monolithic integration technologies include the following:

- Integrating LDOs on the load die are well-suited for rails where the output voltage is close to the input voltage but have unacceptably low efficiency for large voltage step-downs.

- Integrating switched-capacitor converters on the load die are well-suited for rails where the output voltage is an optimal ratio of the input voltage but have unacceptably low efficiency if the ratio deviates from the optimal.

- Integrating buck regulators on the load die are limited to low (<2V) input voltage and low current density due to advanced CMOS processes' ultra-thin gate oxide.

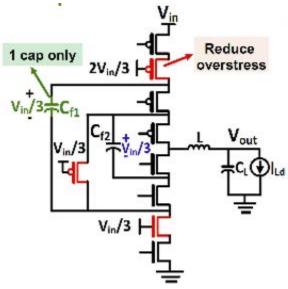

- Integrating in a power supply on chip (PwrSoC) all the different components for a buck regulator (i.e., controller, gate drivers, power transistors and passives), which is also limited to (i) low voltage for high switching frequency and (ii) low current density. Examples include a 100 MHz 2-stage PSiP implemented in 130nm CMOS which provides 87% efficiency for 1.5V input, 1V output and 1A output per phase (4 phases) with a 1.5A/mm² current density;³¹ a 100MHz IVR PMIC implemented in 40nm CMOS with integrated thin-film inductors which provides 82% peak efficiency for 1.8V input and 0.85V/20A/16-phase output in a ~15mm² chip scale package;³² and a 50MHz 3-level buck converter implemented in 65nm CMOS which provides 50% efficiency for 5V input and 0.6V, 0.7A output in a 1.875x1.25mm die.³³

The challenge is to significantly increase current density for 5V input and high switching frequency.

#### Power transistor technologies include the following:

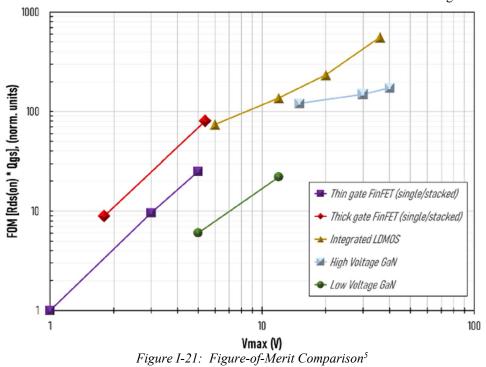

• MOSFETs (metal oxide semiconductor field effect transistors) made with advanced CMOS processes have an excellent on-resistance • gate charge figure of merit (FoM) due to their short gate length, so can support high switching frequency; however, their thin gate oxide limits their input voltage to approximately 1V. Increasing the input voltage to 1.8V requires a cascade configuration (Figure 20) which increases conduction loss, limiting current density and making it impractical to further increase input voltage. Power MOSFETs employ a laterally or vertically diffused region near the drain to support higher voltage and are widely used in PCB-mounted VRs. Given the conduction versus switching loss tradeoff, lateral MOSFETs for 3-5V input can support high switching frequency (up to 10MHz) but only for low output current (<1A). To supply higher output current, their switching frequency is low (typically <1MHz). Vertical MOSFETs support higher input voltage and output current but also with typically <1MHz switching frequency. MOSFET performance is asymptotically reaching its limit.

Figure I-20: Cascode configuration for IVR power stage<sup>3</sup>

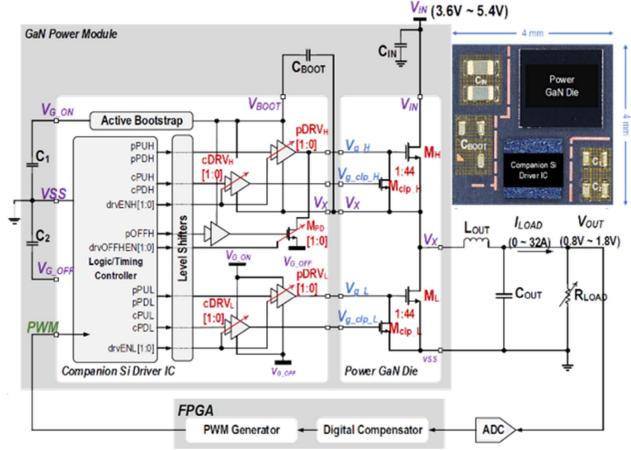

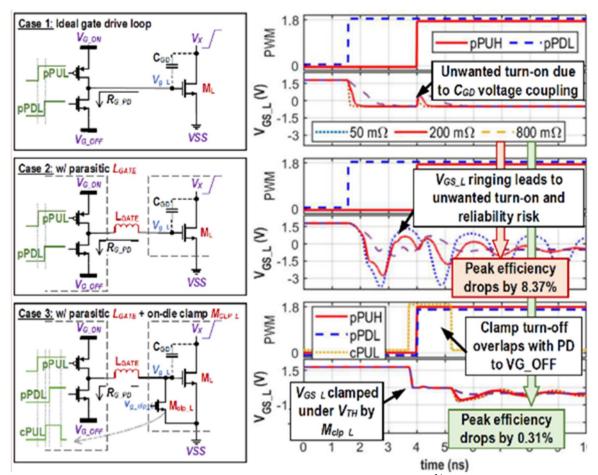

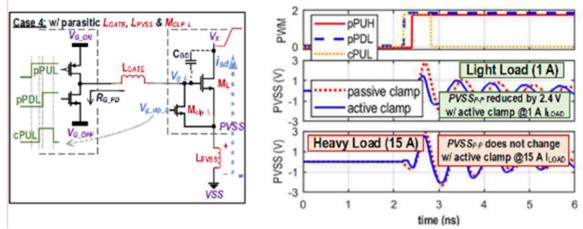

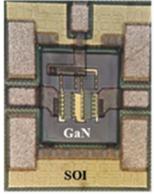

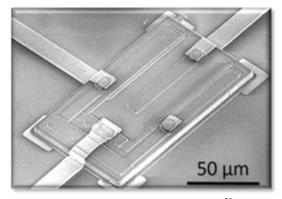

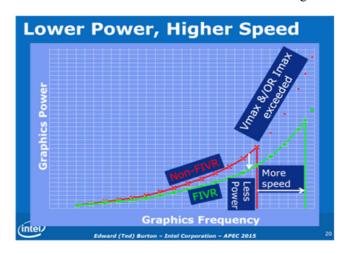

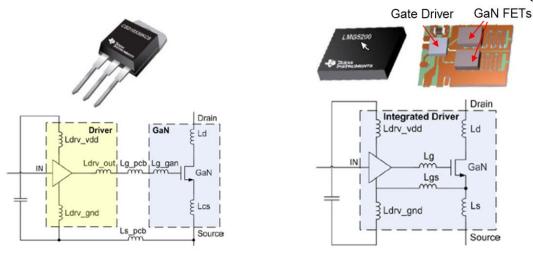

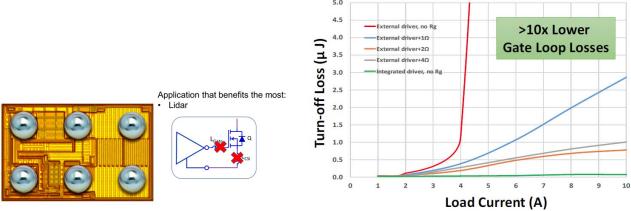

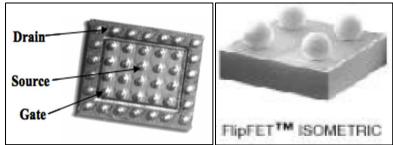

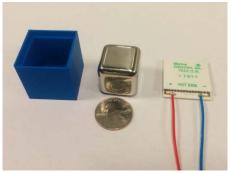

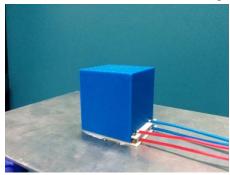

• GaN HEMTs (gallium nitride high electron mobility transistors) provide a superior FOM compared to MOSFETs (Figure 21), so are increasingly used in PCB-mounted medium voltage (100V+) DC-DC converters for applications including consumer power adapters, audio, wireless charging, motor drives and server/telecom power supplies. GaN-on-silicon HEMTs offer the potential to be manufactured in trailing-edge silicon fabs, extending the useful life of these fabs. A 5V, 10 MHz buck regulator that copackages a GaN power transistor die, a silicon gate drive die and capacitors for the power stage in a 4x4mm² package (Figure 22) supplies 22A output current with 83% efficiency for 5V-to-1V (Figure 23). Roughly 50% of the low-side power transistor's resistance is due to the device itself and the other 50% is due to the die metal, package and board interconnects (Figure 24). The challenges are to (i) significantly increase the power stage's current density from 1.4A/mm² (22A/16mm²) to 10-20A/mm² and increase its efficiency and/or switching frequency by reducing the interconnect resistance, gate routing parasitics (Figure 25) and power routing parasitics (Figure 27) and (ii) significantly reduce the power stage's z-dimension.<sup>34</sup>

Figure I-22: 5V, 10MHz GaN Buck Regulator Power Stage<sup>34</sup>

15 10 20 Figure I-23: 5V, 10MHz Buck Regulator Efficiency<sup>34</sup>

5V - 1V (10MHz)

I<sub>load</sub> (A)

November 2021

94%

90%

86%

82%

78%

74%

70%

Figure I-24: Resistance Split of Low-Side Power Transistor<sup>34</sup>

Total (sim.)

$2.57m\Omega$

0.5

25

Figure I-25: Impact of Gate Routing Resistance<sup>34</sup>

Figure I-26: Impact of Power Routing Parasitics<sup>34</sup>

- GaAs pHEMTs (gallium arsenide pseudomorphic high electron mobility transistors), a mature technology widely used for RF applications, have superior FOM compared to MOSFETs for low-voltage applications. GaAs-based power stages have the same challenges as described above for GaN-based ones (i.e., reducing the interconnect resistance, gate and power routing parasitics and z-dimension, as opposed to improving intrinsic device performance). GaAs high-volume production currently uses 150mm wafers, although it's possible to scale GaAs to larger wafers. Few, if any, companies are presently working to commercialize use of GaAs pHEMTs for power conversion.

- **SiC** (silicon carbide) serves high voltage 600V to 3,300V applications, such as electric vehicle drive trains and charging, solar inverters, rail traction, servo drives and AC power supplies. SiC does not provide an advantage over MOSFETs for 3-5V input voltage.

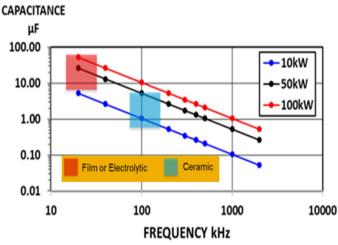

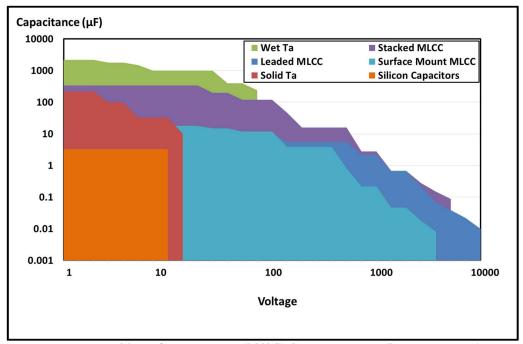

**Integrated capacitor** technologies include electrolytic capacitors, ceramic capacitors and silicon capacitors and are discussed in detail in Section II of this chapter.

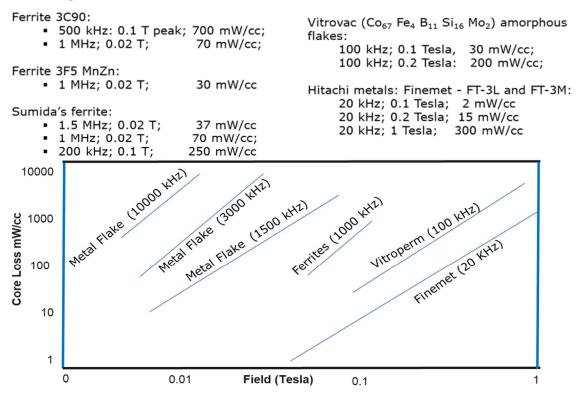

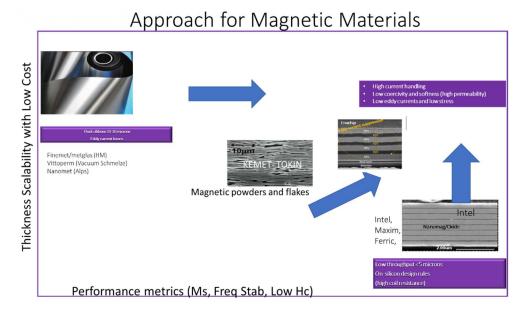

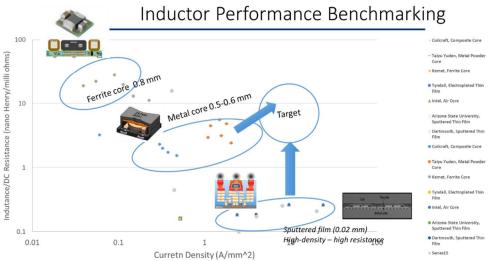

**Integrated inductor** technologies which are currently in commercial products include the following (Table 1).<sup>36</sup> The challenges associated with the current version of each technology are also outlined.

- Discrete magnetic composite-core inductors as single inductor or in a magnetic inductor array attached using surface mount technology on the land side of the package substrate (Figure 27). Key challenges for this technology are the need for lower height profile and the need for improved inductance vs dc resistance this parameter should be measured in nH per milliOhm.

- Embedded, air-core inductors (Figure 28) integrated in the organic microprocessor/SOC package substrate. As the number of inductors required increases for more complex granular power requirements (i.e. more separate loads on SOC or processor chip), this technology will require a reduced footprint for each inductor this could compromise the benefit of the solution due to increased dc resistance and poorer nH/mOhm.

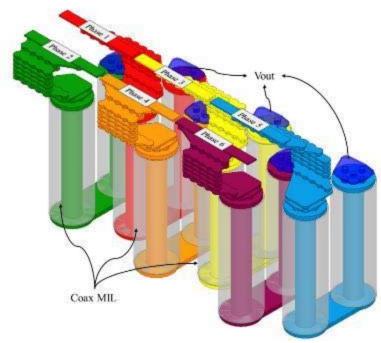

- Coaxial magnetic composite core inductors integrated in the package substrate (Figure 29).

- Air-core inductors on silicon or as part of the 2.5D/3D heterogeneous integration structure. This solution may suit very low inductance requirements (1nH approximately) that will be required for IVRs operating at or above 100MHz. It could make use of RDL and bump/solder ball interconnect to provide the required inductance. The challenge may be achieving sufficiently low dc resistance. EMI may also be an issue in terms of effects on nearby on-chip circuitry. This technology has the potential to effectively deliver an inductor array platform for granular power distribution.

- Thin-film, magnetic-core, planar inductors fabricated on silicon, made using Permalloy or CZT. This technology is currently available from only one high-volume foundry with other foundries, and the wider supply chain, beginning to engage. Currently the technology is delivering solenoid inductors in high volume these are currently limited in terms of nH/mOhm (less than 1.0) and in terms of saturation current (less than 1 amp dc), unless used in coupled inductor format (up to 2.5 to 3 Amp dc). This technology has the potential to deliver an effective inductor array platform for highly granular power distribution.

*Table I-3: Comparison of metrics for integrated inductors*<sup>36</sup>

| Inductor Metric | Composite Core<br>(This Work) | Air Core Inductor [2]   | Composite Core<br>[7]  | Composite Core<br>[12] | Thin Film<br>Magnetics [11] | Thin Film<br>Magnetics [13] |

|-----------------|-------------------------------|-------------------------|------------------------|------------------------|-----------------------------|-----------------------------|

| Inductance      | 2.5 nH                        | 1.2 nH                  | 3.0 nH                 | 374 nH                 | 3.9 nH                      | 120 nH                      |

| DC Resistance   | 12 mQ *                       | 7 mΩ *                  | 12 mQ *                | 24 ms2                 | 39 m/O                      | 270 mQ                      |

| Imax            | 8 A                           | 8 A                     | 4 A                    | 2.5 A                  | 1.25 A                      | 0.4 A                       |

| L/Rdc           | 208 nH/Ω *                    | 171 nH/Ω *              | 250 nH/Ω *             | 1558 nH/Ω              | 100 nH/Ω                    | 444 nH/Ω                    |

| Area            | 0.4 mm²                       | 2 mm²                   | 0.5 mm <sup>2</sup>    | 6 nun²                 | 0.5 mm²                     | 0.9 mm <sup>2</sup>         |

| Current Density | 20 A/mm <sup>2</sup>          | 4 A/mm²                 | 8 A/mm <sup>2</sup>    | 0.41 A/mm <sup>2</sup> | 2.5 A/mm <sup>2</sup>       | 0.44 A/mm <sup>2</sup>      |

| Energy Density  | 200 nJ/mm²                    | 19.2 nJ/mm <sup>2</sup> | 48 a.J/mm <sup>3</sup> | 195 nJ/mm²             | 6.1 nJ/mm²                  | 10.7 nJ/mm <sup>3</sup>     |

| Peak Q (Freq)   | 33 (90 MHz) *                 | 24 (140 MHz) *          | 18 (100 MHz) *         | 29 (10 MHz)            | 15 (100 MHz)                | 14.5 (15 MHz)               |

<sup>\*</sup> Includes the parasitic routing impedance from the powertrain to the inductor and from the inductor to the load.

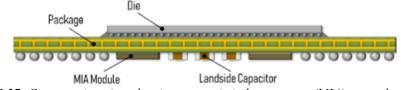

Figure I-27: Cross section view showing magnetic inductor array (MIA) on package land side<sup>37</sup>

Figure I-28: Bottom view of package substrate integrating inductors<sup>38</sup>

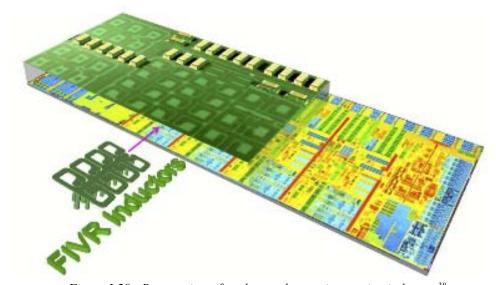

**Fully Integrated Voltage Regulators (FIVRs),** introduced by Intel in their Haswell processor in 2014, have demonstrated the merits of improving fine-grain power management and the PDN.<sup>39</sup> Intel's 10nm Icelake mobile 9-28W TDP processor, introduced in 2019, attaches several magnetic inductor array (MIA) modules as landside components to the processor's package (Figure 27) to minimize output voltage ripple and enable single-phase operation during light loads to increase efficiency. A typical Intel processor can have over 100 inductors. The magnetic inductor arrays are used sparingly for phases that are active during typical workloads in which the processor spends the majority of its time. Additional air-core inductors are active only during peak workloads which draw the maximum current but only for a small amount of time.<sup>37</sup> The challenges are to increase input voltage (from 1.8V to 5V) and current density and reduce cost.

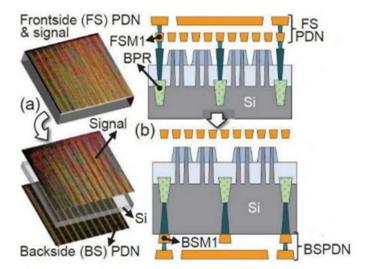

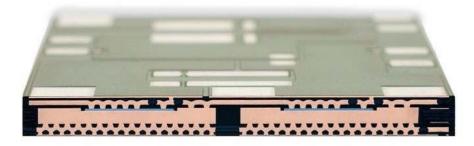

**Backside Power Delivery Network** (Figure 30), such as Intel's PowerVia technology, improves voltage droop characteristics, allowing for faster transistor switching while enabling denser signal routing on the top of the chip compared to a conventional Frontside Power Delivery Network. IVRs are still needed to supply the backside power delivery network.

Figure I-29: Array of coaxial magnetic composite core inductors used in a 6-phase IVR<sup>36</sup>

Figure I-30: Backside Power Delivery Network (BSPDN)<sup>40</sup>

#### I.4. POTENTIAL SOLUTIONS

To support a wide range of voltage rails, phases and current demand, N-number of IPECs may be integrated in the SiP using one or more of the packaging architectures (Figure 4), such as the following:

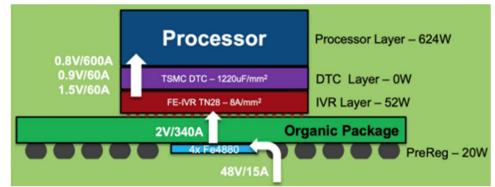

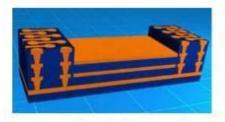

- Integrate IPECs on the active side of the load die using 3D stacking. An example is Ferric Semiconductor's stacked IVR (Figure 31), which stacks on the load die (i) an IVR die that integrates the power transistors and control circuits made using TSMC's 28nm CMOS with integrated inductors in the CMOS back-end-of line (BEOL) metal interconnects, and (ii) a Deep Trench Capacitor (DTC) die having low Equivalent Series Resistance (ESR) and Equivalent Series Inductance (ESL). The stacked IVR supports a 2V input voltage. 42

- Integrate IPECs on the backside of the load die. Challenges include compromising thermal management for load die using backside cooling and integrating TSVs in the load die to interconnect the IPEC outputs to the load and the IPEC inputs from the interposer.

- Integrate IPECs in an active interposer under the load die. An example is a CEA-LETI's demonstration vehicle that integrates in a 198mm<sup>2</sup> 65nm CMOS interposer with six 2.5V switched-capacitor

- converters, one under each of the six load die (Figure 32).  $^{43,44,45}$  2:1 conversion efficiency is 82% for 1A output and 50% for 5A output. The interposer has micro-bumps (10µm diameter, 20µm pitch) and through-silicon vias (10µm diameter, 40µm pitch).

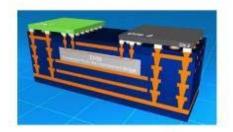

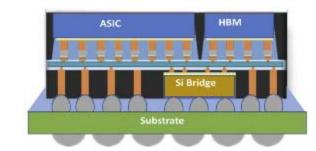

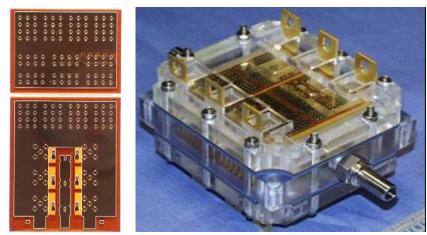

- Embed IPECs in cavities in the package substrate, form interconnects using semi-additive panel-level build-up processes, and attach the load die on top, similar to Intel's Embedded Multi-chip Interconnect Bridge (EMIB) process (Figure 33). Similar to embedding many (10 or more) EMIB die in the package substrate (Figure 34 and Figure 35)<sup>53</sup> to interconnect load die, embed many IPECs in the package substrate between the interconnect bridges to place IVRs in close proximity to the load die.

- Bond IPECs to the load die similar to IBM's Direct Bonded Heterogeneous Integration (DBHi), which directly bonds a silicon bridge to and between die using copper pillars and housed in trenches machined in the laminate substrate (Figure 36). Its major difference from Intel's EMIB is that DBHi has C4 bumps formed on the chip pads that attach to the substrate and micro bumps formed on the bridge pads, while EMIB forms both C4 bumps and micro bumps on the chip pads, a more complex process. 47

- Embed IPECs in organic-based packages, such as:

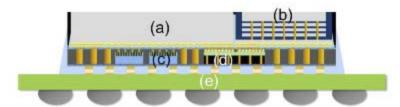

- Amkor's S-Connect process (Figure 37), which embeds semiconductor die and integrated passive devices (c) and silicon bridge die (d) in an RDL interposer, made using silicon, glass or an epoxy mold compound, with an ASIC (a) and HBM (b) on top. 48

- ASE's Stacking Fan Out Chip on Substrate (sFOCoS) (Figure 38) whose test vehicle embeds a ~6x6mm silicon bridge die with 0.8/0.8μm interconnects and 55μm micro-bump pitch into the fanout organic RDL layers. The fan-out chip module size is 27x14mm and the package dimension is 40x30 mm. <sup>49</sup>

- TSMC's Chip-on-Wafer-on-Substrate-LSI (CoWoS-L) (Figure 39), which embeds an LSI in an organic substrate with high-density RDL interconnects. The LSI may be an integrated passive device (IPD) in addition to a local silicon interconnect.<sup>50</sup>

Figure I-31: Ferric Semiconductor's Stacked IVR<sup>42</sup>

Figure I-32: 96-Core Processor with 6 Chiplets 3D-Stacked on an Active Interposer

1) HDI substrate build-up to cavity layer

2) EMIB Die embedding into cavity

3) EMIB interconnect and HDI substrate FLI formation

4) Die attach onto EMIB substrate

5) EMIB functioning as D2D interconnects

Figure I-33: EMIB die embedding process<sup>28</sup>

Figure I-34: Silicon bridge die<sup>28</sup>

Figure I-35: 10+ EMIBs embedded in package substrate<sup>28</sup>

Figure I-36: IBM's Direct Bonded Heterogeneous Integration (DBHi) 46

Figure I-37: Amkor's S-Connect Process<sup>48</sup>

Figure I-38: ASE's Stacking Fan-Out Chip on Substrate (sFOCoS) 49

Figure I-39: TSMC's CoWoS-L<sup>50</sup>

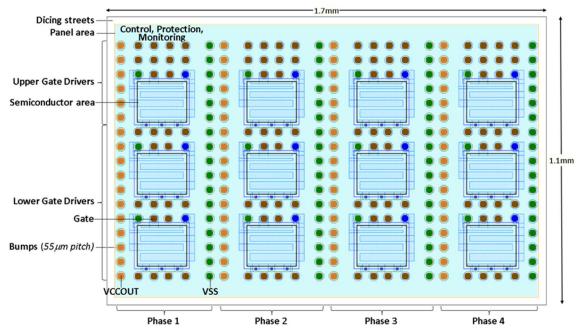

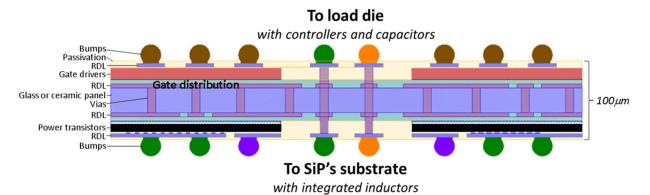

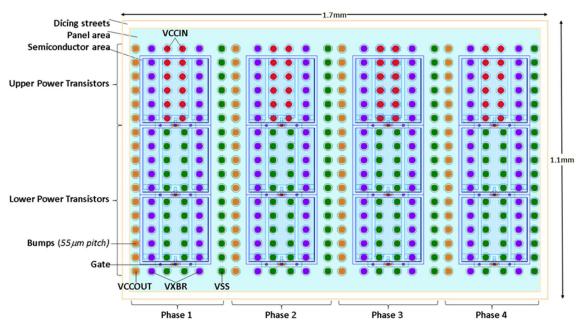

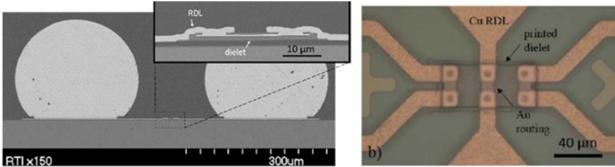

One potential IPEC solution disaggregates separately-manufactured semiconductor die into small, very thin chips (called x-chips) that are transferred to large area panels which serve as the heterogeneous integration platform. An example of a 4-phase buck converter power stage IPEC, where each phase is sized for the integrated inductor (e.g.,  $\sim$ 2A continuous and  $\sim$ 6A+ peak current) and the IPEC is constructed as follows:

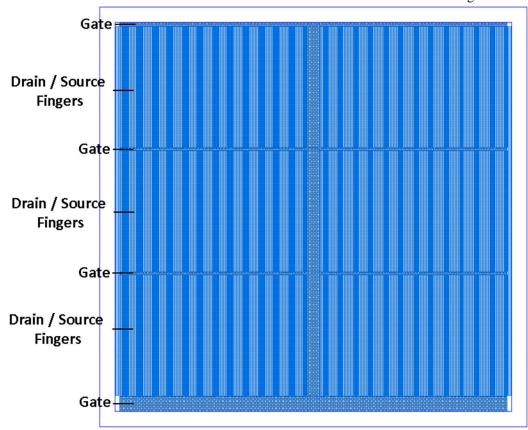

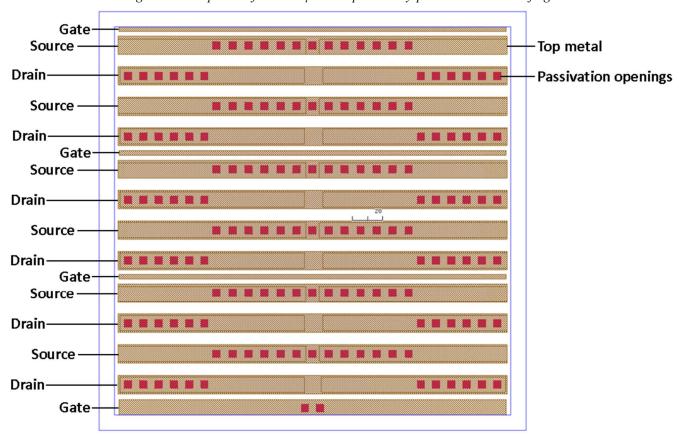

- GaN, GaAs or silicon power transistors are disaggregated into large arrays of small (e.g., 275x280μm), thin (<15μm) x-chips (Figure 40), which densely pack the source/drain fingers to minimize RDS(on) Area, connect gates to both sides of the power transistor and minimize lateral current flow (e.g., <100μm) in the thin metal layers made using a semiconductor wafer fab. The last step in the semiconductor wafer fab process is passivation openings to top metal, and the passivation openings are arranged for subsequent RDL interconnects using coarse (>10μm/10μm) L/S design rules to the source, drain and gate (Figure 41). CMOS gate driver x-chips are similarly manufactured on separate silicon wafers

- Gate driver x-chips are transferred to the top side (Figure 42) of an ultra-thin, large area glass or ceramic substrate with through-substrate vias with their active side facing up towards the load die (Figure 43).

- Power transistor x-chips are transferred to the bottom side of the substrate (Figure 44) with their active side facing down towards the package substrate.

- Since the gate driver and power transistor x-chips are ultra-thin and small, it's straightforward to use RDL for interconnections.

Figure I-40: Top view of 275x280µm x-chip's densely-packed source/drain fingers<sup>10</sup>

Figure I-41: Top view of 275x280mm x-chip's passivation openings to top metal<sup>10</sup>

Figure I-42: IPEC Top View<sup>10</sup>

Figure I-43: IPEC Cross-Section View<sup>10</sup>

Figure I-44: IPEC Bottom View<sup>10</sup>

This example shows the following benefits of this heterogeneous integration approach:

- Tightly coupling separately manufactured components: The interconnection distance between the power transistors and gate drivers is just slightly more than 100µm which significantly reduces the parasitics and switching loss.

- Reduced electrical and thermal resistance to support high current density: Multiple thick RDL interconnects made using panel-level processing supplement the semiconductor die's thin interconnects made using wafer-level processing. Thick PLP RDL is used for all high-current interconnects as well as gate distribution and routing of the control, protection and monitoring signals. Lateral current flow in the thin semiconductor die's interconnects is minimized.

- Cost reduction: The majority of the interconnects consume substrate area (Figure 43) rather than semiconductor area (Figure 1). Substrate area is significantly lower cost than semiconductor area. In this IPEC example, the gate driver and power transistor semiconductors fill less than 25% and 50%, respectively, of the substrate area.

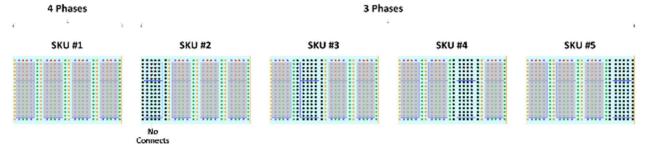

- Known good die (KGD): The IPECs can be tested and binned, for example into five different SKUs (Stock Keeping Units), one SKU with four good phases plus four SKUs with just three good phases (Figure 45).

Figure I-45: IPEC Binning Options<sup>10</sup>

Figure I-46: MTP spreads out x-chips tightly packed on semiconductor wafers on panels<sup>10</sup>

An example of a potential method for manufacturing IPECs is to use micro transfer printing (MTP), a massively parallel pick-and-place process that efficiently transfers large arrays of ultra-thin (<15µm), small, separately manufactured components from one or more source wafers to destination silicon wafers or large-area glass or ceramic substrates. A fully automatic ISO 4 class clean room system transfers up to 50x50mm arrays of x-chips from source wafers (up to 300mm) to destination wafers (up to 300mm) or panels (up to 450x450mm). By customizing the post spacing of the MTP system's stamp, x-chips tightly packed on the source wafer (maximizing source wafer HIR 2021 version (eps.ieee.org/hir)

Chapter 10, Page 28

Heterogeneous Integration Roadmap

utilization) are efficiently spread out on the panel (Figure 46). Placement accuracy is +/-1.5µm (3 sigma), which resolves the critical position accuracy requirement for the RDL interconnect process.<sup>55,56</sup> Die shift issues are eliminated since x-chips are held in place with a thin adhesive layer underneath with RDL on top and no epoxy mold compounds are used. Examples of MTP applications include fan-out packaging of microdevices (Figure 47),<sup>57</sup> GaN/RF-SOI SPST switch (Figure 48)<sup>58</sup> and GaN HEMTs on silicon (Figure 49).<sup>59</sup> An example of a foundry that offers high volume MTP capabilities is X-FAB.<sup>60</sup>

Figure I-47: Fan-out packaging of microdevices made with MTP<sup>57</sup>

Figure I-48: GaN/RF-SOI SPST switch<sup>58</sup>

Figure I-49: GaN HEMTs on silicon<sup>59</sup>

Integrated inductor technology options that have recently been proposed and show promise include:

- Small footprint (0201 0.2mm x 0.1mm) discrete inductors, using high frequency (100MHz+) polymer-loaded composites or fired magnetic material, with low profile (less than 0.1 to 0.3 mm). These components can be used in a PSiP platform, either as surface-mount devices [MuRata], or with copper terminations, embedded in the SOC organic substrate or package [Taiyo Yuden].

- High frequency ferrite cores embedded in 2.5D/3D heterogeneous integration structure using BEOL interconnect processing to provide windings [IMEC].

- Vertical coaxial magnetic composite core inductors (Figure 29) integrated in the package substrate by plated-through holes drilled in the package substrate and encapsulated with a composite magnetic material [Intel].

- Embedded magnetic-on-silicon inductors embedded in PCB substrate or package [Wurth].

- Embedded thin film CZT combined with copper windings in PCB substrate or package [Tyndall].

- Electroplated planar copper windings with electro-deposited magnetic core [Enachip].

- Vertical inductors based on thin film CZT deposited on the sidewalls of low-profile electroplated copper pillars [Tyndall].

#### I.5. REQUIRED R&D

R&D focused on IPECs is needed in the following areas:

**Panel-level packaging (PLP)** employing a portfolio of state-of-the-art heterogeneous integration technologies (e.g., pick-and-place, die bonding, micro-transfer printing, RDL, through-substrate vias, sort/test, etc.) for prototyping and volume production. Prototyping should be done using manufacturing flows that are representative of volume production. A state-of-the-art PLP foundry would enable and stimulate R&D. The cost of building such a PLP foundry

is on the order of \$0.1B versus \$10B for a state-of-the-art wafer fab and would leverage decades of experience and technologies from PCB, flat panel display and solar panel manufacturing.

Electronic Design Automation (EDA) tools and Process Design Kits (PDKs) for PLP heterogeneous integration. Tools are required for the holistic co-design optimization, simulation and integration of separately manufactured IVR components. A variety of stack-ups, layer maps and models, including measured versus modeled correlation and improving load energy efficiency through improving the PDN and fine-grain power management is required. PDKs for the diverse IVR components and heterogeneous integration method which provide design guidelines and incorporate the results of reliability testing and analysis (so it's known when, how and why various IVR components fail during high current density and high-frequency operation). Tools should also include cost modeling to identify and resolve early in the IPEC design cycle roadblocks and trade-offs in cost and yield among various heterogeneous integration options. Such cost modeling can build upon the substantial activity-based cost modeling, which breaks down a process flow into all of its cost components (e.g., labor, materials, capital and yield), that has been done for chip-on-interposer on substrate and fan-out on substrate.

**Optimization of separately manufactured components for IVRs**, including power transistors, gate drivers, controllers, inductors and capacitors. Key R&D for power transistors include employing compound semiconductors (GaN and GaAs), which have very low gate and output charge and no reverse recovery charge, and minimizing their on-resistance • area figure-of-merit, optimized for 3-5V operation. Key R&D for IVR inductors, which requires a multidisciplinary approach with considerations of 3D inductor design, magnetic material synthesis and processing, integration and assembly into packages, substrates and interposers, include:

- Increasing dc nH/milliOhm beyond 1.0 (up to 5.0 to 10.0).

- For magnetic core solutions, increasing the saturation current up to 5 to 10Amps dc.

- Exploiting the vertical direction to provide reduced footprint, ultra-low dc resistance inductors to produce a useful, single vertical inductor (either air core or with magnetic core) using discrete, embedded components, plated through holes in PCB or the RDL/bump interconnect in a 2.5D interconnect system.

- Exploring integrated inductor arrays in interposers or substrates for complex granular power architectures.

- Consider the EMI implications of integrated inductors and appropriate solutions.

- Utilize the "parasitic inductances" within the system architecture, either with or without magnetic material enhancements, which is the "holy grail" for integrated inductors.

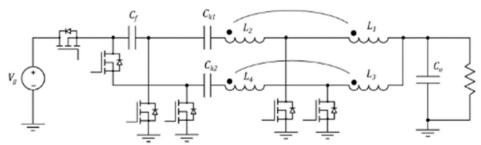

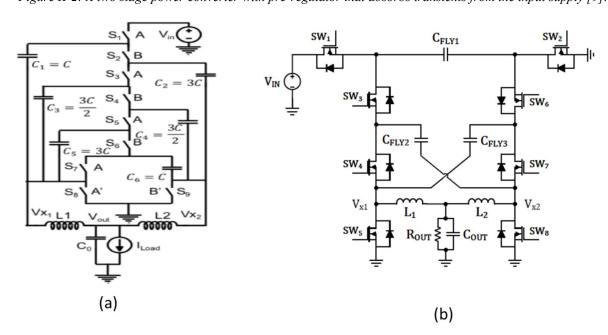

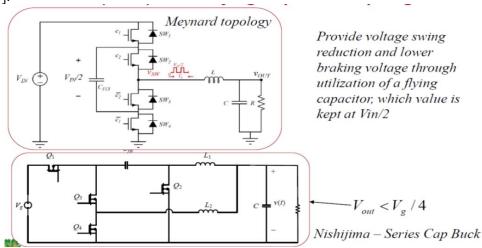

**Integrating arrays of separately-manufactured components in IPECs customized for advanced topologies**, such as a 3-level buck converter (Figure 50), 4-level buck converter (Figure 51) or hybrid series-capacitor tapped buck converter (Figure 52), which improve performance and reduce voltage requirements but require an increased number of power transistors, gate drivers and passive components.

**Stacking separately-manufactured components**, such as power transistors, to increase their gate periphery, reducing conduction loss, or capacitors to increase bypass capacitance.

Figure I-50: 3-Level Buck Converter<sup>62</sup>

Figure I-51: Modified 4-Level Buck Converter<sup>29</sup>