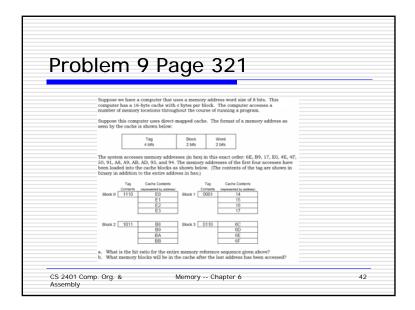

| The dia like.       | gram be             | elow is a sch                                                   | ematic of wha                                            | t cache looks            |

|---------------------|---------------------|-----------------------------------------------------------------|----------------------------------------------------------|--------------------------|

| like.               | Block               | Tag                                                             | Data                                                     | Valid                    |

|                     | 0                   | 00000000                                                        | words A, B, C,                                           | 1                        |

|                     | 1                   | 11110101                                                        | words L, M, N,                                           | 1                        |

|                     | 2                   |                                                                 |                                                          | 0                        |

|                     | 3                   |                                                                 |                                                          | 0                        |

| identifi<br>words i | ed with<br>dentifie | ns multiple w<br>the tag 0000<br>d with the ta<br>blocks are no | ords from mai<br>0000. Block<br>g 11110101.<br>ot valid. | in memory,<br>1 contains |

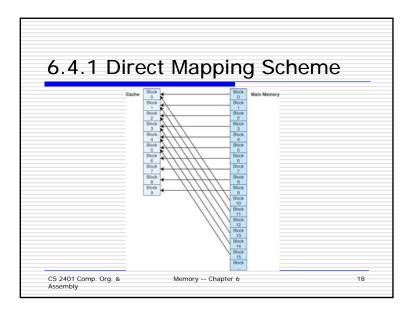

| Main Memory                | Maps to | Cache   |  |  |  |  |  |

|----------------------------|---------|---------|--|--|--|--|--|

| Block 0 (addresses 0, 1)   |         | Block 0 |  |  |  |  |  |

| Block 1 (addresses 2, 3)   |         | Block 1 |  |  |  |  |  |

| Block 2 (addresses 4, 5)   |         | Block 2 |  |  |  |  |  |

| Block 3 (addresses 6, 7)   |         | Block 3 |  |  |  |  |  |

| Block 4 (addresses 8, 10)  |         | Block 0 |  |  |  |  |  |

| Block 5 (addresses 10, 11) |         | Block 1 |  |  |  |  |  |

| Block 6 (addresses 12, 13) |         | Block 2 |  |  |  |  |  |

| Block 7 (addresses 14, 15) |         | Block 3 |  |  |  |  |  |

Memory -- Chapter 6

22

CS 2401 Comp. Org. &

Assembly

## 6

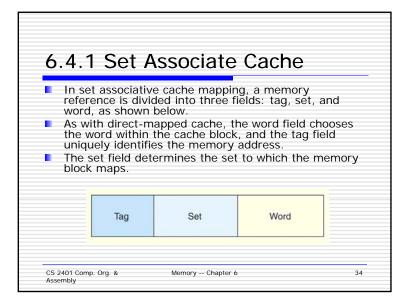

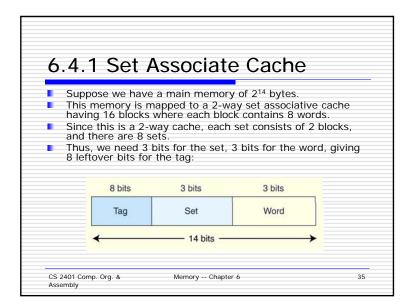

|          | The num         | ber of cache b                    | locks | per set in | set associativ | ve         |

|----------|-----------------|-----------------------------------|-------|------------|----------------|------------|

|          |                 | ries according                    |       |            |                |            |

|          | conceptu        | nple, a 2-way s<br>alized as show | vn in | the schema | atic below.    |            |

|          |                 | contains two                      |       |            |                |            |

|          |                 |                                   |       |            | <u> </u>       |            |

|          |                 |                                   |       |            |                |            |

| Sot      | Tag             | Block 0 of set                    | Valid | Tag        | Block 1 of set | Valid      |

| Set      | Tag             | Block 0 of set                    | Valid | Tag        | Block 1 of set |            |

| Set<br>0 | Tag<br>00000000 | Words A, B, C,                    | Valid |            | Block 1 of set | Valid<br>0 |

|          | 00000000        |                                   | 1     |            | P, Q, R,       | -          |

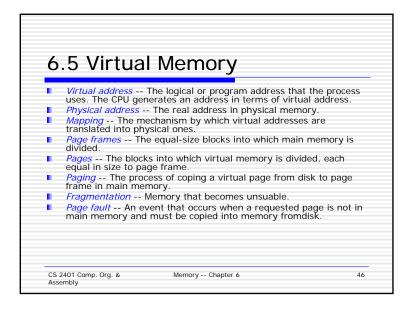

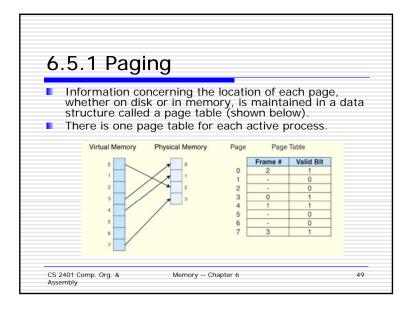

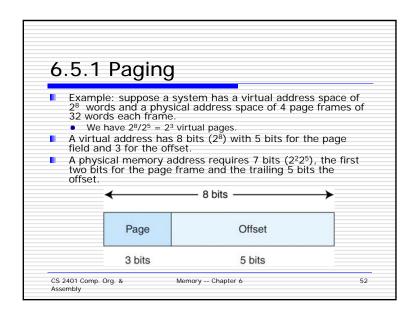

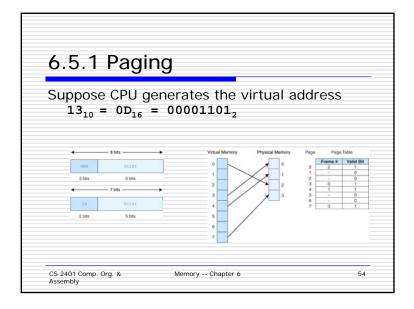

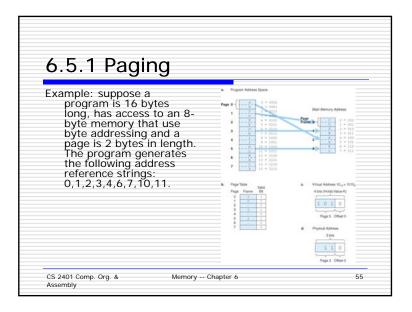

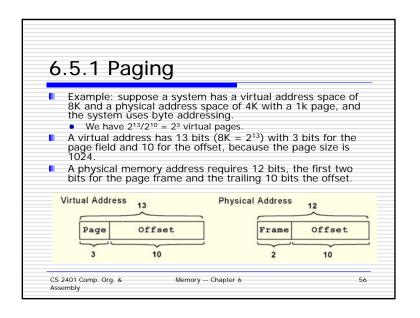

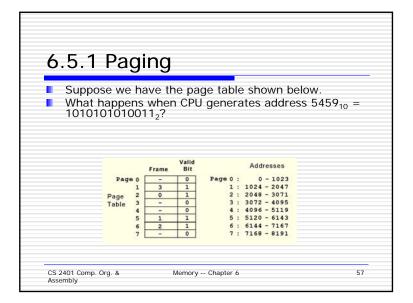

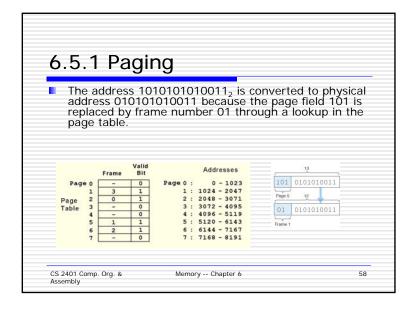

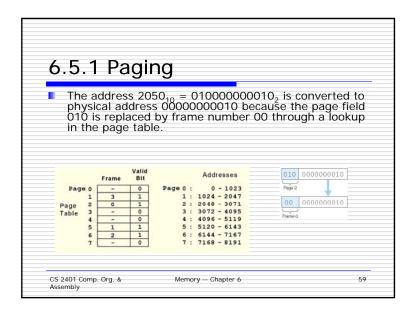

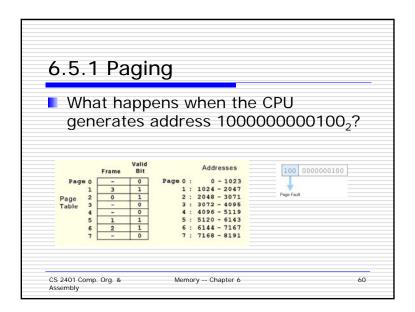

| 6 | .5.1 Paging                                                                                                                                                                                                                                                                                         |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • | A <i>physical address</i> is the actual memory<br>address of physical memory.<br>Programs create <i>virtual addresses</i> that are<br>mapped to physical addresses by the<br>memory manager.<br><i>Page faults</i> occur when a logical address<br>requires that a page be brought in from<br>disk. |

| • | Memory <i>fragmentation</i> occurs when the paging process results in the creation of small, unusable clusters of memory addresses.                                                                                                                                                                 |

| Main memory and virtual memory are divided into equal sized pages.                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

| The entire address space required by a process need<br>not be in memory at once. Some parts can be on disk,<br>while others are in main memory. |

| Further, the pages allocated to a process do not need to be stored contiguously either on disk or in memory.                                    |

| In this way, only the needed pages are in memory at<br>any time, the unnecessary pages are in slower disk<br>storage.                           |

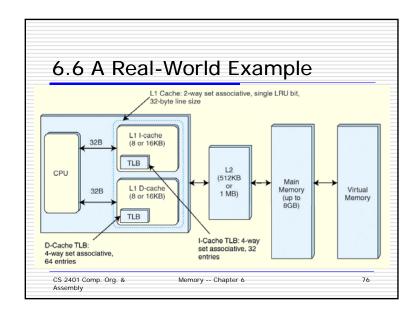

|               |                   |                   | 101               | orle              | J T          | vom                             | nla                             |                  |                           |

|---------------|-------------------|-------------------|-------------------|-------------------|--------------|---------------------------------|---------------------------------|------------------|---------------------------|

| 5.6 A         |                   | ear               | -                 | JIIC              |              | xan                             | ipie                            |                  |                           |

|               |                   |                   |                   |                   |              |                                 |                                 |                  |                           |

|               |                   |                   |                   |                   |              |                                 |                                 |                  |                           |

|               | PPC<br>601        | PPC<br>603        | PPC<br>604        | PPC<br>620        | SPARC        | R10000                          | R4400                           | Pentium          | P-Pro                     |

| Blocking      | 1                 | 0                 | 4                 |                   |              |                                 |                                 |                  |                           |

| Split?        | No                | Yes               | Yes               | Yes               | Yes          | Yes                             | Yes                             | Yes              | Yes                       |

| Data          | 32K               | 8K.               | 16K               | 32K               | 16K          | 32K                             | 16K.                            | SK.              | 8K                        |

| Instruct.     | Unified           | 8K.               | 16K               | 32K               | 16K          | 32K                             | 16K.                            | 8K.              | 8K                        |

| Associativity | 8                 | 2                 | 4                 |                   | D: 1/I:<br>2 | 2                               | 1                               | 2                | D: 4/1<br>2               |

| Line size     | 64 B              | 32 B              | 32 B              |                   |              |                                 | 16 or 32 B                      | 32 B             |                           |

| Data Write    | Back<br>(through) | Back<br>(through) | Back<br>(through) | Back<br>(through) |              |                                 |                                 | Back<br>(drough) | Back<br>(through          |

| Replacement   |                   |                   | LRU               |                   |              |                                 |                                 |                  |                           |

| Notes:        |                   |                   |                   |                   |              | I-cache<br>predecodes<br>instr. | I-cache<br>predecodes<br>instr. |                  | 256KB<br>4-way<br>L2 cach |