# **Digital Palettes** Color Film Recorders (CI3000 / CI5000)

October 1990

Americas Business Center Technical Services 201 Burlington Road Bedford MA 01730 TEL: 1.781.386.5309 FAX: 1.781.386.5988 This page intentionally blank

## POLAROID DIGITAL PALETTE SERVICE MANUAL

## CONTENTS

- SECTION 1 GENERAL DESCRIPTION

- SECTION 2 THEORY OF OPERATION

- SECTION 3 TROUBLESHOOTING

- SECTION 4 PARTS REPLACEMENT

- SECTION 5 CALIBRATION & ADJUSTMENTS

This page intentionally blank

# **1. General Description**

## Table of Contents

| A. | Product Description                                                                          | 1-3                                           |

|----|----------------------------------------------------------------------------------------------|-----------------------------------------------|

|    | <ol> <li>Resolution</li></ol>                                                                | 1-3<br>1-4<br>1-4<br>1-5<br>1-5               |

|    | 5. Other Accessories                                                                         | 1-5                                           |

| B. | Major Components                                                                             | 1-6                                           |

|    | <ol> <li>Logic Board</li> <li>SCSI Board</li> <li>Power Supply Board</li> <li>CRT</li> </ol> | 1-7<br>1-7<br>1-7<br>1-7<br>1-7<br>1-7        |

| C. | Controls and Indicators                                                                      | 1-8                                           |

| D. | Dimensions and Specifications                                                                | 1-9                                           |

|    | <ol> <li>Addressable Resolution</li></ol>                                                    | 1-9<br>1-9<br>1-9<br>1-9<br>1-9<br>-10<br>-10 |

| E. | mage Recording Features 1                                                                    | -10                                           |

## GENERAL DESCRIPTION

This page intentionally blank

## A. Product Description

The Polaroid Digital Palette Film Recorder system is a high resolution imaging device that produces slides and prints in a variety of formats, using an almost unlimited spectrum of colors. It represents the next generation of Polaroid desktop film recorders.

## 1. Model CI-3000 and Model CI-5000

The system consists of two models:

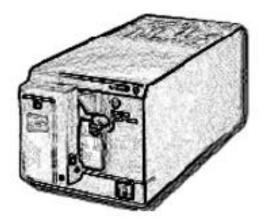

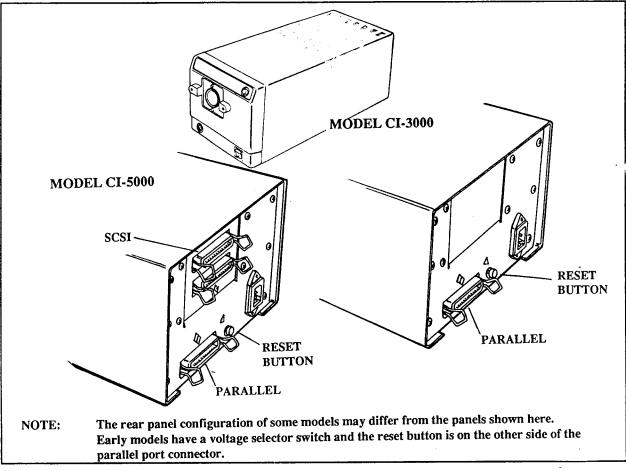

- The Model CI-3000 (Figure 1-1) is designed to operate with IBM or compatible computers only. It connects to the host computer via a standard Centronics parallel interface.

- The Model CI-5000 (Figure 1-1) is used with IBM or compatible PC's, Macintosh computers, and UNIX-based workstations. It has both a Centronics parallel interface for IBM and compatible PC's, and a small computer system interface (SCSI) for Macintosh computers.

## Figure 1-1. Model CI-3000 and Model CI-5000

## 2. Resolution

The Model CI-3000 is capable of imaging at resolutions up to 2048 X 1366 (2K), and the Model CI-5000 can achieve resolutions of up to 4096 X 2732 (4K). Color resolution is 256 levels for each primary color (red, green, and blue) resulting in a color space of 16.7 million colors.

## **3.** Film Formats

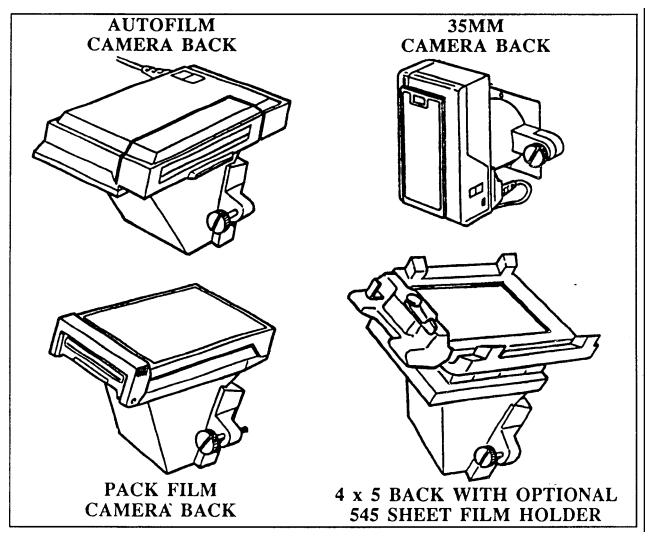

The recorder captures images, created by graphics software, on Polaroid 35mm slides,  $3 \frac{1}{4} \times 4 \frac{1}{4}$  inch prints and overhead transparencies,  $4 \times 5$  inch prints, or  $3 \times 4$  inch self-developing prints. A 35mm camera back is provided with each system; camera backs for pack film, AutoFilm, and 4X5 film are available as accessories (Figure 1-2).

Figure 1-2. Camera Backs

## 4. Film Types

| 35mm:     | PolaChrome, PolaChrome HC, PolaPan, PolaGraph, PolaBlue, and<br>Presentation Chrome, High Definition 100, Conventional 100 ISO<br>and 200 ISO |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Autofilm: | Types 339 and 331 (3" X 4")                                                                                                                   |

| Pack::    | Types 669, 691, and 664 (3 1/4" X 4 1/4")                                                                                                     |

| 4X5:      | Types 54, 59, 554, and 559                                                                                                                    |

## 5. The System

In addition to the 35mm camera back, the system comes packaged with a user's manual, power cord, Polaroid software diskettes and instructions, and a host interface cable (parallel for IBM and SCSI for Macintosh). For the CI-5000 model, the software diskettes will be packaged in either the IBM or Macintosh configuration depending on the user's requirements. The Macintosh package also includes a SCSI terminator.

#### 6. Other accessories

Optional accessories include:

35mm Power Processor and Illuminated Slide Mounter, Pack Film Camera Back, Autofilm Camera Back, 4" X 5" Camera Back GENERAL DESCRIPTION

## **B.** Major Components

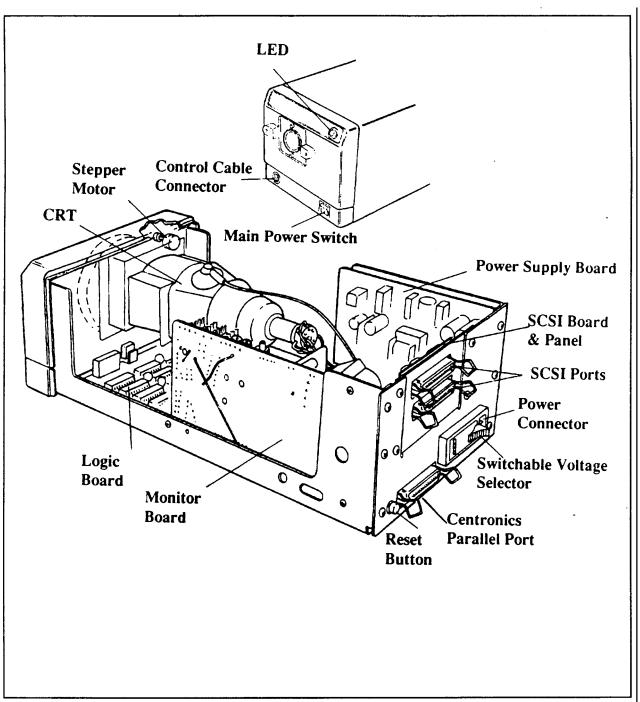

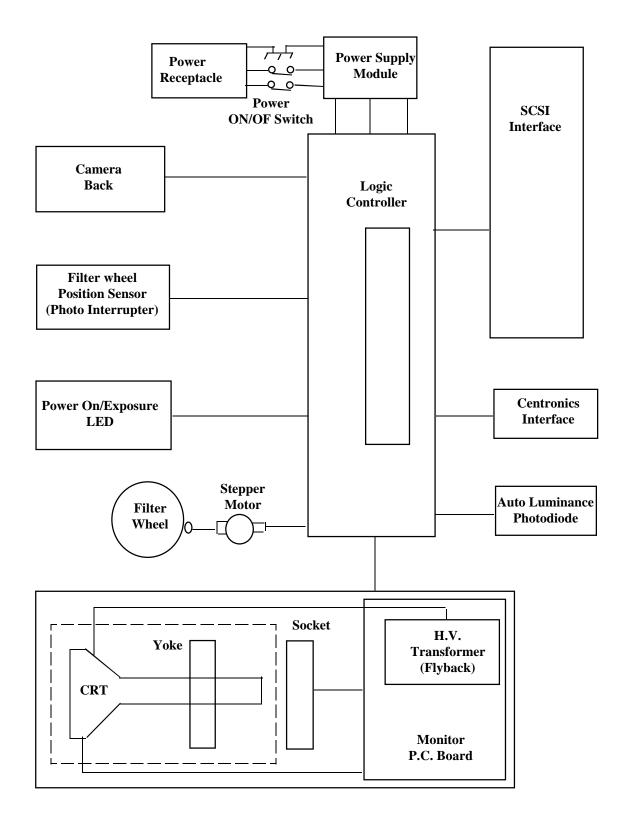

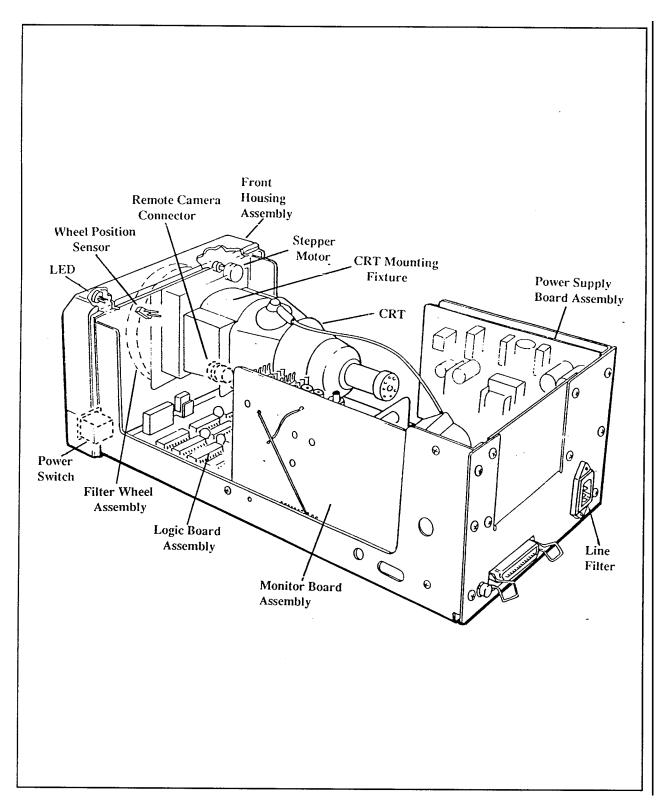

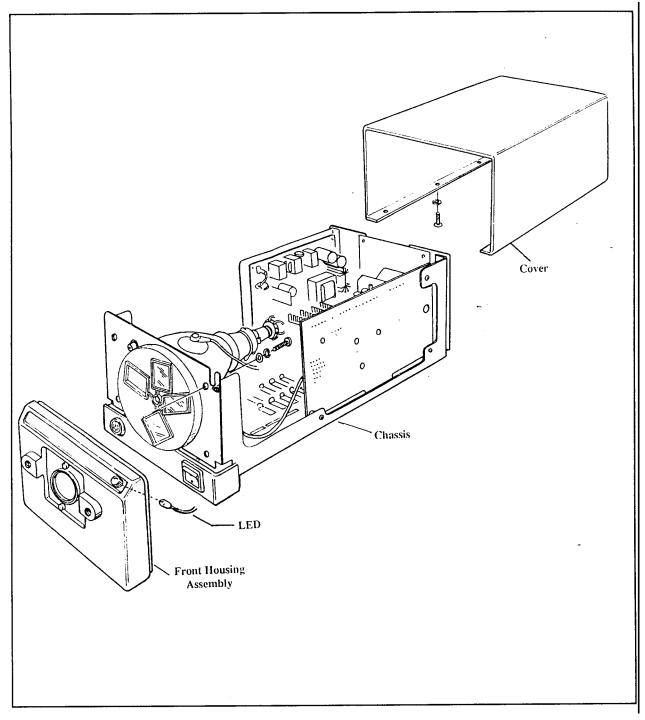

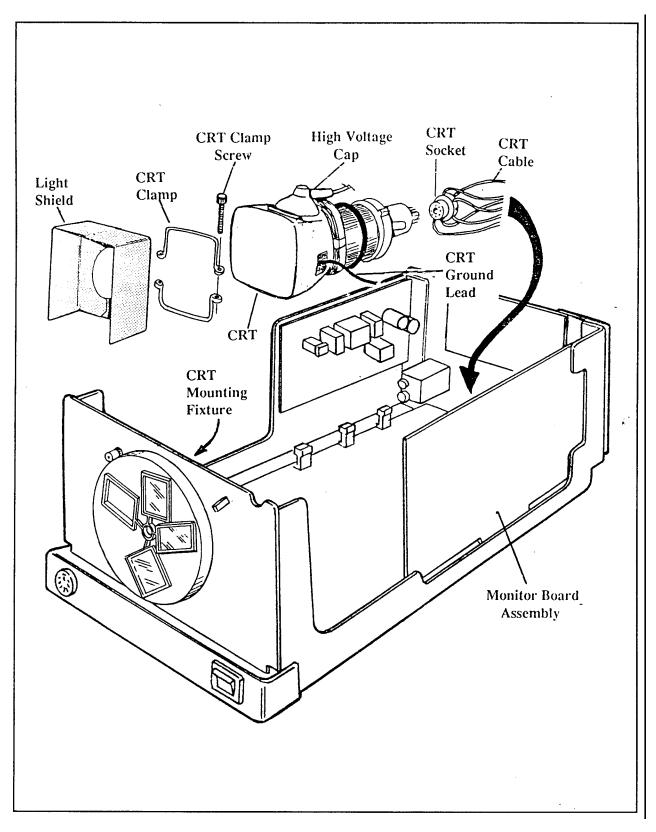

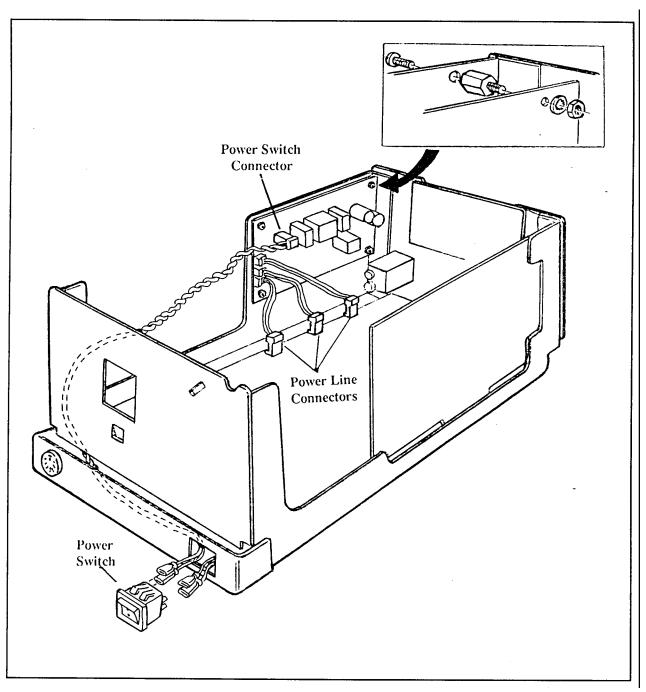

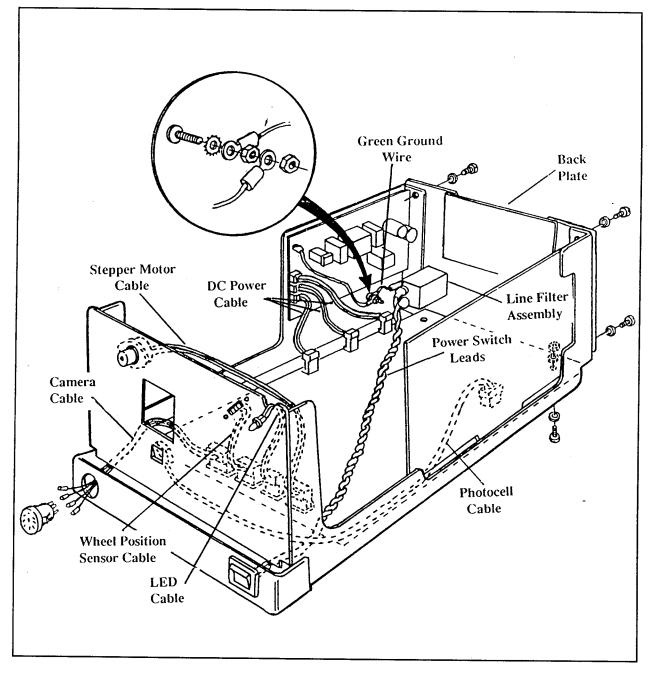

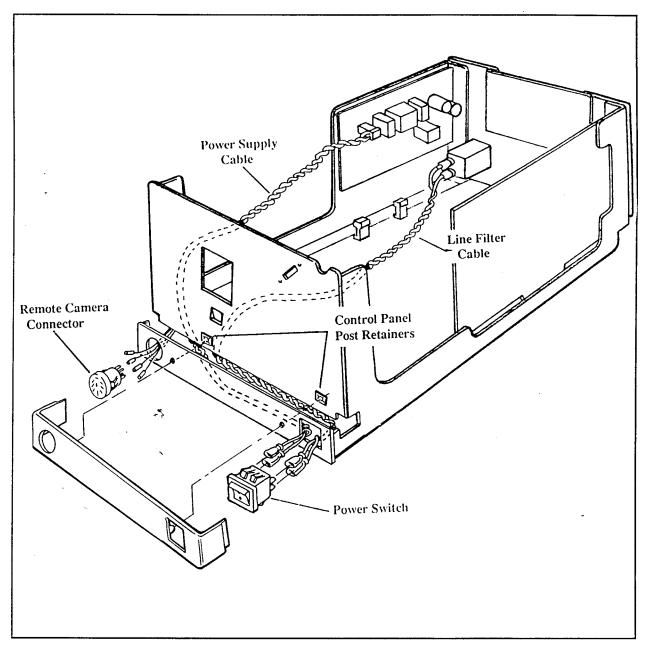

Figure 1-3 shows the major components of the Digital Palette Film Recorder system.

Figure 1-3. Major Components

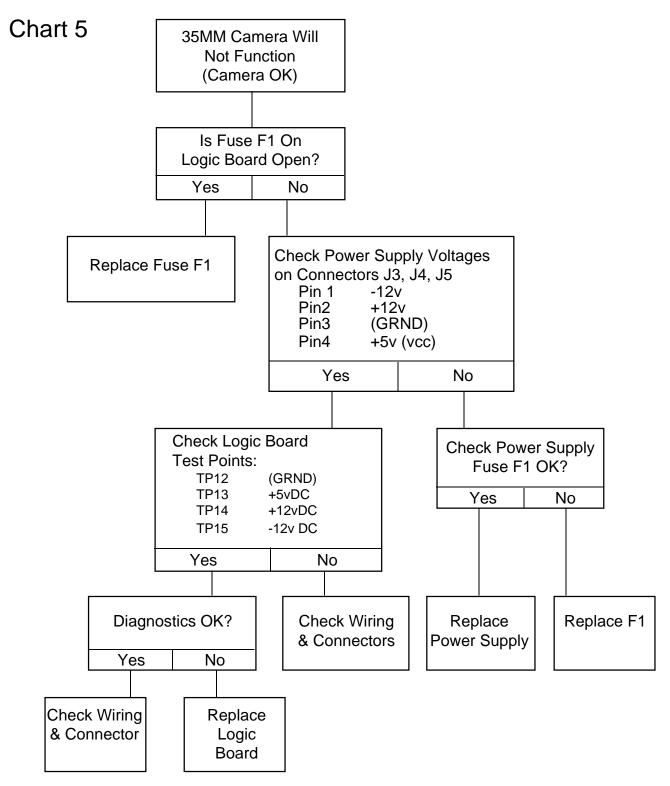

## 1. Monitor Board

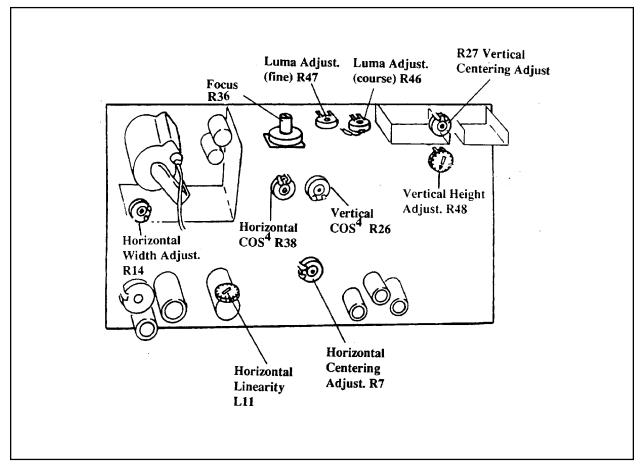

The Monitor Board contains the electronics that control the characteristics of thet CRT - horizontal and vertical deflection, high voltage, luminance, COS<sup>4</sup> exposure correction, focus, and the digital video cathode driver.

## 2. Logic Board

The Logic Board provides the communications link - receiving and confirming signals from the host computer. It contains the Centronics Board for parallel interface and a microprocessor for controlling all memory. The microprocessor utilizes a Video RAM (V RAM) for exposing the image and Dynamic RAM (D RAM) for storing picture information that it receives from the computer. In the Model CI-3000, there is 128K of memory in both V RAM and D RAM, and up to 2K horizontal imaging resolution. The Model CI-5000 has 256K of V RAM, 640K of D RAM, and up to 4K horizontal imaging resolution.

The Logic Board also stores the actual program memory via an EPROM that has 128K of memory; digitally controls vertical deflection up to 4K lines; assures consistent exposure on every image by digitally controlling autoluminance; controls the filter wheel, LED (blinks during exposure), and camera back connection all of which are located on the front panel; it utilizes a frequency synthesiser to control the system's resolution — from 256K in the CI-5000, and from 256K to 2048K in the CI-3000.

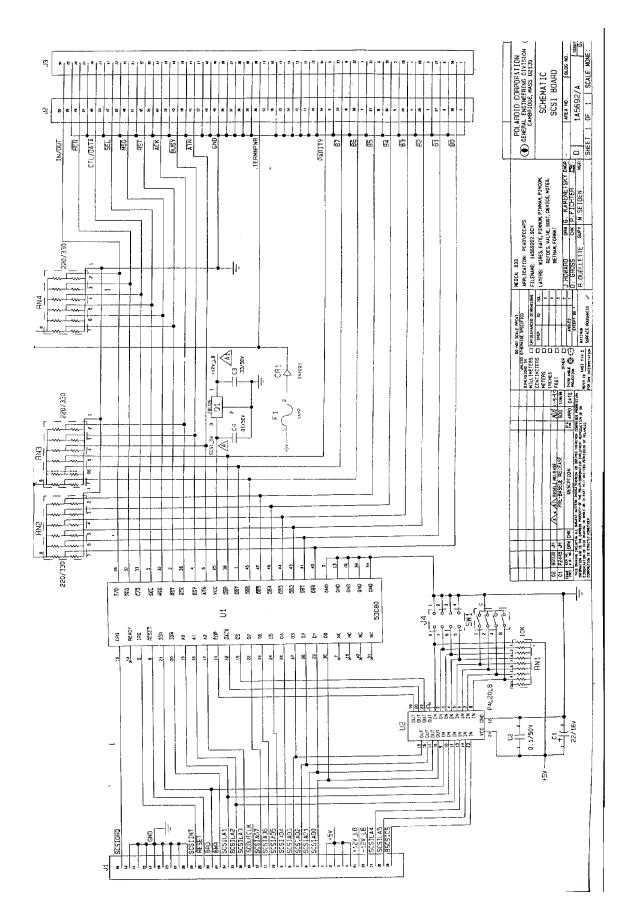

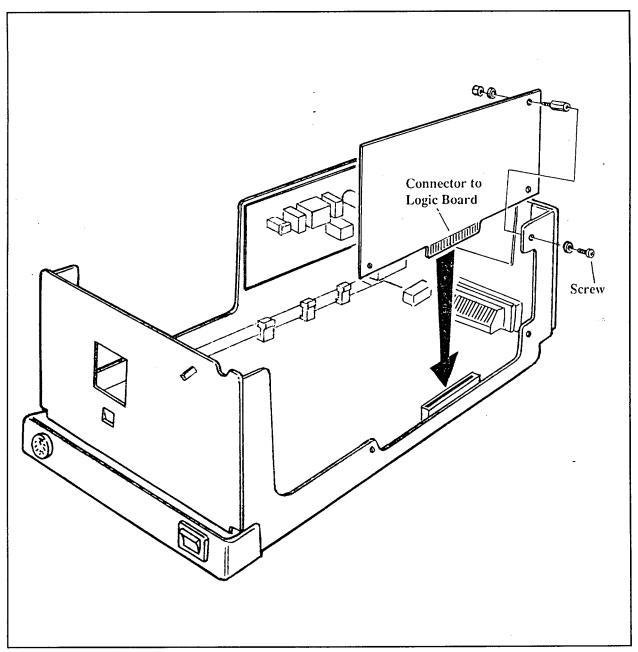

## 3. SCSI Board

The SCSI Board connects to the Logic Board for Macintosh interface.

## 4. Power Supply Board

The Power Supply Board provodes +5V and +12V and automatically switches from 110VAC to 220VAC at 50/60Hz.

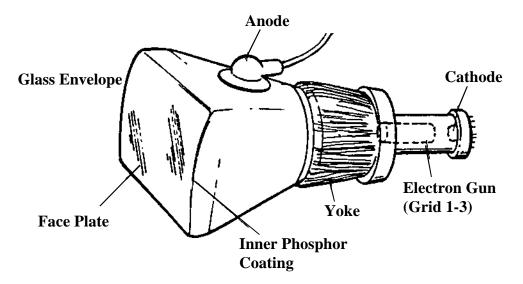

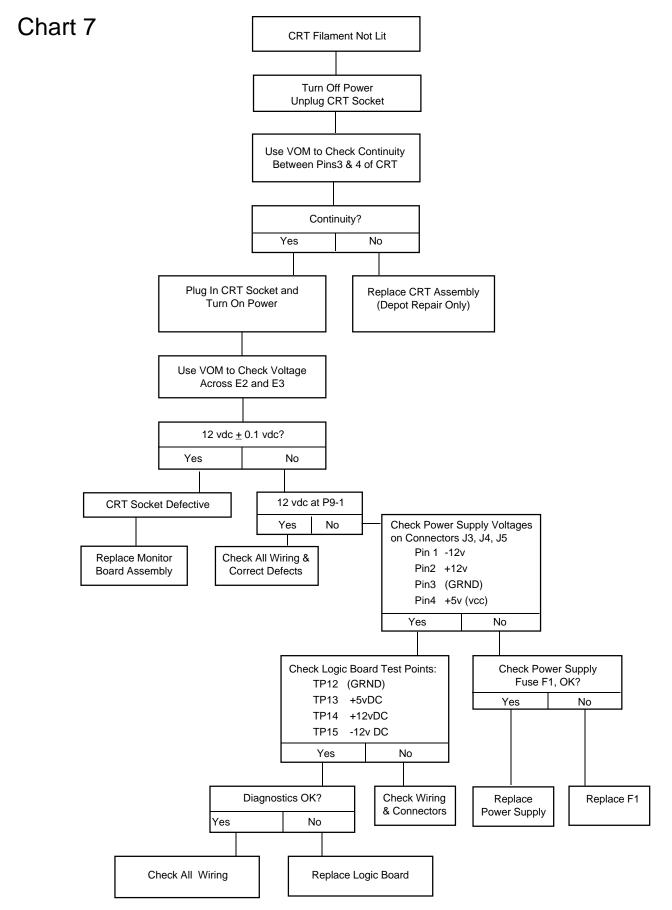

## 5. CRT

The CRT is a flat-faced tube which presents a medium-resolution monochrome black-and-white image. Its normal orientation is rotated 90° around the viewing axis. This means that the horizontal axis is oriented up-and-down and the vertical axis is oriented side-to-side—as viewed from the front of the recorder.

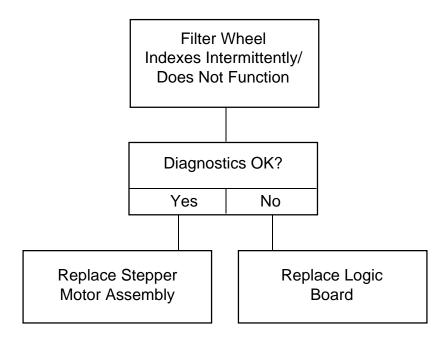

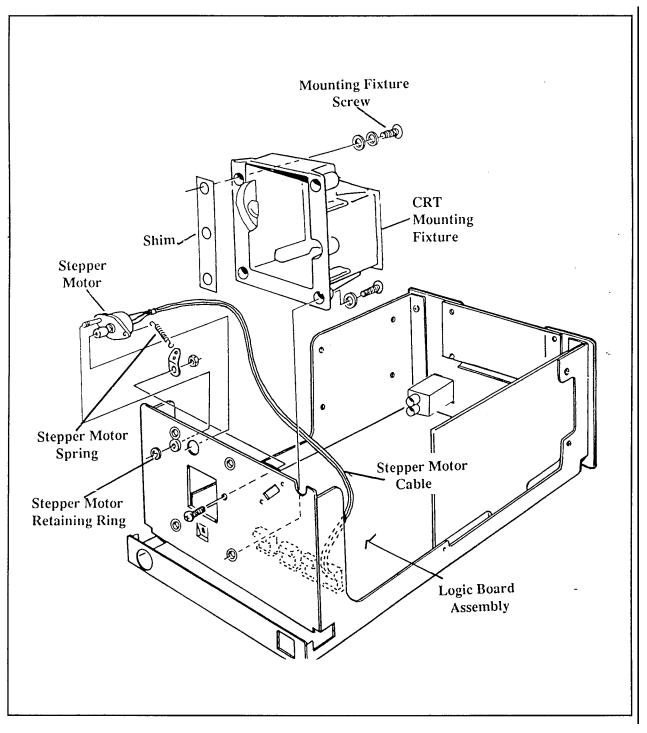

## 6. Stepper Motor

The Stepper Motor is regulated by signals from the Logic Board, moves the filter wheel during the exposure sequence. The filter wheel contains three filters of the primary colors - red, green, and blue.

## GENERAL DESCRIPTION

# C. Controls and Indicators

The function of each of the controls and indicators shown in Figure 1-3 is described in Table 1-1.

| Controls                    | Indicators                                                                                                            |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Front Panel:                |                                                                                                                       |

| Main Power Switch           | Turns the system on and off.                                                                                          |

| Front Panel LED             | When lit, indicates the unit is on.                                                                                   |

| Control Cable Connector     | Accepts control cable for powering the 35mm and AutoFilm camera backs.                                                |

| Rear Panel:                 |                                                                                                                       |

| Reset Button                | Resets the system without powering down.<br>On newer units, if held in, will provide test<br>image of color spectrum. |

| Centronics Parallel Port    | Accepts parallel interface cable for IBM and compatible PC's.                                                         |

| SCSI Port                   | Accepts SCSI interface cable for Macintosh computers.                                                                 |

| Power Connector             | Accepts IEC standard three-pin power cable.                                                                           |

| Switchable Voltage Selector | Automatically selects 110VAC or 220VAC.                                                                               |

## **D.** Dimensions and Specifications

## **1.** Dimensions and Weight (without camera back)

| Height: | 7.125" | (18.097 CM) |

|---------|--------|-------------|

| Width:  | 7.75"  | (19.685 CM) |

| Length  | 16.00" | (40.640 CM) |

## 2. Addressable Resolution (Assuming square pixels)

|                        | Model CI-3000 | Model CI-5000 |

|------------------------|---------------|---------------|

| 35 mm Format:          | 2048 X 1366   | 4096 X 2732   |

| AutoFilm/Pack Formats: | 2048 X 1536   | 4096 X 3072   |

| 4 X 5 Format:          | 2029 X 1536   | 4058 X 3072   |

## 3. Addressable Color Space

256 levels per primary color (16.7 million colors)

## 4. Addressable Grey Scale

256 grey levels

## 5. Target Image Exposure Times \*

| 4096 x 2732: | 6 to 8 minutes   |

|--------------|------------------|

| 2048 X 1366: | 3 to 4 minutes   |

| 1024 X 768:  | 1.5 to 2 minutes |

| 640 X 480:   | 1 minute         |

\* Target exposure times are based on ISO 100 Polaroid Presentation Chrome film when exposing run-length encoded business graphics images with up to 256 levels per primary running on PC/AT (8mhz), or equivalent. Exposure times will decrease with simple word slides and increase for uncompressed "natural" (captured) images.

#### 6. **Power Requirements**

The units meet domestic and international requirements (switchable). +5V and +12V; 110 to 220VAC at 50/60Hz.

## 7. Safety Requirements

The units meet all Polaroid standard safety and certification requirements (e.g. UL, CSA, FCCB, TUV and VDE).

## E. Image Recording Features

Here are some special features of the Digital Palette Film Recording system:

- It is a variable and high addressability system ranging from 256 to 4096 pixels. It will respond to the resolution requirements of the software file that is being imaged.

- **o** There is progressive line scan one line at a time which enhances image resolution.

- The system is capable of imaging up to 16 millions colors; 8 bit per primary color, or 24 bits total.

- Exposure time is faster since scanning starts with the brightest level of each line, rather than beginning at full white.

- In the Model CI-5000, a Buffer Queue Mode provides an additional 512Kb of buffer memory. This frees up the host computer while imaging is taking place. There is 128K of buffer memory in the Model CI-3000.

- A background Mode allows the system to vary the color intensity in the background. With this feature, it's possible to lighten or darken areas of the background in order to highlight the graphic image. Also, this mode makes it possible to select color for a previously black background.

- A COS<sup>4</sup> correction increases the radial luminance of the CRT to prevent light fall-off in the corners. This provides a more even exposure in the finished print/slide no dark corners.

- A resident test image allows the customer to set up and check the system before connecting it to the host computer.

- Image Sizing/Configuration Utility software makes it possible to "Zoom" an image by +5%. This enables the customer to enlarge or shrink the image to suit individual needs.

# 2. Theory of Operation

## **Table of Contents**

| <b>A.</b> | Inti | oduction                                                       |

|-----------|------|----------------------------------------------------------------|

| B.        | Exp  | oosure System 2-8                                              |

|           | 1.   | Component Description 2-8                                      |

|           |      | a. Camera (Back) Adapter Assembly 2-8                          |

|           |      | b. Filter Wheel Assembly                                       |

|           |      | c. Filter Wheel Photo Interrupter (Position Sensor)            |

|           |      | d. Filter Wheel Stepper Motor                                  |

|           |      | e. Auto Luminance Photodiode Assembly (Brightness Sensor) 2-11 |

|           | 2.   | Exposure Description 2-11                                      |

| C.        | Pov  | ver Supply Module 2-12                                         |

|           | 1.   | AC Power                                                       |

|           | 2.   | DC Power                                                       |

| D.        | Log  | gic Controller P.C. Board 2-16                                 |

|           | 1.   | Microprocessor Control 2-16                                    |

|           |      | a. Microprocessor (CPU) 2-16                                   |

|           |      | b. 40 MHz Clock                                                |

|           |      | c. Reset Control                                               |

|           |      | d. Address Latches 2-27                                        |

|           |      | e. Microprocessor Control PAL 2-27                             |

|           |      | f. Communications Bus 2-29                                     |

|           | 2.   | Erasable Programmable Read Only Memory (EPROM)2-29             |

## THEORY OF OPERATION

|    | 3. | Random Access Memory (RAM).    2-30                 |

|----|----|-----------------------------------------------------|

|    |    | a. Dynamic Random Access Memory (DRAM)2-30          |

|    |    | b. Video Random Access Memory (VRAM)2-3             |

|    |    | c. RAM Control PAL's 2-3                            |

|    |    | d. DRAM and VRAM Refresh 2-3.                       |

|    |    | e. Loading VRAM Shift Registers 2-34                |

|    |    | f. VRAM Trigger Signal Generation 2-38              |

|    | 4. | Video Generation                                    |

|    | 5. | Vertical Deflection                                 |

|    | 6. | Horizontal Sync Signal Generation                   |

|    |    | a, Horizontal Sync and Video Timing Generation 2-42 |

|    |    | b. Horizontal Timing Down Counter                   |

|    |    | c. TIMTBL DMA Transaction                           |

|    |    | d. Frequency Synthesizer 2-4                        |

|    | 7. | Auto Luminance (Brightness).    2-47                |

|    | 8. | Digital Palette Operations.    2-43                 |

|    |    | a. Camera Back Control 2-48                         |

|    |    | b. Filter Wheel Motor Control 2-52                  |

|    |    | c. Filter Wheel Position 2-55                       |

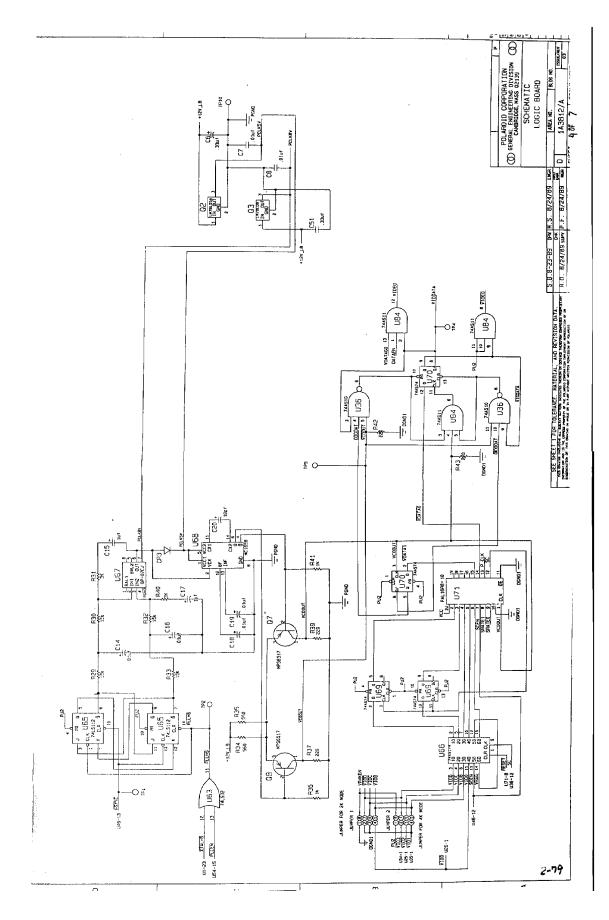

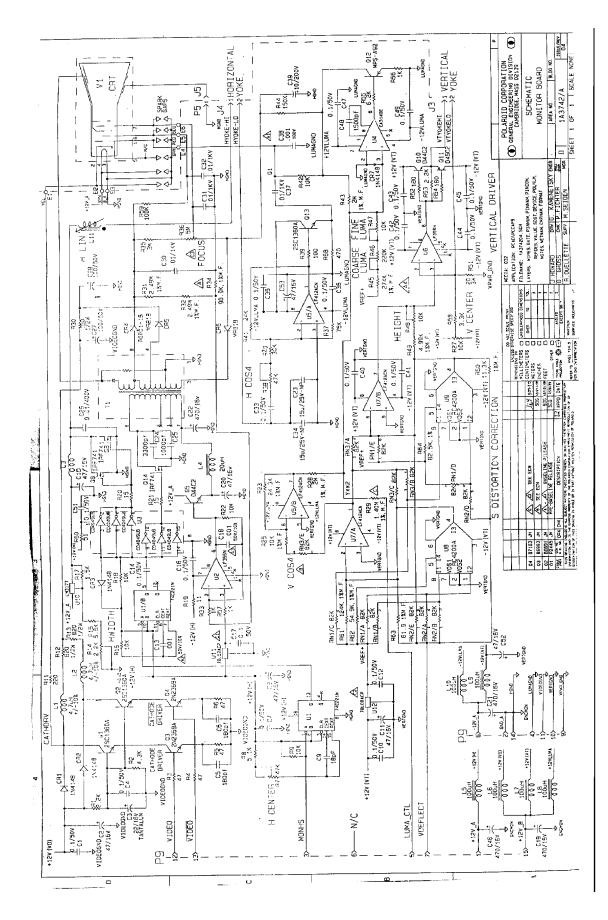

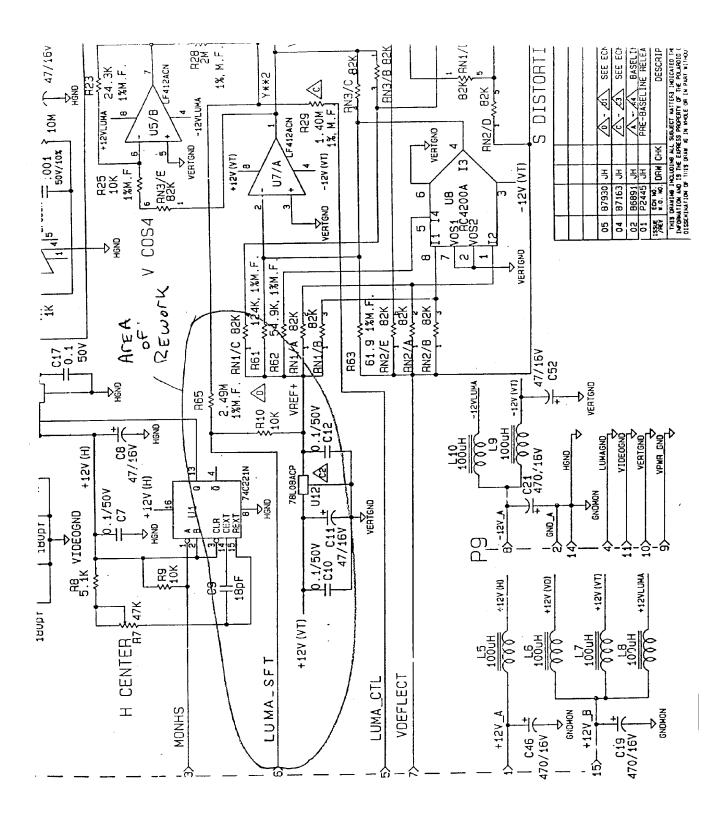

| E. | Mo | nitor Assembly 2-50                                 |

|    | 1. | Controls                                            |

|    | 2. | Cathode Ray Tube 2-60                               |

|    |    | a. Components                                       |

|    |    | b. Functional Description 2-6                       |

|    | 3. | DC Power                                            |

|    |    | a. +12V_ A Regulated DC Voltage 2-62                |

|    |    | b. +12V_ B Regulated DC Voltage                     |

|    |    | c12V_A Regulated DC Voltage 2-6.                    |

|    |    |                                                     |

|    | 4.   | CRT Power                                          |

|----|------|----------------------------------------------------|

|    |      | a. +7 KVDC 2-63                                    |

|    |      | b. +35 VDC 2-64                                    |

|    |      | c130 VDC 2-64                                      |

|    |      | d. +850 VDC 2-65                                   |

|    | 5.   | Cathode Driver 2-65                                |

|    | 6.   | Horizontal Deflection 2-66                         |

|    |      | a. Beam Deflection 2-66                            |

|    |      | b. Beam Shaping 2-67                               |

|    |      | c. Controls 2-67                                   |

|    | 7.   | Vertical Deflection                                |

|    |      | a. Beam Deflection                                 |

|    |      | b. Controls                                        |

|    | 8.   | Luminance                                          |

|    | 9.   | COS4 Exposure Correction. 2-69                     |

| F. | Con  | puter Interface 2-70                               |

|    | 1.   | Centronics Interface 2-70                          |

|    |      | a. Host Interface Cable 2-72                       |

|    |      | b. Centronics Interface Network 2-72               |

|    | 2.   | Small Computer System Interface (SCSI).       2-75 |

|    |      | a. Host Interface Cable 2-75                       |

|    |      | b. SCSI Interface Board 2-75                       |

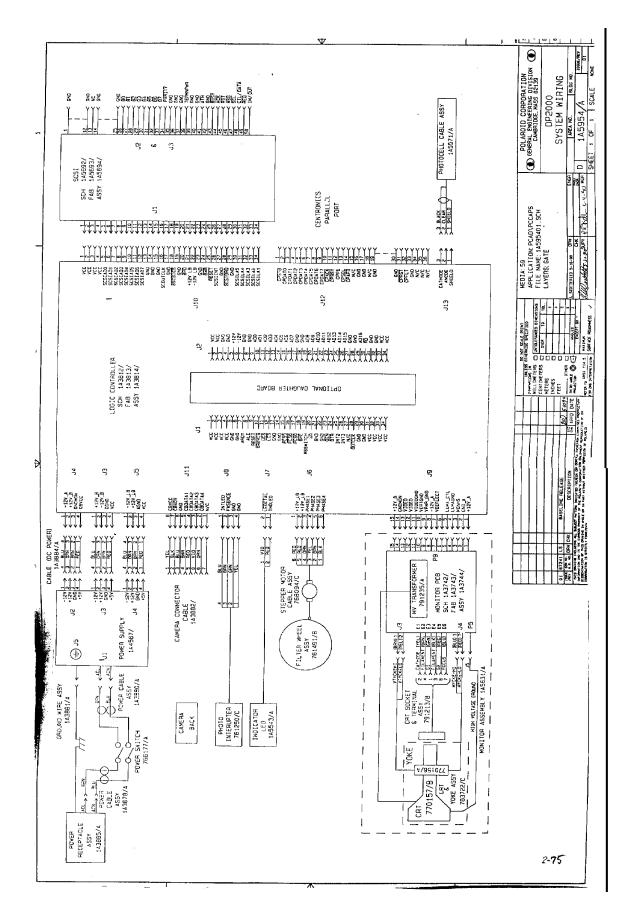

| G. | Syst | em Diagrams and Schematics 2-79                    |

|    | 1.   | Digital Palette Block Diagram                      |

|    | 2.   | System Interconnection Wiring Diagram 2-81         |

## THEORY OF OPERATION

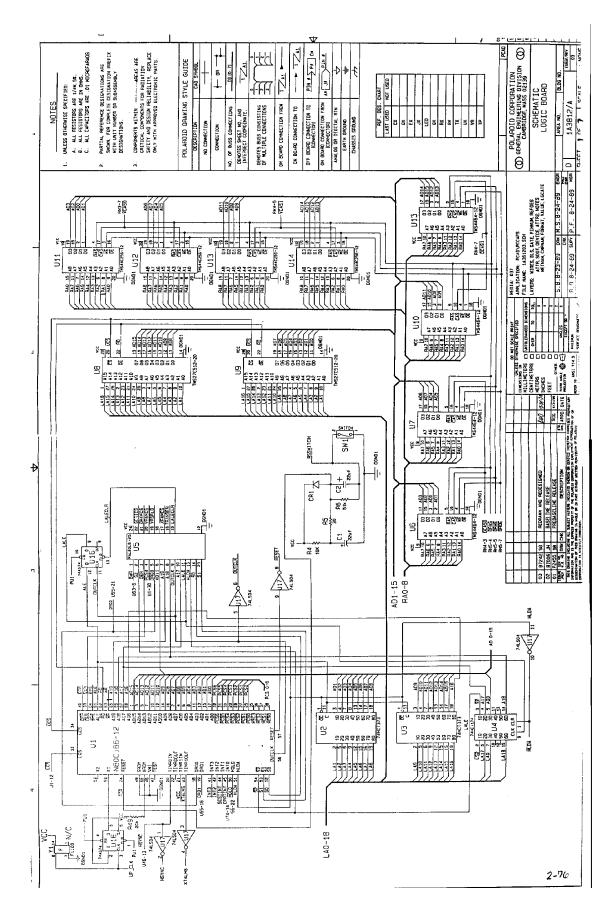

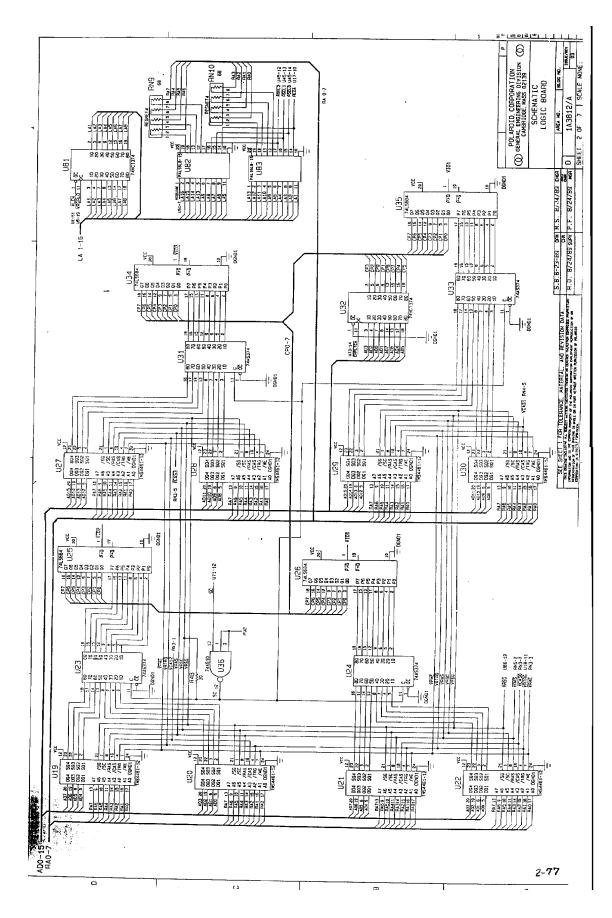

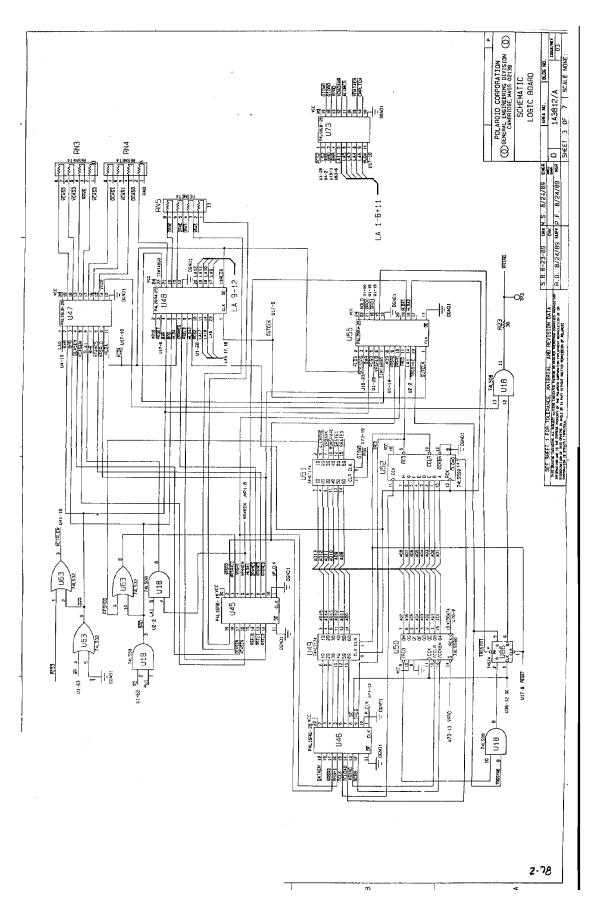

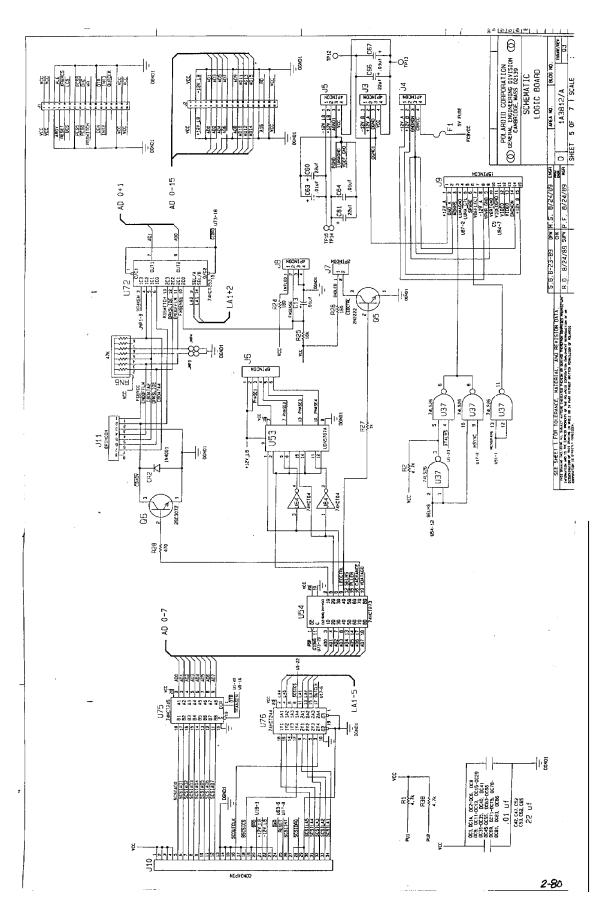

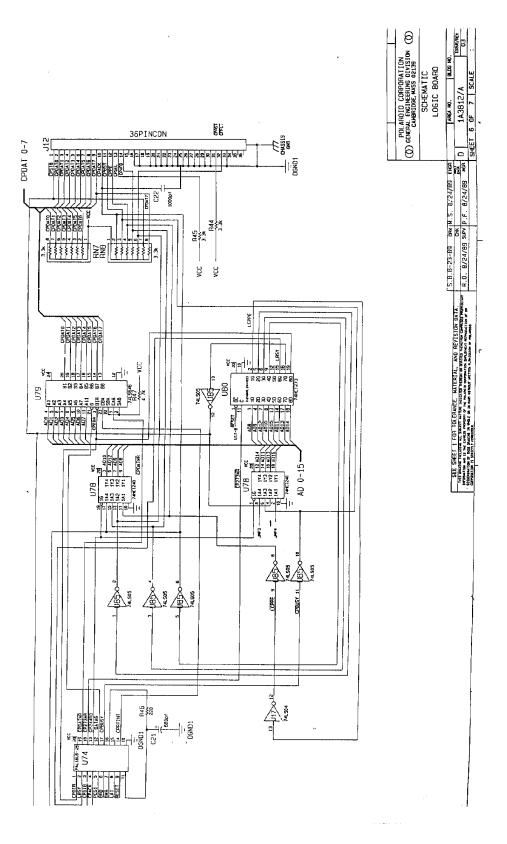

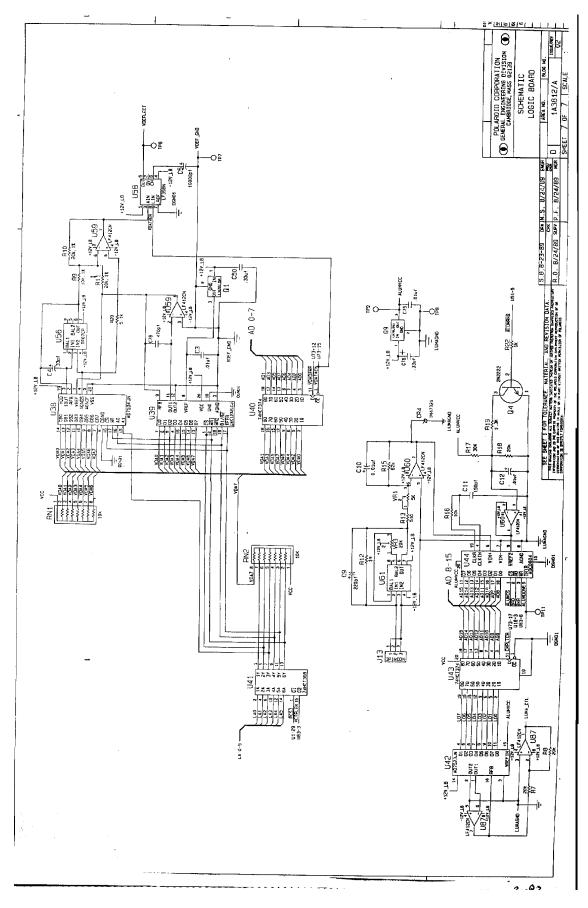

| 3. | Lo | Logic Controller P.C. Board    2-8                        |         |      |  |  |

|----|----|-----------------------------------------------------------|---------|------|--|--|

|    | 0  | Microprocessor Control Network/DRAM Memory                | Sheet 1 | 2-82 |  |  |

|    | 0  | VRAM Memory                                               | Sheet 2 | 2-83 |  |  |

|    | 0  | Horizontal Timing Down Counter                            | Sheet 3 | 2-84 |  |  |

|    | 0  | Video Generation and Pixel Clock<br>Frequency Synthesizer | Sheet 4 | 2-85 |  |  |

|    | 0  | Hardware Control/SCSI Interface                           | Sheet 5 | 2-86 |  |  |

|    | 0  | Centronics Parallel Port Interface Network                | Sheet 6 | 2-87 |  |  |

|    | 0  | Vertical Deflection/Auto Luminance Control                | Sheet 7 | 2-88 |  |  |

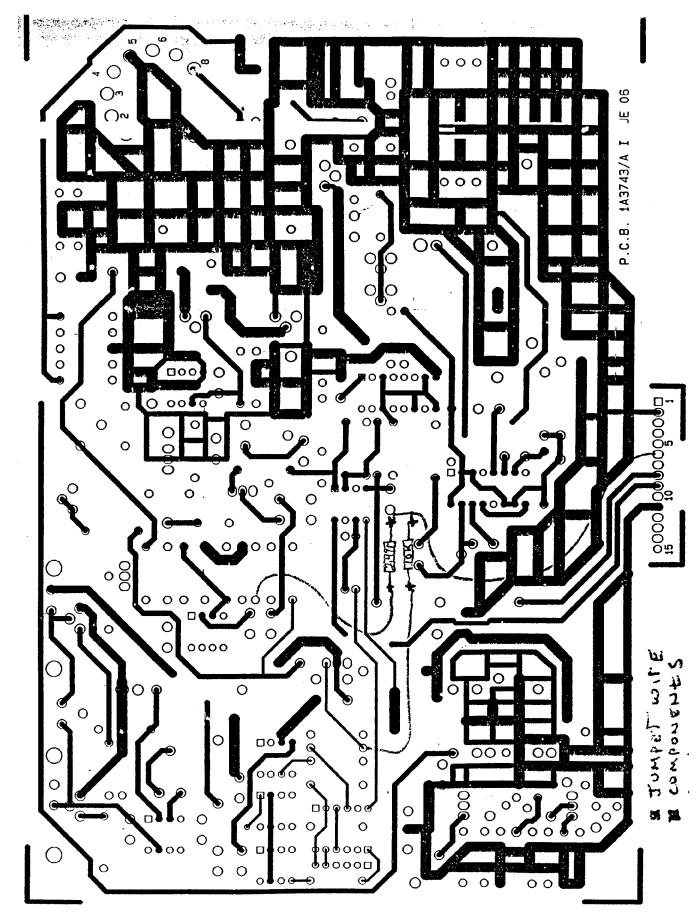

| 4. | Μ  | onitor P.C. Board                                         | ••••    | 2-89 |  |  |

| 5. | Sn | nall Computer System Interface (SCSI) P. C. Board.        |         | 2-90 |  |  |

## List of Illustrations

| Figure 2-11 | Small Computer System Interface (SCSI) P.C. Board.   |                           | 2-90 |

|-------------|------------------------------------------------------|---------------------------|------|

| Figure 2-10 | Monitor P.C. Board                                   |                           | 2-89 |

|             | o Vertical Deflection/Auto Luminance Control         | Sheet 7                   | 2-88 |

|             | o Centronics Parallel Port Interface Network         | Sheet 6                   | 2-87 |

|             | o Hardware Control/SCSI Interface                    | Sheet 5                   | 2-86 |

|             | Frequency Synthesizer                                |                           |      |

|             | o Video Generation and Pixel Clock                   | Sheet 4                   | 2-85 |

|             | o Horizontal Timing Down Counter                     | Sheet 3                   | 2-84 |

|             | o VRAM Memory                                        | Sheet 2                   | 2-83 |

|             | o Microprocessor Control Network/DRAM Memory         | Sheet 1                   | 2-82 |

| Figure 2-9  | Logic Controller P.C. Board.                         | •••••                     | 2-82 |

| Figure 2-8  | System Interconnection Wiring Diagram                |                           | 2-81 |

| Figure 2-7  | Digital Palette Simplified Block Diagram             |                           | 2-80 |

| Figure 2-6  | Cathode Ray Tube                                     |                           | 2-60 |

| Figure 2-5  | Monitor P.C. Board Simplified Block Diagram          |                           | 2-57 |

| Figure 2-4  | Phase-Locked Loop Frequency Synthesizer Block Diag   | ram                       | 2-46 |

| Figure 2-3  | Logic Controller P.C. Board Simplified Block Diagram | 1                         | 2-17 |

| Figure 2-2  | AC/DC Power System                                   | • • • • • • • • • • • • • | 2-14 |

| Figure 2-1  | Exposure System.                                     | • • • • • • • • • • • •   | 2-9  |

## THEORY OF OPERATION

## List of Tables

| Table 2-1         | DC Power System                                  |

|-------------------|--------------------------------------------------|

| Table 2-2         | Microprocessor's Internal Timers                 |

| Table 2-3         | External Interrupt Controller Lines              |

| Table 2-4         | Device I/O Data Select Lines                     |

| Table 2-5         | DMA Controller Channels 2-22                     |

| Table 2-6         | Clock Signals from Microprocessor                |

| Table 2-7         | Microprocessor Control PAL Select Signals 2-27   |

| Table 2-8         | RAM Control PAL's.    2-31                       |

| Table 2-9         | TIMTBL Control Bits 2-35                         |

| <b>Table 2-10</b> | Significance of Address Segment Bits2-41         |

| <b>Table 2-11</b> | Camera Type Codes 2-48                           |

| <b>Table 2-12</b> | Monitor P.C. Board Controls 2-58                 |

| <b>Table 2-13</b> | Control Line for Bi-Directional Octal Latch 2-71 |

| Table 2-14        | Centronics Interface I/O Signal Lines 2-73       |

| <b>Table 2-15</b> | SCSI Interface I/O Signal Lines 2-77             |

## A. Introduction

Note Refer to the provided user manuals for a detailed description of the host computer and its software.

This section of the Service Manual pertains to the Digital Palette hardware. It describes the major systems that make up the Digital Palette and how each system interfaces with the host computer and its software to create an image on the CRT display screen.

There are five major systems internal to the Digital Palette. They are:

o Exposure

o Power Supply Module

o Logic Controller P.C. Board

o Monitor Assembly

o Computer Interface

## **B.** Exposure System

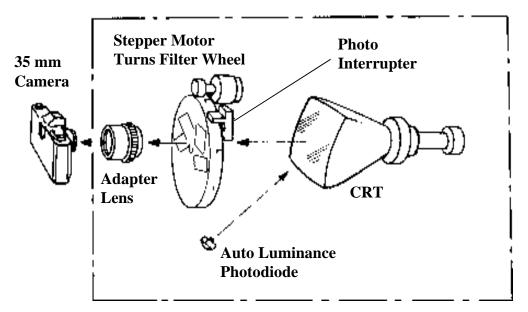

The Exposure System (Figure 2-1) consists of a camera (back) adapter assembly. a filter wheel assembly, a filter wheel photo interrupter (position sensor), a filter wheel stepper motor, an auto luminance photodiode assembly (brightness sensor), and a CRT display assembly.

## 1. Component Description

## a. Camera (Back) Adapter Assembly

Four Polaroid camera back assemblies can be used with the Digital Palette. They are:

- 35mm Camera Back (Auto load, advance, and rewind camera back with high resolution lens);

- Autofilm Camera Back (All Polaroid Autofilms);

- Pack Film Camera Back (All Polaroid 3 1/4 x 4 1/4 pack films);

- 4 x 5 Film Camera Back (All Polaroid 4 x 5 films).

Developed specifically for the Digital Palette by Polaroid, each camera back has its own lens. Focus and aperture are fixed; exposure is controlled by the Digital Palette.

Figure 2-1. Exposure System

Digital Palette is designed for use with Polaroid 35mm film and conventional Polaroid color film. However, conventional 35mm films can be used if their exposure instructions are programmed into the Digital Palette software. For hardcopy of the computer-generated images, the Polaroid Pack Film, AutoFilm, and 4 x 5 Film Camera Backs can be used with their applicable film:

- o Autofilm Camera Back Types 331 and 339

- o Pack Film Camera Back Types 665, 667, 669, and 691

- o 4 x 5 Film Camera Back Types 52, 53, 55, 59

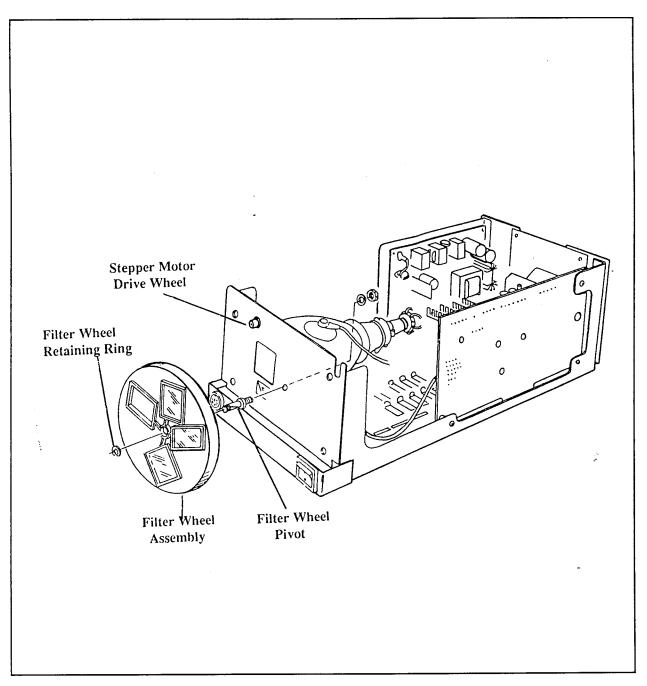

#### b. Filter Wheel Assembly

The filter wheel assembly has five positions associated with it. They are:

- Film Position 0 This position is not usually used by the software driver (host computer); it is a reference point for the system.

- Film Position 1 This position corresponds to the red filter.

- **o** Film Position 2 This position corresponds to the green filter.

- Film Position 3 This position corresponds to the blue filter.

- Film Position 4 This position has no filter. It is a blank opening, used during testing and calibration.

Digital Palette exposures require the positioning of the appropriate colored filters (red, green, or blue) between the images displayed on the CRT and the film.

Filter movement is initiated by the host computer. It instructs the Digital Palette to rotate the filter wheel so that a specified filter is moved between the CRT and the film.

Memory of the last filter wheel position is maintained by the microprocessor control circuit on the Logic Controller P.C. Board. Refer to paragraph D in this Section of the Service Manual for a functional description of the Logic Controller P.C. Board.

Initially, the host computer instructs the microprocessor control circuit to

move the filter wheel to its start (0) position. If the next instruction is to a higher filter position, the filter wheel rotates directly to the specified position. If the instruction is to a lower filter position, the microprocessor control circuit directs the filter wheel to first rotate to the start (0) position and then counts to the requested filter position.

The filter wheel assembly has six notches (or slots) on its rim. The notches are read by the photo interrupter (position sensor). By this method, the specified colored filter is properly positioned in front of the CRT screen before the images are exposed to the film.

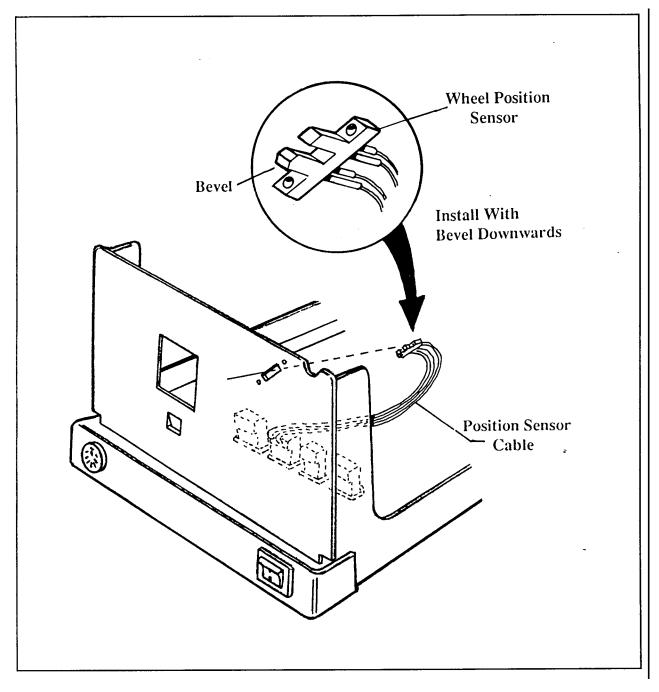

#### c. Filter Wheel Photo Interrupter (Position Sensor)

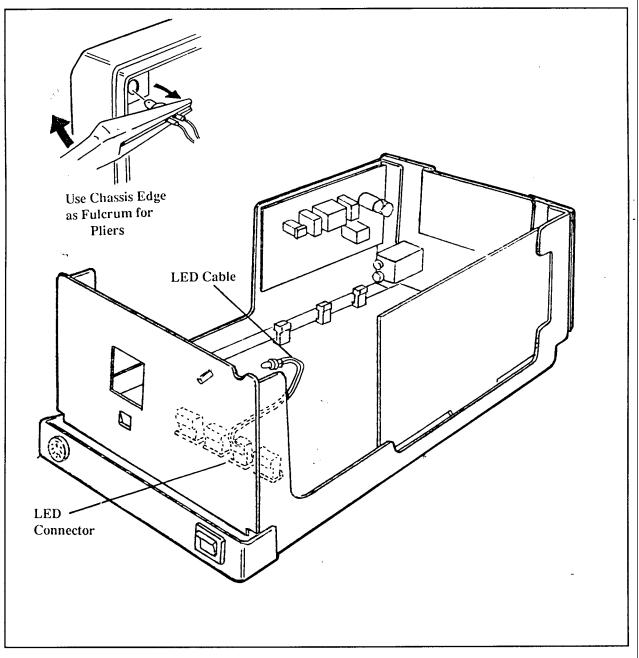

The filter wheel photo interrupter is a U-shaped electrical device mounted on the Digital Palette housing. It consists of a light emitting diode (LED) and a phototransistor.

This device, in conjunction with the microprocessor control circuit on the Logic Controller P.C. Board, generates the signals which are responsible for positioning the specified filter (red, green, or blue) between the CRT display screen and the film.

As the filter wheel assembly rotates to bring the specified colored filter into position, notches on the rim of the filter wheel assembly pass by the photo interrupter.

Each time a notch passes by, a pulse is generated and sent to the microprocessor control circuit on the Logic Controller P.C. Board. This circuit counts the generated pulses to determine when and if the specified colored filter is properly positioned.

Once the specified number of pulses are counted, indicating that the specified filter is in position, the microprocessor control circuit on the Logic Controller P.C. Board stops the filter wheel in that position.

#### d. Filter Wheel Stepper Motor

The filter wheel stepper motor is mounted on the Digital Palette housing. It provides the required driving power to rotate the filter wheel assembly. A small rubber roller attached to the stepper motor shaft transfers this driving power from the stepper motor to the filter wheel assembly.

Pulses from the microprocessor control circuit on the Logic Controller

P.C. Board increment the stepper motor. As the stepper motor turns, it rotates the filter wheel assembly until the specified colored filter (red, green, or blue) is positioned between the CRT and the film.

#### e. Auto Luminance Photodiode Assembly (Brightness Sensor)

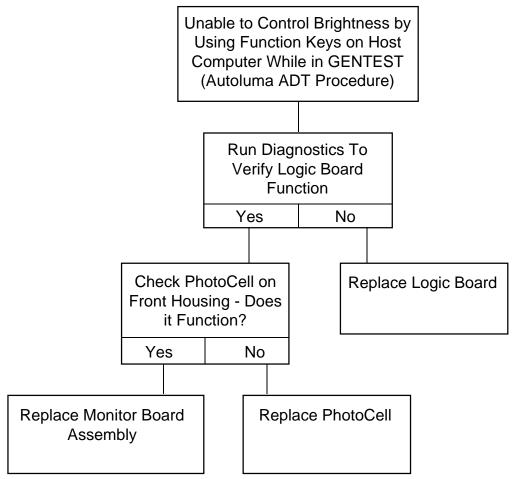

The auto luminance photodiode assembly is a photosensitive diode that is mounted on the Digital Palette housing. This photosensitive diode, in conjunction with the auto luminance network and the microprocessor control circuit on the Logic Controller P.C. Board, monitors the CRT so that its proper brightness is maintained.

#### 2. Exposure Description

Digital Palette uses the ability of the photographic film to remember light, and create a final image of a sequence of colored exposures, each one contributing shape, blending color, or improving resolution. The exposures are made from a two-level black and white computer-generated video image.

Upon command from the host computer, a black and white video image is exposed through different colored filters (red, green, or blue) for specified amounts of time. With this technique, full color images can be created and recorded on film.

For example, if an image was created with three intensities of red, the programmer would create and exposure algorithm which would create on film the image described. The input to the exposure algorithm would be a list of image items, each to be assigned a different intensity of red on film. Refer to the Digital palette Software Guide for a detailed description on how to create an exposure algorithm.

When the image with the three intensities of red is to be recorded by the Digital Palette, the host computer sends an Expose Color command to it. The microprocessor control circuit on the Logic Controller P.C. Board decodes the Expose Color command and positions the red filter on the filter wheel assembly between the CRT and the film. The CRT turns on to expose the first red image items through the filter to the film for the specified time. Once the first exposure is completed, the CRT turns off. This action continues until the film records the image with the three intensities of red.

This sequential exposure technique can also be used to combine exposures of each of the primary colors to produce almost any shade or hue desired. Refer to the Digital Palette Specification Manual for a detailed description of a sequential exposure.

## C. Power Supply Module

## 1. AC Power

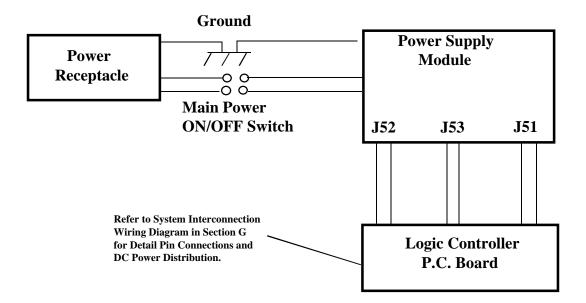

The Digital Palette operates from domestic or international commercial AC Power (Figure 2-2) applied through the Main Power Switch and the Switchable Voltage Selector.

Note

The Digital Palette meets domestic and international power requirements. It automatically operates from 100/115 to 220/240 volts at 50/60 Hz, commercial AC power.

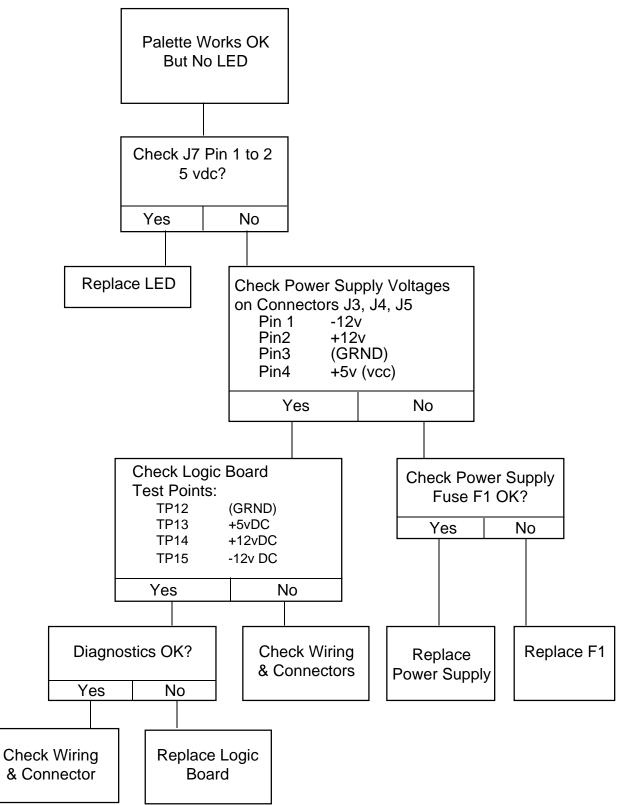

When the Main Power Switch is set to its ON position, AC power is applied to the Power Supply Module. A red LED on the upper right corner of the front panel of the Digital Palette lights to indicate that power is turned on.

The Power Supply Module supplies regulated dc operating voltages to power the Logic Controller P.C. Board. Regulated dc voltages from the Power Supply Module are applied through connectors J51, J52, and J53 to the Logic Controller P.C. Board.

#### 2. DC Power

The Power Supply Module outputs the following regulated dc voltages through connectors J51, J52, and J53 to the Logic Controller P.C. Board:

- **o** +5 vdc

- -12 vdc

- $o \quad +12 \ vdc$

The regulated dc output voltages from the Power Supply Module are used to power the following:

- **o** Logic Controller P.C. Board.

- Monitor Assembly and P.C. Board via connector J9 on the Logic Controller P.C. Board.

- Filter wheel stepper motor via connector J6 on the Logic Controller P.C. Board.

- o Camera back via connector J11 on the Logic Controller P.C. Board.

- Optional Small System Computer Interface (SCSI) via connector J10 on the Logic Controller P.C. Board.

• Optional Daughter Board via connectors J1 and J2 on the Logic Controller P.C Board.

Figure 2-2 shows the DC Power system. Table 2-1 identifies the output voltage/voltages for a particular connector/connectors and indicates the electronic circuitry that it powers.

Figure 2-2. AC/DC Power System Block Diagram

#### Table 2-1. DC Power System

| Connector | Output Voltage | Function                                                                                                                                                                                                                                                  |

|-----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J51       | -12V_LB        | This dc output voltage powers the following on the Logic Controller P.C Board:                                                                                                                                                                            |

|           |                | <ul> <li>o Auto luminance (brightness sensor)<br/>circuit (Sheet 7).</li> <li>o Vertical deflection circuit (Sheet 7).</li> <li>o Optional Daughter Board (Sheet 5).</li> <li>o Optional Small System Computer<br/>Interface (SCSI) (Sheet 5).</li> </ul> |

| Table 2-1. D | C Power System (Con't) |

|--------------|------------------------|

|--------------|------------------------|

| Connector   | Output Voltage | Function                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J51 (Con't) | +12V_LB        | This dc output voltage powers the following on the Logic Controller P.C. Board:                                                                                                                                                                                                                                                                                                                                    |

|             |                | <ul> <li>Video Generation circuit (Sheet 4)<br/>(Pixel Clock frequency Synthesizer).</li> <li>Auto luminance (brightness sensor)<br/>circuit (Sheet 7).</li> <li>Vertical deflection circuit (Sheet 7).</li> <li>Optional Daughter Board (Sheet 5).</li> <li>Optional Small System Computer<br/>Interface (SCSI) (Sheet 5).</li> <li>Filter wheel stepper motor circuit via<br/>connector J6 (Sheet 5).</li> </ul> |

| J52         | -12V_A         | This dc output voltage powers the following on the Monitor P.C. Board:                                                                                                                                                                                                                                                                                                                                             |

|             |                | <ul> <li>o Luminance circuit.</li> <li>o Vertical deflection circuit (S-Distortion<br/>Correction, Height, Center, and Driver).</li> <li>o COS4 exposure correction circuit.</li> </ul>                                                                                                                                                                                                                            |

|             | +12V_B         | This dc output voltage powers the following on the Monitor P. C. Board:                                                                                                                                                                                                                                                                                                                                            |

|             |                | <ul> <li>o CRT Cathode Driver Circuit.</li> <li>o Luminance circuit.</li> <li>o Vertical deflection circuit (S-Distortion Correction, Height, Center, and Driver).</li> <li>o COS4 exposure correction circuit.</li> </ul>                                                                                                                                                                                         |

|             | CBVCC (+5vdc)  | This dc output voltage powers the camera<br>back drive motor circuit via connector J11<br>on the Logic Controller P.C. Board.                                                                                                                                                                                                                                                                                      |

| J53         | -12V_B         | This dc output voltage is not used.                                                                                                                                                                                                                                                                                                                                                                                |

## Table 2-1. DC Power System (Con't)

| Connector   | Output Voltage | Function                                                                                                                                            |

|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| J53 (Con't) | +12V_A         | This dc output voltage powers the following on the Monitor P.C. Board:                                                                              |

|             |                | <ul> <li>o Horizontal deflection circuit (Center, width, and Linearity).</li> <li>o CRT heater filament.</li> </ul>                                 |

| J51/J53     | VCC (+5vdc)    | The dc output voltages via these connectors<br>supply +5 vdc to power the digital circuits<br>on the Logic Controller P.C. Board<br>(Sheets 1 - 7). |

## **D.** Logic Controller P.C. Board

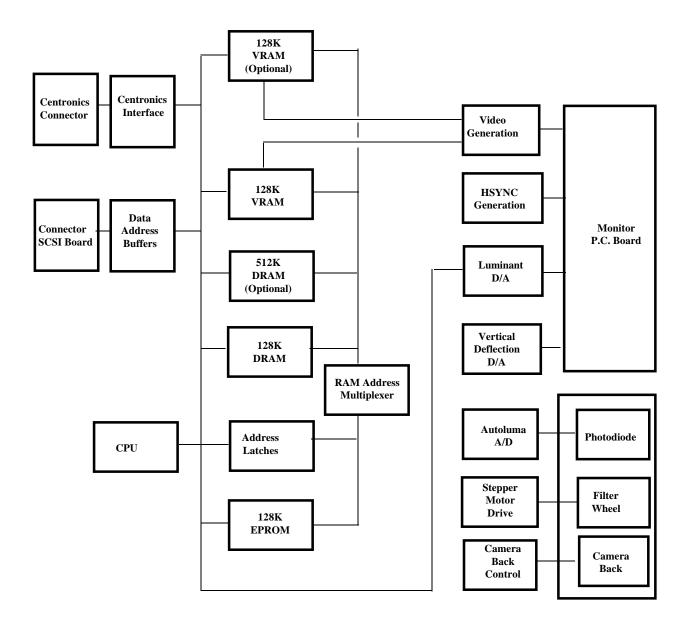

The Logic Controller P.C. Board contains all the necessary electronic circuitry to con trol the Digital Palette operations specified by the computer software and to communi cate with the host computer.

The electronic circuits that make-up the Logic Controller P.C. Board are:

- o Microprocessor Control Network

- o Erasable Programmable Memory (EPROM)

- o Random Access Memory (RAM)

- Video Signal Generation

- Vertical Deflection

- o Horizontal Sync Signal Generation

- Auto Luminance (Brightness)

- o Digital Palette Operations (Camera Back, Filter Wheel Motor, and Position)

Figure 2-3 shows a simplified block diagram of the Logic Controller P.C. Board. Refer to the Logic Controller P.C Board logic schematics (Figure 2-9, sheets 1 - 7) in Section G of this Service Manual for detailed information pertaining to the logic circuits on the Logic Controller P.C. Board. Both the simplified block diagram and the detailed logic schematics should be referenced while reading the following functional descriptions of the circuits that make-up the Logic Controller P.C. Board

#### 1. Microprocessor Control Network

The Microprocessor Control Network (Figure 2-9, sheet 1) consists of:

- a. Microprocessor (CPU)

- b. 40 MHz Clock

- c. Reset Control

- d. Address Latches

- e. Microprocessor Control PAL

- f. Communications Bus

#### a. Microprocessor (CPU)

The CPU (Figure 2-9, sheet 1) used in the Digital Palette to control the sequential exposure of a computer-generated image is an enhanced 80186, 16-Bit microprocessor. Its purpose is to process the instructions supplied to it by the host computer software. In a sense, this microprocessor is the Digital Palette's brain: it controls the Digital Palette by directing the necessary hardware functions that controls the sequential exposure.

When the microprocessor receives instructions via the applicable parallel

Figure 2-3. Logic Controller P.C. Board Simplified Block Diagram

#### THEORY OF OPERATION

interface, it interprets (decodes) them and then directs the specified operating function of the Digital Palette - downloads pixel image information from Dynamic Memory to Video Memory, correctly positions the filter wheel so that the specified color filter is placed between the film frame and the CRT display screen, opens the attached camera back shutter, exposes the pixel image information, closes the attached camera back shutter, ejects or advances the film frame.

The instructions that the microprocessor receives are in the microprocessor's own vocabulary, known as the microprocessor's instruction set. Refer to the Parallel Port Interface Specification Manual for detailed information pertaining to the instruction set format from the host computer.

The Microprocessor operating features include:

- 1) Programmable Timers

- 2) Programmable Interrupt Controller Lines

- 3) Device I/O Select Lines

- 4) DMA Controller Channels

- 5) Programmable Memory

The following paragraphs describe each of the microprocessor features.

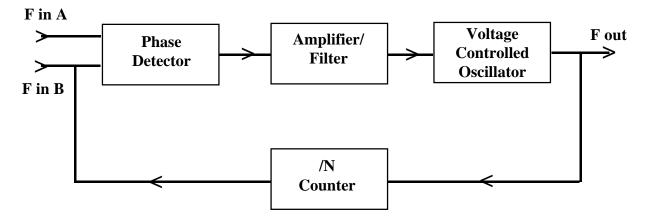

#### 1) **Programmable Timers**

The microprocessor contains three 16-bit programmable internal timers: Timer 0 (TIMRO IN/OUT), Timer 1 (TIMR1 IN/OUT), and Timer 2 (TIMR2 - No Output Lines). Table 2-2 lists and describes the function of each of the microprocessor 's internal timers.

#### Table 2-2. Microprocessor's Internal Timers

#### Timer

#### Function

- **Timer 0 (TIMRO)** This internal timer generates the Horizontal Synthesized Sync (/HSYNC) signal. It is used for diagnostic purpose to verify that the pixel frequency synthesizer is functioning properly.

- **Timer 1 (TIMR1)** This internal timer generates the Horizontal Sync (XTALHS) signal. It is programmed to run from the internal clock.

## Table 2-2. Microprocessor's Internal Timers (Con't)

| Timer                      | Function                                                                                                                                                                                    |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timer 1 (TIMR1)<br>(Con't) | The XTALHS signal is used to drive the phase detector of the pixel clock frequency generator.                                                                                               |

| Timer 2 (TIMR2)            | This internal timer generates a 1 msec interrupt signal that<br>is used for program timing. <b>IT IS ONLY USED FOR</b><br><b>INTERNAL COUNTING. IT HAS NO</b><br><b>INPUT/OUTPUT LINES.</b> |

#### 2) Programmable Interrupt Controller Lines

The microprocessor has four external interrupt controller lines. It also has number of internal interrupt sources such as internal timers and DMA controllers. Refer to the paragraph 1 for a description of the internal timers and to paragraph 4 for a description of the DMA Controllers.

Table 2-3 lists and describes each of the microprocessor 's external general purpose interrupt controller lines.

| Interrupt Controller Line            | Function                                                                                                                                         |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupt 0 (INTO)                   | This interrupt line generates the Centronics Port<br>Interrupt (CPRTINT).                                                                        |

| Interrupt 1 (INT1)                   | This interrupt lines generates the SCSI Port<br>Interrupt (SCSIINT).                                                                             |

| Interrupt 3 and 4<br>(INT3 and INT4) | These interrupt lines are not used at this time. They<br>are connected to the external bus and are available<br>for devices on expansion boards. |

## Table 2-3. External Interrupt Controller Lines

## 3) Device I/O Select Lines

The microprocessor has 64 Kbytes of I/O space. Within this I/O space, the microprocessor is capable of generating select signals for up to seven devices. The select lines are active for seven contiguous blocks of 128 bytes above a programmable base address. This base address is set by the start up code to be 0x0000 in the I/O space.

Table 2-4 lists and describes the microprocessor's select lines that control the various devices on the Logic Controller P.C. Board.

| Select Line | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCSO        | This select line is asserted for I/O addresses $0x0000$ to $0x7F$ . Address Bit 1 is the only address line in this space which is important.                                                                                                                                                                                                                                                                                                                                                                                                         |

|             | When this bit is low, DMA controller channel 0 and 1 transactions are disabled. When high, DMA controller channel 0 and 1 transactions are enabled.                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | Therefore, a write to I/O address 0 disables DMA<br>tranactions and a write to I/O address 2 enables I/O<br>transactions. During these write cycles, the content select<br>lines are ignored. This capability is required in interrupt<br>service routines which are time critical. It is important in<br>these routines to disable further innterrupts and guarantee<br>that DMA transactions will not occur. In these routines,<br>the DMA controller channels are temporarily disabled<br>until the time critical portion of the routine has run. |

| PCS1        | This select line is asserted for I/O addresses 0x80 to 0xFF.<br>Its I/O space is dedicated to the Centronics Port. Address<br>Bit 1 is the only address line in this space which is<br>important.                                                                                                                                                                                                                                                                                                                                                    |

|             | The I/O map for this space is:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             | 0x0080 WR - Centronics Data Port Write<br>0x0080 RD - Centronics Data and Control Port<br>0x0082 WR - Centronics Control Port Write                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Select Line | Function                                                                                                                                                                                                                                                                                               |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCS2        | This select line is asserted for I/O addresses 0x100 to 0x17F.                                                                                                                                                                                                                                         |

|             | The I/O map for this space is:                                                                                                                                                                                                                                                                         |

|             | 0x0100 RD- General I/O Read0x0100 WR- General I/O Write108 WR- Vertical D/A Data Write108 WR- Video Data Position Read118 RD- Clear Vertical D/A Data Enable118 WR- Enable Vertical D/A Data120 RD- Clear Refresh DMA Transactions120 WR- Enable Refresh DMA Transaction140 RD- Auto Luminant A/D Read |

| PCS3        | This select line is asserted for I/O addresses 0x180 to 0x1FF. It address space is used to control the loading of information into the vertical D/A devices. The low 6 bits of the address bus (LA0 to LA5) serve as the control bits for the Vertical D/A's.                                          |

| PCS4        | This select line is asserted for addresses 0x200 to 0x27F.<br>Its address space is used for the optional SCSI daughter<br>board.                                                                                                                                                                       |

| PCS5        | This select line is asserted for addresses 0x280 to 0x2FF. It is available on the external bus connectors for I/O devices on expansion boards. There are no I/O devices at this time that will respond to reads or writes in this I/O space.                                                           |

| PCS6        | This select line is asserted for addresses 0x300 to 0x37F. It is available on the external bus connectors for I/O devices on expansion boards. There are no I/O devices at this time that will respond to reads or writes in this I/O space.                                                           |

## Table 2-4. Device I/O Data Select Lines (Con't)

## 4) DMA Controller Channels

The microprocessor has two general purpose DMA controller channels: DMA controller channel 0 and DMA controller channel 1. It also has a third type DMA controller channel transfer that is generated externally. Table 2-5 lists and describes the DMA controller channels.

## Table 2-5. DMA Controller Channels

| DMA Controller Channel | Function                                                                                                                                                                                                                                                                                                        |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMA 0                  | This DMA controller channel is available for<br>general tasks. It is available for DMA transactions<br>from the optional SCSI port.                                                                                                                                                                             |

| DMA 1                  | This DMA controller channel is dedicated to<br>performing a VRAM shift register load at the end<br>of the active video time of the horizontal scan. It<br>will read a word from a table in memory and write<br>to VRAM.                                                                                         |

|                        | This special write will consider the address as the<br>VRAM row which is loaded into VRAM shift<br>register. This data which is written during this<br>transfer contains the comparator value and the<br>luminant level. The comparator value is in the low<br>byte and the luminant level is in the high byte. |

| DMA External           | This external DMA controller channel is used to<br>update the horizontal time. It is also used to<br>provide refresh cycles to the DRAM and VRAM<br>memory. This refresh cycle is called the TIMTBL<br>DMA cycle. It uses the HOLD/HLDA signals from<br>the microprocessor.                                     |

#### 5) **Programmable Memory**

The Microprocessor Control Network (Figure 2-9, sheet 1) uses three types of memory:

- Erasable Programmable Read Only (EPROM)

- o Dynamic Random Access Memory (DRAM)

- Video Random Access Memory VRAM)

Refer to the paragraphs D3, D4, and D5 for a detailed description of how the Microprocessor Control Network uses its available memory.

## b. 40 MHz Clock

The 40 MHz Clock is a crystal oscillator (Figure 2-9, sheet 1) that provides the necessary clock pulses to run the Microprocessor and its associated circuitry.

When the Digital Palette is powered up, the crystal oscillator generates a 40 MHz clock (UP CLK) signal. This UP CLK signal provides the necessary clock pulses that operate the microprocessor. It also provides the necessary clock pulses that operate the RAM Timing Control PAL (RCTLP1) in the RAM Contol circuit. Refer to the paragraph 3 for a functional description of RAM Timing Control PAL.

The UP CLK signal is reduced to 20 Mhz clock signal by the divide-by-2 network and then applied to the clock input of the microprocessor. This inputted clock signal provides the necessary internal timing for the microprocessor.

The microprocessor, in turn, divides its input clock signal by 1/2 and then outputs three clock signals to the associated circuits that are required to operate synchronously with it. Table 2-6 lists and defines the clock signals outputted by the microprocessor.

| Clock Signal | Function                                                                                                                                                                                                                                                                                         |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OUTCLK       | This microprocessor clock signal operates:                                                                                                                                                                                                                                                       |  |

|              | <ul> <li>o Control PAL for the microprocessor.</li> <li>o Addressable latches for the microprocessor.</li> <li>o Control PAL's for the Horizontal Timing Generator.</li> <li>o Addressable latch for the optional SCSI Parallel<br/>Interface.</li> </ul>                                        |  |

| HSYNC        | This microprocessor clock signal operates:                                                                                                                                                                                                                                                       |  |

|              | <ul> <li>o Horizontal Sync Driver. (This Horizontal Sync Driver produces the necessary Horizontal Sync signal (MONHS) that operates the Horizontal Deflection network on the Monitor P.C. Board.</li> <li>o Horizontal Timing Generator.</li> <li>o Horizontal Frequency Synthesizer.</li> </ul> |  |

| XTALHS       | This microprocessor clock signal, in conjunction with the HSYNC clock signal, operates the Horizontal Frequency Synthesizer.                                                                                                                                                                     |  |

## Table 2-6. Clock Signals from Microprocessor

## c. Reset Control

The Reset Control circuit (Figure 2-9, sheet 1) provides a reset signal that initializes the Microprocessor Control network and its associated circuitry. This reset signal is generated automatically when the computer Imager is first powered up (turned on) or when the user momentarily presses the RESET switch on the rear panel of the Digital Palette.

## 1) Power Up Reset

When the Digital Palette is turned on, the RC network in the Reset Control circuit generates a power reset signal that is applied to the reset line of the microprocessor. This signal initializes the microprocessor. The microprocessor generates a RESET and a clear signal that initializes its associated circuitry. The generated RESET signal initializes:

- Horizontal Timing Generator (Control PAL, Pixel Latch, Horizontal 9-Bit Down Counter).

- **o** Video Generation Circuit (Address Latch).

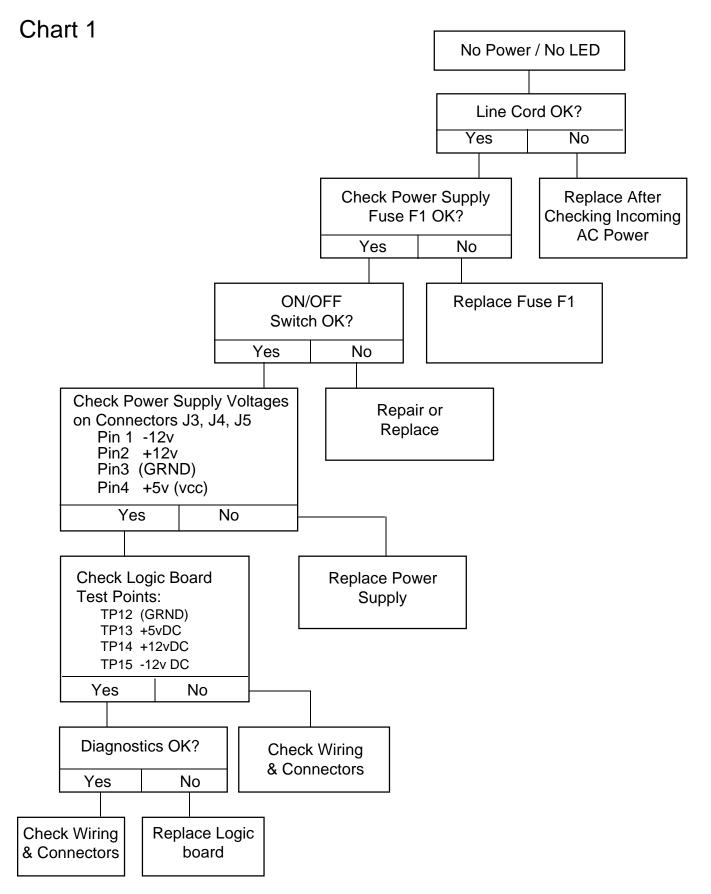

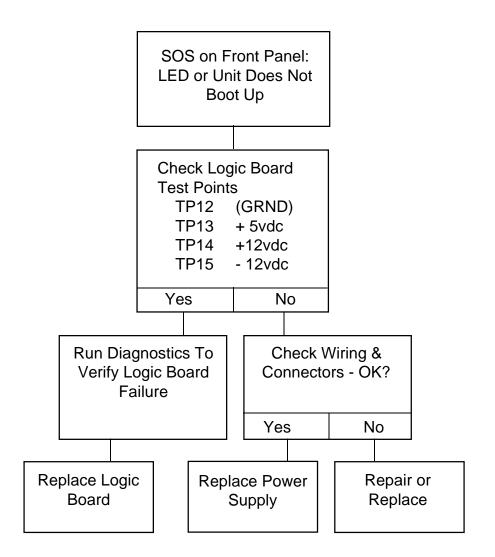

Upon Power-up or manual Reset, the firmware in EPROM will perform system diagnostics. If any diagnostics fail, the front panel LED will blink the familiar SOS pattern. If all diagnostics pass, the LED will by turned on. Four diagnostics are performed:

- **o** DRAM diagnostics: the base 128Kbytes of memory are tested with various patterns. If the optional 512K of DRAM is available, it is also tested.

- **o** VRAM diagnostics: the VRAM devices are tested with similar patterns to verify their operation.

- Frequency synthesizer operation: the frequency synthesizer is tested by allowing it to lock and verifying that the synthesized HSYNC signal, which appears as an input to the TIMR1 input of the CPU, is stable and at the proper frequency.

- Video data test: the feed-back loop of video data is used to verify that video data is being properly generated.

If the base 128 Kbytes of memory fails it's diagnostics, the '186 is unable to perform any additional diagnostics and will not be able to communicate with the host. Any other diagnostic failure, however, does not prevent the '186 from communicating with the host system. In this case, the host can use the INQUIRE ERROR command to determine the specific diagnostic which has failed.

#### 2) Manual Reset

The manual RESET switch mounted on the rear panel of the Digital Palette initializes the Digital Palette just like the Power Up Reset explained in paragraph 1. However, it is also used to expose the resident test image to verify that the Digital Palette is functioning properly.

#### THEORY OF OPERATION

When the Digital Palette operator momentarily presses the RESET switch, the Reset Control circuit generates a reset signal that initializes the Microprocessor Control network and its associated circuitry. The reset signal from the RC network of the Reset Control circuit is ac coupled so that the switch can be pressed for an extended period of time (in the order of a few seconds). In most cases, it is released quickly resulting in a very short reset signal that causes the microprocessor and its associated circuitry to be initialized.

If the RESET switch is held in (pressed) for an extended period of time, the microprocessor still initializes the Digital Palette but it also reads the state of the pressed RESET switch. Once the microprocessor determines that the RESET switch is in its pressed state, the microprocessor flags the resident test image program for the applicable EPROM and then initiates an exposure sequence of the resident test image.

## 3) Host Computer Reset

The Microprocessor Control Network and its associated circuitry can also be initialized by the host computer prior to or during an exposure sequence of the computed-generated image. In fact, a RESET command is typically the first command issued by a host computer application.

If a RESET command is sent to the Digital Palette by the host computer, it does not affect the exposure state or any images that are completely buffered for an exposure. A prior image that was completely transmitted will be properly exposed. Any partially transmitted image will be lost (cleared).

For example, assume that a prior application program issused an Exposure Sequence (Start Exposure, Parameters, Expose Color, Pixel Image Data for a particular color, and Terminate Exposure) before it was interrupted by a subsequent Reset command. This command would cancel the partially transmitted image, set all parameters to their default values, and if possible eject or advance the film. After the RESET command, the Digital Palette is again ready to begin an exposure sequence. For detailed information pertaining to the RESET command from the host computer, refer to the Digital Palette Product Specification Manual or the applicable Parallel Port Interface Specifications Manual.

## d. Address Latches

Address latches (figure 2-9, sheet 1) are used because the microprocessor has a multiplexed address/data communications bus. At the beginning of a memory or an I/O cycle, the applicable address appears on the communications bus. It must be externally latched by the address latch. Data will appear on the communications bus during the remainder of the memory or I/O cycle.

## e. Microprocessor Control PAL

The Microprocessor Control PAL (Figure 2-9, sheet 1) provide the necessary decoded select signals for the Digital Palette Buffer Memory (DRAM and VRAM Memory). It also provides select signals for the optional SCSI interface.

Specified select signals from the microprocessor Control PAL download the image data initially stored in the DRAM memory into VRAM memory. From VRAM memory, the image data is sent to the Video Generation circuit where it is processed into a serial VIDEO signal that turns on the CRT in the Monitor P.C. Board.

Table 2-7, on the following page, lists and describes the function of each of the decoded select signals.

# Table 2-7. Microprocessor Control PAL Select Signals

| <u>Select Signal</u> | <b>Function</b>                                                                                                                                                                                                                                 |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SCSICS               | Asserted during an IO read/write cycle to the optional SCSI device. This signal is guaranteed to be asserted only while the address lines are stable.                                                                                           |  |

| DRAMCS               | Asserted during a memory read/write cycle to the base 128K bytes of memory.                                                                                                                                                                     |  |

| VRAMCS               | Asserted druing a memory read/write cycle to the VRAMS.                                                                                                                                                                                         |  |

| ľ                    | <b>NOTE:</b> For memory read/write cycles to the optional 512K DRAM, both DRAMCS and VRAMCS are asserted. Both of these signals go to the RAM control PAL, RCTLP1, which generates the appropriate control signals to the memory devices.       |  |

| VRSALD               | VRAM Shift Register Load. This signal is asserted on any IO read/write cycle to the IO addresses 800hex to FFEhex. (LA11 is high) during this cycle, the VRAMS will load a row of data into their internal shift registers.                     |  |

| XRAMCS               | This signal is asserted on any memory read/write cycle<br>to access additional memory on an expansion board. This<br>expansion option does not currently exist.                                                                                 |  |

| TRANSEN              | This signal controls the data buffers for the optional SCSI board.                                                                                                                                                                              |  |

| LALECLR              | This signal clears the latch which generates LALE.<br>LALE is asserted on the rising edge of OUTCLK and must<br>be deasserted on the falling edge of OUTCLK to guarantee<br>that the address lines are valid for the entire duration of<br>LALE |  |

## f. Communications Bus

The communications bus consist of 16 lines. It functions as an address/data bus and a latch /address bus.

As an address/data bus, it provides the signal flow path for all data and instruction codes between the Digital Palette and the host computer. It also provides the signal flow path for all data and instruction codes between the microprocessor and the electrical devices that control the operations of the Digital Palette.

As a latch/address bus, it provides the signal flow path for address instructions between the control PALs and the applicable address latches for a particular operation (i.e., loading the VRAM shift registers).

## 2. Erasable Programmable Read Only Memory (EPROM)

Two 8-bit EPROM's (Figure 2-9, sheet 1) are used in conjunction with the Microprocessor Control network to contol the operating functions of the Digital Palette. Depending on the Digital Palette's configuration, the two 8-bit EPROM's can total 64 Kbytes or 128 Kbytes of memory. For 64 Kbyte memory configurations, each 8-bit EPROM contains 32 Kbytes of memory. For 128 Kbyte memory configurations, each EPROM contains 64 Kbytes of memory. (On newer boards there are only two 64Kbytes of memory.)

The two 8-bit EPROM's are considered the Digital Palette's firmware because they contain the necessary operating program that make the Digital Palette work. Collectively, they store the Digital Palette operating programs that:

- o Initializes the Digital Palette when it is first powered Up (Turned On).

- o Runs POWER ON diagnostics

- o Checks to see if the Digital Palette has optional DRAM memory available.

- Provides a resident test image for the user to self test the exposure operation by holding in the RESET pushbutton on the back panel of the Digital Palette.

- o Controls the auto luminance operation.

- **o** Controls the positioning of the filter wheel.

- Controls the blinking of the front panel LED to indicate when an exposure sequence is taking place.

- Controls the sequential exposure of the computer-generated image.

- Controls vertical deflection up to 4K lines, depending on the configuration of the Digital Palette.

- Controls the ejection or the advancement of the film frame after the sequential exposure computer-generated image is completed.

#### THEORY OF OPERATION

#### 3. Random Access Memory (RAM)

The Digital Palette uses two types of Random Access Memory: Dynamic Read Address Memory (DRAM) and Video Random Access Memory (VRAM).

The DRAM memory receives and stores the commands and pixel image data via the applicable parallel interface from the host computer. Its the exposure sequence (Start Exposure, Parameters, Expose Color, Pixel Image Data for a particular color, and Terminate Exposure) that is loaded into the DRAM's.

The VRAM is the exposure memory. It momentarily stores the pixel image data when it is downloaded from the DRAM memory.

#### a. Dynamic Random Access Memory (DRAM) (Figure 2-9, sheet 1)

The basic Digital Palette Configuration uses 256K of DRAM (four 64K x 4-Bit DRAM's) as its storage memory. The Digital Palette can accomodate an additional 512K of DRAM (four optional 256K x 4-Bit DRAM's).

The DRAM address bus (RA0 - RA7) is generated by two RAM control PAL's in the RAM Control circuit. Its data lines are connected directly to the Address/Data Communications Bus. Select signals (control lines) are generated by the PAL's in the RAM Control circuit. Refer to paragraph c for a functional description of the RAM Control circuit.

#### b. Video Random Access Memory (VRAM) (Figure 2-9, sheet 2)

The basic Digital Palette Configuration uses 128K of VRAM (four 64K x 4-Bit VRAM's) as its exposure memory. The Digital Palette can accomadate an additional 128K of VRAM (four optional 64K x 4-Bit VRAM's).

The VRAM address bus (RA0 - RA7) is generated by two RAM control PAL's in the RAM Control circuit. Its data lines are connected directly to the Address/Data Communications Bus. Select signals (control lines) are generated by the PAL's in the RAM Control circuit. Refer to paragraph c for a functional description of the RAM Control circuit.

The basic Digital Palette Configuration (128K of VRAM) provides the ability to expose images with a horizontal resolution of 512 to 2048 pixels. This configuration of the Digital Palette uses four 64K x 4 VRAM's.

The Digital Palette with the optional VRAM's added (Additional 128K of VRAM) provides the ability to expose images with a horizontal resoultion up to 4096 pixels.

Refer to paragraph d for a functional explanation of the VRAM Internal Shift Register.

## c. RAM Control PAL's (Figure 2-9, sheet 3)

There are two types of memory transactions (transfers) for the DRAM and VRAM memory: when the microprocessor controls the Address/Data communications bus and when the DMA Channel Controller HOLD/ HLDA (TIMTBL) cycle of the microprocessor controls the Address/Data communications bus.

When the microprocessor controls the Address/Data communications bus, the following memory transactions take place:

- o DRAM (128K) Read/Write Cycle

- o DRAM (512K) Read/Write Cycle

- o VRAM (2K Mode) Video Resolution Read/Write Cycle

- o VRAM (4K Mode) Video Resolution Read/Write Cycle

When the DMA Channel Controller Hold/HLDA (TIMTBL) cycle of the microprocessor controls the Address/Data communications bus, the following memory transactions take place:

- DRAM (128K) reads DMA Channel Controller Hold/HLDA (TIMTBL) entry (no intermediate VRAM shift register load occurs)

- VRAM intermediate shift register load 1 (VRSRINTLD1)

- VRAM intermediate shift register load 2 (VRSRINTLD2)

- VRAM intermediate shift register load 3 (VRSRINTLD3)

Both types of memory transactions are controlled by five RAM control PAL's (Figure 2-9, sheet 3). Table 2-8 lists and defines the function each of the RAM Control PAL's.

#### THEORY OF OPERATION

# Table 2-8. RAM Control PAL's

| Control PAL | Function                                                                                                           |         |                                                                                                                                                                                                                                                                  |

|-------------|--------------------------------------------------------------------------------------------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCTLP1      | The RCTLP1                                                                                                         | contro  | ol PAL provides the following operation signals:                                                                                                                                                                                                                 |

| 0           | RSEL2<br>RSEL1<br>RSELO                                                                                            | -       | Control signals sent to the RAM Address Multiplexer<br>PALS, RCTLP4 and RCTLP5. These control lines<br>are used to indicate which addresses are sent to the<br>DRAMS and VRAMS.                                                                                  |

| 0           | VCASEN                                                                                                             | -       | VRAM CAS enable. Asserted when CAS (Column Address Strobe) should be asserted on the VRAMS.                                                                                                                                                                      |

| 0           | DCASEN                                                                                                             | -       | DRAM CAS enable. Asserted when CAS should be asserted to the DRAMs.                                                                                                                                                                                              |

| 0           | DRAS                                                                                                               | -       | This is the RAS (Row Address Strobe) signal for the DRAM devices.                                                                                                                                                                                                |

| 0           | VRAS                                                                                                               | -       | This is the RAS signal for the VRAM devices.                                                                                                                                                                                                                     |

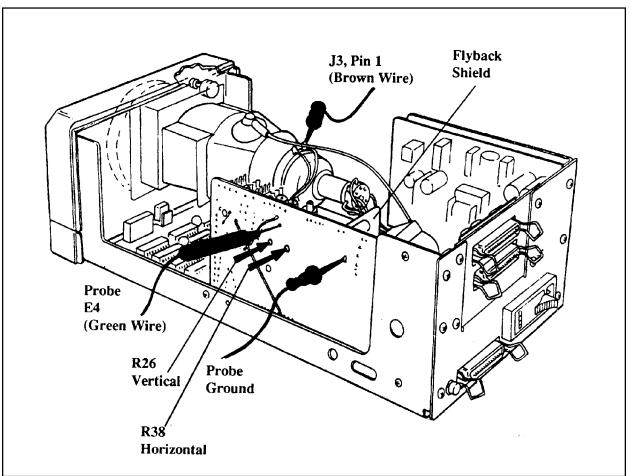

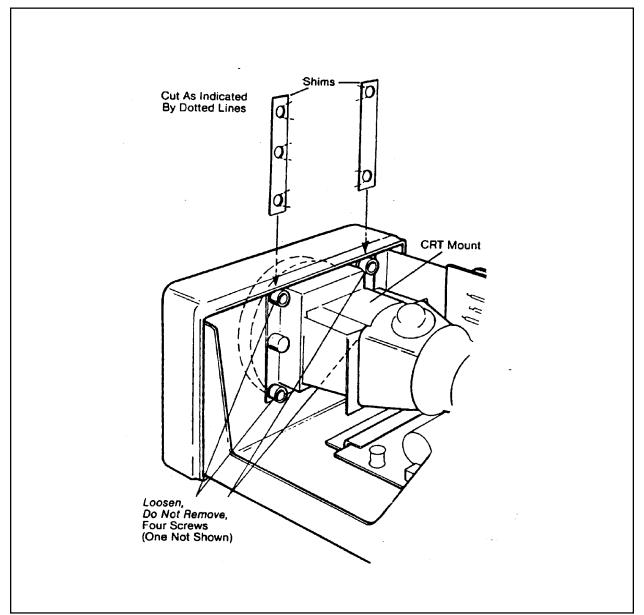

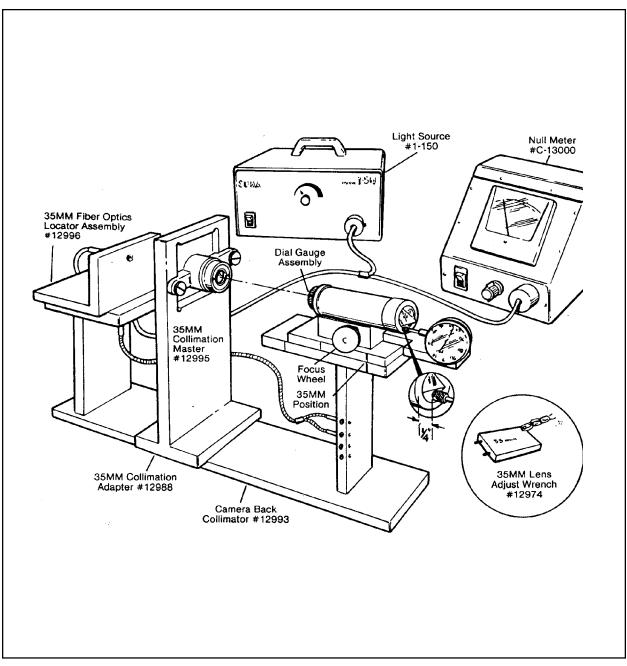

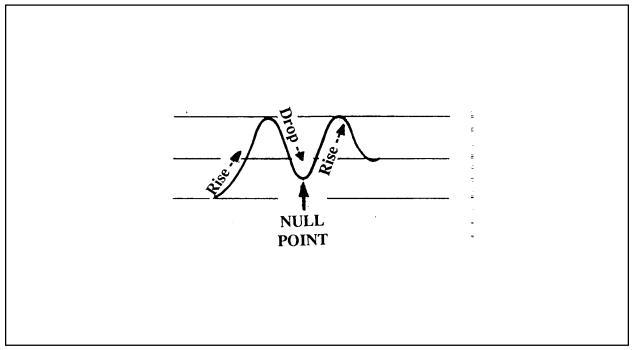

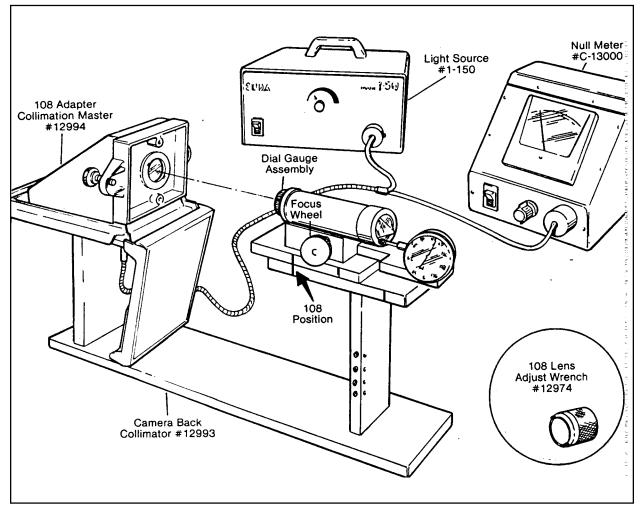

| RCTLP2      |                                                                                                                    | s the w | AL generates the necessary memory CAS signals. It rite enable signal (/VRWE) and the output enable the VRAM's.                                                                                                                                                   |