# Circuit Sizing w/ Corner Models Challenges & Applications

Matthias Sylvester April 11th, 2013

## Agenda

- Introduction

- Corners & Process Monte Carlo

- Application: Performance Tuning

- Application: Customer Cases

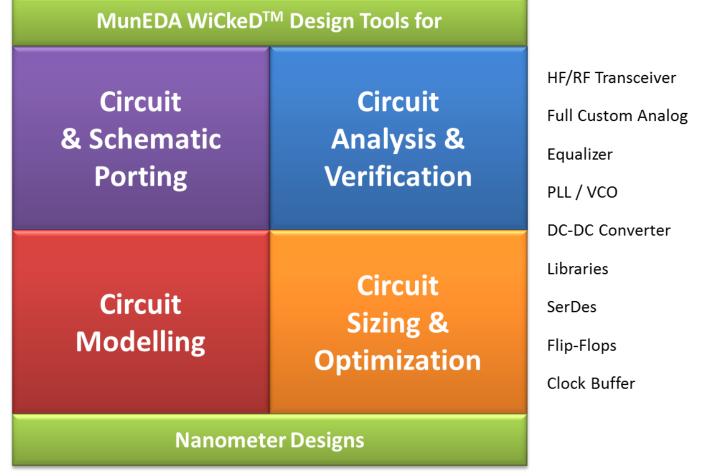

#### MunEDA Corporate Overview

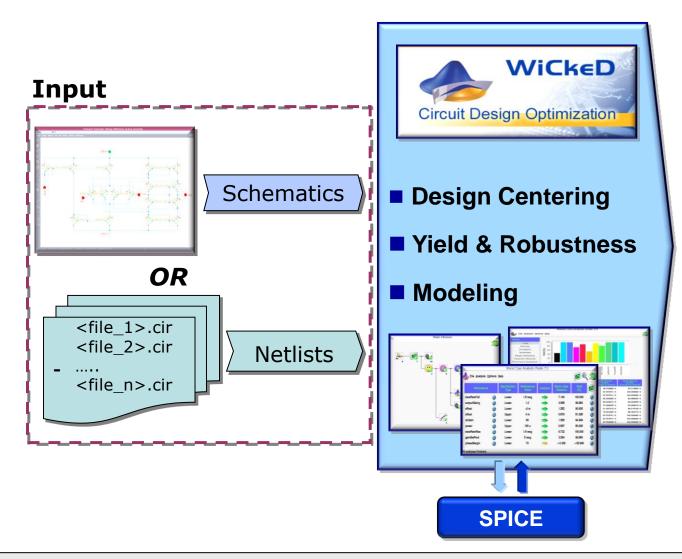

- **7** EDA Software Vendor Design Tool Suite WiCkeD™ for Porting, Analysis, Modeling & Sizing of nanometer IC designs

- Founded in 2001 Headquarters in Munich Germany

- Worldwide Sales & Support Offices in USA, Korea, Taiwan, Japan, UK, Ireland, Scandinavia, South America

- Worldwide Customer Base of Semiconductor IDMs, Fabless Design Houses & Foundries

MunEDA Corporate Headquarter in Munich, Germany

MunEDA Inc. (US Office) in Sunnyvale, CA, USA

## MunEDA WiCkeD™ Circuit Design & Sizing Environment

High Speed I/O

Standard Cell

Memory Interface

Full Custom Digital

SRAM, DRAM, Flash

FPGA Core

High-Performance IC

Mixed-Signal

Low-Power Analog

## Challenges of advanced node design

- **↗** Circuit sizing: Designers have to carefully set circuit parameters like W, L, R, C, ...

- to meet performance targets

- to reduce sensitivities vs. Vdd, temperature, process, LDE, mismatch

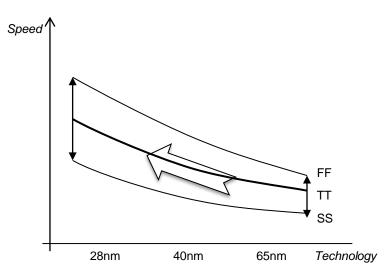

# Creating a robust design becomes more challenging in advanced nodes

- higher sensitivity vs. supply voltage

- higher sensitivity vs. temperature

- reduced voltage headroom

- wider corner spread

- increased local variation

- layout dependent effects (LDE)

See Beacham et al. (Synopsys Inc.): "Mixed-Signal IP Design Challenges in 28 nm and Beyond". www.design-reuse.com

## Process corner support

- Process variation is usually modeled in two ways

- 1. Process corners (ss/ff/sf/fs/ ...)

- 2. Process Monte Carlo vth ~  $N(\mu_{vth}, \sigma^2_{vth})$ tox ~  $N(\mu_{tox}, \sigma^2_{tox})$

. . .

Most foundry PDKs contain both models.

Local variation (mismatch) is always modeled by MC statistics.

What's the advantages / disadvantages of using corners or process MC?

## Corners & Process Monte Carlo

## Comparison: Corners vs Process Monte Carlo

|                                                                             | Corners | Process MC |

|-----------------------------------------------------------------------------|---------|------------|

| Simulation effort for pure CMOS                                             | low     | medium     |

| Simulation effort for large # of device types (MOS/BJT/res/cap/) per design | high    | medium     |

| Check timing for full-custom digital designs                                | yes     | no         |

| Correct device correlation                                                  | no      | yes        |

| Check operating conditions of analog designs                                | yes     | yes        |

| Check analog performance variability                                        | no      | yes        |

| Estimate yield                                                              | no      | yes        |

| Process parameter sensitivities                                             | no      | yes        |

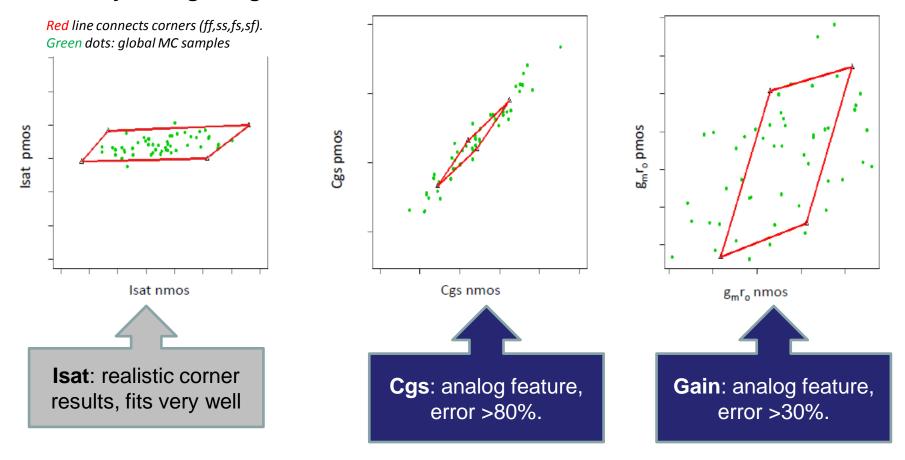

## Analog performance variability

→ Compare ss/ff/fs/sf corner results with global MC for a popular 65nm process that's used by analog designers worldwide:

→ Good estimate for Isat, Vth; difference at analog small signal parameters.

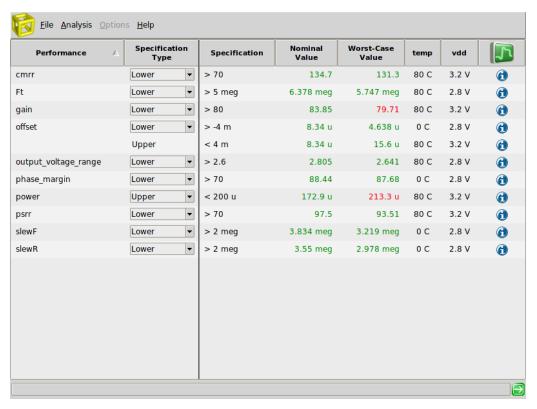

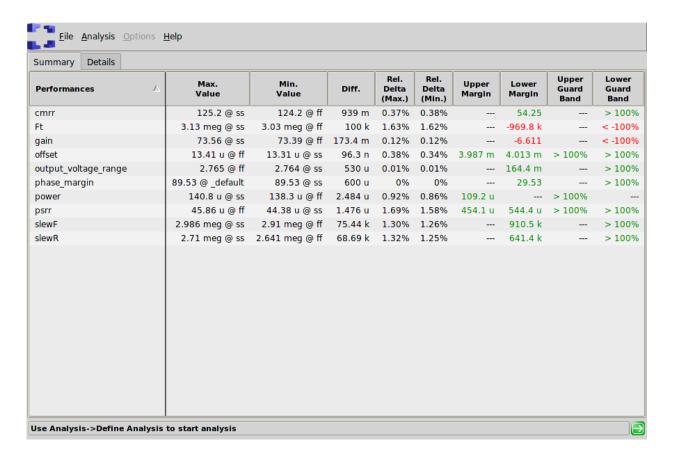

#### Tools of WiCkeD – Analysis & Verfication – WCO Worst-Case Operation

Circuit

Analysis &

Verification

- Find worst-case operating condition & corner

- Includes structural constraints

- Can handle non-linear dependency (=worst-case not in the corner)

#### Tools of WiCkeD- Analysis & Verification — CRN Corner Run Analysis

Circuit

Analysis &

Verification

- Check all corners, show corner overview and summary

- 7 Distributed simulation in a network of hosts

## Finding worst-case conditions

If you simulated all but one corner, is there a reliable way to guess its value?

Unfortunately, no.

No matter what kind of model you use and no matter how many parameters there are, extrapolating models over a large distance is unreliable.

WiCkeD uses methods to build models over operating parameters to guess where's the worst-case condition before simulating it.

This is very useful to speed up optimization inside the optimizer's loop.

But for verification, better don't skip corners just because they are OK in a model.

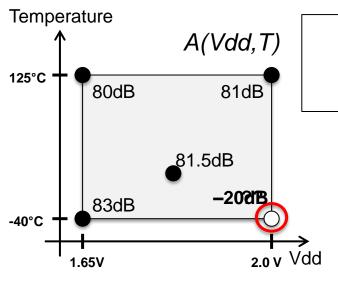

## WiCkeD WCO modeling

For continuous operating parameters:

- Star + Box DOE

- Quadratic model to detect non-linearities, resimulating estimated minima

- Checking corners

For larger # of operating parameters:

Option to run only Star DOE, create quadratic model and re-simulate

For enumerated corners:

• Full run, no short-cuts

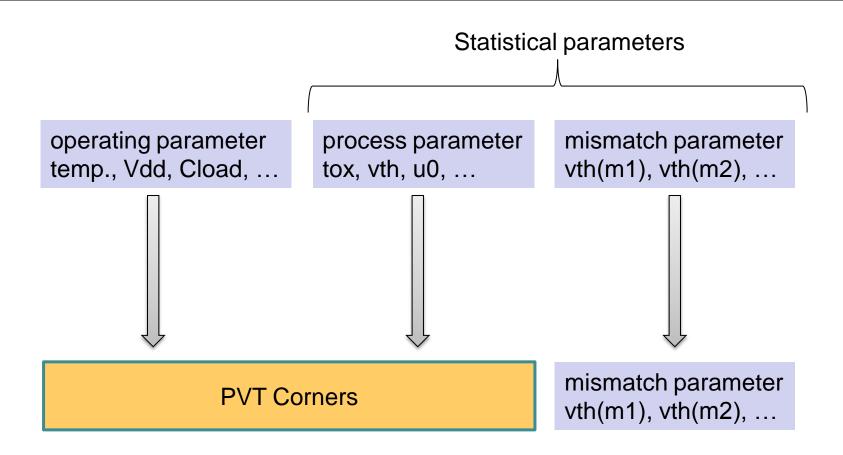

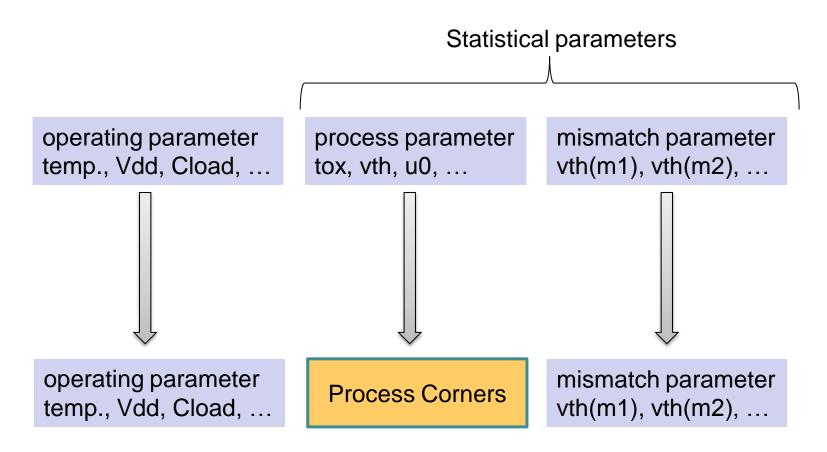

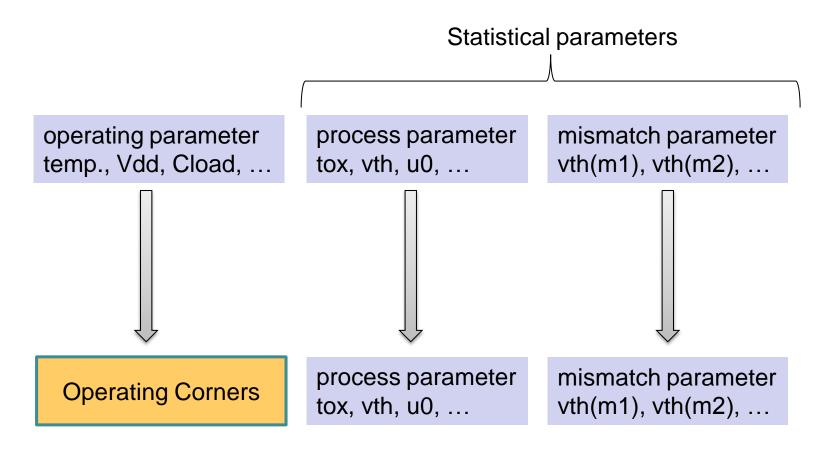

#### PVT corners and parameters (1)

- Most usual case: instead of operating parameters and process parameters, corners are defined.

- But there are alternatives ...

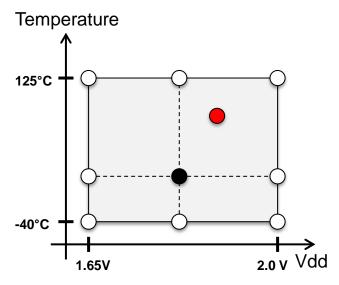

## PVT corners and parameters (2)

- WCO can handle continuous operating parameter together with corners

- Allows temperature sweeps at corners

## PVT corners and parameters (3)

- MCA can vary process parameters also if there are corners defined

- Enables running process MC for selected corner conditions

# Performance Tuning

## **Performance Tuning**

- Many circuits require precise tuning of fast transient signals, noise, transfer characteristics, ...

- Designers have to find good values for all transistors' W and L that fulfill all specs considering

- Operating conditions

- Process variation (global Monte Carlo statistics, or corners)

- Mismatch (on-chip variation)

- Designers re-size the circuit whenever

- specs get updated

- model files get updated

- multiple versions are to be generated (low-leakage, high-speed, ...)

- IP is ported to a new process (IP reuse, design migration)

- → Designers spend much time with iterative simulation-based sizing.

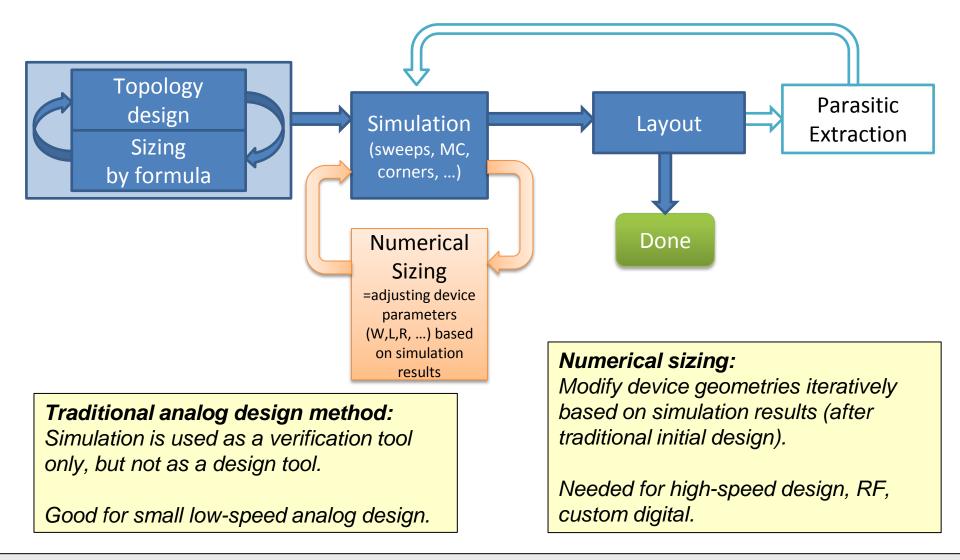

## Numerical Sizing in Advanced Circuit Design

Circuit

Sizing &

Optimization

#### Manual sizing is easy, as long as

- symbolic small-signal approximations are sufficiently accurate

- there are no tough trade-offs between multiple hard specs

- process variation and mismatch can be compensated by safety margins and structural solutions (feedback, symmetry, trimming, ...)

- there are only few design variables, best case with a 1:1 relationship to specs

#### Reality is not as easy as an analog textbook example ...

- Large impact of second order effects, parasitics, noise, ...

- Non-linear specs with no good symbolic estimate

- Impact of PVT variation and mismatch to be compensated by sizing

- Tight specs, multiple trade-offs

- Many design variables, m:n dependency to specs

#### **7** Trade-offs:

The optimum of one spec violates another spec

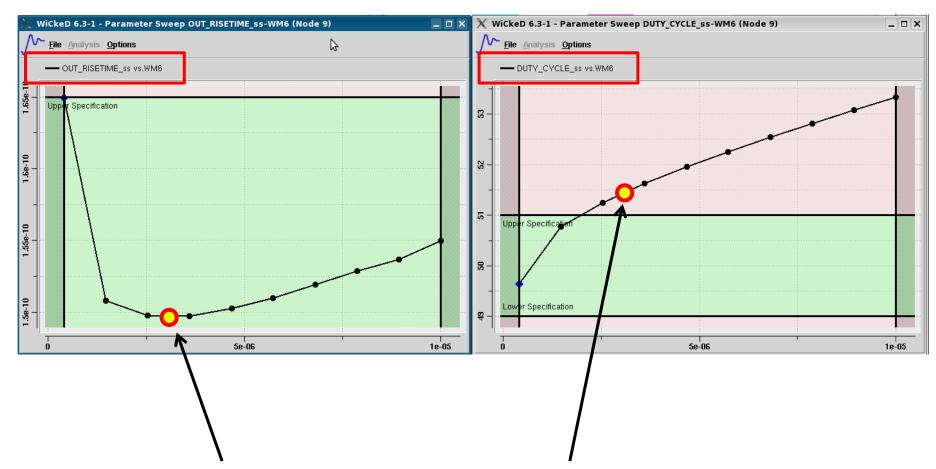

#### Non-linear parameter dependency with mixed effects

The optimum of one parameter depends on the value of other parameters

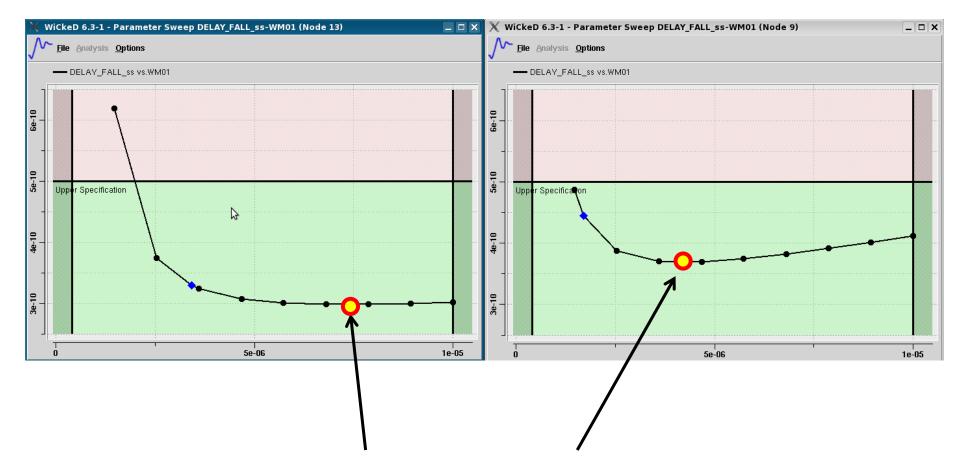

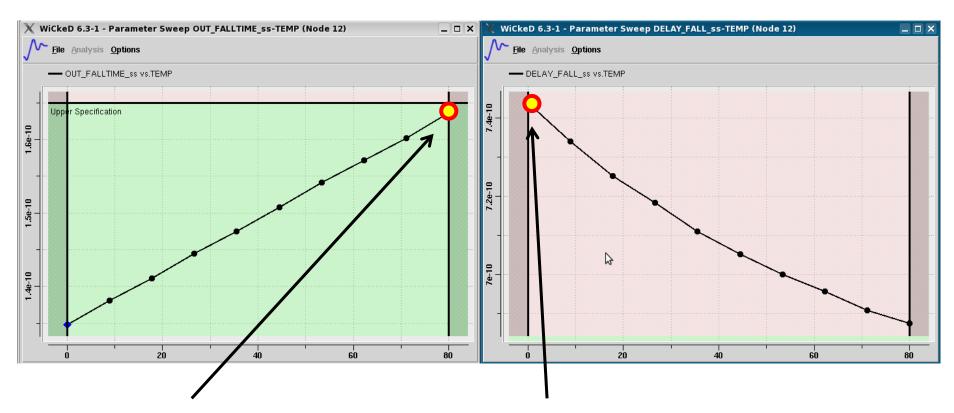

#### Different worst-cases regarding temperature / Vdd / load / ...

falltime worst-case: 80°C, delay\_fall worst-case: 0°C

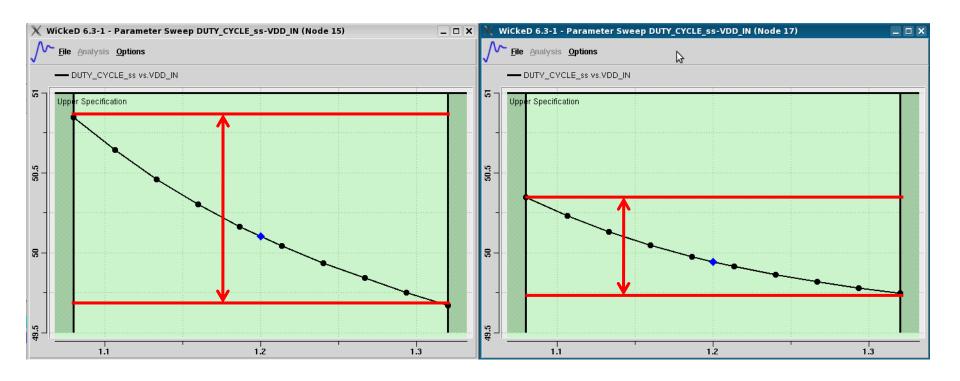

#### Sensitivities have to be minimized.

For some specs, it's not enough to shift the nominal value; you can reduce sensitivities, too.

7 Local variation (mismatch) has a significant influence

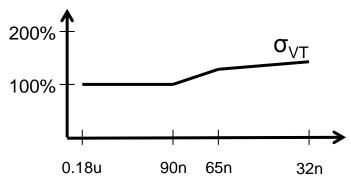

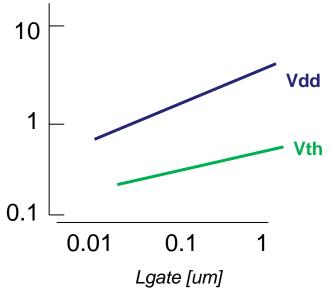

#### Scaling trend

- Absolute Vth variation of the minimum device grows

- Vth shrinks, Vdd shrinks faster

- $\Rightarrow$  Relative impact of local variation  $\sigma_{VT}$  / ( $V_{dd}$ - $V_{th}$ ) grows

- ⇒ We have to size the circuits for robustness vs. local variation in addition to PVT corners

## Typical WiCkeD Applications in I/O designs and Libraries

**Common tasks:** sizing, statistical analysis, performance optimization, modeling, robustness optimization, reduce area, reduce power consumption, initial design (low voltage), ...

#### **↗** Libraries, I/O

- Circuits: Transmitter, PCIe equalizer, LVDS drivers, level shifter, bandgap, voltage regulators, impedance control, short/overload detector, power-on-reset, SerDes, ...

- Performance metrics: jitter, eye diagram opening, duty cycle, temperature stability, voltage levels, delays, PSRR, stability, ...

#### Software: Data flow

#### **Output**

Sized & Optimized Circuit Schematic or Netlist(s)

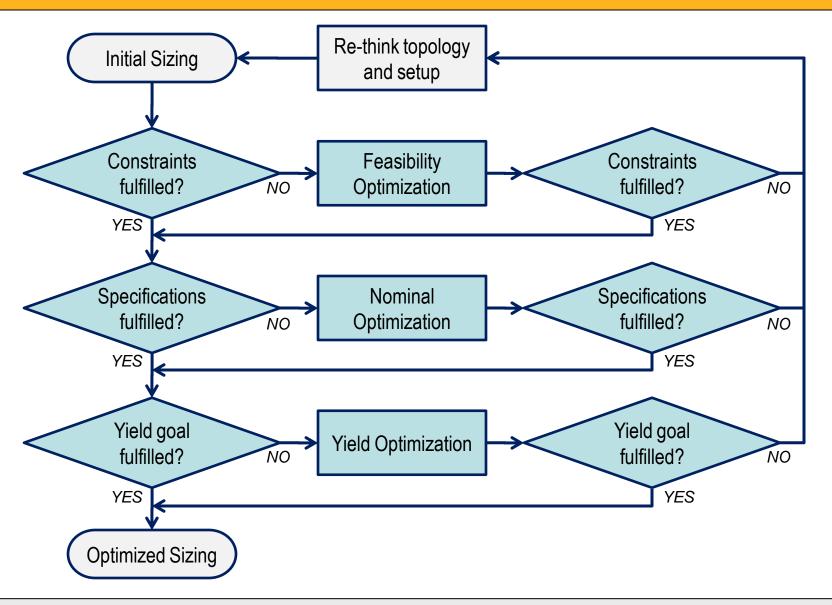

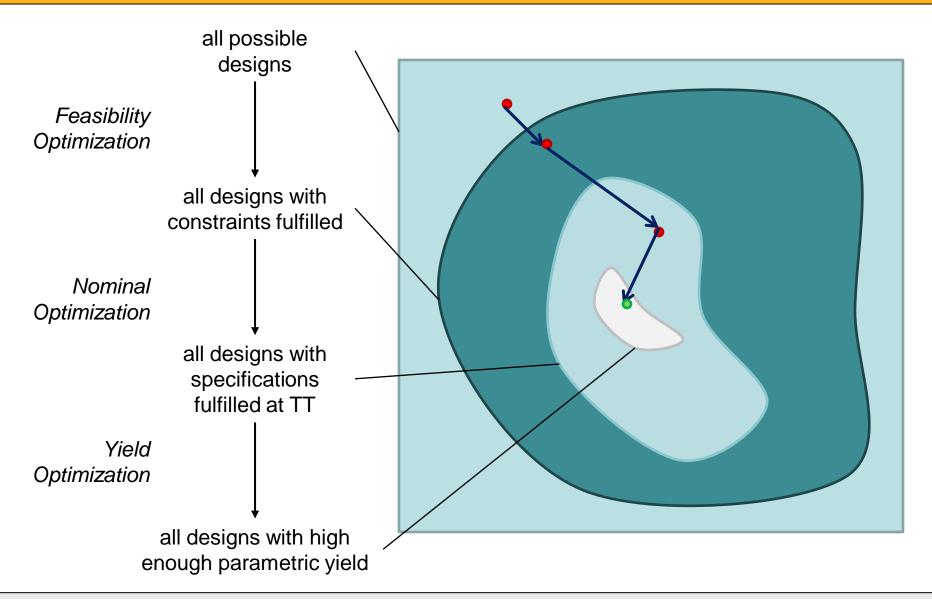

## Three Optimization Steps

#### 1. Feasibility Optimization

- Fulfills constraints on DC operating conditions (saturation, inversion, current symmetries, overdrive, ...)

- Is optional (some circuits don't have such constraints)

- May include constraints on SOA (aging), becoming more important in <28nm</li>

#### 2. Nominal Optimization

- Optimizes performance (delays, eye diagram, jitter, power ...) over PVT corners

- Keeps constraints on DC operating conditions fulfilled

- Not considering local variation (mismatch), therefore "nominal" optimization

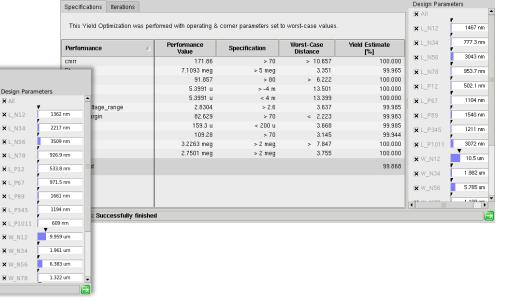

#### 3. Yield Optimization

- Optimizes design yield (robustness) considering local variation (mismatch)

- Should start from a design point after nominal optimization to save time

## Optimization Steps (Vastly Simplified Flow Chart)

#### **Solution Search**

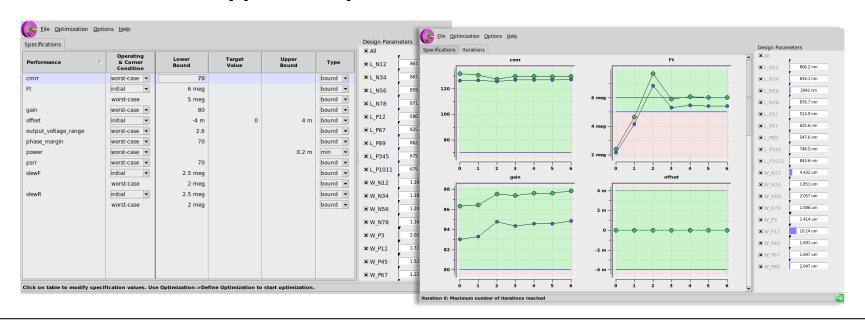

#### Tools of WiCkeD – Sizing & Optimization— DNO & GNO Nominal Optimization

Circuit

Sizing &

Optimization

- **▶** Fast and efficient. Scales well also for larger circuits.

- Multiple parameters, goals, corners & test benches optimized simultaneously

- Pre- and post-layout

- Broad simulator support, scriptable.

Tools of WiCkeD – Sizing & Optimization — Design Centering (Yield Optimization)

X | N12

**X** L\_N56

X | N78

X L P67

X L P89

Circuit Sizing & **Optimization**

## The unique flagship: **Automated Yield Optimization**

Eile Optimization Options Help

- Improve robustness vs process variation and mismatch

- Multiple performances simultaneously

Based on worst-case distance and sigma measures

Yield [%]

File Optimization Options Help

Specifications Iteration

60 -

40 -

Iteration 6: Successfully finished

## **Customer Cases**

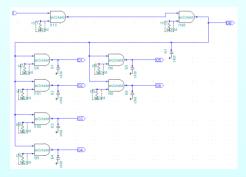

#### Customer Example – Faraday – Batch-mode optimization of standard cells

#### Standard cell: Clock buffers

- **▼** Task: Balance slopes

- Challenge: many cell & process variants, multiple slews and output loads, frequent model update

#### Solution:

# MunEDA Nominal Optimization in Batch Mode

|      | PTNT (%)          |                   |                   |                   | PFNF (%)          |                   |                   | PSNS (%)          |                   |                   |                   |                   |

|------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

|      | 0.00<br>1500<br>P | 0.00<br>7287<br>P | 0.01<br>6060<br>P | 0.03<br>5400<br>P | 0.00<br>1500<br>P | 0.00<br>7287<br>P | 0.01<br>6060<br>P | 0.03<br>5400<br>P | 0.00<br>1500<br>P | 0.00<br>7287<br>P | 0.01<br>6060<br>P | 0.03<br>5400<br>P |

| BAL1 | 2                 | 1.5               | 1                 | ~ 1               | 3.3               | 3.3               | 3.2               | 3.3               | 2.8               | 2.9               | 3.1               | 3.5               |

| BAL2 | 1.8               | 1.4               | ~1                | ~1                | 3.2               | 3.1               | 3.1               | 3.1               | 2.9               | 3.0               | 3.2               | 3.6               |

| BAL3 | 1.5               | 1                 | ~1                | ~1                | 2.9               | 2.9               | 2.9               | 2.9               | 3.0               | 3.1               | 3.3               | 3.7               |

| BAL4 | ~1                | ~1                | ~1                | ~1                | 2.3               | 2.3               | 2.3               | 2.5               | 3.2               | 3.4               | 3.5               | 3.8               |

| BAL5 | ~1                | 3.8               | 1.5               | 1.9               | 1.1               | 1.1               | 1.2               | 1.5               | 3.7               | 3.9               | 3.9               | 4.1               |

| BAL6 | 3.7               | 1.1               | 3.9               | 4.1               | ~1                | ~1                | ~1                | ~1                | 5.1               | 5.2               | 5.2               | 5.3               |

Complete automation reduces design time significantly.

Equal or better results than manual design.

Analog IP Migration & Design

Synthesis Platform with WiCkeD

David Wu, Faraday Technology Corp.

Kun-Cheng Wu, Faraday Technology Corp.

Michael Prodath, MunEDA GmbH

June 13, 2008

MunEDA FARADA

Results published by Faraday at MTF Anaheim 2008

Sizing & Optimization

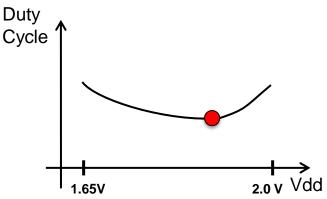

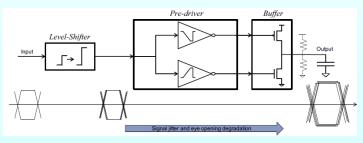

Customer Example – Sizing & Design Centering with MunEDA WiCkeD Optimization Tools STMicroelectronics - Optimization of High-Speed I/O circuits in 28nm

- Task: Reduce jitter and duty cycle

- Challenge: Manual tuning takes 2 weeks

#### Solution:

Use MunEDA **Sensitivity Analysis** and **Corner Optimization**

477

Sizing & Optimization

Design Time reduced from 2 weeks to only 3 hours

Corner spread reduced by 50%

Easy analysis of circuit sensitivities

Results published by STMicroelectronics at MUGM 2011

Optimization of a 2.133GHz level shifter in 28nm (with WiCkeD)

Nicolas Seller - STMicroelectronics (Crolles)

November, 25th 2011

STMicroelectronics

# Customer Example – Sizing & Design Centering with MunEDA WiCkeD Optimization Tools TOP Microprocessor Company - Using MunEDA tools to optimize AMS/RF IP in 65nm

Circuit Sizing & Optimization

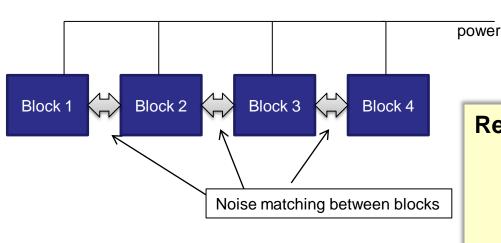

#### TOP Microprocessor Company - RF receiver path in advanced node

- Task: reduce power consumption while keeping noise low

- To see the noise vs power trade-off, the complete path has to be considered

- Circuit size: ~2000 MOS, ~8000 parasitics.

Simulation time: 40min. for a single run (dc+pss+pnoise)

- Optimization complexity: 80 specs, 50 design parameters

Three process corners + temperature + Vdd

#### Results:

- Power consumption significantly reduced.

- Sizing task performed completely automatically.

- Designer attention time is reduced from 4 weeks to a few hours.