#### Topics:

- 1. Intro

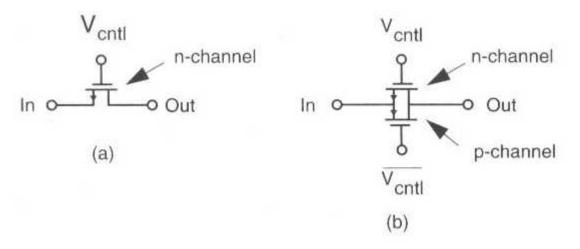

- 2. Transmission Gate Logic Design

- 3. X-Gate 2-to-1 MUX

- 4. X-Gate XOR

- 5. X-Gate 8-to-1 MUX

- 6. X-Gate Logic Latch

- 7. Voltage Drop of n-CH X-Gates

- 8. n-CH Pass Transistors vs. CMOS X-Gates

- 9. n-CH Pass Transistors vs. CMOS X-Gates

- 10. Full Swing n-CH X-Gate Logic

- 11. Leakage Currents

- 12. Static CMOS Digital Latches

- 13. Static CMOS Digital Latches

- 14. Static CMOS Digital Latches

- 15. Static CMOS Digital Latches

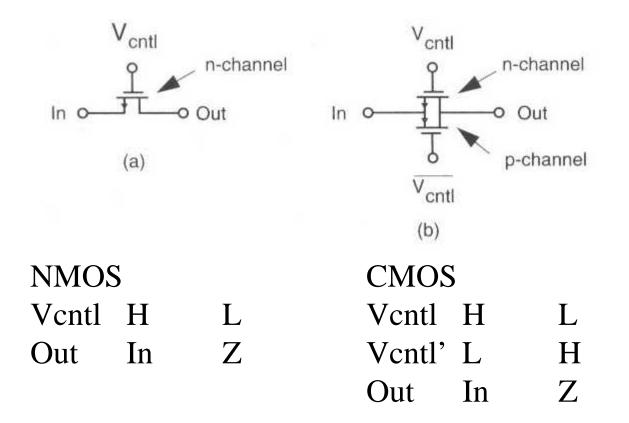

Transmission Gates (Martin, c5.1)

Pass Transistors, a.k.a., Transmission Gates are same as a relayWhy? Usually allows for a reduction in number of transistors

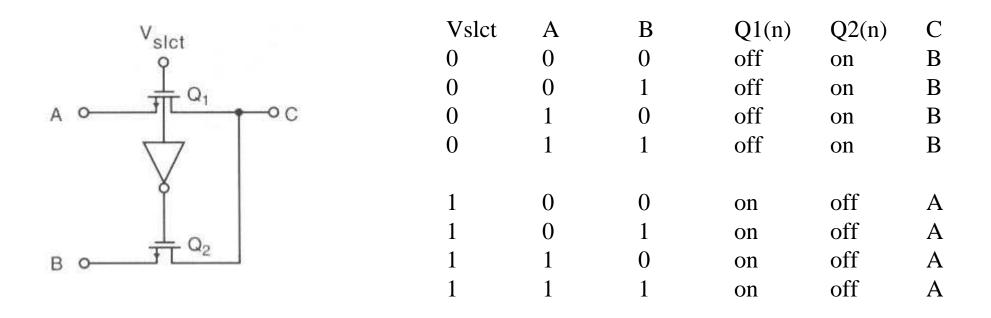

#### Transmission Gate 2-to-1 MUX (Martin, c5.1)

#### This same design will be revisited shortly for an 8-to-1 MUX

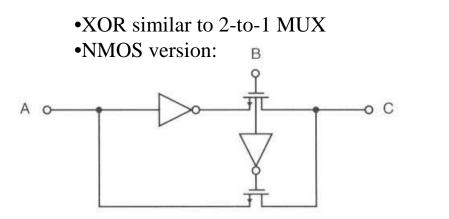

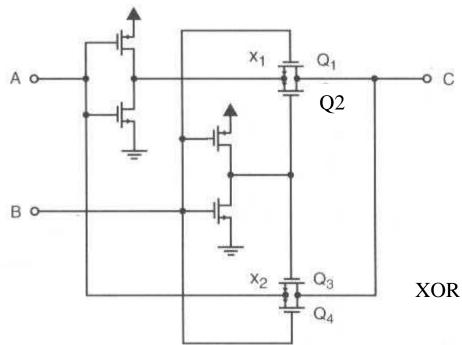

Transmission Gate XOR (Martin, c5.1)

| В | А | Q1(n) | Q2(n) | С      |

|---|---|-------|-------|--------|

| 0 | 0 | off   | on    | 0 (A)  |

| 0 | 1 | off   | on    | 1 (A)  |

|   |   |       |       |        |

| 1 | 0 | on    | off   | 1 (A') |

| 1 | 1 | on    | off   | 0 (A') |

•CMOS version:

Table 5.1 The Truth Table of the exclusive-or Function

| А              | В                          |                | С                   |

|----------------|----------------------------|----------------|---------------------|

| 0              | 0                          |                | 0                   |

| 0              | 1                          |                | 1                   |

| 1              | 0                          |                | 1                   |

| 1              | 1                          |                | 0                   |

| NMOS<br>X-Gate | pseudo-NMOS<br>traditional | CMOS<br>X-Gate | CMOS<br>traditional |

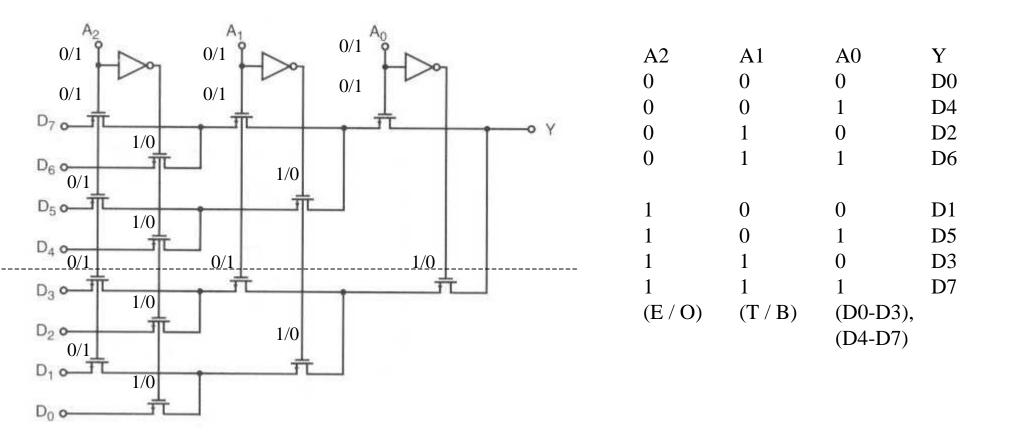

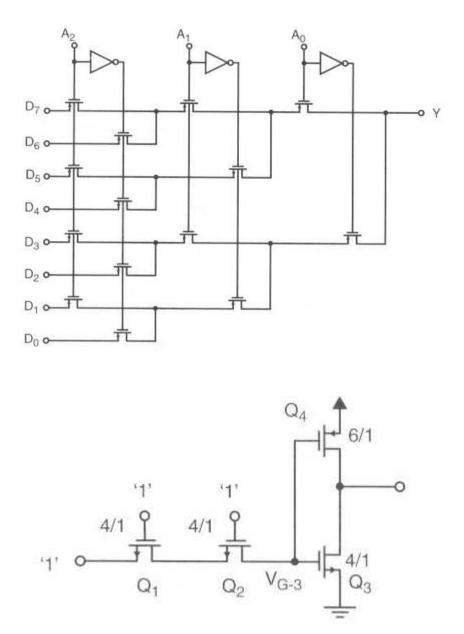

Transmission Gate 8-to-1 MUX (Martin, c5.1)

Typically, one would not use more than 8-to-1 MUX. Why?

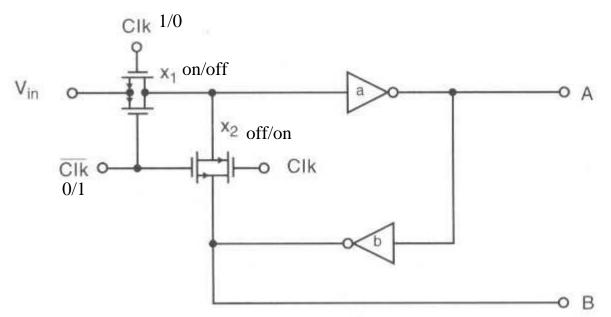

Transmission Gate Clocked Latch (Martin, c5.1)

Figure 5.6 A transmission-gate-based clocked latch.

data is latched to Vin at time of clock transition

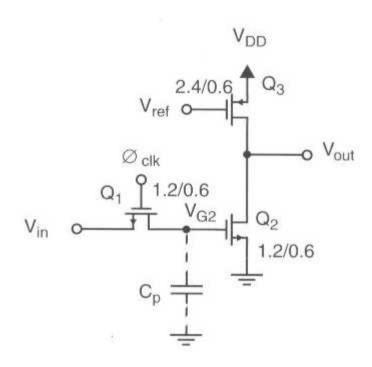

Voltage Drop of n-CH X-Gates (Martin, c5.1)

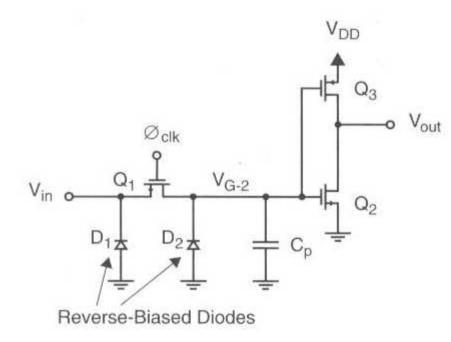

Pseudo-NMOS X-Gate delay line cell

Desired operation:

•Start with  $\phi_{clk} = 1$ ,  $V_{G2} = V_{in}$

- •Transition,  $\phi_{clk}$  1->0, Q1 on->off, Cp keeps voltage

- •AKA source follower or common drain buffer

- •Cp is due to what?

•Vout = Vin'

Problems with circuit:

•Start with Vin=0, and  $\phi_{clk}$  0->1

• $V_{G2} = V_{in} = 0V$ , so Q1 S/D are at ground (Q1 is in what region?)

•If Vin -> VDD, while  $\phi_{clk} = 1$ , initially LHS of Q1 is drain

RHS is the source, and Vgs=VDD, and Vgd=0

(Q1 is in what region?)

$\bullet V_{G2}$  charges up to VDD-Vtn

•Veff for Q1 will become zero (Vgs-Vtn=0)

•Q1 shuts off when Vgs=Vtn, or when  $V_{G2} = VDD$ -Vtn

•Thus V<sub>G2</sub> never gets to VDD, and body effect determines how far from VDD the node ends up

•As body effect goes up, Vtn goes up,  $V_{G2}$  goes down

•So what is the problem?

Voltage Drop of n-CH X-Gates (Martin, c5.1)

Through how many series transistors does the data pass?

•Equivalency says that two series transistors with W/L is the same as one transistor with W/2L

•Voltage at gate of Q3 is the same, it just takes longer to rise

=>

#### n-CH vs. CMOS X-Gates (Martin, c5.1)

- •Area may be smaller if NMOS used vs. CMOS

- •CMOS X-Gates transfer "1" and "0" efficiently. Why?

- •CMOS X-Gates after faster in 0->1 transition. Why?

- •N-CH voltage drop a major disadvantage, but can be eliminated

Speed:

- •When junction capacitance dominates, which should be used?

- •When load capacitance dominates, which should be used? Power:

- •Which is more sensitive to Vt value?

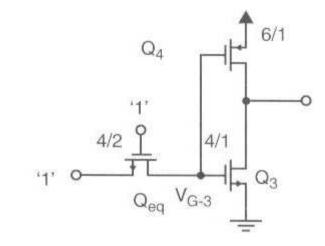

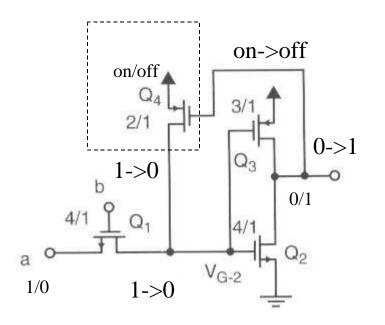

Full-Swing n-CH X-Gates (Martin, c5.1)

•Applicable when an inverter follows a pass transistor

•Q4 must have W/L small compared to Q1 for 1->0 at Q2 gate. Why?

•p-ch load (Q3) will be completely turned off with the addition of Q4. If not, what would occur?

Leakage Currents (Martin, c5.1)

•What happens to voltages when  $\phi_{clk}$  is high and Vin=1?

•Cp obtains what value?

- •What happens to Cp if  $\phi_{clk}$  remains low

- •How does this vary with temperature?

- •What else would cause this to vary?

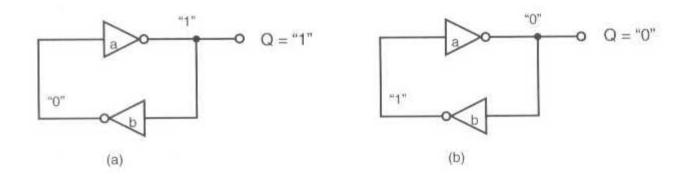

#### Static CMOS Digital Latches (Martin, c7.1)

Example of a two cross coupled inverters, having positive feedback:

Latch realized below using what type of logic?

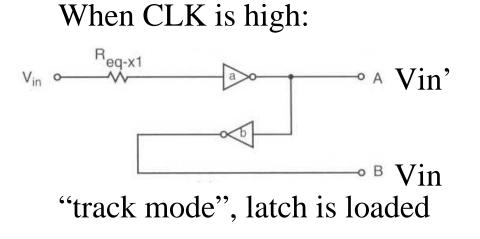

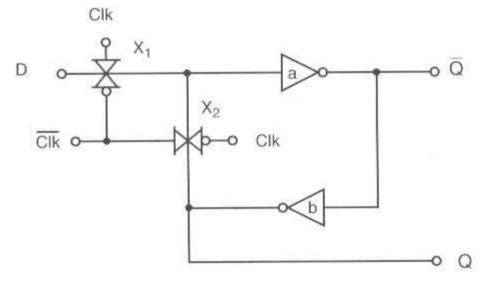

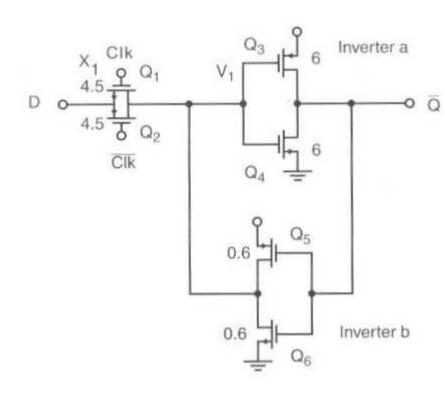

Static CMOS Digital Latches (Martin, c7.1)

•What has changed from previous slide for latch?

•When CLK is high, D is passed to V1, but why is it not inverted by Q5/Q6?

Good: hysteresis is added, noise immunity for slow-moving signals, less area than latch of previous foil

Bad: Only inverter a is a driver. Why?

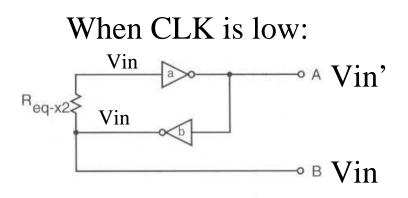

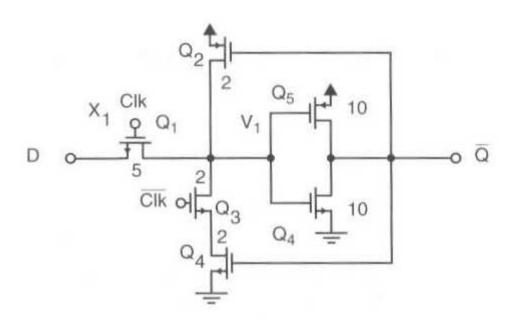

Static CMOS Digital Latches (Martin, c7.1)

•Q1 is used as a pass transistor, so why is Q2 in the circuit?

•Q2 ratio W/L should be small or large compared to Q1?

•When CLK is low, Q3 is on, reinforcing a stored "0" at V1.

•What reinforces the stored "1" at V1 when CLK is low?

Static CMOS Digital Latches (Martin, c7.1)

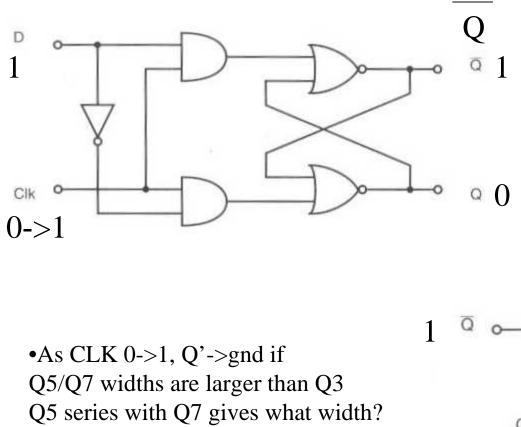

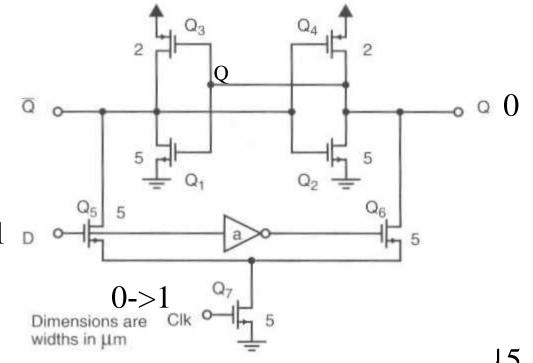

•Cross coupled NOR gates •Q=D when Clk=1 •Q preserved when Clk=0

•Compare to what width of Q3? •When Q' is low, Q4 is on, Q2 off, Q is 1 •This means one inverter delay

Joseph A. Elias, PhD