## Combinational Circuit Design

### COE 202

### **Digital Logic Design**

Dr. Muhamed Mudawar

King Fahd University of Petroleum and Minerals

### Presentation Outline

- How to Design a Combinational Circuit

- Designing a BCD to Excess-3 Code Converter

- Designing a BCD to 7-Segment Decoder

- Hierarchical Design

- Iterative Design

### **Combinational Circuit**

✤ A combinational circuit is a block of logic gates having:

*n* inputs:  $x_1, x_2, \ldots, x_n$

*m* outputs:  $f_1, f_2, \dots, f_m$

- Each output is a function of the input variables

- Each output is determined from present combination of inputs

- Combination circuit performs operation specified by logic gates

### How to Design a Combinational Circuit

#### 1. Specification

♦ Specify the inputs, outputs, and what the circuit should do

#### 2. Formulation

♦ Convert the specification into truth tables or logic expressions for outputs

#### 3. Logic Minimization

♦ Minimize the output functions using K-map or Boolean algebra

#### 4. Technology Mapping

- ♦ Draw a logic diagram using ANDs, ORs, and inverters

- ♦ Map the logic diagram into the selected technology

- ♦ Considerations: cost, delays, fan-in, fan-out

#### 5. Verification

$\diamond$  Verify the correctness of the design, either manually or using simulation

### Designing a BCD to Excess-3 Code Converter

#### 1. Specification

- ♦ Convert BCD code to Excess-3 code

- ♦ Input: BCD code for decimal digits 0 to 9

- $\diamond$  Output: Excess-3 code for digits 0 to 9

#### 2. Formulation

- $\diamond$  Done easily with a truth table

- $\diamond$  BCD input: *a*, *b*, *c*, *d*

- $\diamond$  Excess-3 output: *w*, *x*, *y*, *z*

- ♦ Output is don't care for 1010 to 1111

| BCD  |   |   | Excess-3 |   |   |   |   |

|------|---|---|----------|---|---|---|---|

| а    | b | С | d        | W | X | у | z |

| 0    | 0 | 0 | 0        | 0 | 0 | 1 | 1 |

| 0    | 0 | 0 | 1        | 0 | 1 | 0 | 0 |

| 0    | 0 | 1 | 0        | 0 | 1 | 0 | 1 |

| 0    | 0 | 1 | 1        | 0 | 1 | 1 | 0 |

| 0    | 1 | 0 | 0        | 0 | 1 | 1 | 1 |

| 0    | 1 | 0 | 1        | 1 | 0 | 0 | 0 |

| 0    | 1 | 1 | 0        | 1 | 0 | 0 | 1 |

| 0    | 1 | 1 | 1        | 1 | 0 | 1 | 0 |

| 1    | 0 | 0 | 0        | 1 | 0 | 1 | 1 |

| 1    | 0 | 0 | 1        | 1 | 1 | 0 | 0 |

| 1010 | t | 0 | 1111     | Х | Х | Х | Х |

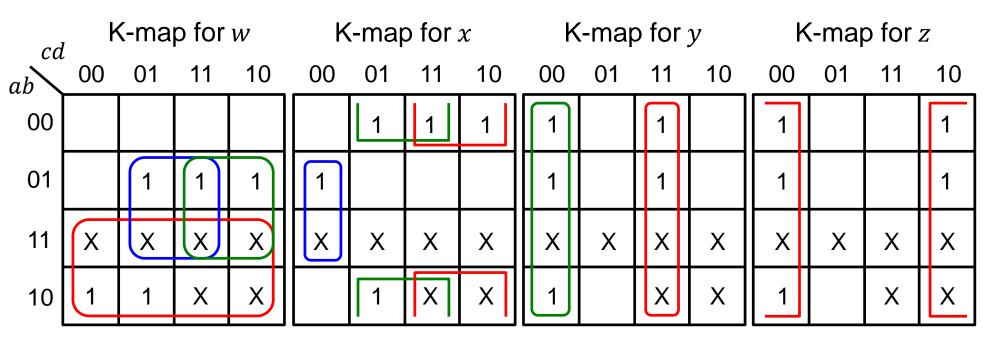

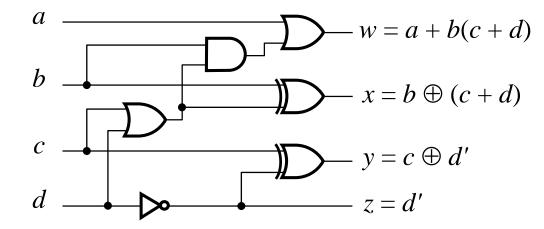

### Designing a BCD to Excess-3 Code Converter

#### **3. Logic Minimization using K-maps**

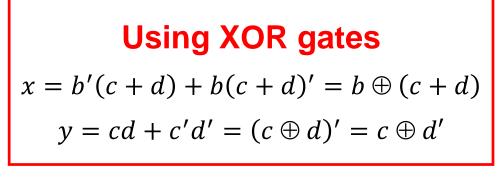

Minimal Sum-of-Product expressions:

w = a + bc + bd, x = b'c + b'd + bc'd', y = cd + c'd', z = d'

Additional 3-Level Optimizations: extract common term (c + d)

$$w = a + b(c + d)$$

,  $x = b'(c + d) + b(c + d)'$ ,  $y = cd + (c + d)'$

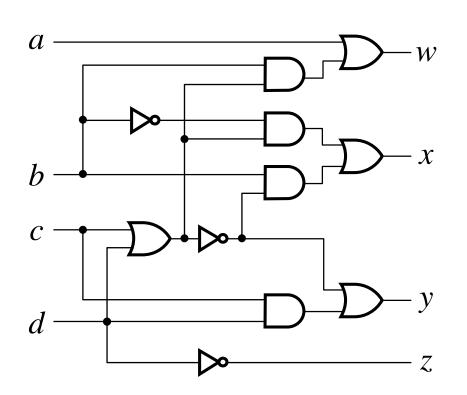

### Designing a BCD to Excess-3 Code Converter

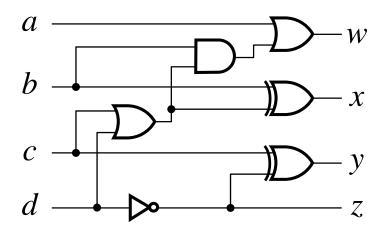

#### 4. Technology Mapping

Draw a logic diagram using ANDs, ORs, and inverters

Other gates can be used, such as NAND, NOR, and XOR

#### Combinational Circuit Design

### Designing a BCD to Excess-3 Code Converter

#### 5. Verification

Can be done manually

Extract output functions from circuit diagram Find the truth table of the circuit diagram Match it against the specification truth table Verification process can be automated Using a simulator for complex designs

#### Truth Table of the Circuit Diagram

| BCD  |     |        | Ex | Ce | es | s-3 |

|------|-----|--------|----|----|----|-----|

| abcd | c+d | b(c+d) | W  | X  | У  | z   |

| 0000 | 0   | 0      | 0  | 0  | 1  | 1   |

| 0001 | 1   | 0      | 0  | 1  | 0  | 0   |

| 0010 | 1   | 0      | 0  | 1  | 0  | 1   |

| 0011 | 1   | 0      | 0  | 1  | 1  | 0   |

| 0100 | 0   | 0      | 0  | 1  | 1  | 1   |

| 0101 | 1   | 1      | 1  | 0  | 0  | 0   |

| 0110 | 1   | 1      | 1  | 0  | 0  | 1   |

| 0111 | 1   | 1      | 1  | 0  | 1  | 0   |

| 1000 | 0   | 0      | 1  | 0  | 1  | 1   |

| 1001 | 1   | 0      | 1  | 1  | 0  | 0   |

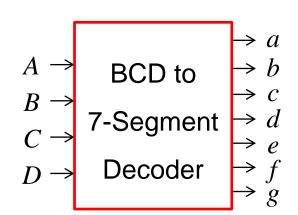

### BCD to 7-Segment Decoder

- Seven-Segment Display:

- ♦ Made of Seven segments: light-emitting diodes (LED)

- $\diamond$  Found in electronic devices: such as clocks, calculators, etc.

- ✤ BCD to 7-Segment Decoder

- ♦ Accepts as input a BCD decimal digit (0 to 9)

- $\diamond\,$  Generates output to the seven LED segments to display the BCD digit

- $\diamond$  Each segment can be turned on or off separately

### Designing a BCD to 7-Segment Decoder

#### 1. Specification:

- $\diamond$  Input: 4-bit BCD (A, B, C, D)

- $\diamond$  Output: 7-bit (*a*, *b*, *c*, *d*, *e*, *f*, *g*)

- Display should be OFF for

Non-BCD input codes

#### 2. Formulation

- $\diamond$  Done with a truth table

- $\diamond$  Output is zero for 1010 to 1111

# $\begin{array}{c} a \\ f & b \\ e & g \\ d \end{array}$

#### **Truth Table**

| <b>BCD</b> input | 7-Segment decoder |

|------------------|-------------------|

| ABCD             | abcdefg           |

| 0000             | 1 1 1 1 1 1 0     |

| 0001             | 0110000           |

| 0010             | 1 1 0 1 1 0 1     |

| 0011             | 1 1 1 1 0 0 1     |

| 0100             | 0110011           |

| 0101             | 1011011           |

| 0110             | 1011111           |

| 0111             | 1110000           |

| 1000             | 1 1 1 1 1 1 1     |

| 1001             | 1 1 1 1 0 1 1     |

| 1010 to 1111     | 0000000           |

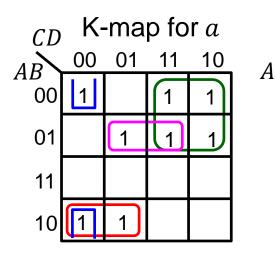

### Designing a BCD to 7-Segment Decoder

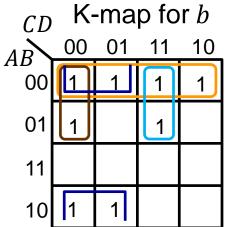

#### 3. Logic Minimization Using K-Maps

$\begin{array}{c|c} CD & \text{K-map for } c \\ AB & 00 & 01 & 11 & 10 \\ 00 & 1 & 1 & 1 & 1 \\ 01 & 1 & 1 & 1 & 1 \\ 01 & 1 & 1 & 1 & 1 \\ 11 & 1 & 1 & 1 \\ 10 & 1 & 1 & 1 \end{array}$

a = A'C + A'BD + AB'C' + B'C'D' b = A'B' + B'C' + A'C'D' + A'CD c = A'B + B'C' + A'DExtracting common terms

Let

$$T_1 = A'B$$

,  $T_2 = B'C'$ ,  $T_3 = A'D$

Optimized Logic Expressions  $a = A'C + T_1 D + T_2 A + T_2 D'$   $b = A'B' + T_2 + A'C'D' + T_3C$   $c = T_1 + T_2 + T_3$  $T_1, T_2, T_3$  are shared gates

#### 3. Logic Minimization Using K-Maps

### Designing a BCD to 7-Segment Decoder

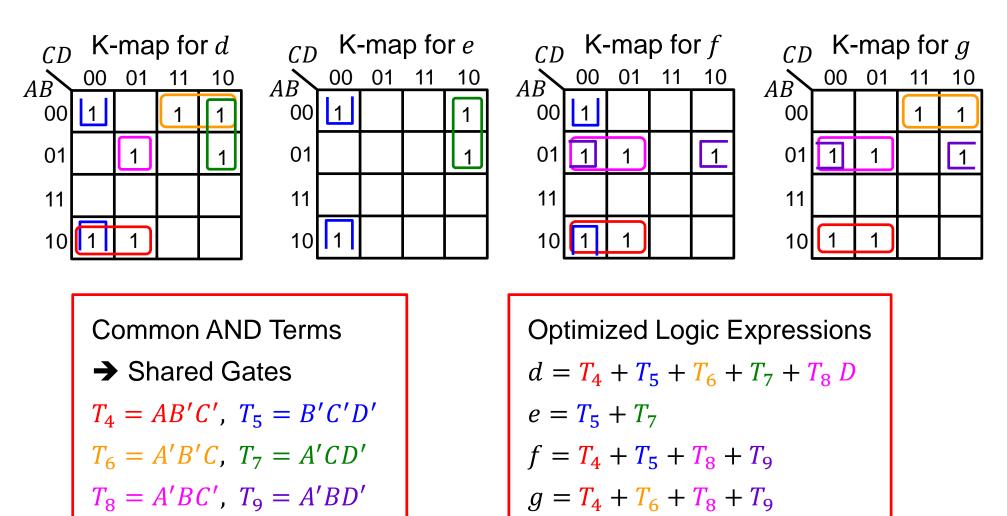

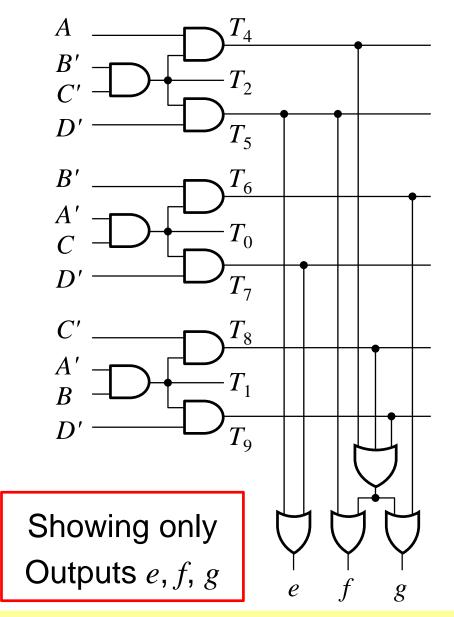

#### 4. Technology Mapping

Many Common AND terms:  $T_0$  thru  $T_9$  $T_0 = A'C, T_1 = A'B, T_2 = B'C'$  $T_3 = A'D, T_4 = AB'C', T_5 = B'C'D'$  $T_6 = A'B'C$ ,  $T_7 = A'CD'$  $T_8 = A'BC', T_9 = A'BD'$ **Optimized Logic Expressions**  $a = T_0 + T_1 D + T_4 + T_5$  $b = A'B' + T_2 + A'C'D' + T_3C$  $c = T_1 + T_2 + T_3$  $d = T_4 + T_5 + T_6 + T_7 + T_8 D$  $e = T_{5} + T_{7}$  $f = T_4 + T_5 + T_8 + T_9$  $g = T_4 + T_6 + T_8 + T_9$

### Verification Methods

- Manual Logic Analysis

- ♦ Find the logic expressions and truth table of the final circuit

- ♦ Compare the final circuit truth table against the specified truth table

- ♦ Compare the circuit output expressions against the specified expressions

- ♦ Tedious for large designs + Human Errors

#### Simulation

- ♦ Simulate the final circuit, possibly written in HDL (such as Verilog)

- ♦ Write a test bench that automates the verification process

- ♦ Generate test cases for ALL possible inputs (exhaustive testing)

- ♦ Verify the output correctness for ALL input test cases

- ♦ Exhaustive testing can be very time consuming for many inputs

### Modeling the 7-Segment Decoder

```

// Module BCD_to_7Segment: Modeled using continuous assignment

module BCD_to_7Segment (input A,B,C,D, output a,b,c,d,e,f,g);

wire T0, T1, T2, T3, T4, T5, T6, T7, T8, T9;

assign TO=~A&C; assign T1=~A&B; assign T2=~B&~C;

assign T3=~A&D; assign T4=T2&A; assign T5=T2&~D;

assign T6=T0&~B; assign T7=T0&~D; assign T8=T1&~C;

assign T9=T1&~D;

assign a = T0 | T1&D | T4 | T5;

assign b = -A\&-B \mid T2 \mid -A\&-C\&-D \mid T3\&C;

assign c = T1 | T2 | T3;

assign d = T4 | T5 | T6 | T7 | T8&D;

assign e = T5 | T7;

assign statements can

assign f = T4 | T5 | T8 | T9;

assign g = T4 | T6 | T8 | T9;

appear in any order

endmodule

```

### Testing the BCD to 7-Segment Decoder

module Test\_BCD\_to\_7Segment; // No need for Ports **reg** A, B, C, D; // variable inputs wire a, b, c, d, e, f, g; // wire outputs // Instantiate the module to be tested BCD to 7Segment BCD 7Seg (A, B, C, D, a, b, c, d, e, f, g); // initial block initial begin A=0; B=0; C=0; D=0; // at t=0 **#200** \$finish; // at t=200 finish simulation // end of initial block end always #10 D=~D; // invert D every 10 time units // invert C every 20 time units always #20 C=~C; always #40 B=~B; // invert B every 40 time units always **#80** A=~A; // invert A every 80 time units

endmodule

### The initial and always Blocks

- There are two types of procedural blocks in Verilog

- 1. The **initial** block

- ♦ Executes the enclosed statement(s) once

- 2. The always block

- ♦ Executes the enclosed statement(s) repeatedly until simulation terminates

- The body of the initial and always blocks is procedural

- ♦ Can enclose one or more procedural statements

- Procedural statements surrounded by begin ... end execute sequentially

- #delay is used to delay the execution of the procedural statement

- Procedural blocks can appear in any order inside a module

- Multiple procedural blocks run in parallel inside the simulator

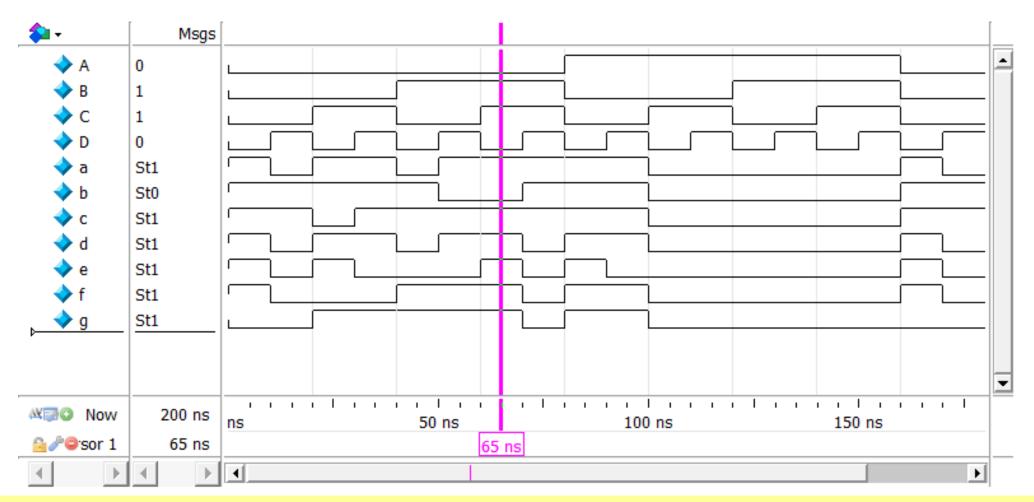

### Simulator Waveforms

All sixteen input test cases of A, B, C, D are generated between t=0 and t=160 ns. Verify that outputs a to g match the truth table.

Combinational Circuit Design

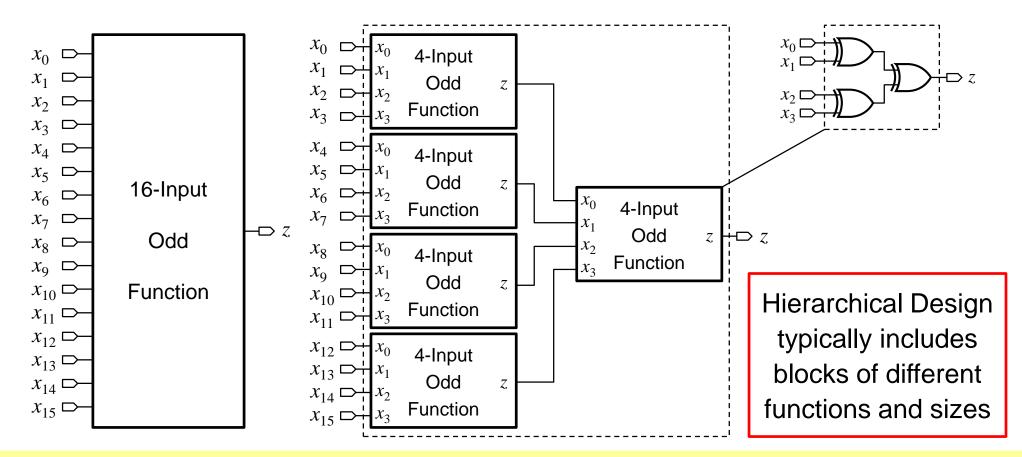

### Hierarchical Design

Why Hierarchical Design?

To simplify the implementation of a complex circuit

What is Hierarchical Design?

Decompose a complex circuit into smaller pieces called blocks

Decompose each block into even smaller blocks

Repeat as necessary until the blocks are small enough

Any block not decomposed is called a primitive block

The hierarchy is a tree of blocks at different levels

- The blocks are verified and well-document

- They are placed in a library for future use

### Example of Hierarchical Design

Top Level: 16-input odd function: 16 inputs, one output

♦ Implemented using Five 4-input odd functions

Second Level: 4-input odd function that uses three XOR gates

Combinational Circuit Design

### Top-Down versus Bottom-Up Design

- A top-down design proceeds from a high-level specification to a more and more detailed design by decomposition and successive refinement

- A bottom-up design starts with detailed primitive blocks and combines them into larger and more complex functional blocks

- Design usually proceeds top-down to a known set of building blocks, ranging from complete processors to primitive logic gates

### Hierarchical Design in Verilog

```

// Module Odd_4: 4-input Odd function uses three xor gates

module Odd_4 (input [0:3] x, output z);

wire [0:1] w;

xor g1(w[0], x[0], x[1]);

xor g2(w[1], x[2], x[3]);

xor g3(z, w[0], w[1]);

endmodule

```

```

// Module Odd_16: 16-input Odd function

module Odd_16 (input [0:15] x, output z);

wire [0:3] w;

Odd_4 block0 (x[0:3], w[0]);

Odd_4 block1 (x[4:7], w[1]);

Odd_4 block2 (x[8:11], w[2]);

Odd_4 block3 (x[12:15], w[3]);

Odd_4 block4 (w[0:3], z);

Five instances of

the Odd_4 module

endmodule

```

### Bit Vectors in Verilog

- ✤ A Bit Vector is multi-bit declaration that uses a single name

- A Bit Vector is specified as a Range [msb:lsb]

- \* msb is most-significant bit and lsb is least-significant bit

- Examples:

- input [0:15] x; // x is a 16-bit input vector

- wire [0:3] w; // Bit 0 is most-significant bit

- reg [7:0] a; // Bit 7 is most-significant bit

- Bit select: w[1] is bit 1 of vector w

- Part select: x[8:11] is a 4-bit select of x with range [8:11]

- The part select range must be consistent with vector declaration

### Testing Hierarchical Design

- Exhaustive testing can be very time consuming (or impossible)

- $\diamond$  For a 16-bit input, there are  $2^{16} = 65,536$  test cases (combinations)

- $\diamond$  For a 32-bit input, there are  $2^{32} = 4,294,967,296$  test cases

- $\Rightarrow$  For a 64-bit input, there are  $2^{64} = 18,446,744,073,709,551,616$  test cases!

- Testing a hierarchical design requires a different strategy

- Test each block in the hierarchy separately

- $\diamond$  For smaller blocks, exhaustive testing can be done

- ♦ It is easier to detect errors in smaller blocks before testing complete circuit

- Test the top-level design by applying selected test inputs

- Make sure that the test inputs exercise all parts of the circuit

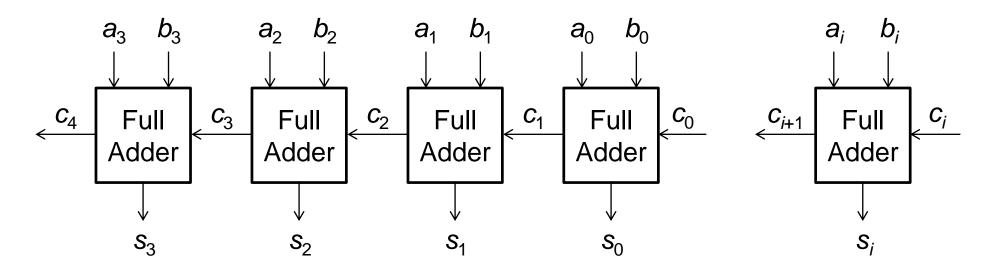

### Iterative Design

- Using identical copies of a smaller circuit to build a large circuit

- Example: Building a 4-bit adder using 4 copies of a full-adder

- The cell (iterative block) is a full adder

Adds 3 bits:  $a_i$ ,  $b_i$ ,  $c_i$ , Computes: Sum  $s_i$  and Carry-out  $c_{i+1}$

Carry-out of cell *i* becomes carry-in to cell (*i*+1)

### Full Adder

| Full adder adds 3 bits: a, b, and c    |   |   | Truth Tabl |      |  |  |

|----------------------------------------|---|---|------------|------|--|--|

| Two output bits:                       | а | b | С          | cout |  |  |

| 1. Carry bit: cout                     | 0 | 0 | 0          | 0    |  |  |

| 2. Sum bit: <b>sum</b>                 | 0 | 0 | 1          | 0    |  |  |

| Sum bit is 1 if the number of 1's in   | 0 | 1 | 0          | 0    |  |  |

| the input is odd (odd function)        | 0 | 1 | 1          | 1    |  |  |

| sum = (a⊕b)⊕c                          | 1 | 0 | 0          | 0    |  |  |

| Carry bit is 1 if the number of 1's in | 1 | 0 | 1          | 1    |  |  |

| the input is 2 or 3                    | 1 | 1 | 0          | 1    |  |  |

| cout = a·b + (a⊕b)·c                   | 1 | 1 | 1          | 1    |  |  |

**Table**

| the input is 2 or 3               |

|-----------------------------------|

| $cout = a \cdot b + (a \oplus b)$ |

| Circuit Design                    |

sum

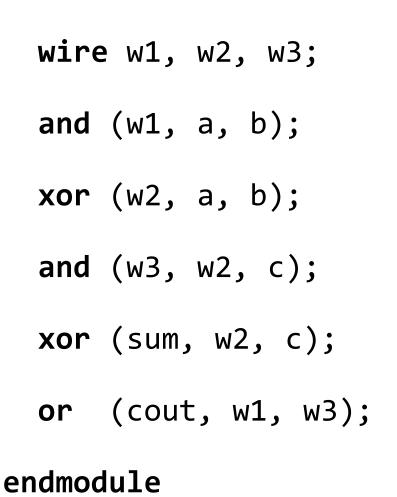

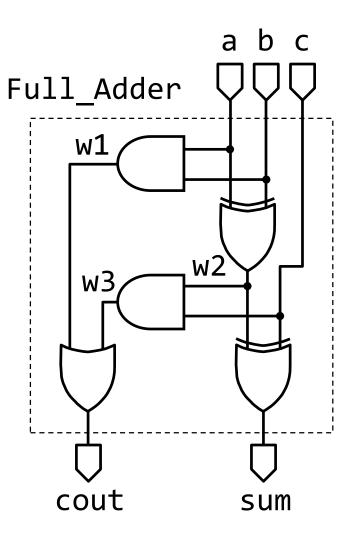

### Full Adder Module (Gate-Level Description)

module Full\_Adder(input a, b, c, output cout, sum);

### 16-Bit Adder with Array Instantiation

```

// Input ports: 16-bit a and b, 1-bit cin (carry input)

// Output ports: 16-bit sum, 1-bit cout (carry output)

```

| wire [16:0] c;                  | <pre>// carry bits</pre>   |

|---------------------------------|----------------------------|

| <pre>assign c[0] = cin;</pre>   | <pre>// carry input</pre>  |

| <pre>assign cout = c[16];</pre> | <pre>// carry output</pre> |

```

// Instantiate an array of 16 Full Adders

// Each instance [i] is connected to bit select [i]

```

```

Full_Adder adder [15:0] (a[15:0], b[15:0], c[15:0], c[16:1], sum[15:0]);

```

#### endmodule

Array Instantiation of identical modules by a single statement

### 16-Bit Adder with Continuous Assignment

| wire [16:0] c;                  | // carry bits              |

|---------------------------------|----------------------------|

| <pre>assign c[0] = cin;</pre>   | // carry input             |

| <pre>assign cout = c[16];</pre> | <pre>// carry output</pre> |

endmodule

### Testing the 16-bit Adder

- Exhaustive testing:  $2^{16} \times 2^{16} \times 2 = 8,589,934,592$  test cases

- $\bigstar$  Let us choose only:  $3 \times 3 \times 2 = 18$  test cases

- Input test cases for a[15:0] = 'h158A, 'h52AF, 'hB903 Chosen randomly with values shown in hexadecimal 'h158A (hexadecimal) = 'b0001\_0101\_1000\_1010 (binary) Underscores are ignored (used to enhance readability)

- Input test cases for b[15:0] = 'h7095, 'h9A4E, 'hC6BD Also chosen randomly with values shown in hexadecimal Radix symbol: 'b (binary), 'o (octal), 'd (decimal), 'h (hex)

- Input test cases for cin = 0, 1

### Writing a Test bench for the 16-bit Adder

```

module Test Adder 16;

// Test bench for Adder 16

reg [15:0] A, B; reg Cin;

// Data and Carry inputs

wire [15:0] Sum; wire Cout;

// Sum and Carry outputs

Adder 16 Test (A, B, Cin, Sum, Cout); // Instantiate 16-bit adder

initial begin

A='h158A; B='h7095; Cin=0;

// Initialize A, B, Cin

// t=10, Change Cin

#10 Cin=1;

#10 B='h9A4E; Cin=0;

// t=20, Change B and Cin

#10 Cin=1;

// t=30, Change Cin

// t=40, Change B and Cin

#10 B='hC6BD; Cin=0;

#10 Cin=1;

// t=50, Change Cin

// t=60, Change A, B and Cin

#10 A='h52AF; B='h7095; Cin=0;

// t=70, Change Cin

#10 Cin=1;

#10 B='h9A4E; Cin=0;

// t=80, Change B and Cin

// more test cases

• • •

#10 $finish;

// End simulation

end

endmodule

```

### Generating Test Cases in parallel with always

```

module Test Adder 16;

// Test bench for Adder_16

reg [15:0] A, B; reg Cin;

// Data and Carry inputs

wire [15:0] Sum; wire Cout;

// Sum and Carry outputs

Adder 16 Test (A, B, Cin, Sum, Cout); // Instantiate 16-bit adder

initial begin

A='h158A; B='h7095; Cin=0;

// Initialize A, B, Cin

#200 $finish;

// At t=200 end simulation

end

always begin

// Change A every 60 ns

#60 A='h52AF; #60 A='hB903; #60 A='h158A;

end

always begin

// Change B every 20 ns

#20 B='h9A4E; #20 B='hC6BD; #20 B='h7095;

end

always #10 Cin = ~Cin;

// Invert Cin every 10 ns

endmodule

```

Combinational Circuit Design

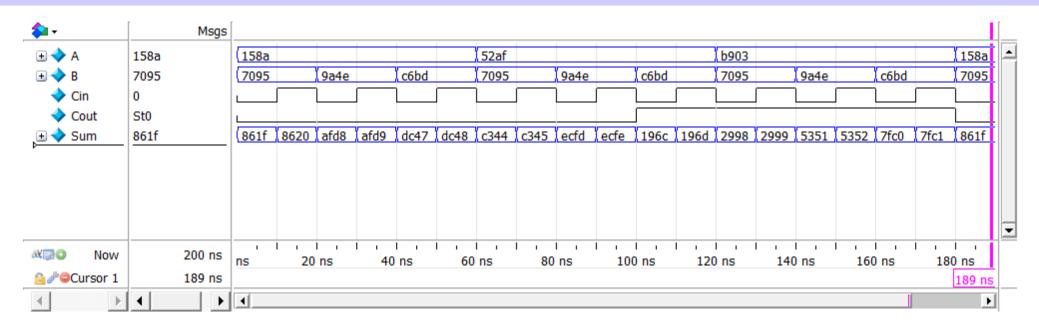

### Simulator Waveforms

The values of A, B, and Sum are shown in hexadecimal

Can change the radix to binary, octal, and decimal

- The values of Sum and Cout can be verified easily

- ✤ All 18 test cases of A, B, and Cin are generated (t=0 to 180 ns)