# Combinational Circuits (DC-IV) MCQs & Numerical Problems

The problems considered here are put under the following five subtopics. These are:

- (a) Arithmetic circuits

- (b) Multiplexers

- (c) Decoders and encoders

- (d) Code converters

- (e) Comparators

Some problems have been taken from previous GATE examination and some other problems are added for practice.

Special efforts are put to arrange them in the increasing order of their complexity, so that it is easier to learn progressively.

Video solution to some typical Gate problems will be given separately.

## Arithmetic Circuits

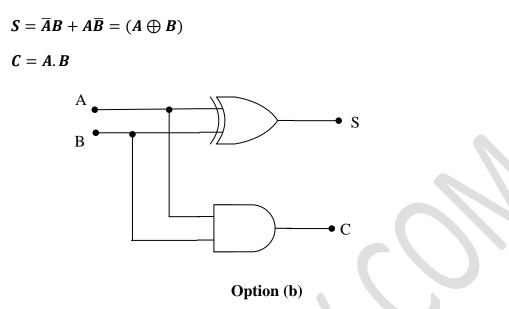

**1.** For a binary half adder having two inputs A and B the correct set of logical expressions the output

S(=A plus B) and C(= carry)

Are: (also given logic diagram)

(a)  $S = AB + \overline{AB}$  &  $C = \overline{AB}$ (b)  $S = \overline{AB} + A\overline{B}$  & C = AB(c)  $S = \overline{AB} + A\overline{B}$  &  $C = \overline{AB}$ (d)  $S = AB + \overline{AB}$  &  $C = A\overline{B}$

Sol. Half adder: logic circuit which adds two one bit number is called half adder.

**Truth table**

| Inputs |  |   | Outputs            |   |

|--------|--|---|--------------------|---|

| Α      |  | В | S (sum)<br>(carry) | С |

|        |  |   | (carry)            |   |

| 0      |  | 0 | 0                  | 0 |

| 0      |  | 1 | 1                  | 0 |

| 1      |  | 0 | 1                  | 0 |

| 1      |  | 1 | 0                  | 1 |

Expressions for sum and carry can be written from the truth table

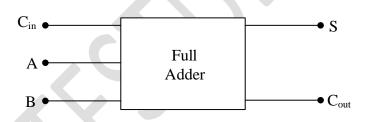

- **<u>2.</u>** Find the expression for sum and carry for binary full adder

- Soln. Full adder: Half adder has only two inputs (no provision of carry from lower order bits) when multi bit addition is preformed full adder takes care of it. Block diagram is shown in the Fig.

It consists of 3 inputs and 2 outputs.

**Truth table**

| Inputs |   |     | Outputs |                     |

|--------|---|-----|---------|---------------------|

| Α      | В | Cin | S (sum) | Cout (carry output) |

| 0      | 0 | 0   | 0       | 0                   |

| 0      | 0 | 1   | 1       | 0                   |

| 0      | 1 | 0   | 1       | 0                   |

| 0      | 1 | 1   | 0       | 1                   |

| 1      | 0 | 0   | 1       | 0                   |

| 1      | 0 | 1   | 0       | 1                   |

| 1      | 1 | 0   | 0       | 1                   |

| 1      | 1 | 1   | 1       | 1                   |

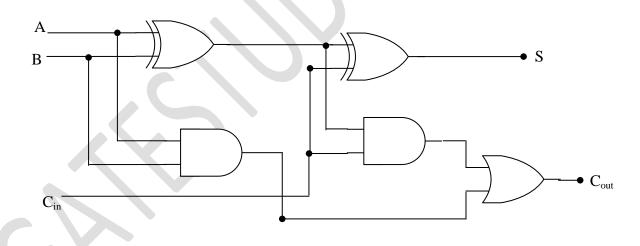

$$S = \overline{AB} C_{in} + \overline{AB}\overline{C}_{in} + A\overline{B}\overline{C}_{in} + ABC_{in}$$

$$= \overline{A}(\overline{B}C_{in} + B\overline{C}_{in}) + A(\overline{B}\overline{C}_{in} + BC_{in})$$

$$S = \overline{A}(B \oplus C_{in}) + A(\overline{B \oplus C_{in}})$$

$$S = A \oplus B \oplus C_{in}$$

(1)

$$C_{out} = \overline{A}BC_{in} + A\overline{B}C_{in} + AB\overline{C}_{in} + ABC_{in}$$

$$= BC_{in}(A + \overline{A}) + A\overline{B}C_{in} + ABC_{in}$$

$$C_{out} = BC_{in} + A\overline{B}C_{in} + AB\overline{C}_{in}$$

This expression can be written in the following form

$$C_{out} = BC_{in} + AC_{in} + AB$$

K-map simplification can also be done for above expressions full adder can also be implemented using two half adders and one OR gate. Figure gives such implementations

The S<sub>output</sub> from the second half adder is EX-OR of C<sub>in</sub>. C<sub>out</sub> is as per the expression, used modulo 2 adders instead of simple adder.

It is implemented with two half adders and one OR gate.

**<u>3.</u>** Find the expression for difference and borrow for binary full sub tractor.

## Soln. Half and full subtractors can be implemented in the same way

#### Half sub tractor

$D = X \oplus Y$  $B_{out} = \overline{X}Y$

**Full sub tractor**

$D = X \oplus Y \oplus B_{in}$

$B_{out} = \overline{X}Y + \overline{X}B_{in} + YB_{in}$

Full sub tractor can be implemented using two half sub tractors.

**<u>4.</u>** For a binary half sub tractor having two inputs A and B, the correct set of logical expressions for the outputs D (= A minus B) and X (= borrow) are

(a)  $D = AB + \overline{A}B, X = \overline{A}B$

(b)  $D = \overline{AB} + A\overline{B} + A\overline{B}, X = A\overline{B}$

- (c)  $D = \overline{AB} + A\overline{B}, X = \overline{AB}$

- (d)  $D = AB + \overline{A}\overline{B}, X = A\overline{B}$

[GATE-1999: 2 Marks]

## Soln. Truth table for the half sub tractor can be written as

| A B |   | D (Difference) | X (Borrow) |  |

|-----|---|----------------|------------|--|

| 0   | 0 | 0              | 0          |  |

| 0   | 1 | 1              | 1          |  |

| 1   | 0 | 1              | 0          |  |

| 1   | 1 | 0              | 0          |  |

**Boolean equation for Col D can be written as**

$D = \overline{A}B + A\overline{B}$

For Col. X

$X = \overline{A}B$  Option (C)

- 5. A 2 bit binary multiplier can be implemented using

- (a) 2 input ANDs only

- (b) 2 input X-ORs and 4-input AND gates only

- (c) Two (2) input NORs and one XNOR gate

- (d) XOR gates and shift registers

## [GATE-1997: 1 Mark]

Soln. Multiplication of binary numbers is done in the same manner as multiplication of decimal numbers. The process is simple because the multiplier digits are either 0 or 1

| <b>B</b> 1 | Bo    | Multiplicand    |

|------------|-------|-----------------|

| $A_1$      | A     | Multiplier      |

| A0 B1      | A0 B0 | Partial product |

A<sub>1</sub> B<sub>1</sub> A<sub>1</sub> B<sub>0</sub>

C<sub>3</sub> C<sub>2</sub> C<sub>1</sub> C<sub>0</sub>

Final product is sum of partial products. So it needs AND and OR operations

## **Multiplexers**

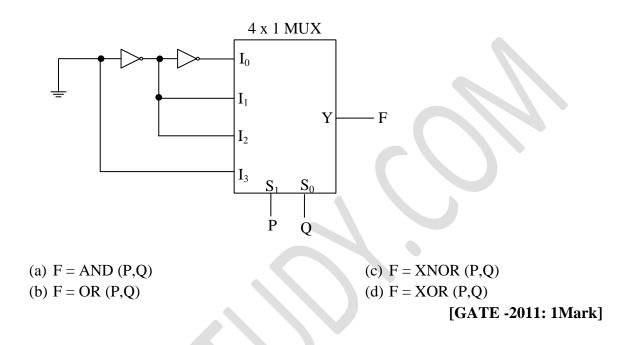

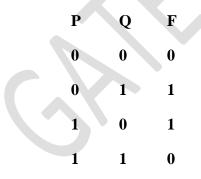

**<u>6</u>**. The logic function implemented by the circuit below is (ground implies a logic "0")

## Soln. Above circuit is redrawn to indicate the voltage levels

Truth table for MUX can be written as:

Output F can be written as

$F = \overline{P}Q + P\overline{Q} = P \oplus Q$

**Option** (d)

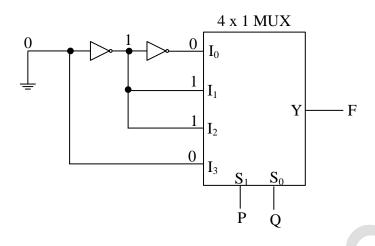

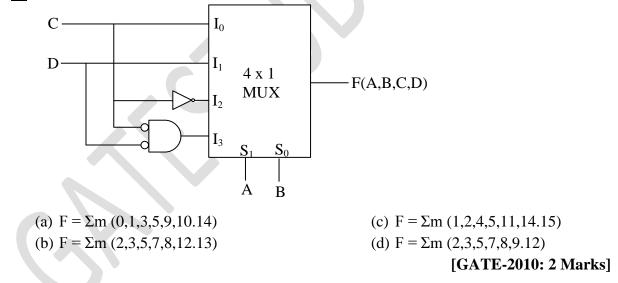

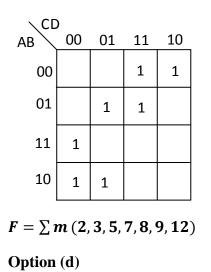

**7.** The Boolean function realized by the logic circuit shown is

Soln. Output can be written as

$F = \overline{A}\overline{B}C + \overline{A}BD + A\overline{B}\overline{C} + AB(\overline{C},\overline{D})$

Since the result is to be given in min term form, we expand the terms.

$$F = \overline{ABC}(D + \overline{D}) + \overline{ABD}(C + \overline{C}) + A\overline{B}\overline{C}(D + \overline{D}) + AB\overline{C}\overline{D}$$

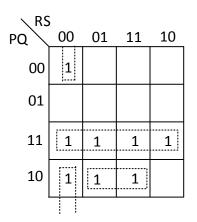

Min. terms are put in K-map

- **8.** What are the minimum number of 2-to-1 multiplexers required to generate a 2- input AND gate and a 2-input Ex-OR gate?

- (a) 1 and 2

- (b) 1 and 3

(c) 1 and 1(d) 2 and 2

[GATE-2009: 2 Marks]

## Soln. Consider 2-input AND gate

B is used in select line.

$F = \overline{B}.0 + B.A = AB$

AND gate

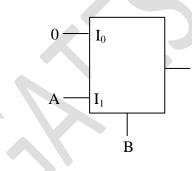

2-input EX-OR gate

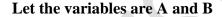

Let the variables be A & B for EX-OR gate complements of variable are also needed

$$F = \overline{B}A + \overline{A}B$$

#### Option (a) 1 and 2

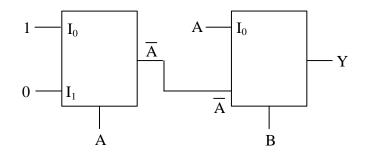

**9.** For the circuit shown in the following figure,  $I_0 - I_3$  are input to the 4:1 multiplexer R (MSB) and S are control bits.

(a)  $PQ + P\bar{Q}S + \bar{Q}\bar{R}\bar{S}$ (b)  $P\bar{Q} + PQ\bar{R} + \bar{P}Q\bar{S}$ (c)  $P\bar{Q}\bar{R} + \bar{P}QR + PQRS + \bar{Q}\bar{R}\bar{S}$ (d)  $PQ\bar{R} + PQR\bar{S} + P\bar{Q}\bar{R}S + \bar{Q}\bar{R}\bar{S}$ [GATE-2008: 2 Marks]

Soln.

$\overline{RS}.(P+\overline{Q})+\overline{RS}.P+R\overline{S}PQ+RSP$

$$= \overline{RSP} + \overline{RSQ} + \overline{RSP} + R\overline{SPQ} + RSP$$

Plot on K-map & simplify

$Z = PQ + P\overline{Q}S + \overline{Q}\overline{R}\overline{S}$

**Option** (a)

Result is in expanded form.

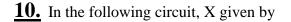

$$X = \overline{(\overline{A}B + A\overline{B})}.C + (\overline{A}B + A\overline{B}).\overline{C}$$

$$= \overline{\overline{A}B}.\overline{A}\overline{B}.C + \overline{A}B\overline{C} + A\overline{B}\overline{C}$$

$$= (A + \overline{B})(\overline{A} + B)C + \overline{A}B\overline{C} + A\overline{B}\overline{C}$$

$$ABC + \overline{A}\overline{B}C + \overline{A}B\overline{C} + A\overline{B}C$$

Option (a)

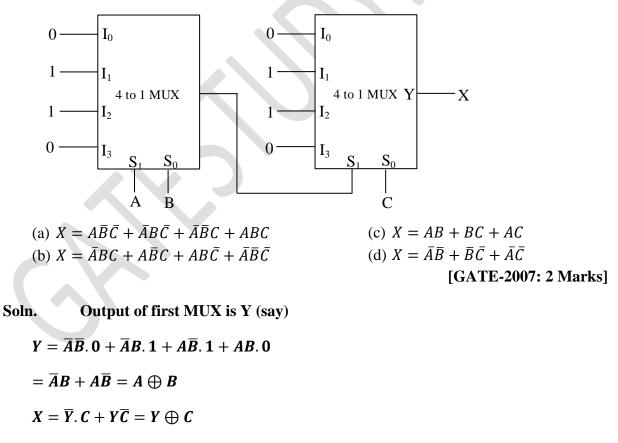

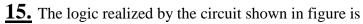

**<u>11.</u>** The Boolean function f implemented in the figure using two input multiplexers is

$E = \overline{B}C + B\overline{C}$

Output f can be written as

$$f = \overline{E} \cdot \mathbf{0} + EA = E \cdot A$$

So,

$$f = EA = A\overline{B}C + AB\overline{C}$$

**Option** (a)

**<u>12.</u>** The minimum number of 2-to-1 multiplexers required to realize a 4-to-1 multiplexer is

- (a) 1 (c) 3

- (b) 2 (d) 4

[GATE-2004: 2 Marks]

Soln. For lager number of inputs a tree is created. It is achieved by enable/strobe signal. No of inputs is double i.e. from 2 to 4

So we need the output from both these OR gate is required. One could also use 2:1 MUX instead of OR gate

So total number 2:1 MUX required is 2+1=3

**Option** (c)

**13.** Without any additional circuitry an 8:1 MUX can be used to obtain

- (a) Some but not all Boolean functions of 3 variables

- (b) All function of 3 variables but none of 4 variables

- (c) All functions of 3 variables and some but not all of 4 variables

- (d) All functions of 4 variables

[GATE-2003: 1 Mark]

## Soln. Note that

A 2<sup>n</sup>:1 MUX can implement all logic functions of (n+1) variables without any additional circuitry.

Thus 8:1 MUX can implement all logic functions of (3+1) variables

For 4 variables there are 16 possible combinations. So to use 8:1 MUX use 3 inputs as select lines of MUX and the 4<sup>th</sup> input as input of MUX

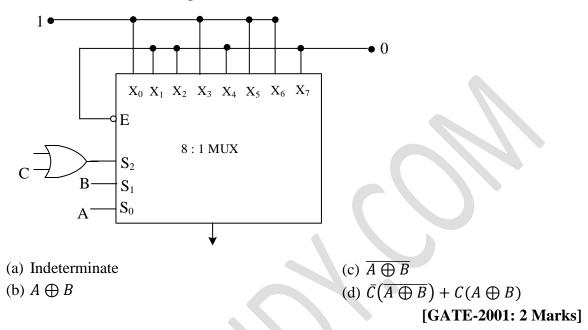

**<u>14.</u>** In the TTL circuit in the figure,  $S_2$  and  $S_0$  are select lines and  $X_7$  and  $X_0$  are input lines.  $S_0$  and  $X_0$  are LSBs. The output Y is

Soln. It is given that the MUX is made up of TTL circuit. For TTL circuit open terminal is taken high, since S<sub>2</sub> select line is connected to OR gate whose one terminal connected to C and the other is open (high) so OR gate output is  $S_2 = 1 + C = 1$

**So**,

$$S_2 = 1$$

| $S_2 = 1$ | S1(B) | <b>S0(A)</b> | Y |

|-----------|-------|--------------|---|

| 1         | 0     | 0            | 0 |

| 1         | 0     | 1            | 1 |

| 1         | 1     | 0            | 1 |

| 1         | 1     | 1            | 0 |

$Y = (S_1 \oplus S_0) = (A \oplus B)$

(b)

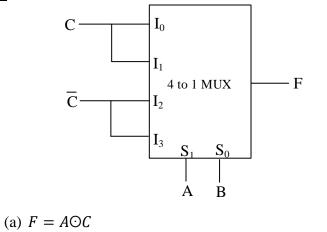

$$F = A \oplus C$$

(c)

$$F = B \odot C$$

(d)  $F = B \oplus C$

$F = \overline{A}\overline{B}C + \overline{A}BC + A\overline{B}\overline{C} + AB\overline{C}$

$$=\overline{A}C(\overline{B}+B)+A\overline{C}(\overline{B}+B)$$

- $=\overline{A}C+A\overline{C}$

- $= (A \oplus C)$

## **Code Convertors**

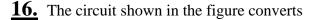

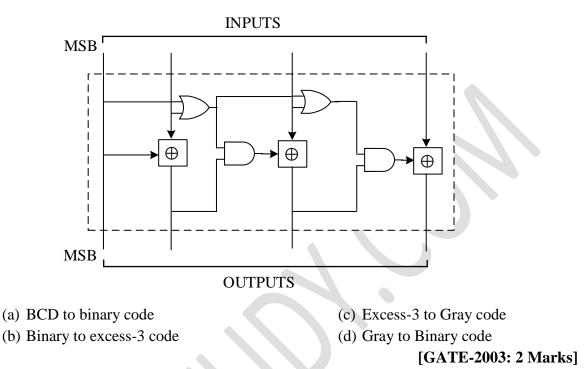

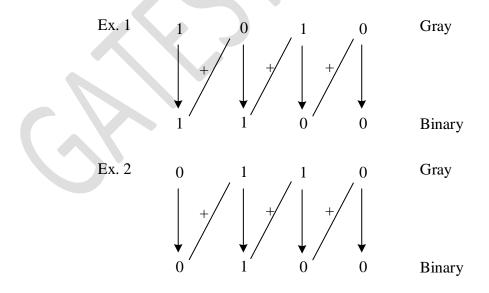

Soln. The circuit is a code converter i.e. converts input bit code to some other code. It uses EX-OR gates, and the inputs to EX-OR are from the input bit and output bit. So the guess is that the circuit is for gray to binary converter. Take some simple input bits and verify

Note that EX-OR gate is modulo 2 adder.

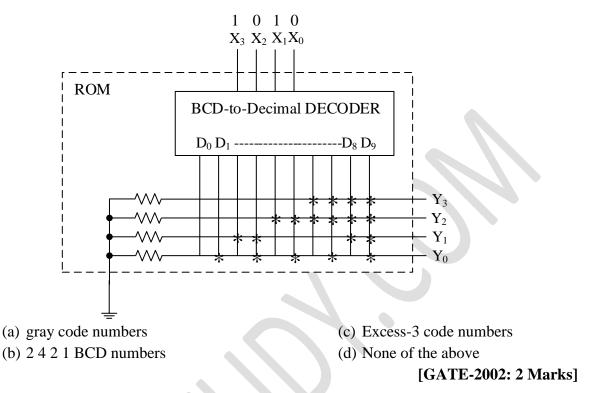

**<u>17.</u>** If the input X<sub>3</sub>, X<sub>2</sub>, X<sub>1</sub>, X<sub>0</sub> to the ROM in the figure are 8, 4, 2, 1 BCD numbers, then the output Y<sub>3</sub>, Y<sub>2</sub>, Y<sub>1</sub>, Y<sub>0</sub> are

Soln. The given circuit is for BCD to decimal decoder.

Consider input BCD code as 1001 this is equivalent to decimal  $9_{10}$  i.e.  $D_9$ . For this the outputs are

$Y_3 Y_2 Y_1 Y_0$  i.e. 1111

Take another BCD code.

1000 this is equivalent to  $8_{10}$  i.e.  $D_8$  the output is 1110

It can be verified that this corresponds to 2421 BCD numbers