# OUTLINE

Digital ICs

| 4-1 | Sum-of-Products Form          | 4-10 |

|-----|-------------------------------|------|

| 4-2 | Simplifying Logic Circuits    |      |

| 4-3 | Algebraic Simplification      | 4-11 |

| 4-4 | Designing Combinational       | 4-12 |

|     | Logic Circuits                | 4-13 |

| 4-5 | Karnaugh Map Method           |      |

| 4-6 | Exclusive-OR and              | 4-14 |

|     | <b>Exclusive-NOR Circuits</b> | 4-15 |

| 4-7 | Parity Generator and Checker  | 4-16 |

| 4-8 | Enable/Disable Circuits       | 4-17 |

| 4-9 | Basic Characteristics of      |      |

| 4-10 | Troubleshooting Digital Systems     |

|------|-------------------------------------|

| 4-11 | Internal Digital IC Faults          |

| 4-12 | External Faults                     |

| 4-13 | Troubleshooting Prototyped Circuits |

| 4-14 | Programmable Logic Devices          |

| 4-15 | Representing Data in HDL            |

| 4-16 | Truth Tables Using HDL              |

| 4-17 | <b>Decision Control Structures</b>  |

in HDL

# CHAPTER OUTCOMES

Upon completion of this chapter, you will be able to:

- Convert a logic expression into a sum-of-products expression.

- Perform the necessary steps to reduce a sum-of-products expression to its simplest form.

- Use Boolean algebra and the Karnaugh map as tools to simplify and design logic circuits.

- Explain the operation of both exclusive-OR and exclusive-NOR circuits.

- Design simple logic circuits without the help of a truth table.

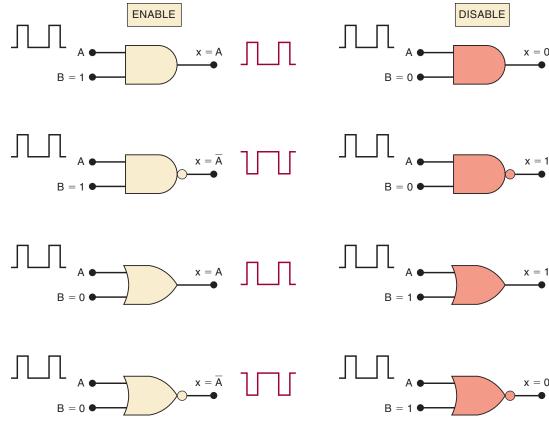

- Describe how to implement enable circuits.

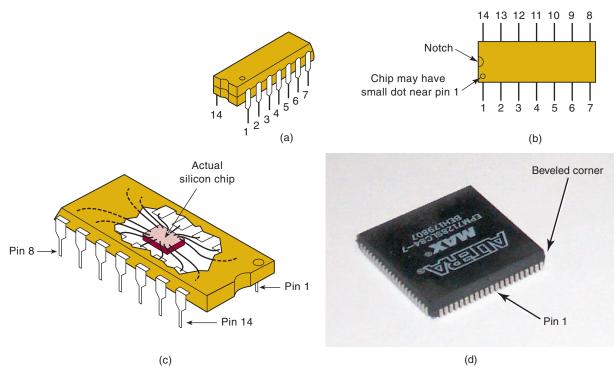

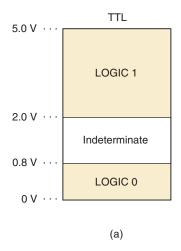

- Cite the basic characteristics of TTL and CMOS digital ICs.

- Use the basic troubleshooting rules of digital systems.

- Deduce from observed results the faults of malfunctioning combinational logic circuits.

- Describe the fundamental idea of programmable logic devices (PLDs)

- Describe the steps involved in programming a PLD to perform a simple combinational logic function.

- Describe hierarchical design methods.

- Identify proper data types for single-bit, bit array, and numeric value variables.

- Describe logic circuits using HDL control structures IF/ELSE, IF/ ELSIF, and CASE.

- Select the appropriate HDL control structure for a given problem.

# INTRODUCTION

In Chapter 3, we studied the operation of all the basic logic gates, and we used Boolean algebra to describe and analyze circuits that were made up of combinations of logic gates. These circuits can be classified as *combinational* logic circuits because, at any time, the logic level at the output depends on the combination of logic levels present at the inputs. A combinational circuit has no *memory* characteristic, so its output depends *only* on the current value of its inputs.

In this chapter, we will continue our study of combinational circuits. To start, we will go further into the simplification of logic circuits. Two methods will be used: one uses Boolean algebra theorems; the other uses a mapping technique. In addition, we will study simple techniques for designing combinational logic circuits to satisfy a given set of requirements. A complete study of logic-circuit design is not one of our objectives, but the methods we introduce will provide a good introduction to logic design.

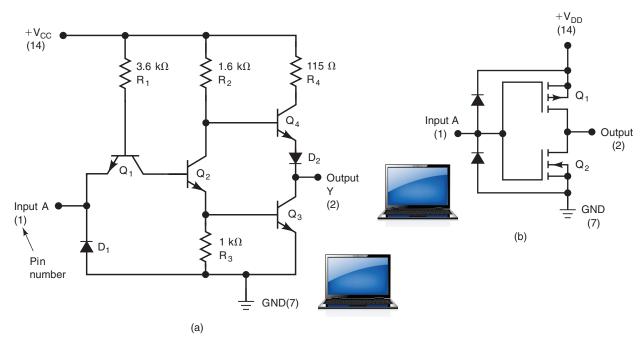

137

A good portion of this chapter is devoted to the topic of *troubleshooting*. This term has been adopted as a general description of the process of isolating a problem or fault in any system and identifying a way of fixing it. The analytical skills and efficient methods of troubleshooting are equally applicable to any system whether it is a plumbing problem, a problem with your car, a health issue, or a digital circuit. Digital systems, implemented using TTL-integrated circuits, have for decades provided an exceptional vehicle for the study of efficient, systematic troubleshooting methods. As with any system, the practical characteristics of the pieces that make up the system must be understood in order to effectively analyze its normal operation, locate the trouble, and propose a remedy. We will present some basic characteristics and typical failure modes of logic ICs in the TTL and CMOS families that are still commonly used for laboratory instruction in introductory digital courses and take advantage of this technology to teach some fundamental troubleshooting principles.

In the last sections of this chapter, we will extend our knowledge of programmable logic devices and hardware description languages. The concept of programmable hardware connections will be reinforced, and we will provide more details regarding the role of the development system. You will learn the steps followed in the design and development of digital systems today. Enough information will be provided to allow you to choose the correct types of data objects for use in simple projects to be presented later in this text. Finally, several control structures will be explained, along with some instruction regarding their appropriate use.

### 4-1 SUM-OF-PRODUCTS FORM

# **OUTCOMES**

Upon completion of this section, you will be able to:

- Identify the form of a sum-of-products (SOP) expression.

- Identify the form of a product-of-sums (POS) expression.

The methods of logic-circuit simplification and design that we will study require the logic expression to be in a sum-of-products (SOP) form. Some examples of this form are:

- 1.  $ABC + \overline{A}B\overline{C}$

- 2.  $AB + \overline{A}B\overline{C} + \overline{C}\overline{D} + D$

- 3.  $\overline{A}B + C\overline{D} + EF + GK + H\overline{L}$

Each of these sum-of-products expressions consists of two or more AND terms (products) that are ORed together. Each AND term consists of one or more variables *individually* appearing in either complemented or uncomplemented form. For example, in the sum-of-products expression  $ABC + \overline{A}B\overline{C}$ , the first AND product contains the variables A, B, and C in their uncomplemented (not inverted) form. The second AND term contains A and C in their complemented (inverted) form. Note that in a sum-of-products expression, one inversion sign *cannot* cover more than one variable in a term (e.g., we cannot have  $\overline{ABC}$  or  $\overline{RS}T$ ).

#### **Product-of-Sums**

Another general form for logic expressions is sometimes used in logic-circuit design. Called the **product-of-sums (POS)** form, it consists of two or more OR

terms (sums) that are ANDed together. Each OR term contains one or more variables in complemented or uncomplemented form. Here are some product-of-sum expressions:

1.

$$(A + \overline{B} + C)(A + C)$$

2.

$$(A + \overline{B})(\overline{C} + D)F$$

3.

$$(A + C)(B + \overline{D})(\overline{B} + C)(A + \overline{D} + \overline{E})$$

The methods of circuit simplification and design that we will be using are based on the sum-of-products form, so we will not be doing much with the product-of-sums form. It will, however, occur from time to time in some logic circuits that have a particular structure.

OUTCOME ASSESSMENT QUESTIONS

1. Which of the following expressions is in SOP form?

(a)

$$AB + CD + E$$

(b)

$$AB(C + D)$$

(c)

$$(A + B)(C + D + F)$$

(d)

$$\overline{MN} + PQ$$

2. Repeat question 1 for the POS form.

# 4-2 SIMPLIFYING LOGIC CIRCUITS

## **OUTCOMES**

Upon completion of this section, you will be able to:

- Justify the use of simplification.

- Name two simplification techniques for digital circuits.

Once the expression for a logic circuit has been obtained, we may be able to reduce it to a simpler form containing fewer terms or fewer variables in one or more terms. The new expression can then be used to implement a circuit that is equivalent to the original circuit but that contains fewer gates and connections.

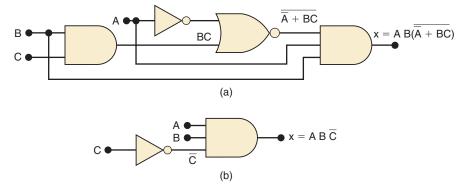

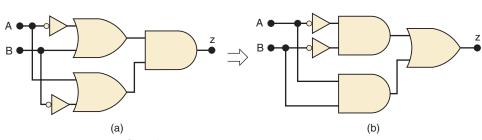

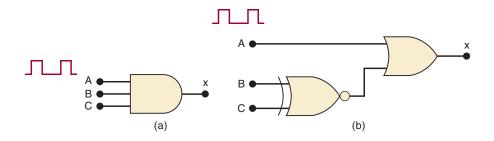

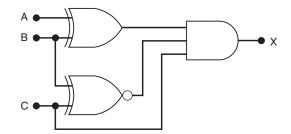

To illustrate, the circuit of Figure 4-1(a) can be simplified to produce the circuit of Figure 4-1(b). Both circuits perform the same logic, so it should be obvious that the simpler circuit is more desirable because it contains fewer

**FIGURE 4-1** It is often possible to simplify a logic circuit such as that in part (a) to produce a more efficient implementation, shown in (b).

gates and will therefore be smaller and cheaper than the original. Furthermore, the circuit reliability will improve because there are fewer interconnections that can be potential circuit faults.

Another strategic advantage of simplifying logic circuits involves the operational speed of circuits. Recall from previous discussions that logic gates are subject to propagation delay. If practical logic circuits are configured such that logical changes in the inputs must propagate through many layers of gates in order to determine the output, they cannot possibly operate as fast as circuits with fewer layers of gates. For example, compare the circuits of Figure 4-1(a) and (b). In Figure 4-1(a), the longest path a signal must travel involves three gates. In Figure 4-1(b), the longest signal path (C) only involves two gates. Working toward a common form such as SOP or POS assures similar propagation delay for all signals in the system and helps determine the maximum operating speed of the system.

In subsequent sections, we will study two methods for simplifying logic circuits. One method will utilize the Boolean algebra theorems and, as we shall see, is greatly dependent on inspiration and experience. The other method (Karnaugh mapping) is a systematic, step-by-step approach. Some instructors may wish to skip over this latter method because it is somewhat mechanical and probably does not contribute to a better understanding of Boolean algebra. This can be done without affecting the continuity or clarity of the rest of the text.

OUTCOME ASSESSMENT QUESTIONS

- 1. List two advantages of simplification.

- 2. List two methods of simplification.

### 4-3 ALGEBRAIC SIMPLIFICATION

### **OUTCOMES**

Upon completion of this section, you will be able to:

- Apply Boolean algebra theorems and properties to reduce Boolean expressions.

- Manipulate expressions into POS or SOP form.

We can use the Boolean algebra theorems that we studied in Chapter 3 to help us simplify the expression for a logic circuit. Unfortunately, it is not always obvious which theorems should be applied to produce the simplest result. Furthermore, there is no easy way to tell whether the simplified expression is in its simplest form or whether it could have been simplified further. Thus, algebraic simplification often becomes a process of trial and error. With experience, however, one can become adept at obtaining reasonably good results.

The examples that follow will illustrate many of the ways in which the Boolean theorems can be applied in trying to simplify an expression. You should notice that these examples contain two essential steps:

1. The original expression is put into SOP form by repeated application of DeMorgan's theorems and multiplication of terms.

2. Once the original expression is in SOP form, the product terms are checked for common factors, and factoring is performed wherever possible. The factoring should result in the elimination of one or more terms.

### **EXAMPLE 4-1**

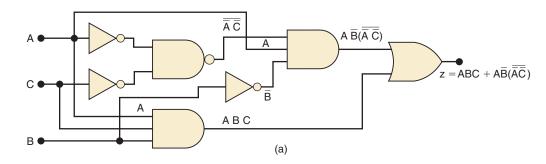

Simplify the logic circuit shown in Figure 4-2(a).

FIGURE 4-2 Example 4-1.

#### **Solution**

The first step is to determine the expression for the output using the method presented in Section 3-6. The result is

$$z = ABC + A\overline{B} \cdot (\overline{\overline{A} \ \overline{C}})$$

Once the expression is determined, it is usually a good idea to break down all large inverter signs using DeMorgan's theorems and then multiply out all terms.

$$\begin{split} z &= ABC + A\overline{B}(\overline{\overline{A}} + \overline{\overline{C}}) & \text{[theorem (17)]} \\ &= ABC + A\overline{B}(A + C) & \text{[cancel double inversions]} \\ &= ABC + A\overline{B}A + A\overline{B}C & \text{[multiply out]} \\ &= ABC + A\overline{B} + A\overline{B}C & \text{[$A \cdot A = A$]} \end{split}$$

With the expression now in SOP form, we should look for common variables among the various terms with the intention of factoring. The first and third terms above have *AC* in common, which can be factored out:

$$z = AC(B + \overline{B}) + A\overline{B}$$

Since  $B + \overline{B} = 1$ , then

$$z = AC(1) + A\overline{B}$$

$$= AC + A\overline{B}$$

We can now factor out A, which results in

$$z = A(C + \overline{B})$$

This result can be simplified no further. Its circuit implementation is shown in Figure 4-2(b). It is obvious that the circuit in Figure 4-2(b) is a great deal simpler than the original circuit in Figure 4-2(a).

### **EXAMPLE 4-2**

Simplify the expression  $z = A\overline{B} \ \overline{C} + A\overline{B}C + ABC$ .

#### **Solution**

The expression is already in SOP form.

*Method 1:* The first two terms in the expression have the product  $A\overline{B}$  in common. Thus,

$$z = A\overline{B}(\overline{C} + C) + ABC$$

=  $A\overline{B}(1) + ABC$

=  $A\overline{B} + ABC$

We can factor the variable *A* from both terms:

$$z = A(\overline{B} + BC)$$

Invoking theorem (15b):

$$z = A(\overline{B} + C)$$

*Method 2:* The original expression is  $z = A\overline{B}\overline{C} + A\overline{B}C + ABC$ . The first two terms have  $A\overline{B}$  in common. The last two terms have AC in common. How do we know whether to factor  $A\overline{B}$  from the first two terms or AC from the last two terms? Actually, we can do both by using the  $A\overline{B}C$  term *twice*. In other words, we can rewrite the expression as:

$$z = A\overline{B}\,\overline{C} + A\overline{B}C + A\overline{B}C + ABC$$

where we have added an extra term  $A\overline{B}C$ . This is valid and will not change the value of the expression because  $A\overline{B}C + A\overline{B}C = A\overline{B}C$  [theorem (7)]. Now we can factor  $A\overline{B}$  from the first two terms and AC from the last two terms:

$$z = A\overline{B}(C + \overline{C}) + AC(\overline{B} + B)$$

=  $A\overline{B} \cdot 1 + AC \cdot 1$

=  $A\overline{B} + AC = A(\overline{B} + C)$

Of course, this is the same result obtained with method 1. This trick of using the same term twice can always be used. In fact, the same term can be used more than twice if necessary.

### **EXAMPLE 4-3**

Simplify  $z = \overline{A}C(\overline{\overline{A}BD}) + \overline{A}B\overline{C}\overline{D} + A\overline{B}C$ .

#### **Solution**

First, use DeMorgan's theorem on the first term:

$$z = \overline{A}C(A + \overline{B} + \overline{D}) + \overline{A}B\overline{C}\overline{D} + A\overline{B}C$$

(step 1)

Multiplying out yields

$$z = \overline{A}CA + \overline{A}C\overline{B} + \overline{A}C\overline{D} + \overline{A}B\overline{C}\overline{D} + A\overline{B}C$$

(2)

Because  $\overline{A} \cdot A = 0$ , the first term is eliminated:

$$z = \overline{A}\overline{B}C + \overline{A}C\overline{D} + \overline{A}B\overline{C}\overline{D} + A\overline{B}C$$

(3)

This is the desired SOP form. Now we must look for common factors among the various product terms. The idea is to check for the largest common factor between any two or more product terms. For example, the first and last terms have the common factor  $\overline{BC}$ , and the second and third terms share the common factor  $\overline{AD}$ . We can factor these out as follows:

$$z = \overline{B}C(\overline{A} + A) + \overline{A}\overline{D}(C + B\overline{C})$$

(4)

Now, because  $\overline{A} + A = 1$ , and  $C + B\overline{C} = C + B$  [theorem (15a)], we have

$$z = \overline{B}C + \overline{A}\overline{D}(B + C) \tag{5}$$

This same result could have been reached with other choices for the factoring. For example, we could have factored *C* from the first, second, and fourth product terms in step 3 to obtain

$$z = C(\overline{A}\overline{B} + \overline{A}\overline{D} + A\overline{B}) + \overline{A}B\overline{C}\overline{D}$$

The expression inside the parentheses can be factored further:

$$z = C(\overline{B}[\overline{A} + A] + \overline{A}\overline{D}) + \overline{A}B\overline{C}\overline{D}$$

Because  $\overline{A} + A = 1$ , this becomes

$$z = C(\overline{B} + \overline{A}\overline{D}) + \overline{A}B\overline{C}\overline{D}$$

Multiplying out yields

$$z = \overline{B}C + \overline{A}C\overline{D} + \overline{A}B\overline{C}\overline{D}$$

Now we can factor  $\overline{A}\overline{D}$  from the second and third terms to get

$$z = \overline{B}C + \overline{A}\overline{D}(C + B\overline{C})$$

If we use theorem (15a), the expression in parentheses becomes B + C. Thus, we finally have

$$z = \overline{B}C + \overline{A}\overline{D}(B + C)$$

This is the same result that we obtained earlier, but it took us many more steps. This illustrates why you should look for the largest common factors: it will generally lead to the final expression in the fewest steps.

Example 4-3 illustrates the frustration often encountered in Boolean simplification. Because we have arrived at the same equation (which appears irreducible) by two different methods, it might seem reasonable to conclude that this final equation is the simplest form. In fact, the simplest form of this equation is

$$z = \overline{A}B\overline{D} + \overline{B}C$$

But there is no apparent way to reduce step (5) to reach this simpler version. In this case, we missed an operation earlier in the process that could have led to the simpler form. The question is, "How could we have known that we missed a step?" Later in this chapter, we will examine a mapping technique that will always lead to the simplest SOP form.

### **EXAMPLE 4-4**

Simplify the expression  $x = (\overline{A} + B)(A + B + D)\overline{D}$ .

#### **Solution**

The expression can be put into sum-of-products form by multiplying out all the terms. The result is

$$x = \overline{A}A\overline{D} + \overline{A}B\overline{D} + \overline{A}D\overline{D} + BA\overline{D} + BB\overline{D} + BD\overline{D}$$

The first term can be eliminated because  $\overline{A}A = 0$ . Likewise, the third and sixth terms can be eliminated because  $D\overline{D} = 0$ . The fifth term can be simplified to  $B\overline{D}$  because BB = B. This gives us

$$x = \overline{A}B\overline{D} + AB\overline{D} + B\overline{D}$$

We can factor  $B\overline{D}$  from each term to obtain

$$x = B\overline{D}(\overline{A} + A + 1)$$

Clearly, the term inside the parentheses is always 1, so we finally have

$$x = B\overline{D}$$

### **EXAMPLE 4-5**

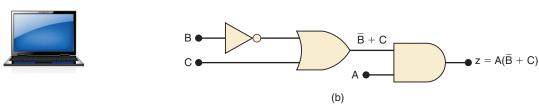

Simplify the circuit of Figure 4-3(a).

FIGURE 4-3 Example 4-5.

#### **Solution**

The expression for output z is

$$z = (\overline{A} + B)(A + \overline{B})$$

Multiplying out to get the sum-of-products form, we obtain

$$z = \overline{A}A + \overline{A}\overline{B} + BA + B\overline{B}$$

We can eliminate  $\overline{A}A = 0$  and  $B\overline{B} = 0$  to end up with

$$z = \overline{A}\overline{B} + AB$$

This expression is implemented in Figure 4-3(b), and if we compare it with the original circuit, we see that both circuits contain the same number of gates and connections. In this case, the simplification process produced an equivalent, but not simpler, circuit.

**EXAMPLE 4-6**

Simplify

$$x = A\overline{B}C + \overline{A}BD + \overline{C}\overline{D}$$

.

#### Solution

You can try, but you will not be able to simplify this expression any further.

OUTCOME ASSESSMENT QUESTIONS

- 1. State which of the following expressions are *not* in the sum-of-products form:

- (a)  $RS\overline{T} + \overline{R}S\overline{T} + \overline{T}$

- (b)  $A\overline{CD} + \overline{A}CD$

- (c)  $MN\overline{P} + (M + \overline{N})P$

- (d)  $AB + \overline{A}B\overline{C} + A\overline{B}\overline{C}D$

- 2. Simplify the circuit in Figure 4-1(a) to arrive at the circuit of Figure 4-1(b).

- 3. Change each AND gate in Figure 4-1(a) to a NAND gate. Determine the new expression for x and simplify it.

# 4-4 DESIGNING COMBINATIONAL LOGIC CIRCUITS

### **OUTCOMES**

Upon completion of this section, you will be able to:

- Systematically design a circuit to perform any logic function of up to four variables.

- List the steps of the design process.

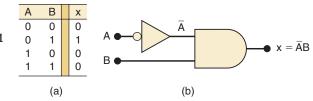

When the desired output level of a logic circuit is given for all possible input conditions, the results can be conveniently displayed in a truth table. The Boolean expression for the required circuit can then be derived from the truth table. For example, consider Figure 4-4(a), where a truth table is shown for a circuit that has two inputs, A and B, and output x. The table shows that output x is to be at the 1 level *only* for the case where A = 0

**FIGURE 4-4** Circuit that produces a 1 output only for the A = 0, B = 1 condition.

and B=1. It now remains to determine what logic circuit will produce this desired operation. It should be apparent that one possible solution is that shown in Figure 4-4(b). Here an AND gate is used with inputs  $\overline{A}$  and B, so that  $x=\overline{A}\cdot B$ . Obviously x will be 1 *only if* both inputs to the AND gate are 1, namely,  $\overline{A}=1$  (which means that A=0) and B=1. For all other values of A and B, the output x will be 0.

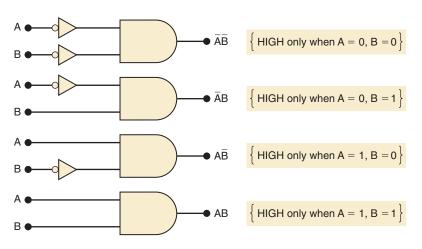

A similar approach can be used for the other input conditions. For instance, if x were to be HIGH only for the A=1, B=0 condition, the resulting circuit would be an AND gate with inputs A and  $\overline{B}$ . In other words, for any of the four possible input conditions, we can generate a HIGH x output by using an AND gate with appropriate inputs to generate the required AND product. The four different cases are shown in Figure 4-5. Each of the AND gates shown generates an output that is HIGH *only* for one given input condition and the output is LOW for all other conditions. It should be noted that the AND inputs are inverted or not inverted depending on the values that the variables have for the given condition. If the variable is LOW for the given condition, it is inverted before entering the AND gate.

**FIGURE 4-5** An AND gate with appropriate inputs can be used to produce a HIGH output for a specific set of input levels.

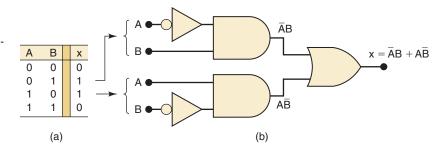

Let us now consider the case shown in Figure 4-6(a), where we have a truth table that indicates that the output x is to be 1 for two different cases: A=0, B=1 and A=1, B=0. How can this be implemented? We know that the AND term  $\overline{A} \cdot B$  will generate a 1 only for the A=0, B=1 condition, and the AND term  $A \cdot \overline{B}$  will generate a 1 for the A=1, B=0 condition. Because x=1 for *either* condition, it should be clear that these terms should be ORed together to produce the desired output, x. This implementation is shown in Figure 4-6(b), where the resulting expression for the output is  $x=\overline{A}B+A\overline{B}$ .

In this example, an AND term is generated for each case in the table where the output x = 1. The AND gate outputs are then ORed together to produce the total output x, which will be 1 when either AND term is 1. This same procedure can be extended to examples with more than two inputs. Consider the truth table for a three-input circuit (Table 4-1). Here there

FIGURE 4-6 Each set of input conditions that is to produce a 1 output is implemented by a separate AND gate. The AND outputs are ORed to produce the final output.

are three cases where the output x = 1. The required AND term for each of these cases is shown. Again, note that for each case where a variable is 0, it appears inverted in the AND term. The sum-of-products expression for x is obtained by ORing the three AND terms.

$$x = \overline{A}B\overline{C} + \overline{A}BC + ABC$$

**TABLE 4-1** Generating AND terms.

| A | В | С | х |                                         |

|---|---|---|---|-----------------------------------------|

| 0 | 0 | 0 | 0 |                                         |

| 0 | 0 | 1 | 0 |                                         |

| 0 | 1 | 0 | 1 | $\rightarrow \overline{A}B\overline{C}$ |

| 0 | 1 | 1 | 1 | $\rightarrow \overline{A}BC$            |

| 1 | 0 | 0 | 0 |                                         |

| 1 | 0 | 1 | 0 |                                         |

| 1 | 1 | 0 | 0 |                                         |

| 1 | 1 | 1 | 1 | $\rightarrow ABC$                       |

|   |   |   |   |                                         |

# **Complete Design Procedure**

Any logic problem can be solved using the following step-by-step procedure.

- 1. Interpret the problem and set up a truth table to describe its operation.

- 2. Write the AND (product) term for each case where the output is 1.

- 3. Write the sum-of-products (SOP) expression for the output.

- 4. Simplify the output expression if possible.

- 5. Implement the circuit for the final, simplified expression.

The following example illustrates the complete design procedure.

# **EXAMPLE 4-7**

Design a logic circuit that has three inputs, *A*, *B*, and *C*, and whose output will be HIGH only when a majority of the inputs are HIGH.

# Solution

### **Step 1.** Set up the truth table.

On the basis of the problem statement, the output x should be 1 whenever two or more inputs are 1; for all other cases, the output should be 0 (Table 4-2).

**TABLE 4-2** Example 4-7: truth table with AND terms.

| Α | В | С | x |                              |

|---|---|---|---|------------------------------|

| 0 | 0 | 0 | 0 |                              |

| 0 | 0 | 1 | 0 |                              |

| 0 | 1 | 0 | 0 |                              |

| 0 | 1 | 1 | 1 | $\rightarrow \overline{A}BC$ |

| 1 | 0 | 0 | 0 |                              |

| 1 | 0 | 1 | 1 | $\rightarrow A\overline{B}C$ |

| 1 | 1 | 0 | 1 | $\rightarrow AB\overline{C}$ |

| 1 | 1 | 1 | 1 | $\rightarrow ABC$            |

|   |   |   |   |                              |

## **Step 2.** Write the AND term for each case where the output is a 1.

There are four such cases. The AND terms are shown next to the truth table (Table 4-2). Again note that each AND term contains each input variable in either inverted or noninverted form.

**Step 3.** Write the sum-of-products expression for the output.

$$x = \overline{A}BC + A\overline{B}C + AB\overline{C} + ABC$$

### **Step 4.** Simplify the output expression.

This expression can be simplified in several ways. Perhaps the quickest way is to realize that the last term *ABC* has two variables in common with each of the other terms. Thus, we can use the *ABC* term to pair with each of the other terms. The expression is rewritten with the *ABC* term occurring three times (recall from Example 4-2 that this is legal in Boolean algebra):

$$x = \overline{A}BC + ABC + A\overline{B}C + ABC + AB\overline{C} + ABC$$

Factoring the appropriate pairs of terms, we have

$$x = BC(\overline{A} + A) + AC(\overline{B} + B) + AB(\overline{C} + C)$$

Each term in parentheses is equal to 1, so we have

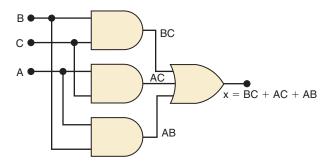

$$x = BC + AC + AB$$

# **Step 5.** Implement the circuit for the final expression.

This expression is implemented in Figure 4-7. Since the expression is in SOP form, the circuit consists of a group of AND gates working into a single OR gate.

**FIGURE 4-7** Example 4-7.

### **EXAMPLE 4-8**

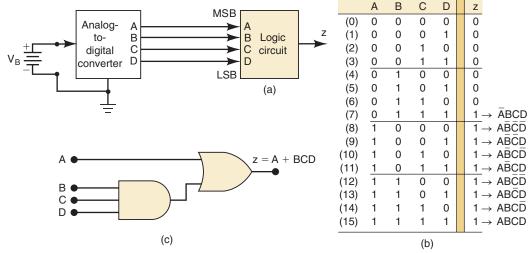

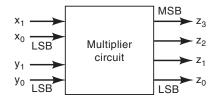

Refer to Figure 4-8(a), where an analog-to-digital converter is monitoring the dc voltage ( $V_{\rm B}$ ) of a 12-V storage battery on an orbiting spaceship. The converter's output is a four-bit binary number, ABCD, corresponding to the battery voltage in steps of 1 V, with A as the MSB. The converter's binary outputs are fed to a logic circuit that is to produce a HIGH output as long as the binary value is greater than  $0110_2 = 6_{10}$ ; that is, the battery voltage is greater than 6 V. Design this logic circuit.

FIGURE 4-8 Example 4-8

### Solution

The truth table is shown in Figure 4-8(b). For each case in the truth table, we have indicated the decimal equivalent of the binary number represented by the *ABCD* combination.

The output z is set equal to 1 for all those cases where the binary number is greater than 0110. For all other cases, z is set equal to 0. This truth table gives us the following sum-of-products expression:

$$z = \overline{A}BCD + A\overline{B}\overline{C}\overline{D} + A\overline{B}\overline{C}D + A\overline{B}C\overline{D} + A\overline{B}CD + AB\overline{C}\overline{D} + ABC\overline{D} + ABC\overline{D} + ABCD$$

Simplification of this expression will be a formidable task, but with a little care it can be accomplished. The step-by-step process involves factoring and eliminating terms of the form  $A+\overline{A}$ :

$$\begin{split} z &= \overline{A}BCD + A\overline{B}\,\overline{C}(\overline{D} + D) + A\overline{B}C(\overline{D} + D) + AB\overline{C}(\overline{D} + D) + ABC(\overline{D} + D) \\ &= \overline{A}BCD + A\overline{B}\,\overline{C} + A\overline{B}C + AB\overline{C} + ABC \\ &= \overline{A}BCD + A\overline{B}(\overline{C} + C) + AB(\overline{C} + C) \\ &= \overline{A}BCD + A\overline{B} + AB \\ &= \overline{A}BCD + A(\overline{B} + B) \\ &= \overline{A}BCD + A \end{split}$$

This can be reduced further by invoking theorem (15a), which says that  $x + \overline{xy} = x + y$ . In this case x = A and y = BCD. Thus,

$$z = \overline{A}BCD + A = BCD + A$$

This final expression is implemented in Figure 4-8(c).

As this example demonstrates, the algebraic simplification method can be quite lengthy when the original expression contains a large number of terms. This is a limitation that is not shared by the Karnaugh mapping method, as we will see later.

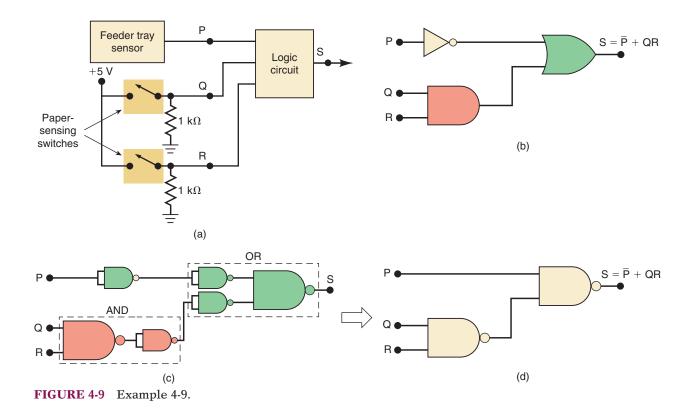

# **EXAMPLE 4-9**

Refer to Figure 4-9(a). In a simple copy machine, a stop signal, *S*, is to be generated to stop the machine operation and energize an indicator light whenever either of the following conditions exists: (1) there is no paper in the paper feeder tray; or (2) the two microswitches in the paper path are activated, indicating a jam in the paper path. The presence of paper in the feeder tray is indicated by a HIGH at logic signal *P*. Each of the microswitches produces a logic signal (*Q* and *R*) that goes HIGH whenever paper is passing over the switch to activate it. Design the logic circuit to produce a HIGH at output signal *S* for the stated conditions, and implement it using the 74HC00 CMOS quad two-input NAND chip.

#### **Solution**

We will use the five-step process used in Example 4-7. The truth table is shown in Table 4-3. The S output will be a logic 1 whenever P=0 because this indicates no paper in the feeder tray. S will also be a 1 for the two cases where Q and R are both 1, indicating a paper jam. As the table shows, there are five different input conditions that produce a HIGH output. (Step 1)

**TABLE 4-3** Example 4-9: Truth table with AND terms.

| P  | Q | R | S |                                        |

|----|---|---|---|----------------------------------------|

| 0  | 0 | 0 | 1 | $\overline{P}\overline{Q}\overline{R}$ |

| 0  | 0 | 1 | 1 | $\overline{P}\overline{Q}R$            |

| 0  | 1 | 0 | 1 | $\overline{P}Q\overline{R}$            |

| 0  | 1 | 1 | 1 | $\overline{P}QR$                       |

| 1  | 0 | 0 | 0 |                                        |

| 1  | 0 | 1 | 0 |                                        |

| 1  | 1 | 0 | 0 |                                        |

| _1 | 1 | 1 | 1 | PQR                                    |

The AND terms for each of these cases are shown. (Step 2)

The sum-of-products expression becomes

$$S = \overline{P}\overline{Q}\overline{R} + \overline{P}\overline{Q}R + \overline{P}Q\overline{R} + \overline{P}QR + PQR$$

(Step 3)

We can begin the simplification by factoring out  $\overline{PQ}$  from terms 1 and 2 and by factoring out  $\overline{PQ}$  from terms 3 and 4:

$$S = \overline{P}\overline{Q}(\overline{R} + R) + \overline{P}Q(\overline{R} + R) + PQR$$

Now we can eliminate the  $\overline{R} + R$  terms because they equal 1:

$$S = \overline{PQ} + \overline{PQ} + PQR$$

Factoring  $\overline{P}$  from terms 1 and 2 allows us to eliminate Q from these terms:

$$S = \overline{P} + PQR$$

Here we can apply theorem (15b)  $(\bar{x} + xy = \bar{x} + y)$  to obtain

$$S = \overline{P} + QR \tag{Step 4}$$

As a double check of this simplified Boolean equation, let's see if it matches the truth table that we started out with. This equation says that the output *S* will be HIGH whenever *P* is LOW OR both *Q* AND *R* are HIGH. Look at Table 4-3 and observe that the output is HIGH for all four cases when *P* is LOW. *S* is also HIGH when *Q* AND *R* are both HIGH, regardless of the state of *P*. This agrees with the equation.

The AND/OR implementation for this circuit is shown in Figure 4-9(b). (Step 5)

To implement this circuit using the 74HC00 quad two-input NAND chip, we must convert each gate and the INVERTER by substituting their NAND-gate equivalents (per Section 3-12). This is shown in Figure 4-9(c). Clearly, we can eliminate two pairs of double inverters to produce the NAND-gate

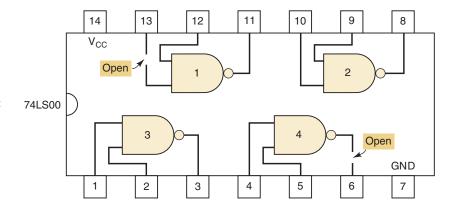

The final wired-up circuit is obtained by connecting two of the NAND gates on the 74HC00 chip. This CMOS chip has the same gate configuration and pin numbers as the TTL 74LS00 chip of Figure 3-31. Figure 4-10 shows the wired-up circuit with pin numbers, including the +5V and GROUND pins. It also includes an output driver transistor and LED to indicate the

implementation shown in Figure 4-9(d).

state of output S.

FIGURE 4-10 Circuit of Figure 4-9(d) implemented using 74HC00 NAND chip.

OUTCOME ASSESSMENT QUESTIONS

- 1. Write the sum-of-products expression for a circuit with four inputs and an output that is to be HIGH only when input *A* is LOW at the same time that exactly two other inputs are LOW.

- 2. Implement the expression of question 1 using all four-input NAND gates. How many are required?

- 3. List the steps of the systematic design process.

# 4-5 KARNAUGH MAP METHOD

### **OUTCOMES**

*Upon completion of this section, you will be able to:*

- Identify "Don't care" conditions and use them in truth tables.

- Use K maps to generate the simplest SOP form from a truth table.

The Karnaugh map (K map) is a graphical tool used to simplify a logic equation or to convert a truth table to its corresponding logic circuit in a simple, orderly process. Although a K map can be used for problems involving any number of input variables, its practical usefulness is limited to five or six variables. The following discussion will be limited to problems with up to four inputs because even five- and six-input problems are too involved and are best done by a computer program.

## **Karnaugh Map Format**

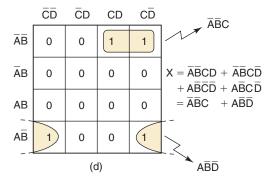

The K map, like a truth table, is a means for showing the relationship between logic inputs and the desired output. Figure 4-11 shows three examples of K maps for two, three, and four variables, together with the corresponding truth tables. These examples illustrate the following important points:

1. The truth table gives the value of output X for each combination of input values. The K map gives the same information in a different

**(**

FIGURE 4-11 Karnaugh maps and truth tables for (a) two, (b) three, and (c) four variables.

| A D \                                                                                                      | 1                                                                                                                                                                         |                                                                                                                                                                        |          |                  | B          | В       | _               |

|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|------------|---------|-----------------|

| 0 0                                                                                                        | $\frac{X}{1} \rightarrow \overline{A}\overline{B}$                                                                                                                        | $\left\{ x = \overline{A}\overline{B} + AB \right\}$                                                                                                                   |          | Ā                | 1          | 0       |                 |

| 1 0 (                                                                                                      |                                                                                                                                                                           | (                                                                                                                                                                      |          | Α                | 0          | 1       |                 |

|                                                                                                            | _                                                                                                                                                                         | (a)                                                                                                                                                                    |          |                  |            |         |                 |

|                                                                                                            | _                                                                                                                                                                         |                                                                                                                                                                        |          |                  | Ē          | С       | _               |

| A B C 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                  | $\frac{X}{1 \to \overline{A}\overline{B}\overline{C}}$                                                                                                                    |                                                                                                                                                                        |          | $\bar{A}\bar{B}$ | 1          | 1       |                 |

| 0 0 1<br>0 1 0<br>0 1 1                                                                                    | $ \begin{array}{c} 1 \to \overline{A}\overline{B}C \\ 1 \to \overline{A}B\overline{C} \\ 0 \end{array} $                                                                  | $\left[X = \overline{A}\overline{B}\overline{C} + \overline{A}\overline{B}C\right]$                                                                                    |          | $\bar{A}B$       | 1          | 0       |                 |

| 1 0 0                                                                                                      | 0                                                                                                                                                                         | $\begin{cases} X = \overline{A}\overline{B}\overline{C} + \overline{A}\overline{B}C \\ + \overline{A}\overline{B}\overline{C} + A\overline{B}\overline{C} \end{cases}$ |          | AB               | 1          | 0       |                 |

| 1 1 0                                                                                                      | $ \begin{array}{c} 1 \to AB\overline{C} \\ 0 \\ \hline \end{array} $                                                                                                      | (b)                                                                                                                                                                    |          | $A\overline{B}$  | 0          | 0       |                 |

|                                                                                                            |                                                                                                                                                                           | (b)                                                                                                                                                                    |          |                  |            |         | •               |

|                                                                                                            |                                                                                                                                                                           |                                                                                                                                                                        |          |                  |            |         |                 |

| A B C D 0 0 0 0                                                                                            | 0                                                                                                                                                                         |                                                                                                                                                                        |          | ĒĒ               | $\bar{C}D$ | CD      | $C\overline{D}$ |

| 0 0 0 0<br>0 0 0 1<br>0 0 1 0                                                                              | $ \begin{array}{c} 0 \\ 1 \to \overline{A}\overline{B}\overline{C}D \\ 0 \end{array} $                                                                                    |                                                                                                                                                                        | ĀĒ       | CD<br>0          | ŌD         | CD<br>0 | CD<br>0         |

| 0 0 0 0<br>0 0 0 1<br>0 0 1 0<br>0 0 1 1<br>0 1 0 0<br>0 1 0 1                                             | $ \begin{array}{c} 0 \\ 1 \to \overline{A}\overline{B}\overline{C}D \\ 0 \\ 0 \end{array} $                                                                               | $\int X = \overline{A}\overline{B}\overline{C}D + \overline{A}B\overline{C}D$                                                                                          | ĀB<br>ĀB |                  |            |         |                 |

| 0 0 0 0<br>0 0 0 1<br>0 0 1 0<br>0 0 1 1<br>0 1 0 0<br>0 1 0 1<br>0 1 1 0<br>0 1 1 1                       | $ \begin{array}{c} 0 \\ 1 \to \overline{A}B\overline{C}D \\ 0 \\ 0 \\ 1 \to \overline{A}B\overline{C}D \\ 0 \\ 0 \end{array} $                                            | $ \left\{ \begin{aligned} X &= \overline{A} \overline{B} \overline{C} D + \overline{A} B \overline{C} D \\ &+ A B \overline{C} D + A B C D \end{aligned} \right\} $    |          | 0                | 1          | 0       | 0               |

| 0 0 0 0<br>0 0 0 1<br>0 0 1 0<br>0 0 1 1<br>0 1 0 0<br>0 1 0 1<br>0 1 1 0                                  | $ \begin{array}{c} 0 \\ 1 \to \overline{A}B\overline{C}D \\ 0 \\ 0 \\ 1 \to \overline{A}B\overline{C}D \\ 0 \end{array} $                                                 | $ \left\{ \begin{aligned} X &= \overline{A} \overline{B} \overline{C} D + \overline{A} B \overline{C} D \\ &+ A B \overline{C} D + A B C D \end{aligned} \right\} $    | ĀB       | 0                | 1          | 0       | 0               |

| 0 0 0 0<br>0 0 0 1<br>0 0 1 0<br>0 0 1 1<br>0 1 0 0<br>0 1 0 1<br>0 1 1 0<br>0 1 1 1<br>1 0 0 0<br>1 0 0 1 | $\begin{array}{c} 0 \\ 1 \rightarrow \overline{A}\overline{B}\overline{C}D \\ 0 \\ 0 \\ 0 \\ 1 \rightarrow \overline{A}B\overline{C}D \\ 0 \\ 0 \\ 0 \\ 0 \\ \end{array}$ | $ \left\{ \begin{aligned} X &= \overline{A} \overline{B} \overline{C} D + \overline{A} B \overline{C} D \\ &+ A B \overline{C} D + A B C D \end{aligned} \right\} $    | ĀB<br>AB | 0 0 0            | 1 1 1      | 0 0 1   | 0 0             |

format. Each case in the truth table corresponds to a square in the K map. For example, in Figure 4-11(a), the A=0, B=0 condition in the truth table corresponds to the  $\overline{AB}$  square in the K map. Because the truth table shows X=1 for this case, a 1 is placed in the  $\overline{AB}$  square in the K map. Similarly, the A=1, B=1 condition in the truth table corresponds to the AB square of the K map. Because X=1 for this case, a 1 is placed in the AB square. All other squares are filled with 0s. This same idea is used in the three- and four-variable maps shown in the figure.

2. The K-map squares are labeled so that horizontally adjacent squares differ only in one variable. For example, the upper left-hand square in the four-variable map is  $\overline{A}\,\overline{B}\,\overline{C}\,\overline{D}$ , while the square immediately to its right is  $\overline{A}\,\overline{B}\,\overline{C}D$  (only the D variable is different). Similarly, vertically adjacent squares differ only in one variable. For example, the upper left-hand square is  $\overline{A}\,\overline{B}\,\overline{C}\,\overline{D}$ , while the square directly below it is  $\overline{A}\,\overline{B}\,\overline{C}\,\overline{D}$  (only the B variable is different).

Note that each square in the top row is considered to be adjacent to a corresponding square in the bottom row. For example, the  $\overline{A}\overline{B}CD$  square in the top row is adjacent to the  $A\overline{B}CD$  square in the bottom

- row because they differ only in the *A* variable. You can think of the top of the map as being wrapped around to touch the bottom of the map. Similarly, squares in the leftmost column are adjacent to corresponding squares in the rightmost column.

- 3. In order for vertically and horizontally adjacent squares to differ in only one variable, the top-to-bottom labeling must be done in the order shown:  $\overline{A}\overline{B}$ ,  $\overline{A}B$ , AB,  $A\overline{B}$ . The same is true of the left-to-right labeling:  $\overline{C}\overline{D}$ ,  $\overline{C}D$ , CD,  $C\overline{D}$ .

- 4. Once a K map has been filled with 0s and 1s, the sum-of-products expression for the output X can be obtained by ORing together those squares that contain a 1. In the three-variable map of Figure 4-11(b), the  $\overline{A}\overline{B}\overline{C}$ ,  $\overline{A}\overline{B}C$ ,  $\overline{A}\overline{B}C$ , and  $AB\overline{C}$  squares contain a 1, so that  $X = \overline{A}\overline{B}\overline{C} + \overline{A}\overline{B}C + \overline{A}\overline{B}\overline{C} + AB\overline{C}$ .

# Looping

The expression for output X can be simplified by properly combining those squares in the K map that contain 1s. The process for combining these 1s is called **looping**.

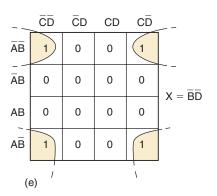

# **Looping Groups of Two (Pairs)**

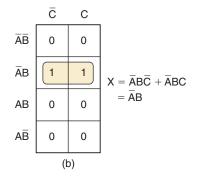

Figure 4-12(a) is the K map for a particular three-variable truth table. This map contains a pair of 1s that are vertically adjacent to each other; the first represents  $\overline{ABC}$ , and the second represents  $AB\overline{C}$ . Note that in these two terms only the A variable appears in both normal and complemented (inverted) form, while B and  $\overline{C}$  remain unchanged. These two terms can be

**FIGURE 4-12** Examples of looping pairs of adjacent 1s.

looped (combined) to give a resultant that eliminates the *A* variable because it appears in both uncomplemented and complemented forms. This is easily proved as follows:

$$X = \overline{A}B\overline{C} + AB\overline{C}$$

$$= B\overline{C}(\overline{A} + A)$$

$$= B\overline{C}(1) = B\overline{C}$$

This same principle holds true for any pair of vertically or horizontally adjacent 1s. Figure 4-12(b) shows an example of two horizontally adjacent 1s. These two can be looped and the C variable eliminated because it appears in both its uncomplemented and complemented forms to give a resultant of  $X = \overline{AB}$ .

Another example is shown in Figure 4-12(c). In a K map, the top row and bottom row of squares are considered to be adjacent. Thus, the two 1s in this map can be looped to provide a resultant of  $\overline{A}\overline{B}\overline{C} + A\overline{B}\overline{C} = \overline{B}\overline{C}$ .

Figure 4-12(d) shows a K map that has two pairs of 1s that can be looped. The two 1s in the top row are horizontally adjacent. The two 1s in the bottom row are also adjacent because, in a K map, the leftmost column and the rightmost column of squares are considered to be adjacent. When the top pair of 1s is looped, the D variable is eliminated (because it appears as both D and  $\overline{D}$ ) to give the term  $\overline{A}\overline{B}C$ . Looping the bottom pair eliminates the C variable to give the term  $A\overline{B}D$ . These two terms are ORed to give the final result for X.

To summarize:

Looping a pair of adjacent 1s in a K map eliminates the variable that appears in complemented and uncomplemented form.

# **Looping Groups of Four (Quads)**

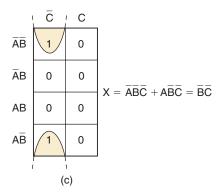

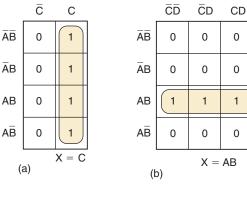

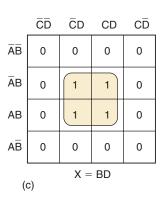

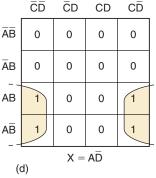

A K map may contain a group of four 1s that are adjacent to each other. This group is called a *quad*. Figure 4-13 shows several examples of quads. In Figure 4-13(a), the four 1s are vertically adjacent and in Figure 4-13(b), they are horizontally adjacent. The K map in Figure 4-13(c) contains four 1s in a square, and they are considered adjacent to each other. The four 1s in Figure 4-13(d) are also adjacent, as are those in Figure 4-13(e), because, as pointed out earlier, the top and bottom rows are considered to be adjacent to each other, as are the leftmost and rightmost columns.

When a quad is looped, the resultant term will contain only the variables that do not change form for all the squares in the quad. For example, in Figure 4-13(a), the four squares that contain a 1 are  $\overline{ABC}$ ,  $\overline{ABC}$ ,  $\overline{ABC}$ , and  $\overline{ABC}$ . Examination of these terms reveals that only the variable C remains unchanged (both A and B appear in complemented and uncomplemented form). Thus, the resultant expression for X is simply X = C. This can be proved as follows:

$$X = \overline{A}\overline{B}C + \overline{A}BC + ABC + A\overline{B}C$$

$$= \overline{A}C(\overline{B} + B) + AC(B + \overline{B})$$

$$= \overline{A}C + AC$$

$$= C(\overline{A} + A) = C$$

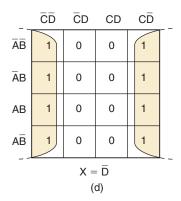

As another example, consider Figure 4-13(d), where the four squares containing 1s are  $AB\overline{C}\overline{D}$ ,  $A\overline{B}\overline{C}\overline{D}$ ,  $ABC\overline{D}$ , and  $A\overline{B}C\overline{D}$ . Examination of these

FIGURE 4-13 Examples of looping groups of four 1s (quads).

terms indicates that only the variables A and  $\overline{D}$  remain unchanged, so that the simplified expression for *X* is

$C\overline{D}$

0

1

0

0

0

0

$$X = A\overline{D}$$

This can be proved in the same manner that was used above. The reader should check each of the other cases in Figure 4-13 to verify the indicated expressions for X.

To summarize:

Looping a quad of adjacent 1s eliminates the two variables that appear in both complemented and uncomplemented form.

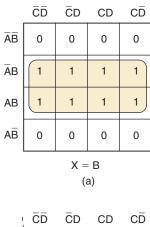

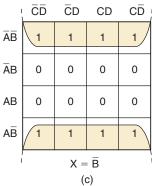

# **Looping Groups of Eight (Octets)**

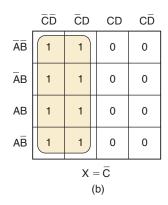

A group of eight 1s that are adjacent to one another is called an octet. Several examples of octets are shown in Figure 4-14. When an octet is looped in a four-variable map, three of the four variables are eliminated because only one variable remains unchanged. For example, examination of the eight looped squares in Figure 4-14(a) shows that only the variable B is in the same form for all eight squares: the other variables appear in complemented and uncomplemented form. Thus, for this map, X = B. The reader can verify the results for the other examples in Figure 4-14.

To summarize:

Looping an octet of adjacent 1s eliminates the three variables that appear in both complemented and uncomplemented form.

**FIGURE 4-14** Examples of looping groups of eight 1s (octets).

# **Complete Simplification Process**

We have seen how looping of pairs, quads, and octets on a K map can be used to obtain a simplified expression. We can summarize the rule for loops of *any* size:

When a variable appears in both complemented and uncomplemented form within a loop, that variable is eliminated from the expression. Variables that are the same for all squares of the loop must appear in the final expression.

It should be clear that a larger loop of 1s eliminates more variables. To be exact, a loop of two eliminates one variable, a loop of four eliminates two variables, and a loop of eight eliminates three. This principle will now be used to obtain a simplified logic expression from a K map that contains any combination of 1s and 0s.

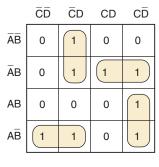

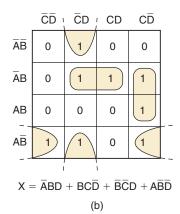

The procedure will first be outlined and then applied to several examples. The steps below are followed in using the K-map method for simplifying a Boolean expression:

- Step 1 Construct the K map and place 1s in those squares corresponding to the 1s in the truth table. Place 0s in the other squares.

- **Step 2** Examine the map for adjacent 1s and loop those 1s that are *not* adjacent to any other 1s. These are called *isolated* 1s.

- Step 3 Next, look for those 1s that are adjacent to only one other 1. Loop *any* pair containing such a 1.

- **Step 4** Loop any octet even if it contains some 1s that have already been looped.

- Step 5 Loop any quad that contains one or more 1s that have not already been looped, *making sure to use the minimum number of loops*.

$\bigoplus$

- **Step 6** Loop any pairs necessary to include any 1s that have not yet been looped, *making sure to use the minimum number of loops*.

- **Step 7** Form the OR sum of all the terms generated by each loop.

These steps will be followed exactly and referred to in the following examples. In each case, the resulting logic expression will be in its simplest sum-of-products form.

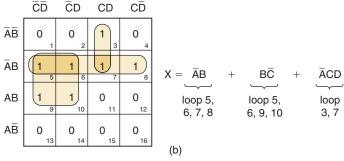

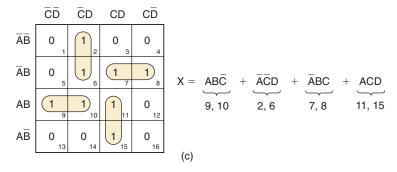

# **EXAMPLE 4-10**

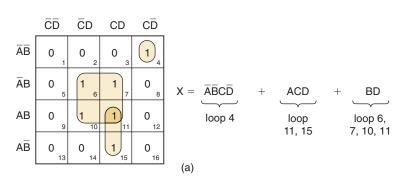

Figure 4-15(a) shows the K map for a four-variable problem. We will assume that Step 1 (construct a K map from the problem truth table) has been completed. The squares are numbered for convenience in identifying each loop. Use steps 2–7 of the simplification process to reduce the K map to an SOP expression.

**FIGURE 4-15** Examples 4-10 to 4-12.

#### **Solution**

- **Step 2** Square 4 is the only square containing a 1 that is not adjacent to any other 1. It is looped and is referred to as loop 4.

- **Step 3** Square 15 is adjacent *only* to square 11. This pair is looped and referred to as loop 11, 15.

- Step 4 There are no octets.

- **Step 5** Squares 6, 7, 10, and 11 form a quad. This quad is looped (loop 6, 7, 10, 11). Note that square 11 is used again, even though it was part of loop 11, 15.

- **Step 6** All 1s have already been looped.

- **Step 7** Each loop generates a term in the expression for *X*. Loop 4 is simply  $\overline{ABCD}$ . Loop 11, 15 is ACD (the *B* variable is eliminated). Loop 6, 7, 10, 11 is BD (*A* and *C* are eliminated).

### **EXAMPLE 4-11**

Consider the K map in Figure 4-15(b). Once again, we can assume that step 1 has already been performed. Simplify.

#### **Solution**

- Step 2 There are no isolated 1s.

- **Step 3** The 1 in square 3 is adjacent *only* to the 1 in square 7. Looping this pair (loop 3, 7) produces the term  $\overline{A}CD$ .

- **Step 4** There are no octets.

- **Step 5** There are two quads. Squares 5, 6, 7, and 8 form one quad. Looping this quad produces the term  $\overline{A}B$ . The second quad is made up of squares 5, 6, 9, and 10. This quad is looped because it contains two squares that have not been looped previously. Looping this quad produces  $B\overline{C}$ .

- Step 6 All 1s have already been looped.

- **Step 7** The terms generated by the three loops are ORed together to obtain the expression for *X*.

#### **EXAMPLE 4-12**

Consider the K map in Figure 4-15(c). Simplify.

# Solution

- **Step 2** There are no isolated 1s.

- **Step 3** The 1 in square 2 is adjacent only to the 1 in square 6. This pair is looped to produce  $\overline{ACD}$ . Similarly, square 9 is adjacent only to square 10. Looping this pair produces  $AB\overline{C}$ . Likewise, loop 7, 8 and loop 11, 15 produce the terms  $\overline{ABC}$  and ACD, respectively.

- **Step 4** There are no octets.

- **Step 5** There is one quad formed by squares 6, 7, 10, and 11. This quad, however, is *not* looped because all the 1s in the quad have been included in other loops.

- **Step 6** All 1s have already been looped.

- **Step 7** The expression for *X* is shown in the figure.

## **EXAMPLE 4-13**

Consider the two K map loopings in Figure 4-16. Is one better than the other?

#### **Solution**

- **Step 2** There are no isolated 1s.

- **Step 3** There are no 1s that are adjacent to only one other 1.

- **Step 4** There are no octets.

**FIGURE 4-16** The same K map with two equally good solutions.

$$X = \overline{A}\overline{C}D + \overline{A}BC + A\overline{B}\overline{C} + AC\overline{D}$$

(a)

Step 5 There are no quads.

Step 6 and 7 There are many possible pairs. The looping must use the minimum number of loops to account for all the 1s. For this map, there are *two* possible loopings, which require only four looped pairs. Figure 4-16(a) shows one solution and its resultant expression. Figure 4-16(b) shows the other. Note that both expressions are of the same complexity, and so neither is better than the other.

# Filling a K Map from an Output Expression

When the desired output is presented as a Boolean expression instead of a truth table, the K map can be filled by using the following steps:

- 1. Get the expression into SOP form if it is not already in that form.

- 2. For each product term in the SOP expression, place a 1 in each K-map square whose label contains the same combination of input variables. Place a 0 in all other squares.

The following example illustrates this procedure.

# **EXAMPLE 4-14**

Use a K map to simplify  $y = \overline{C}(\overline{A}\overline{B}\overline{D} + D) + A\overline{B}C + \overline{D}$ .

#### **Solution**

- 1. Multiply out the first term to get  $y = \overline{A}\overline{B}\overline{C}\overline{D} + \overline{C}D + A\overline{B}C + \overline{D}$ , which is now in SOP form.

- 2. For the  $\overline{AB}\,\overline{CD}$  term, simply put a 1 in the  $\overline{AB}\,\overline{CD}$  square of the K map (Figure 4-17). For the  $\overline{CD}$  term, place a 1 in all squares with  $\overline{CD}$  in their labels, that is,  $\overline{AB}\,\overline{CD}$ ,  $\overline{AB}\,\overline{CD}$ ,  $\overline{AB}\,\overline{CD}$ ,  $\overline{AB}\,\overline{CD}$ . For the  $\overline{AB}\,\overline{CD}$  term, place a 1 in all squares that have an  $\overline{AB}\,\overline{CD}$  in their labels, that is,  $\overline{AB}\,\overline{CD}$ ,  $\overline{AB}\,\overline{CD}$ . For the  $\overline{D}$  term, place a 1 in all squares that have a  $\overline{D}$  in their labels, that is, all squares in the leftmost and rightmost columns.

The K map is now filled and can be looped for simplification. Verify that proper looping produces  $y = A\overline{B} + \overline{C} + \overline{D}$ .

**FIGURE 4-17** Example 4-14.

### **Don't-Care Conditions**

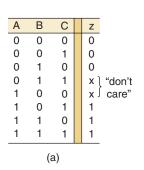

Some logic circuits can be designed so that there are certain input conditions for which there are no specified output levels, usually because these input conditions will never occur. In other words, there will be certain combinations of input levels where we "don't care" whether the output is 1 or 0. This is illustrated in the truth table of Figure 4-18(a).

FIGURE 4-18 "Don'tcare" conditions should be changed to 0 or 1 to produce K-map looping that yields the simplest expression.

Here the output z is not specified as either 0 or 1 for the conditions A, B, C = 1, 0, 0 and A, B, C = 0, 1, 1. Instead, an x is shown for these conditions. The x represents the **don't-care condition**. A don't-care condition can come about for several reasons, the most common being that in some situations certain input combinations can never occur, and so there is no specified output for these conditions.

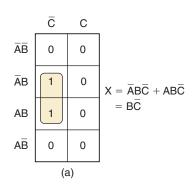

A circuit designer is free to make the output for any don't-care condition either a 0 or a 1 to produce the simplest output expression. For example, the K map for this truth table is shown in Figure 4-18(b) with an x placed in the  $A\overline{B}\overline{C}$  and  $\overline{ABC}$  squares. The designer here would be wise to change the x in the  $A\overline{B}\overline{C}$  square to a 1 and the x in the  $\overline{ABC}$  square to a 0 because this would produce a quad that can be looped to produce z=A, as shown in Figure 4-18(c).

Whenever don't-care conditions occur, we must decide which *x* to change to 0 and which to 1 to produce the best K-map looping (i.e., the simplest expression). This decision is not always an easy one. Several end-of-chapter problems will provide practice in dealing with don't-care cases. Here's another example.

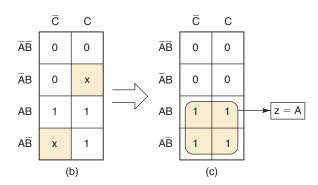

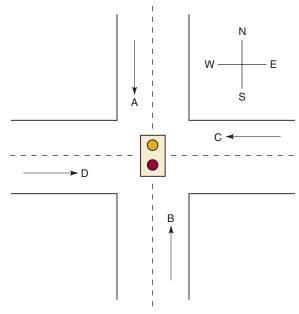

### **EXAMPLE 4-15**

Let's design a logic circuit that controls an elevator door in a three-story building. The circuit in Figure 4-19(a) has four inputs. M is a logic signal that indicates when the elevator is moving (M=1) or stopped (M=0). F1, F2, and F3 are floor indicator signals that are normally LOW, and they go HIGH only when the elevator is positioned at the level of that particular

**FIGURE 4-19** Example 4-15.

(a)

M F1 F2 F3

0 0 0 0

OPEN

0

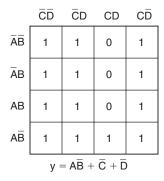

|       | F2 F3 | F2 F3 | F2 F3 | F2 F3 |  |  |  |

|-------|-------|-------|-------|-------|--|--|--|

| ∏ F1  | 0     | 1     | Х     | 1     |  |  |  |

| M̄ F1 | 1     | Х     | Х     | Х     |  |  |  |

| M F1  | 0     | Х     | Х     | Х     |  |  |  |

| M F1  | 0     | 0     | Х     | 0     |  |  |  |

| (c)   |       |       |       |       |  |  |  |

floor. For example, when the elevator is lined up level with the second floor, F2 = 1 and F1 = F3 = 0. The circuit output is the *OPEN* signal, which is normally LOW and will go HIGH when the elevator door is to be opened.

We can fill in the truth table for the OPEN output [Figure 4-19(b)] as follows:

- 1. Because the elevator cannot be lined up with more than one floor at a time, only one of the floor inputs can be HIGH at any given time. This means that all those cases in the truth table where more than one floor input is a 1 are don't-care conditions. We can place an *x* in the *OPEN* output column for those eight cases where more than one *F* input is 1.

- 2. Looking at the other eight cases, when M=1 the elevator is moving, so OPEN must be a 0 because we do not want the elevator door to open. When M=0 (elevator stopped) we want OPEN=1 provided that one of the floor inputs is 1. When M=0 and all floor inputs are 0, the elevator is stopped but is not properly lined up with any floor, so we want OPEN=0 to keep the door closed.

The truth table is now complete and we can transfer its information to the K map in Figure 4-19(c). The map has only three 1s, but it has eight don't-cares. By changing four of these don't-care squares to 1s, we can produce quad loopings that contain the original 1s [Figure 4-19(d)]. This is the best we can do as far as minimizing the output expression. Verify that the loopings produce the *OPEN* output expression shown.

# **Summary**

The K-map process has several advantages over the algebraic method. K mapping is a more orderly process with well-defined steps compared with the trial-and-error process sometimes used in algebraic simplification. K mapping usually requires fewer steps, especially for expressions containing many terms, and it always produces a minimum expression.

Nevertheless, some instructors prefer the algebraic method because it requires a thorough knowledge of Boolean algebra and is not simply a mechanical procedure. Each method has its advantages, and although most logic designers are adept at both, being proficient in one method is all that is necessary to produce acceptable results.

There are other, more complex techniques that designers use to minimize logic circuits with more than four inputs. These techniques are especially suited for circuits with large numbers of inputs where algebraic and K-mapping methods are not feasible. Most of these techniques can be translated into a computer program that will perform the minimization from input data that supply the truth table or the unsimplified expression.

OUTCOME ASSESSMENT QUESTIONS

- 1. Use K mapping to obtain the expression of Example 4-7.

- 2. Use K mapping to obtain the expression of Example 4-8. This should emphasize the advantage of K mapping for expressions containing many terms.

- 3. Obtain the expression of Example 4-9 using a K map.

- 4. What is a don't-care condition?

# 4-6 EXCLUSIVE-OR AND EXCLUSIVE-NOR CIRCUITS

### **OUTCOMES**

Upon completion of this section, you will be able to:

- Define the exclusive-OR and exclusive-NOR logic functions.

- Write Boolean equations using the XOR/XNOR functions.

- Draw the logic symbol for the XOR/XNOR functions.

- Write a truth table describing the XOR/XNOR functions.

- Draw a timing diagram that demonstrates the XOR/XNOR functions.

- Use any of the above methods to infer the correct output of a logic circuit based on its input.

Two special logic circuits that occur quite often in digital systems are the *exclusive-OR* and *exclusive-NOR* circuits.

# **Exclusive-OR**

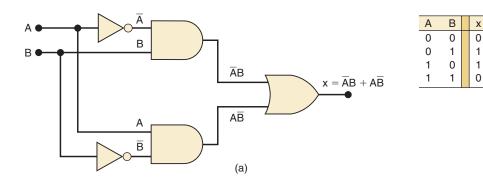

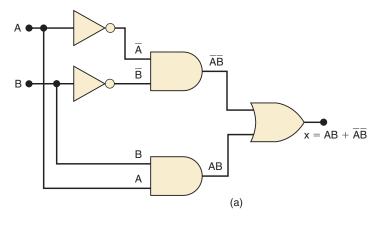

Consider the logic circuit of Figure 4-20(a). The output expression of this circuit is

$$x = \overline{A}B + A\overline{B}$$

**FIGURE 4-20**

(a) Exclusive-OR circuit and truth table; (b) traditional XOR gate symbol.

The accompanying truth table shows that x=1 for two cases: A=0, B=1 (the  $\overline{AB}$  term) and A=1, B=0 (the  $A\overline{B}$  term). In other words:

This circuit produces a HIGH output whenever the two inputs are at opposite levels.

This is the exclusive-OR circuit, which will hereafter be abbreviated XOR.

This particular combination of logic gates occurs quite often and is very useful in certain applications. In fact, the XOR circuit has been given a symbol of its own, shown in Figure 4-20(b). This symbol is assumed to contain all of the logic contained in the XOR circuit and therefore has the same logic expression and truth table. This XOR circuit is commonly referred to as an XOR *gate*, and we consider it as another type of logic gate.

An XOR gate has only *two* inputs; there are no three-input or four-input XOR gates. The two inputs are combined so that  $x = \overline{AB} + A\overline{B}$ . A shorthand way that is sometimes used to indicate the XOR output expression is

$$x = A \oplus B$$

where the symbol  $\oplus$  represents the XOR gate operation.

The characteristics of an XOR gate are summarized as follows:

1. It has only two inputs and its output is

$$x = \overline{A}B + A\overline{B} = A \oplus B$$

2. Its output is *HIGH* only when the two inputs are at *different* levels.

Several ICs are available that contain XOR gates. Those listed below are *quad* XOR chips containing four XOR gates.

| 74LS86 | Quad XOR (TTL family)      |

|--------|----------------------------|

| 74C86  | Quad XOR (CMOS family)     |

| 74HC86 | Quad XOR (high-speed CMOS) |

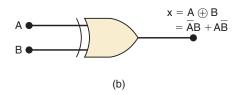

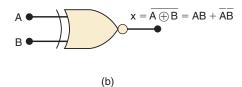

### **Exclusive-NOR**

The exclusive-NOR circuit (abbreviated XNOR) operates completely opposite to the XOR circuit. Figure 4-21(a) shows an XNOR circuit and its accompanying truth table. The output expression is

$$x = AB + \overline{A}\overline{B}$$

which indicates along with the truth table that x will be 1 for two cases: A = B = 1 (the AB term) and A = B = 0 (the  $\overline{AB}$  term). In other words:

The XNOR produces a HIGH output whenever the two inputs are at the same level.

It should be apparent that the output of the XNOR circuit is the exact inverse of the output of the XOR circuit. The traditional symbol for an XNOR gate is obtained by simply adding a small circle at the output of the XOR symbol [Figure 4-21(b)].

#### **FIGURE 4-21**

(a) Exclusive-NOR circuit;

(b) traditional symbol for XNOR gate.

| A B x 0 0 1             |

|-------------------------|

|                         |

| A B x 0 0 1 0 1 0       |

| 0 1 0<br>1 0 0<br>1 1 1 |

| 1 1 1                   |

The XNOR gate also has only two inputs, and it combines them so that its output is

$$x = AB + \overline{A}\overline{B}$$

A shorthand way to indicate the output expression of the XNOR is

$$x = \overline{A \oplus B}$$

which is simply the inverse of the XOR operation. The XNOR gate is summarized as follows:

1. It has only two inputs and its output is

$$x = AB + \overline{A}\overline{B} = \overline{A \oplus B}$$

2. Its output is HIGH only when the two inputs are at the same level.

Several ICs are available that contain XNOR gates. Those listed below are quad XNOR chips containing four XNOR gates.

74LS266 Quad XNOR (TTL family) 74C266 Quad XNOR (CMOS)

74HC266 Quad XNOR (high-speed CMOS)

Each of these XNOR chips, however, has special output circuitry that limits its use to special types of applications. Very often, a logic designer will obtain the XNOR function simply by connecting the output of an XOR to an INVERTER.

### **EXAMPLE 4-16**

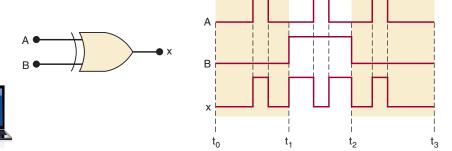

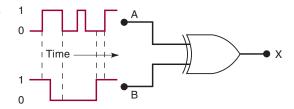

Determine the output waveform for the input waveforms given in Figure 4-22.

**FIGURE 4-22** Example 4-16.

# **Solution**

The output waveform is obtained using the fact that the XOR output will go HIGH only when its inputs are at different levels. The resulting output waveform reveals several interesting points:

- 1. The x waveform matches the A input waveform during those time intervals when B=0. This occurs during the time intervals  $t_0$  to  $t_1$  and  $t_2$  to  $t_3$ .

- 2. The *x* waveform is the *inverse* of the *A* input waveform during those time intervals when B = 1. This occurs during the interval  $t_1$  to  $t_2$ .

- 3. These observations show that an XOR gate can be used as a *controlled INVERTER*; that is, one of its inputs can be used to control whether or not the signal at the other input will be inverted. This property will be useful in certain applications.

### **EXAMPLE 4-17**

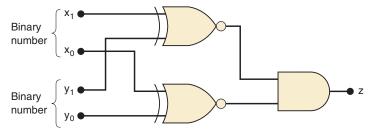

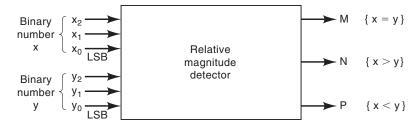

The notation  $x_1x_0$  represents a two-bit binary number that can have any value (00, 01, 10, or 11); for example, when  $x_1 = 1$  and  $x_0 = 0$ , the binary number is 10, and so on. Similarly,  $y_1y_0$  represents another two-bit binary number. Design a logic circuit, using  $x_1$ ,  $x_0$ ,  $y_1$ , and  $y_0$  inputs, whose output will be HIGH only when the two binary numbers  $x_1x_0$  and  $y_1y_0$  are *equal*.

#### **Solution**

The first step is to construct a truth table for the 16 input conditions (Table 4-4). The output z must be HIGH whenever the  $x_1x_0$  values match the  $y_1y_0$  values;

**TABLE 4-4**

| <i>x</i> <sub>1</sub> | <i>x</i> <sub>0</sub> | <i>y</i> <sub>1</sub> | <b>y</b> 0 | z (Output) |

|-----------------------|-----------------------|-----------------------|------------|------------|

| 0                     | 0                     | 0                     | 0          | 1          |

| 0                     | 0                     | 0                     | 1          | 0          |

| 0                     | 0                     | 1                     | 0          | 0          |

| 0                     | 0                     | 1                     | 1          | 0          |

| 0                     | 1                     | 0                     | 0          | 0          |

| 0                     | 1                     | 0                     | 1          | 1          |

| 0                     | 1                     | 1                     | 0          | 0          |

| 0                     | 1                     | 1                     | 1          | 0          |

| 1                     | 0                     | 0                     | 0          | 0          |

| 1                     | 0                     | 0                     | 1          | 0          |

| 1                     | 0                     | 1                     | 0          | 1          |

| 1                     | 0                     | 1                     | 1          | 0          |

| 1                     | 1                     | 0                     | 0          | 0          |

| 1                     | 1                     | 0                     | 1          | 0          |

| 1                     | 1                     | 1                     | 0          | 0          |

| 1                     | 1                     | 1                     | 1          | 1          |

**FIGURE 4-23** Circuit for detecting equality of two two-bit binary numbers.

that is, whenever  $x_1=y_1$  and  $x_0=y_0$ . The table shows that there are four such cases. We could now continue with the normal procedure, which would be to obtain a sum-of-products expression for z, attempt to simplify it, and then implement the result. However, the nature of this problem makes it ideally suited for implementation using XNOR gates, and a little thought will produce a simple solution with minimum work. Refer to Figure 4-23; in this logic diagram,  $x_1$  and  $y_1$  are fed to one XNOR gate, and  $x_0$  and  $y_0$  are fed to another XNOR gate. The output of each XNOR will be HIGH only when its inputs are equal. Thus, for  $x_0=y_0$  and  $x_1=y_1$ , both XNOR outputs will be HIGH. This is the condition we are looking for because it means that the two two-bit numbers are equal. The AND gate output will be HIGH only for this case, thereby producing the desired output.

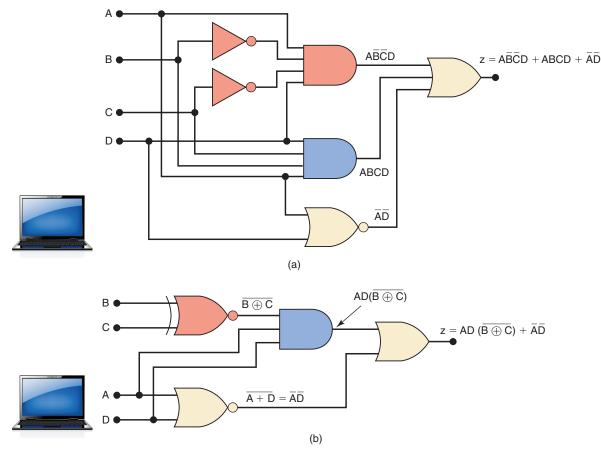

# **EXAMPLE 4-18**

When simplifying the expression for the output of a combinational logic circuit, you may encounter the XOR or XNOR operations as you are factoring. This will often lead to the use of XOR or XNOR gates in the implementation of the final circuit. To illustrate, simplify the circuit of Figure 4-24(a).

#### **Solution**

The unsimplified expression for the circuit is obtained as

$$z = ABCD + A\overline{B}\,\overline{C}D + \overline{A}\,\overline{D}$$

**FIGURE 4-24** Example 4-18, showing how an XNOR gate may be used to simplify circuit implementation.

We can factor *AD* from the first two terms:

$$z = AD(BC + \overline{B}\overline{C}) + \overline{A}\overline{D}$$

At first glance, you might think that the expression in parentheses can be replaced by 1. But that would be true only if it were  $BC + \overline{BC}$ . You should recognize the expression in parentheses as the XNOR combination of B and C. This fact can be used to reimplement the circuit as shown in Figure 4-24(b). This circuit is much simpler than the original because it uses gates with fewer inputs and two INVERTERs have been eliminated.

OUTCOME ASSESSMENT QUESTIONS

- 1. Use Boolean algebra to prove that the XNOR output expression is the exact inverse of the XOR output expression.

- 2. What is the output of an XNOR gate when a logic signal and its exact inverse are connected to its inputs?

- 3. A logic designer needs an INVERTER, and all that is available is one XOR gate from a 74HC86 chip. Does he need another chip?

# 4-7 PARITY GENERATOR AND CHECKER

# **OUTCOMES**

Upon completion of this section, you will be able to:

- Apply XOR gates to make a parity generator.

- Apply XOR gates to make a parity checker.

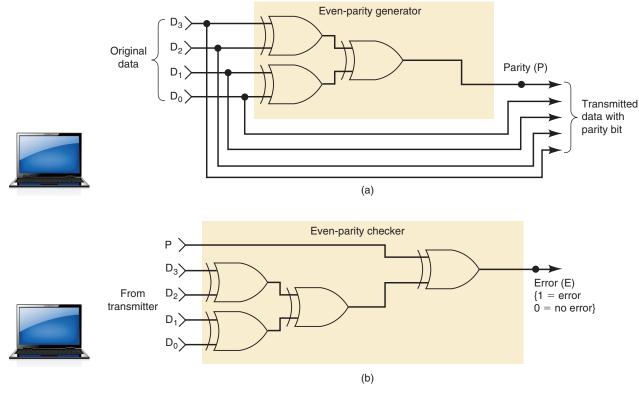

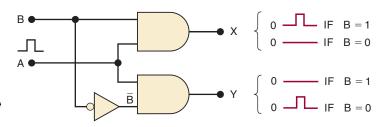

In Chapter 2, we saw that a transmitter can attach a parity bit to a set of data bits before transmitting the data bits to a receiver. We also saw how this allows the receiver to detect any single-bit errors that may have occurred during the transmission. Figure 4-25 shows an example of one type of logic circuitry that is used for **parity generation** and **parity checking**. This particular example uses a group of four bits as the data to be transmitted, and it uses an even-parity bit. It can be readily adapted to use odd parity and any number of bits.

**FIGURE 4-25** XOR gates used to implement (a) the parity generator and (b) the parity checker for an even-parity system.

In Figure 4-25(a), the set of data to be transmitted is applied to the parity-generator circuit, which produces the even-parity bit, P, at its output. This parity bit is transmitted to the receiver along with the original data bits, making a total of five bits. In Figure 4-25(b), these five bits (data + parity) enter the receiver's parity-checker circuit, which produces an error output, E, that indicates whether or not a single-bit error has occurred.

It should not be too surprising that both of these circuits employ XOR gates when we consider that a single XOR gate operates so that it produces a 1 output if an odd number of its inputs are 1, and a 0 output if an even number of its inputs are 1.

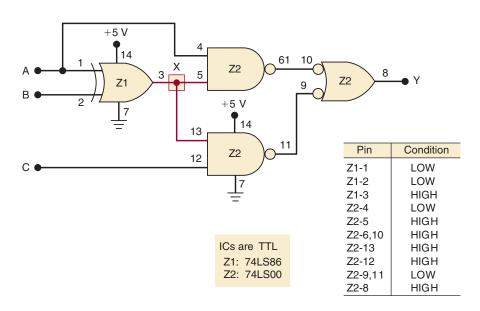

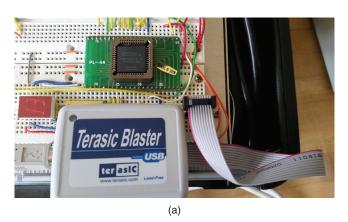

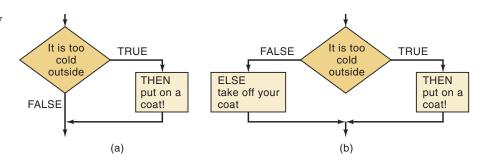

### **EXAMPLE 4-19**