# Combinational Logic Design with Verilog

ECE 152A – Winter 2012

## Reading Assignment

#### Brown and Vranesic

2 Introduction to Logic Circuits

- 2.10 Introduction to Verilog

- 2.10.1 Structural Specification of Logic Circuits

- 2.10.2 Behavioral Specification of Logic Circuits

- □ 2.10.3 How *Not* to Write Verilog Code

## Reading Assignment

#### Brown and Vranesic (cont) <u>1st edition only!</u>

- 4 Optimized Implementation of Logic Functions

- 4.12 CAD Tools

- □ 4.12.1 Logic Synthesis and Optimization

- 4.12.2 Physical Design

- □ 4.12.3 Timing Simulation

- □ 4.12.4 Summary of Design Flow

- □ 4.12.5 Examples of Circuits Synthesized from Verilog Code

## Programmable Logic

Provides low cost and flexibility in a design

- Replace multiple discrete gates with single device

- Logical design can be changed by reprogramming the device

- No change in board design

- Logical design can be changed even after the part has been soldered onto the circuit board in modern, In-system programmable device

- Inventory can focus on one part

- Multiple uses of same device

## Programmable Logic

#### Evolution of Programmable Logic

- Both in time and complexity

- ROM's and RAM's

- Not strictly programmable logic, but useful in implementing combinational logic and state machines

- PAL's

- PAL's Programmable Array Logic

- PLA's Programmable Logic Array

- GAL's Generic Logic Array

## Programmable Logic

#### PLD's

- Programmable Logic Device

- PLDs are (in general) advanced PALs

- CPLD's

- Complex Programmable Logic Device

Multiple PLDs on a single chip

- FPGA's

- Field Programmable Gate Array

# Design Entry

- In previous examples, design entry is schematic based

- TTL implementation using standard, discrete integrated circuits

- PLD implementation using library of primitive elements

- Code based design entry uses a hardware description language (HDL) for design entry

- Code is synthesized and implemented on a PLD

# Verilog Design

Structural Verilog

- Looks like the gate level implementation

- Specify gates and interconnection

- Text form of schematic

- Referred to as "netlist"

- Allows for "bottom up" design

- Begin with primitives, instantiate in larger blocks

# Verilog Design

#### RTL (Register Transfer Level) Verilog

- Allows for "top down" design

- No gate structure or interconnection specified

- Synthesizable code (by definition)

- Emphasis on synthesis, not simulation

- vs. high level behavioral code and test benches

- No timing specified in code

- No initialization specified in code

- Timing, stimulus, initialization, etc. generated in testbench (later)

## Half Adder - Structural Verilog Design

- Recall Half Adder description from schematic based design example

- Operation

- Truth table

- Circuit

- Graphical symbol

Modules are the basic unit of Verilog models

Functional Description

Unambiguously describes module's operation

□ Functional, i.e., without timing information

Input, Output and Bidirectional ports for interfaces

May include instantiations of other modules

Allows building of hierarchy

Module declaration

- □ module ADD\_HALF (s,c,x,y);

- Parameter list is I/O Ports

- Port declaration

#### Can be input, output or inout (bidirectional)

- <u>output s,c;</u>

- input x,y;

#### Declare nodes as wires or reg

- Wires assigned to declaratively

- Reg assigned to procedurally

- More on this later

- In a combinational circuit, all nodes can, but don't have to be, declared wires

- Depends on how code is written

- Node defaults to wire if not declared otherwise

- wire s,c,x,y;

#### Gates and interconnection

- $\Box \underline{\text{xor } G1(s,x,y)};$

- and G2(c,x,y);

- Verilog gate level primitive

- Gate name

- Internal (local) name

- Instance name

- Parameter list

- Output port, input port, input port...

## Gate Instantiation

#### Verilog Gates

Note: *notif* and *bufif* are

tri-state gates

| Table A.2 | Verilog gates.                            |                                                 |

|-----------|-------------------------------------------|-------------------------------------------------|

| Name      | Description                               | Usage                                           |

| and       | $f = (a \cdot b \cdot \cdots)$            | and (f, a, b,)                                  |

| nand      | $f = \overline{(a \cdot b \cdot \cdots)}$ | <b>nand</b> ( <i>f</i> , <i>a</i> , <i>b</i> ,) |

| or        | $f = (a + b + \cdots)$                    | <b>or</b> ( <i>f</i> , <i>a</i> , <i>b</i> ,)   |

| nor       | $f = \overline{(a+b+\cdots)}$             | <b>nor</b> $(f, a, b,)$                         |

| xor       | $f = (a \oplus b \oplus \cdots)$          | <b>xor</b> $(f, a, b,)$                         |

| xnor      | $f = (a \odot b \odot \cdots)$            | <b>xnor</b> $(f, a, b,)$                        |

| not       | $f = \overline{a}$                        | not $(f, a)$                                    |

| buf       | f = a                                     | <b>buf</b> ( <i>f</i> , <i>a</i> )              |

| notif0    | $f = (!e ? \overline{a} : 'bz)$           | <b>notif0</b> $(f, a, e)$                       |

| notif1    | $f = (e ? \overline{a} : bz)$             | notif1 $(f, a, e)$                              |

| bufif0    | f = (!e ? a : 'bz)                        | <b>bufif0</b> $(f, a, e)$                       |

| bufif1    | f = (e ? a : 'bz)                         | <b>bufif1</b> $(f, a, e)$                       |

|           |                                           |                                                 |

# Close the module definition with <u>endmodule</u> Comments begin with //

## Half Adder - Structural Verilog Design

module ADD\_HALF (s,c,x,y);

output s,c; input x,y;

wire s,c,x,y;

// this line is optional since nodes default to wires

xor G1 (s,x,y); // instantiation of XOR gate and G2 (c,x,y); // instantiation of AND gate

endmodule

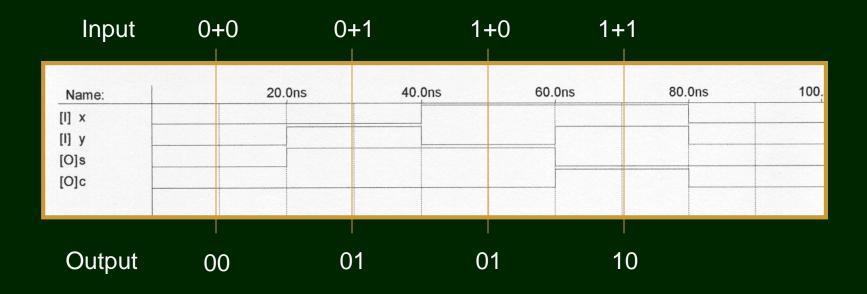

# Half Adder – PLD Implementation

#### Functional Simulation

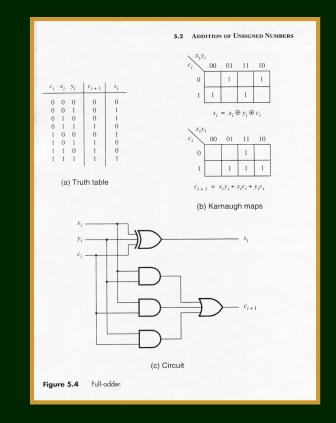

## Full Adder – Structural Verilog Design

- Recall Full Adder description from schematic based design example

- Truth table

- Karnaugh maps

- Circuit

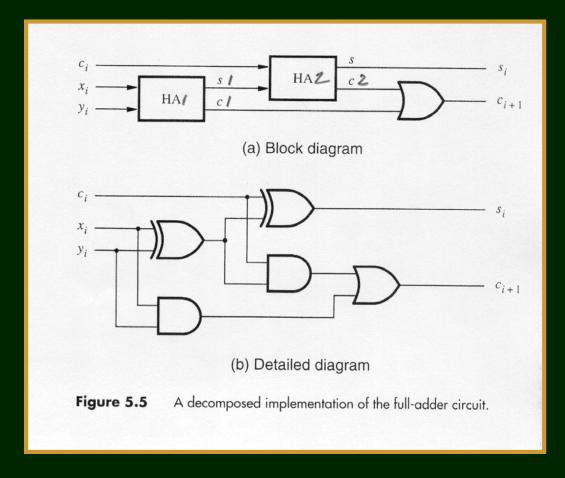

## Full Adder from 2 Half Adders

# Full Adder – Structural Verilog Design

module ADD\_FULL (s,cout,x,y,cin);

output s,cout; input x,y,cin;

//internal nodes also declared as wires

wire cin,x,y,s,cout,s1,c1,c2;

ADD\_HALF HA1(s1,c1,x,y); ADD\_HALF HA2(s,c2,cin,s1); or (cout,c1,c2);

endmodule

January 30, 2012

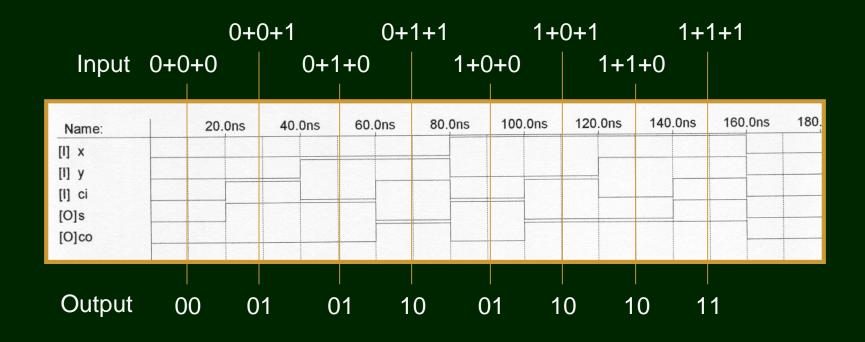

# Full Adder – PLD Implementation

#### Functional Simulation

## Verilog Operators

- The Verilog language includes a large number of logical and arithmetic operators

- Bit length column indicates width of result

| Category    | Examples                                                                                                              | Bit Length               |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------|--|

| Bitwise     | $ \begin{array}{ccc} \sim A, & +A, & -A \\ A \& B, & A \mid B, & A \sim^{\wedge} B, & A \wedge^{\sim} B \end{array} $ | L(A)<br>MAX (L(A), L(B)) |  |

| Logical     | $A, A \& B, A \parallel B$                                                                                            | 1 bit                    |  |

| Reduction   | &A, $\sim$ &A, $ A, \sim  A, ^{\wedge} \sim A, \sim^{\wedge} A$                                                       | 1 bit                    |  |

| Relational  | A == B, A! = B, A > B, A < B<br>A >= B, A <= B<br>A === B, A! == B                                                    | 1 bit                    |  |

| Arithmetic  | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                  | MAX (L(A), L(B))         |  |

| Shift       | A << B, A >> B                                                                                                        | L(A)                     |  |

| Concatenate | $\{A,\ldots,B\}$                                                                                                      | $L(A) + \cdots + L(B)$   |  |

| Replication | ( <i>B</i> { <i>A</i> )}                                                                                              | B * L(A)                 |  |

| Condition   | A ? B : C                                                                                                             | MAX (L(B), L(C)          |  |

#### Behavioral Specification of Logic Circuits

#### Continuous Assignment Operator

- $\square \underline{assign sum} = a \land b;$

- "Assign" to a wire (generated declaratively)

- Equivalent to

- $\Box \underline{\text{xor (sum,a,b)}};$

- Continuous and concurrent with other wire assignment operations

- If a or b changes, sum changes accordingly

- All wire assignment operations occur concurrently

- Order not specified (or possible)

# Full Adder from Logical Operations

module ADD\_FULL\_RTL (sum,cout,x,y,cin);

output sum,cout; input x,y,cin;

//declaration for continuous assignment

wire cin,x,y,sum,cout;

//logical assignment

assign sum = x ^ y ^ cin;

assign cout = x & y | x & cin | y & cin;

endmodule

#### Full Adder from Arithmetic Operations

module ADD\_FULL\_RTL (sum,cout,x,y,cin);

output sum,cout; input x,y,cin;

//declaration for continuous assignment

wire cin,x,y,sum,cout;

// concatenation operator and addition

assign {cout, sum} = x + y + cin;

endmodule

January 30, 2012

## Procedural Verilog Statements

#### Recall:

- Wires assigned to declaratively

- Continuous / concurrent assignment

- Reg "variables" assigned to procedurally

- Value is "registered" until next procedural assignment

- Continuous assignment (wires) occurs immediately on input change

- Enables clocked (synchronous) timing

## Procedural Verilog Statements

#### The "always" block

Syntax is "always at the occurrence (@) of any event on the sensitivity list, execute the statements inside the block (in order)"

> <u>always @ (x or y or cin)</u>  $\{\underline{\text{cout, sum}}\} = x + y + \underline{\text{cin}};$

## RTL Design of Full Adder

module ADD\_FULL\_RTL (sum,cout,x,y,cin);

output sum,cout; input x,y,cin;

//declaration for behavioral model

wire cin,x,y;

reg sum,cout;

// behavioral specification

always @ (x or y or cin)

{cout, sum} = x + y + cin;

endmodule

## Two-bit, Ripple Carry Adder – Structural Verilog

module TWO\_BIT\_ADD (S,X,Y,cin,cout);

input cin; input [1:0]X,Y; // vectored input output [1:0]S; // and output signals output cout;

wire cinternal;

ADD\_FULL AF0(S[0],cinternal,X[0],Y[0],cin); ADD\_FULL AF1(S[1],cout,X[1],Y[1],cinternal);

endmodule

January 30, 2012

## Two-bit, Ripple Carry Adder – PLD Implementation

- Functional Simulation

- Base-4 Bus Representation of X, Y and Sum

| Name:                      | 100.0ns                    | 200.0ns   | 300.0ns                      | 400.0ns           | 500.0ns              | 600.0ns                                                                      | 700.         |

|----------------------------|----------------------------|-----------|------------------------------|-------------------|----------------------|------------------------------------------------------------------------------|--------------|

| [I] cin                    |                            |           |                              |                   |                      |                                                                              |              |

| [I] X                      | 0 1                        | X 2 X     | 3                            |                   |                      |                                                                              | <u>X</u> 0   |

| [I] Y                      | 0/1/2/3/0/1/2/3            | 3 0 1 2 3 | 0/1/2/3/0/1                  | 2230112           | 3 0 1 2              | <u>3 1 1 1 2 1 3 1 3 1 1 2 1 3 1 1 2 1 3 1 1 1 2 1 3 1 1 1 2 1 3 1 1 1 1</u> | <u>3 X 0</u> |

| [O]cout                    |                            |           |                              |                   |                      |                                                                              |              |

| [0]S                       | 0 1 2 3 1 2 3              |           | 3 0 1 2 1 2                  | <u>\3\0\2\3\0</u> | 1 3 0 1              | 21011213                                                                     | 3 🚶 🛛 🗌      |

|                            |                            |           |                              |                   |                      |                                                                              |              |

| 0.1.1                      | 0 1 10                     |           | 1.1                          |                   | 11                   |                                                                              |              |

| 0+1+                       | $3 = 4 = 10_4 \rightarrow$ |           | 1+,                          | 2+2 = 5 =         | $  _4 \rightarrow  $ |                                                                              |              |

|                            |                            |           |                              |                   |                      |                                                                              |              |

| $0+3+0=3=03_4 \rightarrow$ |                            |           | $1+3+3=7=13_{4} \rightarrow$ |                   |                      |                                                                              |              |

|                            | 01010-0                    |           |                              |                   |                      |                                                                              |              |

## Verilog Test Bench

Device Under Test (DUT)

- Circuit being designed/developed

Full adder for this example

- Testbench

- Provides stimulus to DUT

- Like test equipment on a bench

- Instantiate DUT in testbench

- Generate all signals in testbench

- No I/O (parameter list) in testbench

## Full Adder Testbench Example

module ADDFULL\_TB;

reg a,b,ci; wire sum,co;

initial begin

a = 0; b = 0; ci = 0;end always begin #5 a = ~a; end

always begin #10 b = ~b; end

always begin #20 ci = ~ci; end

ADD\_FULL AF1(sum,co,a,b,ci);

endmodule