### Compensation for Simultaneous Switching Noise in VLSI Packaging

Brock J. LaMeres University of Colorado September 15, 2005

September 15, 2005

"Compensation of SSN in VLSI Packaging"

1

### **Problem Statement**

- Package Interconnect Limits VLSI System Performance

- The three main components of this are:

Cost

Power Delivery

Signal Path Reflections

### Agenda

- Current Problems

- Current Solutions

- Proposed Solutions

- Case Study of Proposed Solutions

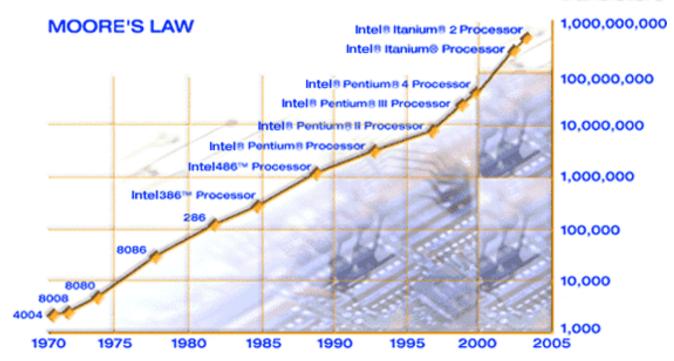

### Why is packaging limiting performance?

#### transistors

#### **Transistor Technology is Outpacing Package Technology**

### Problem #1 - Cost

#### 1) Cost

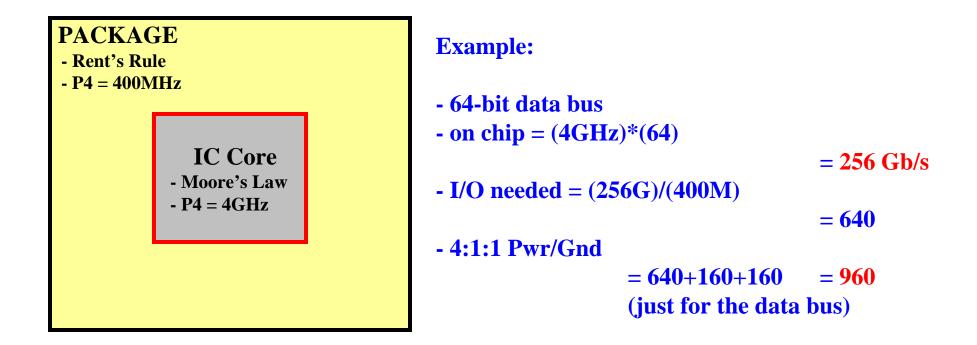

- IC core technology is increasing faster than package technology.

- Simply adding I/O on the package to keep up with core speeds is too expensive.

#### **Problem #1 - Cost**

#### 1) Cost cont...

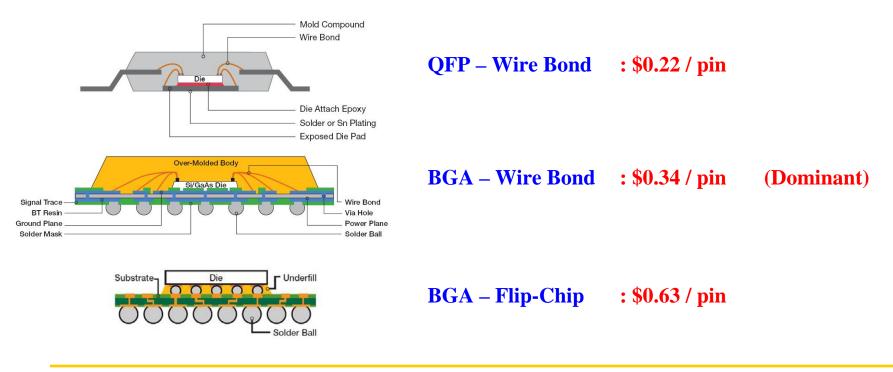

- Aggressive Package Design will increase the data rates of the package

- But it is too expensive for mainstream designs

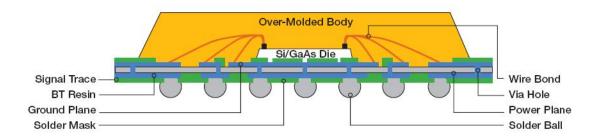

- 95% of VLSI design-starts are wire-bond

"Compensation of SSN in VLSI Packaging"

#### **Problem #1 - Cost**

#### 1) Cost cont...

- The Desired Solution:

- A) Make Existing Package Technology Go Faster

- **B)** Postpone Advanced Packaging Leap as long as possible

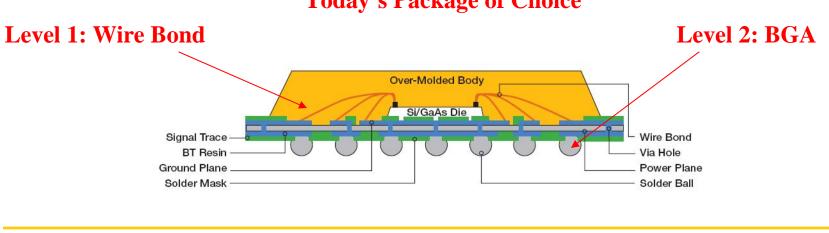

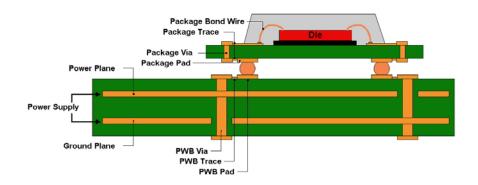

#### "Today's Package of Choice"

"Compensation of SSN in VLSI Packaging"

### **Problem #2 – Power Delivery**

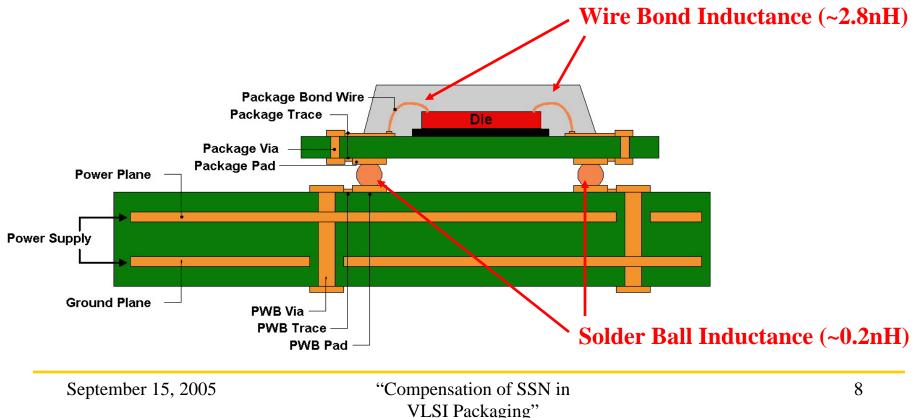

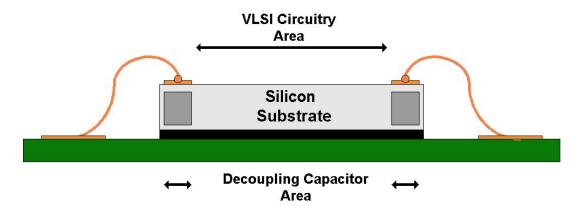

#### 2) Power Delivery

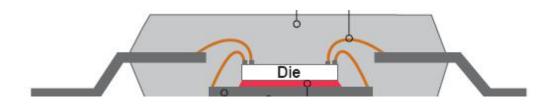

- Modern IC's require large amounts of instantaneous current (P4 = 80Amps)

- The package interconnect has inductance that causes voltage noise.

- The wire bond is the largest source of inductance.

### **Problem #2 – Power Delivery**

#### 2) Power Delivery cont...

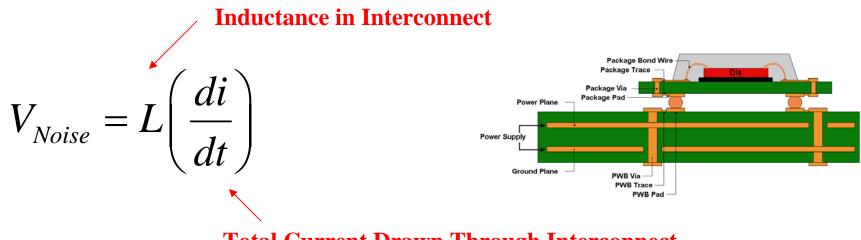

- The voltage noise causes ground bounce and power supply droop.

- These effects cause unwanted switching and slow performance.

- The problem is amplified when a many signals switch at the same time.

- This is called Simultaneous Switching Noise (SSN)

#### **Total Current Drawn Through Interconnect**

### **Problem #2 – Power Delivery**

#### 2) Power Delivery cont...

- The Desired Solution:

- A) Use Existing Package Technology to Deliver Power

- **B)** Postpone Advanced Packaging Leap as long as possible

### **Problem #3 – Reflections**

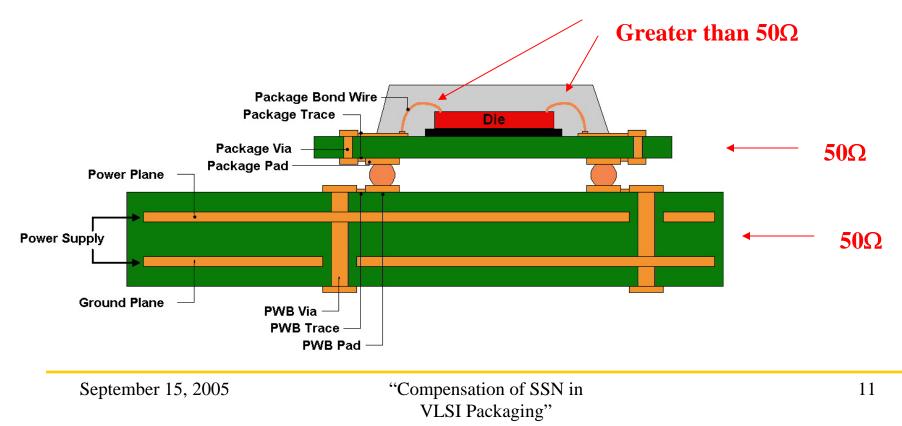

#### **3) Signal Path Reflections**

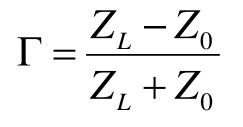

- Typical Motherboards and Packages use 50 $\Omega$  transmission lines.

- The package interconnect has excess inductance that looks >50 $\Omega$ 's.

- This causes reflections due to impedance mismatch.

### **Problem #3 – Reflections**

#### 3) Signal Path Reflections cont...

- Reflections cause unwanted switching

- Reflections slow down rise times

The Reflection due to the Wire-Bond:

$Z_L = Wire Bond Impedance$  $Z_0 = 50\Omega$

"Compensation of SSN in VLSI Packaging"

### **Problem #3 – Reflections**

#### 3) Signal Path Reflections cont...

- The Desired Solution:

- A) Use Existing Package Technology to Transmit Signals

- **B)** Postpone Advanced Packaging Leap as long as possible

## Problem

#### Why is packaging an electrical issue now?

**Cost**

Historically, the transistor delay has dominated performance, not packaging. Inexpensive packaging has met the electrical performance needs.

#### **Power Delivery**

As transistors shrink, more can be put on an IC and they can run faster. This means today more power is being consumed in less time.

#### **Impedance Matching**

Today's rise times are fast enough so that Packages must be treated as transmission lines. Until recently, we didn't care about impedance.

### **Current Solution #1 - Cost**

**Continue to use Wire-Bonding**

1) Use Standard VLSI Processes to Increase Performance of Wire-Bonded BGA Packaging

"Compensation of SSN in VLSI Packaging"

### **Current Solution #1 - Cost**

#### **Limitations of Approach**

- 1) Use Standard VLSI Processes to Increase Performance of Wire-Bonded BGA Packaging

- Modern IC's only implement low-risk solutions

- Advanced techniques are not in use yet.

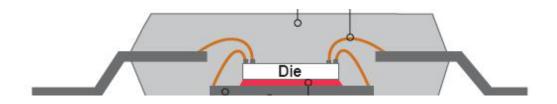

## **Current Solution #2 – Power Delivery Use Redundant Wire Bonds in Power/Ground Path**

1) Wire Bonds in Parallel Reduce the Total Inductance

### **Current Solution #2 – Power Delivery**

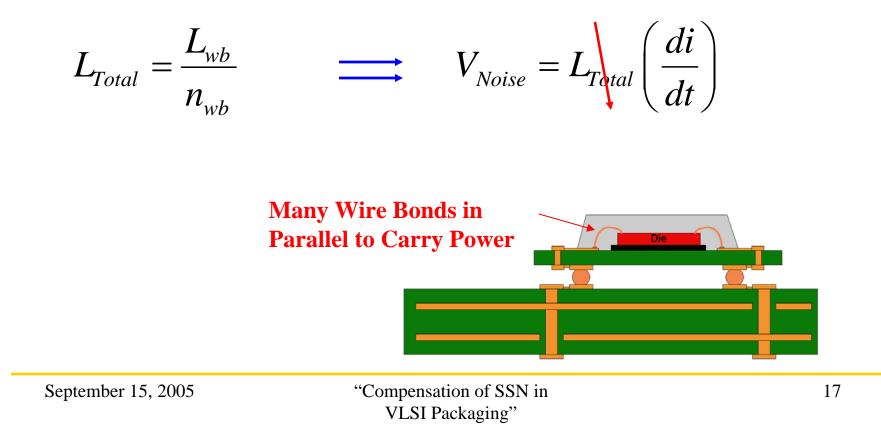

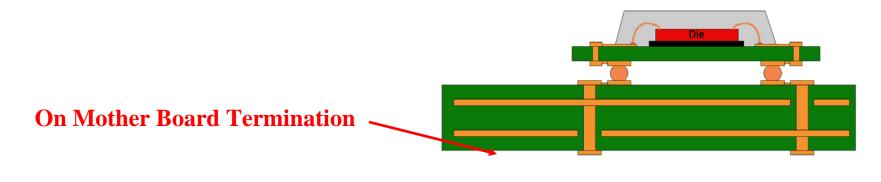

#### **Use Bypass Capacitors to Provide Instantaneous Current**

2) On-Chip Capacitance Provides Current Blocked by Wire-Bond3) On-Mother Board Capacitance Provides Current Blocked by Planes

# **Current Solution #2 – Power Delivery**

#### **Limitations of Approach**

- 1) Wire Bonds in Parallel Reduce the Total Inductance

- The total number of wires is limited by die size

- 2) On-Chip Capacitance Provides Current Blocked by Wire-Bond

We want as much as possible, limited by die size

- 3) On-Mother Board Capacitance Provides Current Blocked by Planes

- Adding discrete components adds cost

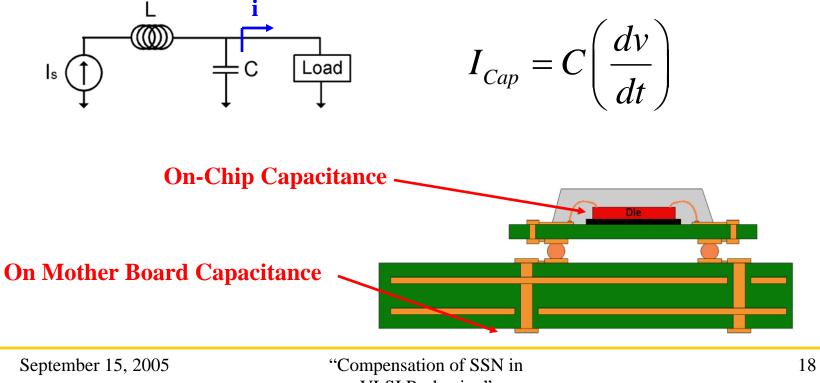

#### **Current Solution #3 – Reflections**

#### **Live with the Signal Path Reflections**

1) Run the signals slow enough so that reflections are small

$$\Gamma = \frac{Z_L - Z_0}{Z_L + Z_0} < 10\%$$

2) Terminate Signals on the Mother board so that reflections are absorbed

## **Current Solution #3 – Reflections Limitations of Approach**

1) Run the signals slow enough so that reflections are small

• Limits System Performance

2) Terminate Signals on the Mother board so that reflections are absorbed

• This only eliminates secondary reflections, the primary still exists

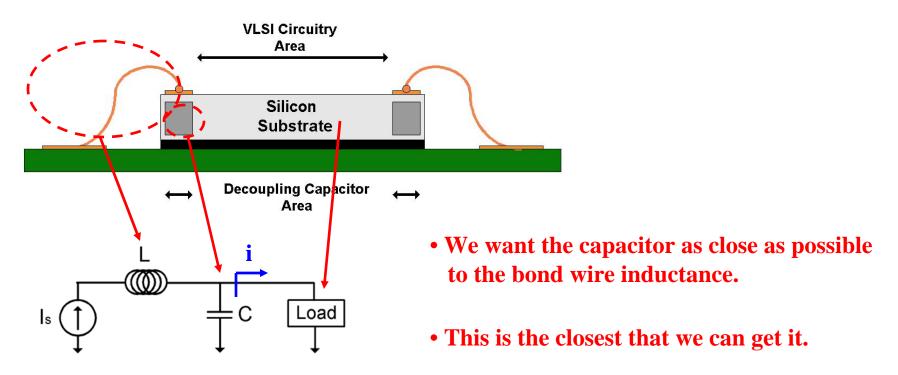

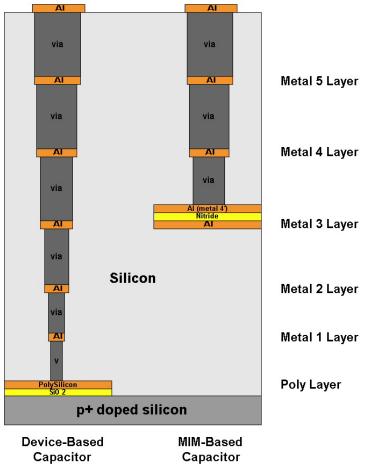

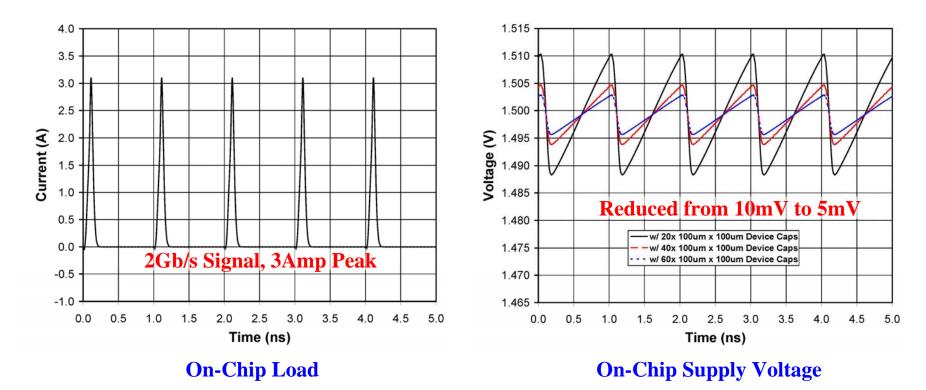

- 1) Use Device-Based Capacitors Beneath Wire-Bond Pads

- A) Placing capacitors beneath the bond wire pad eliminates impact on circuit area

- Area beneath the wire bond pads is typically not used.

- Today's processes have proved that this area is in fact useable.

- Using this area is effectively "free" and doesn't impact circuitry

#### 1) Use Device-Based Capacitors Beneath Wire-Bond Pads cont...

**B)** Placing beneath the bond wire pad is the optimal location

1) Use Device-Based Capacitors Beneath Wire-Bond Pads cont...

C) Device-based (PolySilicon) capacitors are the highest density on-chip capacitors

- Device-Based = 13 fF/um<sup>2</sup>

- MIM-Based = 1.1 fF/um<sup>2</sup>

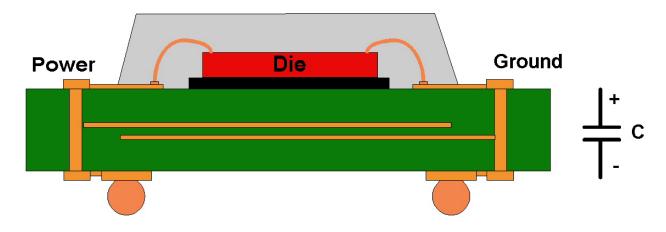

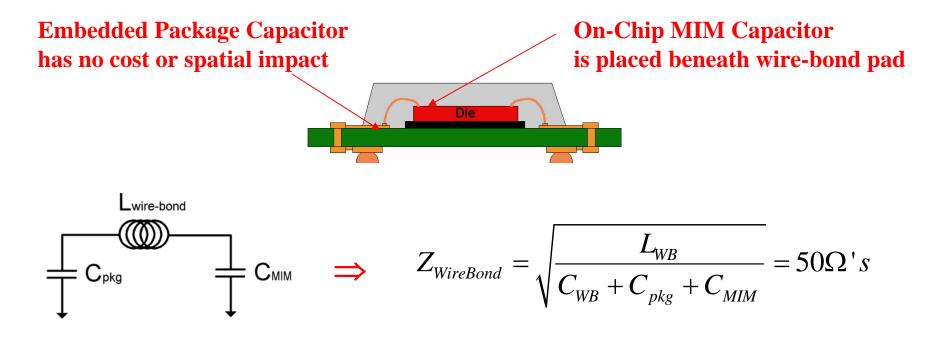

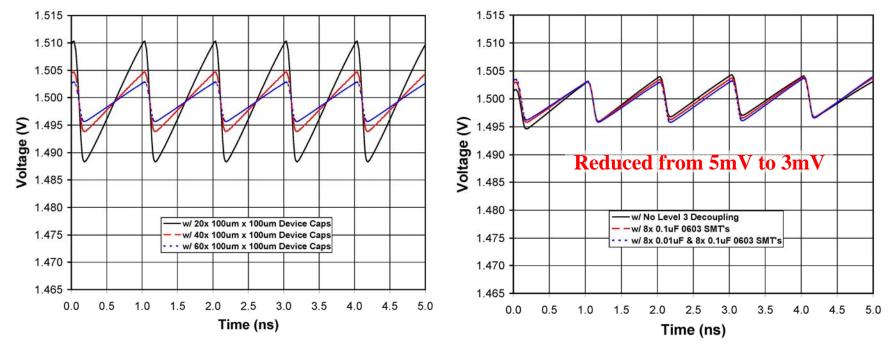

#### 2) Use Embedded Capacitance on Package

- Using plane-to-plane capacitance on the package for additional bypassing

- Modern Packages can achieve plane-to-plane separations of *t*=0.002"

- This translates to 0.64pF/mm<sup>2</sup>

- For a 0.8"x0.8" package, this can mean an additional 256pF

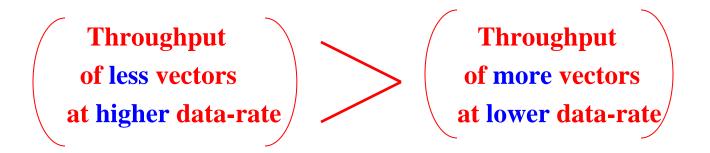

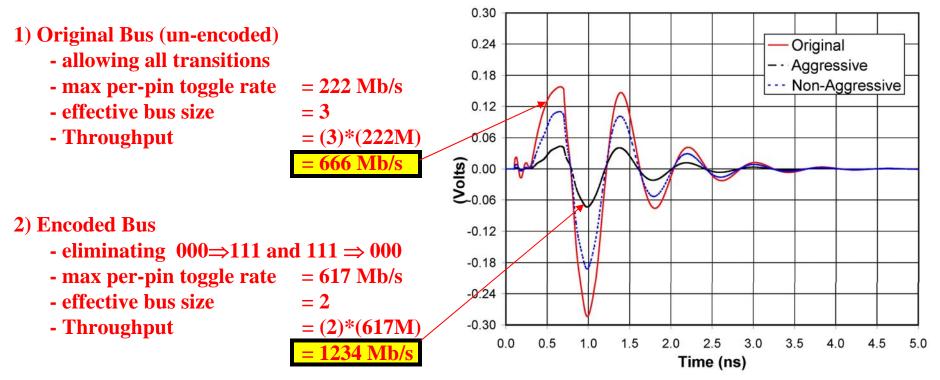

3) Encode the Data to Avoid Worst Case Switching Pattern

- Getting rid of worst case switching patterns reduces max voltage noise.

- The off-chip bus can actually run *faster* encoded.

- The increase in encoded bus speed makes up for smaller symbol set.

3) Encode the Data to Avoid Worst Case Switching Pattern

- ex) 3-bit bus

- worst case SSN is on the transitions:

$\begin{array}{ll} 000 \Rightarrow 111 & \text{and} \\ 111 \Rightarrow 000 & \end{array}$

- add encoder circuit to eliminate these transitions.

- the new data bus has less possible transitions but can run faster

- the increase in speed outweighs the reduction in transitions

#### 1) Add Capacitance Near Bond Wire to Reduce Impedance

- adding addition capacitance lowers the wire bond's impedance.

- matching the bond wire impedance to the system (50 $\Omega$ 's) reduces reflections.

$$Z_{WireBond} = \sqrt{\frac{L_{WireBond}}{C_{WireBond}}} \leftarrow Add Capacitance to lower Z$$

2) Using Static Capacitance Before and After the Bond Wire

- Use embedded capacitors on the package before the wire bond.

- Use On-Chip MIM capacitors after the wire bond.

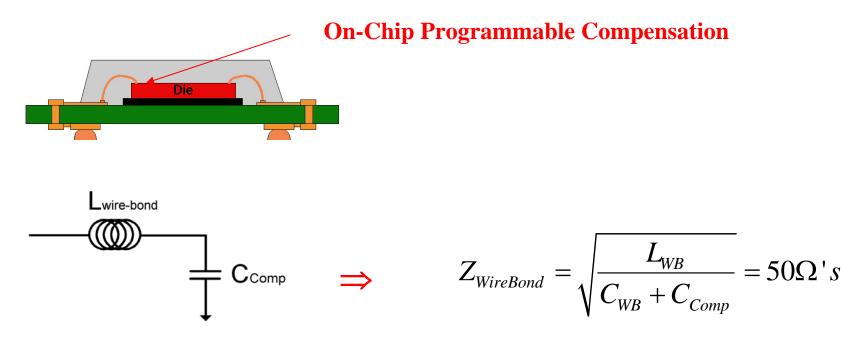

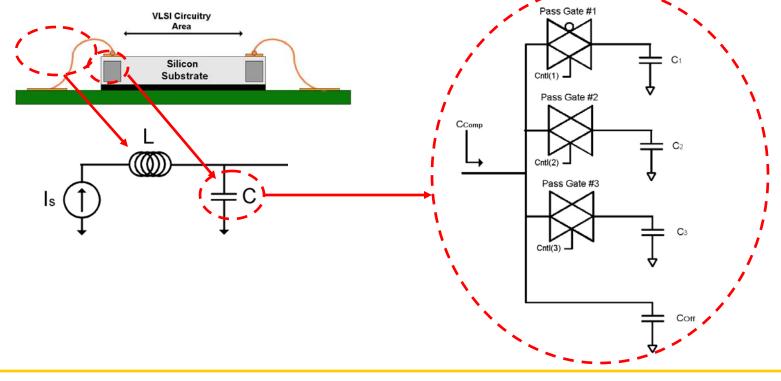

#### **3) Using On-Chip Dynamic Capacitance near the Bond Wire**

- A programmable capacitor circuit is placed beneath the wire-bond pad.

- The programmable range of the circuit covers wire bond variation.

September 15, 2005

"Compensation of SSN in VLSI Packaging"

#### **3) Using On-Chip Dynamic Capacitance near the Bond Wire cont...**

- A programmable capacitor circuit is placed beneath the wire-bond pad.

- The programmable range of the circuit covers wire bond variation.

"Compensation of SSN in VLSI Packaging"

### CASE STUDY

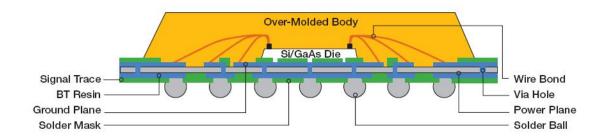

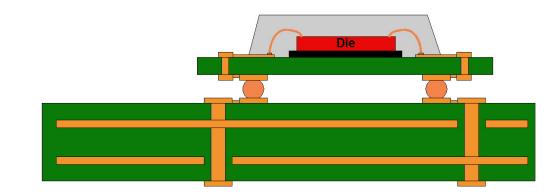

#### • A Modern BGA Package using Wire-Bond

- 340 I/O :

- 1mm Pitch BGA:

- 125um Pitch Gold Bonds:

| 20mm x 20mm |     |  |  |

|-------------|-----|--|--|

|             | 5mm |  |  |

|             | X   |  |  |

|             | 5mm |  |  |

|             |     |  |  |

|             |     |  |  |

|             |     |  |  |

|             |     |  |  |

60 Ground, 60 Power, 110 Input, 110 Output 340 Controlled Collapse Solder Balls 100um x 100um On-Chip Ball Pads (dual row) 100um x 400um On-Package Wedge Pads 5mm Gold Wire Bond (diameter=25um)

### **CASE STUDY – Electrical Modeling**

- Electrical Parameters are Extracted using EM Field Solver

- Values are then used in SPICE Simulations

#### Wire Bond Example

| <b>Length</b> | L       | <u>C</u>    | Z    |

|---------------|---------|-------------|------|

| 1mm           | 0.569nH | <b>26fF</b> | 148Ω |

| 2mm           | 1.138nH | <b>52fF</b> | 148Ω |

| 3mm           | 1.707nH | <b>78fF</b> | 148Ω |

| 4mm           | 2.276nH | 104fF       | 148Ω |

| 5mm           | 2.845nH | 130fF       | 148Ω |

### **CASE STUDY – Power Delivery 1**

• Using On-Chip Device-Based Capacitance Beneath Wire Bond Pads

### **CASE STUDY – Power Delivery 2**

#### Adding On-Package Embedded Capacitance also

**On-Chip Capacitance Only**

**On-Chip + On-Package**

### **CASE STUDY – Power Delivery 3**

# • Encoding Data to Avoid Worst Case Patterns (3-bit bus example)

#### **Ground Bounce**

- Adding Static (fixed) Capacitance on both sides of wire-bond •

- Embedded Capacitance On Package

- MIM Capacitance On-Chip

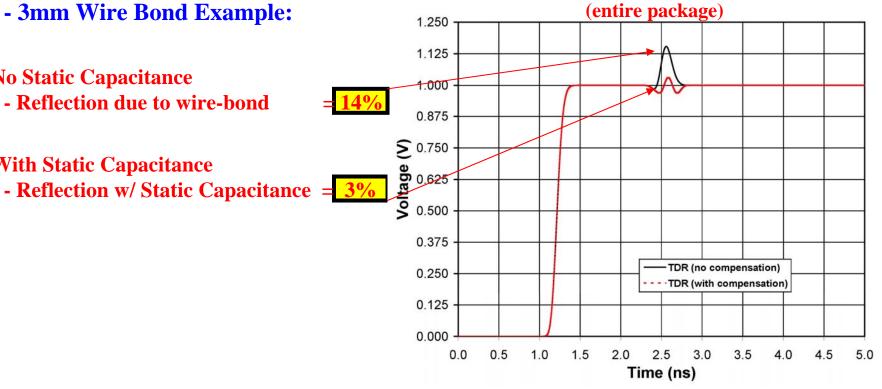

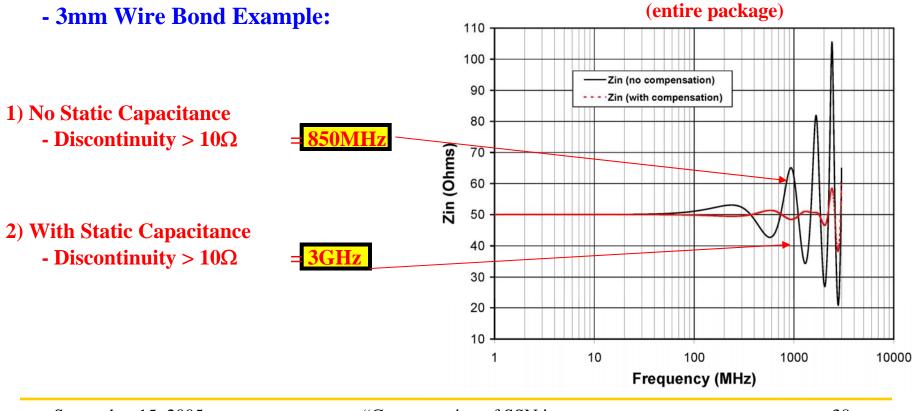

- 3mm Wire Bond Example:

- 2) With Static Capacitance

"Compensation of SSN in VLSI Packaging"

- Adding Static (fixed) Capacitance on both sides of wire-bond

- Embedded Capacitance On Package

- MIM Capacitance On-Chip

- 3mm Wire Bond Example:

#### **Input Impedance**

"Compensation of SSN in VLSI Packaging"

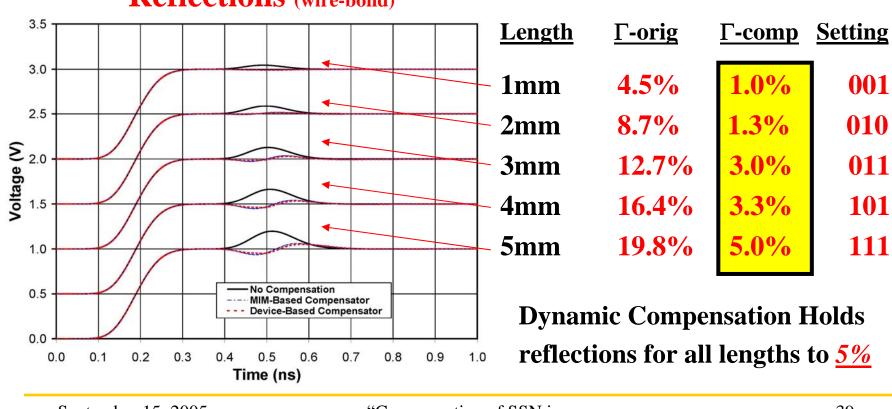

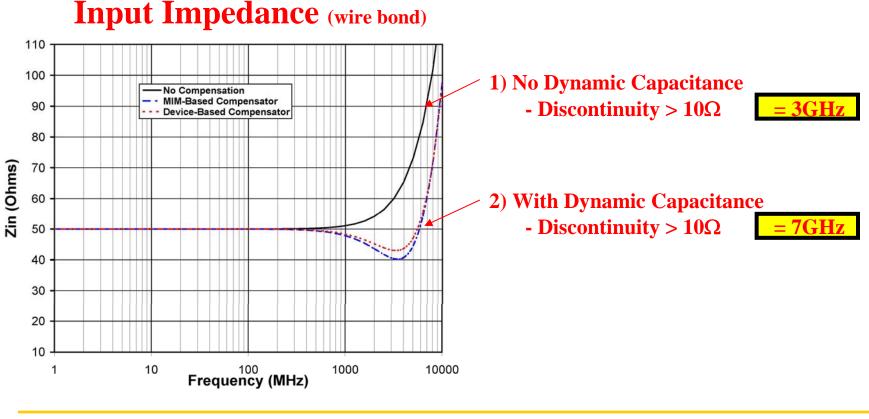

- Adding Dynamic (programmable) Capacitance on-chip

- Device-Based Compensator Outperforms MIM-Based

- 1mm to 5mm Wire Bond Range:

**Reflections** (wire-bond)

September 15, 2005

- Adding Dynamic (programmable) Capacitance on-chip

- Device-Based Compensator Outperforms MIM-Based

- 3mm Wire-Bond Example:

### Summary

- Package Interconnect is now the limiting factor in VLSI Performance

- The move toward Advanced Packaging is Resisted due to Cost

- VLSI Designers are looking for techniques to increase current package performance without adding cost

- Adding On-Chip circuitry does not add cost and is the desired solution

### Summary

Potential Solutions to increase Existing Package Technology

#### **Power Delivery**

- 1) On-Chip Device-Based Capacitance Under Wire Bond Pads

- 2) Embedded Capacitance on the Package

- 3) Encoding Data to Avoid Worst Case SSN Patterns

#### **Reflections**

- 1) Adding Static Capacitance to Package and IC

- 2) Adding Dynamic Capacitance to IC

# **Questions?**

September 15, 2005