Concurrent Programming: Algorithms, Principles, and Foundations

Algorithms, Principles, and Foundations

Bearbeitet von Michel Raynal

1. Auflage 2012. Buch. xxxii, 516 S. Hardcover ISBN 978 3 642 32026 2 Format (B x L): 15,5 x 23,5 cm Gewicht: 979 g

<u>Weitere Fachgebiete > EDV, Informatik > Programmiersprachen: Methoden ></u> <u>Funktionale, logische, parallele und visuelle Programmierung</u>

Zu Inhaltsverzeichnis

schnell und portofrei erhältlich bei

Die Online-Fachbuchhandlung beck-shop.de ist spezialisiert auf Fachbücher, insbesondere Recht, Steuern und Wirtschaft. Im Sortiment finden Sie alle Medien (Bücher, Zeitschriften, CDs, eBooks, etc.) aller Verlage. Ergänzt wird das Programm durch Services wie Neuerscheinungsdienst oder Zusammenstellungen von Büchern zu Sonderpreisen. Der Shop führt mehr als 8 Millionen Produkte.

# Chapter 2 Solving Mutual Exclusion

This chapter is on the implementation of mutual exclusion locks. As announced at the end of the previous chapter, it presents three distinct families of algorithms that solve the mutual exclusion problem. The first is the family of algorithms which are based on atomic read/write registers only. The second is the family of algorithms which are based on specialized hardware operations (which are atomic and stronger than atomic read/write operations). The third is the family of algorithms which are based on read/write registers which are weaker than atomic registers. Each algorithm is first explained and then proved correct. Other properties such as time complexity and space complexity of mutual exclusion algorithms are also discussed.

**Keywords** Atomic read/write register · Lock object · Mutual exclusion · Safe read/write register · Specialized hardware primitive (test&set, fetch&add, compare&swap)

## 2.1 Mutex Based on Atomic Read/Write Registers

## 2.1.1 Atomic Register

The *read/write register* object is one of the most basic objects encountered in computer science. When such an object is accessed only by a single process it is said to be *local* to that process; otherwise, it is a *shared* register. A local register allows a process to store and retrieve data. A shared register allows concurrent processes to also exchange data.

**Definition** A *register R* can be accessed by two base operations: *R*.read(), which returns the value of *R* (also denoted  $x \leftarrow R$  where *x* is a local variable of the invoking process), and *R*.write(*v*), which writes a new value into *R* (also denoted  $R \leftarrow v$ , where *v* is the value to be written into *R*). An *atomic* shared register satisfies the following properties:

- Each invocation op of a read or write operation:

- Appears as if it was executed at a single point  $\tau(op)$  of the time line,

- $-\tau(op)$  is such that  $\tau_b(op) \le \tau(op) \le \tau_e(op)$ , where  $\tau_b(op)$  and  $\tau_e(op)$  denote the time at which the operation op started and finished, respectively,

- For any two operation invocations op1 and op2: (op1  $\neq$  op2)  $\Rightarrow$  ( $\tau$ (op1)  $\neq$   $\tau$ (op2)).

- Each read invocation returns the value written by the closest preceding write invocation in the sequence defined by the  $\tau$ () instants associated with the operation invocations (or the initial value of the register if there is no preceding write operation).

This means that an atomic register is such that all its operation invocations *appear* as if they have been executed sequentially: any invocation op1 that has terminated before an invocation op2 starts appears before op2 in that sequence, and this sequence belongs to the specification of a sequential register.

An atomic register can be single-writer/single-reader (SWSR)—the reader and the writer being distinct processes—or single-writer/multi-reader (SWMR), or multiwriter/multi-reader (MWMR). We assume that a register is able to contain any value. (As each process is sequential, a local register can be seen as a trivial instance of an atomic SWSR register where, additionally, both the writer and the reader are the same process.)

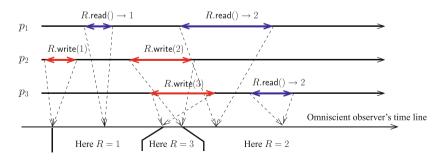

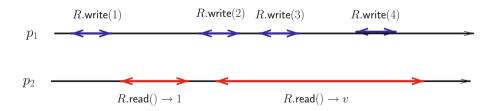

An example An execution of a MWMR atomic register accessed by three processes  $p_1$ ,  $p_2$ , and  $p_3$  is depicted in Fig. 2.1 using a classical space-time diagram. *R*.read()  $\rightarrow v$  means that the corresponding read operation returns the value *v*. Consequently, an external observer sees the following sequential execution of the register *R* which satisfies the definition of an atomic register:

$R.write(1), R.read() \rightarrow 1, R.write(3), R.write(2), R.read() \rightarrow 2, R.read() \rightarrow 2.$

Let us observe that R.write(3) and R.write(2) are concurrent, which means that they could appear to an external observer as if R.write(2) was executed before

Fig. 2.1 An atomic register execution

*R*.write(3). If this was the case, the execution would be correct if the last two read invocations (issued by  $p_1$  and  $p_3$ ) return the value 3; i.e., the external observer should then see the following sequential execution:

$R.write(1), R.read() \rightarrow 1, R.write(2), R.write(3), R.read() \rightarrow 3, R.read() \rightarrow 3.$

Let us also observe that the second read invocation by  $p_1$  is concurrent with both R.write(2) and R.write(3). This means that it could appear as having been executed before these two write operations or even between them. If it appears as having been executed before these two write operations, it should return the value 1 in order for the register behavior be atomic.

As shown by these possible scenarios (and as noticed before) *concurrency* is intimately related to *non-determinism*. It is not possible to predict which execution will be produced; it is only possible to enumerate the set of possible executions that could be produced (we can only predict that the one that is actually produced is one of them).

Examples of non-atomic read and write operations will be presented in Sect. 2.3.

**Why atomicity is important** Atomicity is a fundamental concept because it allows the composition of shared objects for free (i.e., their composition is at no additional cost). This means that, when considering two (or more) atomic registers R1 and R2, the composite object [R1, R2] which is made up of R1 and R2 and provides the processes with the four operations R1.read(), R1.write(), R2.read(), and R2.write() is also atomic. Everything appears as if at most one operation at a time was executed, and the sub-sequence including only the operations on R1 is a correct behavior of R1, and similarly for R2.

This is very important when one has to reason about a multiprocess program whose processes access atomic registers. More precisely, we can keep *reasoning sequentially* whatever the number of atomic registers involved in a concurrent computation. Atomicity allows us to reason on a set of atomic registers as if they were a single "bigger" atomic object. Hence, we can reason in terms of sequences, not only for each atomic register taken separately, but also on the whole set of registers as if they were a single atomic object.

The composition of atomic objects is formally addressed in Sect. 4.4, where it is shown that, as atomicity is a "local property", atomic objects compose for free.

### 2.1.2 Mutex for Two Processes: An Incremental Construction

The mutex algorithm for two processes that is presented below is due to G.L. Peterson (1981). This construction, which is fairly simple, is built from an "addition" of two base components. Despite the fact that these components are nearly trivial, they allow us to introduce simple basic principles.

```

operation acquire_mutex<sub>1</sub>(i) is

AFTER\_YOU \leftarrow i; wait (AFTER\_YOU \neq i); return()

end operation.

operation release_mutex<sub>1</sub>(i) is return() end operation.

```

**Fig. 2.2** Peterson's algorithm for two processes: first component (code for  $p_i$ )

The processes are denoted  $p_i$  and  $p_j$ . As the algorithm for  $p_j$  is the same as the one for  $p_i$  after having replaced *i* by *j*, we give only the code for  $p_i$ .

**First component** This component is described in Fig. 2.2 for process  $p_i$ . It is based on a single atomic register denoted *AFTER\_YOU*, the initial value of which is irrelevant (a process writes into this register before reading it). The principle that underlies this algorithm is a "politeness" rule used in current life. When  $p_i$  wants to acquire the critical section, it sets *AFTER\_YOU* to its identity *i* and waits until *AFTER\_YOU*  $\neq i$  in order to enter the critical section. Releasing the critical section entails no particular action.

It is easy to see that this algorithm satisfies the mutual exclusion property. When both processes want to acquire the critical section, each assigns its identity to the register *AFTER\_YOU* and waits until this register contains the identity of the other process. As the register is atomic, there is a "last" process, say  $p_j$ , that updated it, and consequently only the other process  $p_i$  can proceed to the critical section.

Unfortunately, this simple algorithm is not deadlock-free. If one process alone wants to enter the critical section, it remains blocked forever in the **wait** statement. Actually, this algorithm ensures that, when both processes want to enter the critical section, the first process that updates the register *AFTER\_YOU* is the one that is allowed to enter it.

**Second component** This component is described in Fig. 2.3. It is based on a simple idea. Each process  $p_i$  manages a flag (denoted *FLAG*[*i*]) the value of which is *down* or *up*. Initially, both flags are down. When a process wants to acquire the critical section, it first raises its flag to indicate that it is interested in the critical section. It is then allowed to proceed only when the flag of the other process is equal to *down*.

To release the critical section, a process  $p_i$  has only to reset FLAG[i] to its initial value (namely, down), thereby indicating that it is no longer interested in the mutual exclusion.

operation acquire\_mutex<sub>2</sub>(i) is  $FLAG[i] \leftarrow up$ ; wait (FLAG[j] = down); return() end operation. operation release\_mutex<sub>2</sub>(i) is  $FLAG[i] \leftarrow down$ ; return() end operation.

Fig. 2.3 Peterson's algorithm for two processes: second component (code for  $p_i$ )

It is easy to see that, if a single process  $p_i$  wants to repeatedly acquire the critical section while the other process is not interested in the critical section, it can do so (hence this algorithm does not suffer the drawback of the previous one). Moreover, it is also easy to see that this algorithm satisfies the mutual exclusion property. This follows from the fact that each process follows the following pattern: first write its flag and only then read the value of the other flag. Hence, assuming that  $p_i$  has acquired (and not released) the critical section, we had  $(FLAG[i] = up) \land (FLAG[j] = down)$  when it was allowed to enter the critical section. It follows that, after  $p_j$  has set FLAG[j] to the value up, it reads up from FLAG[i] and is delayed until  $p_i$  resets FLAG[i] to down when it releases the critical section.

Unfortunately, this algorithm is not deadlock-free. If both processes concurrently raise first their flags and then read the other flag, each process remains blocked until the other flag is set down which will never be done.

**Remark: the notion of a livelock** In order to prevent the previous deadlock situation, one could think replacing wait (FLAG[j] = down) by the following statement:

```

while (FLAG[j] = up) do

FLAG[i] \leftarrow down;

p_i delays itself for an arbitrary period of time;

FLAG[i] \leftarrow up

end while.

```

This modification can reduce deadlock situations but cannot eliminate all of them. This occurs, for example when both processes execute "synchronously" (both delay themselves for the same duration and execute the same step—writing their flag and reading the other flag—at the very same time). When it occurs, this situation is sometimes called a *livelock*.

This tentative solution was obtained by playing with asynchrony (modifying the process speed by adding delays). As a correct algorithm has to work despite any asynchrony pattern, playing with asynchrony can eliminate bad scenarios but cannot suppress all of them.

#### 2.1.3 A Two-Process Algorithm

**Principles and description** In a very interesting way, a simple "addition" of the two previous "components" provides us with a correct mutex algorithm for two processes (Peterson's two-process algorithm). This component addition consists in a process  $p_i$  first raising its flag (to indicate that it is competing, as in Fig. 2.3), then assigning its identity to the atomic register *AFTER\_YOU* (as in Fig. 2.2), and finally waiting until any of the progress predicates *AFTER\_YOU*  $\neq i$  or *FLAG*[*j*] = *down* is satisfied.

It is easy to see that, when a single process wants to enter the critical section, the flag of the other process allows it to enter. Moreover, when each process sees that

```

operation acquire_mutex(i) is

FLAG[i] \leftarrow up;

AFTER\_YOU \leftarrow i;

wait ((FLAG[j] = down) \lor (AFTER\_YOU \neq i));

return()

end operation.

operation release_mutex(i) is FLAG[i] \leftarrow down; return() end operation.

```

**Fig. 2.4** Peterson's algorithm for two processes (code for  $p_i$ )

the flag of the other one was raised, the current value of the register *AFTER\_YOU* allows exactly one of them to progress.

It is important to observe that, in the **wait** statement of Fig. 2.4, the reading of the atomic registers FLAG[j] and  $AFTER\_YOU$  are asynchronous (they are done at different times and can be done in any order).

**Theorem 1** The algorithm described in Fig. 2.4 satisfies mutual exclusion and bounded bypass (where the bound is f(n) = 1).

**Preliminary remark for the proof** The reasoning is based on the fact that the three registers FLAG[i], FLAG[j], and  $AFTER\_YOU$  are atomic. As we have seen when presenting the atomicity concept (Sect. 2.1.1), this allows us to reason as if at most one read or write operation on any of these registers occurs at a time.

Proof Proof of the mutual exclusion property.

Let us assume by contradiction that both  $p_i$  and  $p_j$  are inside the critical section. Hence, both have executed acquire\_mutex() and we have then FLAG[i] = up, FLAG[j] = up and  $AFTER_YOU = j$  (if  $AFTER_YOU = i$ , the reasoning is the same after having exchanged *i* and *j*). According to the predicate that allowed  $p_i$  to enter the critical section, there are two cases.

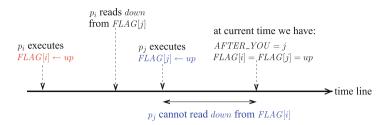

• Process  $p_i$  has terminated acquire\_mutex(i) because FLAG[j] = down.

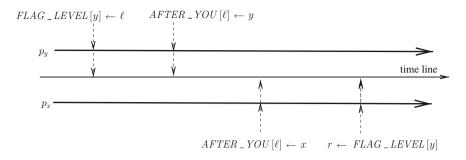

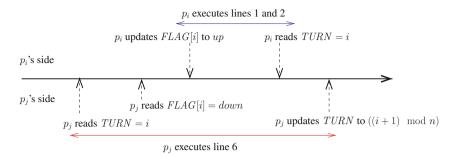

As  $p_i$  has set FLAG[i] to up before reading down from FLAG[j] (and entering the critical section), it follows that  $p_j$  cannot have read down from FLAG[i] before entering the critical section (see Fig. 2.5). Hence,  $p_j$  entered it due to the predicate  $AFTER\_YOU = i$ . But this contradicts the assumption that  $AFTER\_YOU = j$  when both processes are inside the critical section.

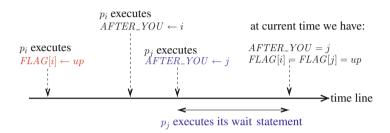

• Process  $p_i$  has terminated acquire\_mutex(*i*) because  $AFTER_YOU = j$ .

As (by assumption)  $p_j$  is inside the critical section,  $AFTER\_YOU = j$ , and only  $p_j$  can write j into  $AFTER\_YOU$ , it follows that  $p_j$  has terminated acquire\_mutex(j) because it has read *down* from FLAG[i]. On another side, FLAG[i] remains continuously equal to up from the time at which  $p_i$  has executed the first statement of acquire\_mutex(i) and the execution of release\_mutex(i) (Fig. 2.6).

Fig. 2.5 Mutex property of Peterson's two-process algorithm (part 1)

Fig. 2.6 Mutex property of Peterson's two-process algorithm (part 2)

As  $p_j$  executes the **wait** statement after writing *j* into *AFTER\_YOU* and  $p_i$  read *j* from *AFTER\_YOU*, it follows that  $p_j$  cannot read *down* from *FLAG*[*i*] when it executes the **wait** statement. This contradicts the assumption that  $p_j$  is inside the critical section.

Proof of the bounded bypass property.

Let  $p_i$  be the process that invokes acquire\_mutex(*i*). If FLAG[j] = down or  $AFTER_YOU = j$  when  $p_i$  executes the **wait** statement, it enters the critical section.

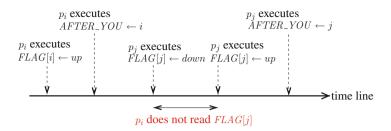

Let us consequently assume that  $(FLAG[j] = up) \land (AFTER\_YOU = i)$  when  $p_i$  executes the **wait** statement (i.e., the competition is lost by  $p_i$ ). If, after  $p_j$  has executed release\_mutex(j), it does not invoke acquire\_mutex(j) again, we permanently have FLAG[j] = down and  $p_i$  eventually enters the critical section.

Hence let us assume that  $p_j$  invokes again acquire\_mutex(j) and sets FLAG[j] to up before  $p_i$  reads it. Thus, the next read of FLAG[j] by  $p_i$  returns up. We have then  $(FLAG[j] = up) \land (AFTER_YOU = i)$ , and  $p_i$  cannot progress (see Fig. 2.7).

It follows from the code of acquire\_mutex(j) that  $p_j$  eventually assigns j to  $AFTER_YOU$  (and the predicate  $AFTER_YOU = j$  remains true until the next invocation of acquire\_mutex() by  $p_i$ ). Hence,  $p_i$  eventually reads j from  $AFTER_YOU$  and is allowed to enter the critical section.

It follows that a process looses at most one competition with respect to the other process, from which we conclude that the bounded bypass property is satisfied and we have f(n) = 1.

Fig. 2.7 Bounded bypass property of Peterson's two-process algorithm

**Space complexity** The space complexity of a mutex algorithm is measured by the number and the size of the atomic registers it uses.

It is easy to see that Peterson's two-process algorithm has a bounded space complexity: there are three atomic registers FLAG[i], FLAG[j], and  $AFTER_YOU$ , and the domain of each of them has two values. Hence three atomic bits are sufficient.

## 2.1.4 Mutex for n Processes: Generalizing the Previous Two-Process Algorithm

**Description** Peterson's mutex algorithm for n processes is described in Fig. 2.8. This algorithm is a simple generalization of the two-process algorithm described in Fig. 2.4. This generalization, which is based on the notion of level, is as follows.

In the two-process algorithm, a process  $p_i$  uses a simple SWMR flag FLAG[i] whose value is either *down* (to indicate it is not interested in the critical section) or up (to indicate it is interested). Instead of this binary flag, a process  $p_i$  uses now a multi-valued flag that progresses from a flag level to the next one. This flag, denoted  $FLAG\_LEVEL[i]$ , is initialized to 0 (indicating that  $p_i$  is not interested in the critical section). It then increases first to level 1, then to level 2, etc., until the level n - 1,

**Fig. 2.8** Peterson's algorithm for *n* processes (code for  $p_i$ )

which allows it to enter the critical section. For  $1 \le x < n-1$ , *FLAG\_LEVEL*[*i*] = *x* means that  $p_i$  is trying to enter level x + 1.

Moreover, to eliminate possible deadlocks at any level  $\ell$ ,  $0 < \ell < n - 1$  (such as the deadlock that can occur in the algorithm of Fig. 2.3), the processes use a second array of atomic registers *AFTER\_YOU*[1..(n - 1)] such that *AFTER\_YOU*[ $\ell$ ] keeps track of the last process that has entered level  $\ell$ .

More precisely, a process  $p_i$  executes a **for** loop to progress from one level to the next one, starting from level 1 and finishing at level n - 1. At each level the two-process solution is used to block a process (if needed). The predicate that allows a process to progress from level  $\ell$ ,  $0 < \ell < n - 1$ , to level  $\ell + 1$  is similar to the one of the two-process algorithm. More precisely,  $p_i$  is allowed to progress to level  $\ell + 1$  if, from its point of view,

- Either all the other processes are at a lower level (i.e.,  $\forall k \neq i:FLAG\_LEVEL$ [k] <  $\ell$ ).

- Or it is not the last one that entered level  $\ell$  (i.e., *AFTER\_YOU*[ $\ell$ ]  $\neq$  *i*).

Let us notice that the predicate used in the **wait** statement of line 4 involves all but one of the atomic registers  $FLAG\_LEVEL[\cdot]$  plus the atomic register  $AFTER\_YOU[\ell]$ . As these registers cannot be read in a single atomic step, the predicate is repeatedly evaluated asynchronously on each register.

When all processes compete for the critical section, at most (n-1) processes can concurrently be winners at level 1, (n-2) processes can concurrently be winners at level 2, and more generally  $(n - \ell)$  processes can concurrently be winners at level  $\ell$ . Hence, there is a single winner at level (n - 1).

The code of the operation release\_mutex(i) is similar to the one of the two-process algorithm: a process  $p_i$  resets *FLAG\_LEVEL*[i] to its initial value 0 to indicate that it is no longer interested in the critical section.

**Theorem 2** *The algorithm described in* Fig. 2.8 *satisfies mutual exclusion and starvation-freedom.*

**Proof** Initially, a process  $p_i$  is such that  $FLAG\_LEVEL[i] = 0$  and we say that it is at level 0. Let  $\ell \in [1..(n-1)]$ . We say that a process  $p_i$  has "attained" level  $\ell$  (or, from a global state point of view, "is" at level  $\ell$ ) if it has exited the **wait** statement of the  $\ell$ th loop iteration. Let us notice that, after it has set its loop index  $\ell$  to  $\alpha > 0$  and until it exits the **wait** statement of the corresponding iteration, that process is at level  $\alpha - 1$ . Moreover, a process that attains level  $\ell$  has also attained the levels  $\ell'$  with  $0 \le \ell' \le \ell \le n - 1$  and consequently it is also at these levels  $\ell'$ .

The proof of the mutual exclusion property amounts to showing that at most one process is at level (n - 1). This is a consequence of the following claim when we consider  $\ell = n - 1$ .

Claim. For  $\ell$ ,  $0 \le \ell \le n - 1$ , at most  $n - \ell$  processes are at level  $\ell$ .

The proof of this claim is by induction on the level  $\ell$ . The base case  $\ell = 0$  is trivial. Assuming that the claim is true up to level  $\ell - 1$ , i.e., at most  $n - (\ell - 1)$

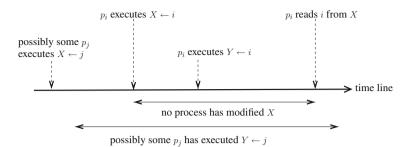

Fig. 2.9 Total order on read/write operations

processes are simultaneously at level  $\ell - 1$ , we have to show that at least one process does not progress to level  $\ell$ . The proof is by contradiction: let us assume that  $n - \ell + 1$  processes are at level  $\ell$ .

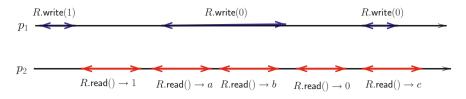

Let  $p_x$  be the last process that wrote its identity into  $AFTER\_YOU[\ell]$  (hence,  $AFTER\_YOU[\ell] = x$ ). When considering the sequence of read and write operations executed by every process, and the fact that these operations are on atomic registers, this means that, for any of the  $n - \ell$  other processes  $p_y$  that are at level  $\ell$ , these operations appear as if they have been executed in the following order where the first two operations are issued by  $p_y$  while the least two operations are issued by  $p_x$  (Fig. 2.9):

- 1. *FLAG\_LEVEL*[y]  $\leftarrow \ell$  is executed before *AFTER\_YOU*[ $\ell$ ]  $\leftarrow$  y (sequentiality of  $p_y$ )

- 2. *AFTER\_YOU*[ $\ell$ ]  $\leftarrow$  *y* is executed before *AFTER\_YOU*[ $\ell$ ]  $\leftarrow$  *x* (assumption: definition of  $p_x$ )

- 3. *AFTER\_YOU*[ $\ell$ ]  $\leftarrow$  *x* is executed before  $r \leftarrow FLAG\_LEVEL[y]$  (sequentiality of  $p_x$ ; *r* is  $p_x$ 's local variable storing the last value read from *FLAG\\_LEVEL[y]* before  $p_x$  exits the **wait** statement at level  $\ell$ ).

It follows from this sequence that  $r = \ell$ . Consequently, as  $AFTER\_YOU[\ell] = x$ ,  $p_x$  exited the **wait** statement of the  $\ell$ th iteration because  $\forall k \neq x$ :  $FLAG\_LEVEL$  $[k] < \ell$ . But this is contradicted by the fact that we had then  $FLAG\_LEVEL[y] = \ell$ , which concludes the proof of the claim.

The proof of the starvation-freedom property is by induction on the levels starting from level n - 1 and proceeding until level 1. The base case  $\ell = n - 1$  follows from the previous claim: if there is a process at level (n - 1), it is the only process at that level and it can exit the **for** loop. This process eventually enters the critical section (that, by assumption, it will leave later). The induction assumption is the following: each process that attains a level  $\ell'$  such that  $n - 1 \ge \ell' \ge \ell$  eventually enters the critical section.

The rest of the proof is by contradiction. Let us assume that  $\ell$  is such that there is a process (say  $p_x$ ) that remains blocked forever in the **wait** statement during its  $\ell$ th

iteration (hence,  $p_x$  cannot attain level  $\ell$ ). It follows that, each time  $p_x$  evaluates the predicate controlling the **wait** statement, we have

$$(\exists k \neq i : FLAG\_LEVEL[k] \ge \ell) \land (AFTER\_YOU[\ell] = x))$$

(let us remember that the atomic registers are read one at a time, asynchronously, and in any order). There are two cases.

• Case 1: There is a process  $p_y$  that eventually executes  $AFTER\_YOU[\ell] \leftarrow y$ .

As only  $p_x$  can execute  $AFTER\_YOU[\ell] \leftarrow x$ , there is eventually a read of  $AFTER\_YOU[\ell]$  that returns a value different from x, and this read allows  $p_x$  to progress to level  $\ell$ . This contradicts the assumption that  $p_x$  remains blocked forever in the **wait** statement during its  $\ell$ th iteration.

• Case 2: No process  $p_y$  eventually executes  $AFTER\_YOU[\ell] \leftarrow y$ .

The other processes can be partitioned in two sets: the set G that contains the processes at a level greater or equal to  $\ell$ , and the set L that contains the processes at a level smaller than  $\ell$ .

As the predicate  $AFTER\_YOU[\ell] = x$  remains forever true, it follows that no process  $p_y$  in L enters the  $\ell$ th loop iteration (otherwise  $p_y$  would necessarily execute  $AFTER\_YOU[\ell] \leftarrow y$ , contradicting the case assumption).

On the other side, due to the induction assumption, all processes in *G* eventually enter (and later leave) the critical section. When this has occurred, these processes have moved from the set *G* to the set *L* and then the predicate  $\forall k \neq i : FLAG\_LEVEL[k] < \ell$  becomes true.

When this has happened, the values returned by the asynchronous reading of  $FLAG\_LEVEL[1..n]$  by  $p_x$  allow it to attain level  $\ell$ , which contradicts the assumption that  $p_x$  remains blocked forever in the **wait** statement during its  $\ell$ th iteration.

In both case the assumption that a process remains blocked forever at level  $\ell$  is contradicted which completes the proof of the induction step and concludes the proof of the starvation-freedom property.

**Starvation-freedom versus bounded bypass** The two-process Peterson's algorithm satisfies the bounded bypass liveness property while the *n*-process algorithm satisfies only starvation-freedom. Actually, starvation-freedom (i.e., finite bypass) is the best liveness property that Peterson's *n*-process algorithm (Fig. 2.8) guarantees.

This can be shown with a simple example. Let us consider the case n = 3. The three processes  $p_1$ ,  $p_2$ , and  $p_3$  invoke simultaneously acquire\_mutex(), and the run is such that  $p_1$  wins the competition and enters the critical section. Moreover, let us assume that  $AFTER_YOU[1] = 3$  (i.e.,  $p_3$  is the last process that wrote  $AFTER_YOU[1]$ ) and  $p_3$  blocked at level 1.

Then, after it has invoked release\_mutex(), process  $p_1$  invokes acquire\_mutex() again and we have consequently  $AFTER_YOU[1] = 1$ . But, from that time,  $p_3$  starts

an arbitrary long "sleeping" period (this is possible as the processes are asynchronous) and consequently does not read  $AFTER_YOU[1] = 1$  (which would allow it to progress to the second level). Differently,  $p_2$  progresses to the second level and enters the critical section. Later,  $p_2$  first invokes release\_mutex() and immediately after invokes acquire\_mutex() and updates  $AFTER_YOU[1] = 2$ . While  $p_3$  keeps on "sleeping",  $p_1$  progresses to level 2 and finally enters the critical section. This scenario can be reproduced an arbitrary number of times until  $p_3$  wakes up. When this occurs,  $p_3$  reads from  $AFTER_YOU[1]$  a value different from 3, and consequently progresses to level 2. Hence:

- Due to asynchrony, a "sleeping period" can be arbitrarily long, and a process can consequently lose an arbitrary number of competitions with respect to the other processes,

- But, as a process does not sleep forever, it eventually progresses to the next level.

It is important to notice that, as shown in the proof of the bounded pass property of Theorem 1, this scenario cannot happen when n = 2.

Atomic register: size and number It is easy to see that the algorithm uses 2n - 1 atomic registers. The domain of each of the *n* registers *FLAG\_LEVEL*[*i*] is [0..(n-1)], while the domain of each of the n - 1 *AFTER\_YOU*[ $\ell$ ] registers is [1..n]. Hence, in both cases,  $\lceil \log_2 n \rceil$  bits are necessary and sufficient for each atomic register.

**Number of accesses to atomic registers** Let us define the time complexity of a mutex algorithm as the number of accesses to atomic registers for one use of the critical section by a process.

It is easy to see that this cost is finite but not bounded when there is contention (i.e., when several processes simultaneously compete to execute the critical section code).

Differently in a contention-free scenario (i.e., when only one process  $p_i$  wants to use the critical section), the number of accesses to atomic registers is (n-1)(n+2) in acquire\_mutex(*i*) and one in release\_mutex(*i*).

**The case of** *k***-exclusion** This is the *k*-mutual exclusion problem where the critical section code can be concurrently accessed by up to *k* processes (mutual exclusion corresponds to the case where k = 1).

Peterson's *n*-process algorithm can easily be modified to solve *k*-mutual exclusion. The upper bound of the **for** loop (namely (n-1)) has simply to be replaced by (n-k). No other statement modification is required. Moreover, let us observe that the size of the array *AFTER\_YOU* can then be reduced to [1..(n-k)].

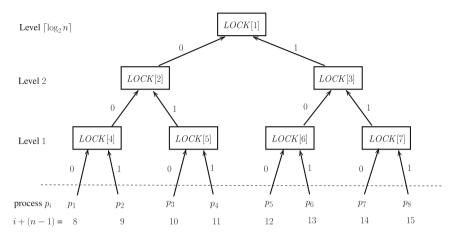

#### 2.1.5 Mutex for n Processes: A Tournament-Based Algorithm

**Reducing the number of shared memory accesses** In the previous *n*-process mutex algorithm, a process has to compete with the (n - 1) other processes before

#### 2.1 Mutex Based on Atomic Read/Write Registers

Fig. 2.10 A tournament tree for *n* processes

being able to access the critical section. Said differently, it has to execute n - 1 loop iterations (eliminating another process at each iteration), and consequently, the cost (measured in number of accesses to atomic registers) in a contention-free scenario is  $O(n) \times$  the cost of one loop iteration, i.e.,  $O(n^2)$ . Hence a natural question is the following: Is it possible to reduce this cost and (if so) how?

**Tournament tree** A simple principle to reduce the number of shared memory accesses is to use a tournament tree. Such a tree is a complete binary tree. To simplify the presentation, we consider that the number of processes is a power of 2, i.e.,  $n = 2^k$  (hence  $k = \log_2 n$ ). If *n* is not a power of two, it has to be replaced by  $n' = 2^k$  where  $k = \lceil \log_2 n \rceil$  (i.e., n' is the smallest power of 2 such that n' > n).

Such a tree for  $n = 2^3$  processes  $p_1, \ldots, p_8$ , is represented in Fig. 2.10. Each node of the tree is any two-process starvation-free mutex algorithm, e.g., Peterson's two-process algorithm. It is even possible to associate different two-process mutex algorithms with different nodes. The important common feature of these algorithms is that any of them assumes that it is used by two processes whose identities are 0 and 1.

As we have seen previously, any two-process mutex algorithm implements a lock object. Hence, we consider in the following that the tournament tree is a tree of (n-1) locks and we accordingly adopt the lock terminology. The locks are kept in an array denoted LOCK[1..(n-1)], and for  $x \neq y$ , LOCK[x] and LOCK[y] are independent objects (the atomic registers used to implement LOCK[x] and the atomic registers used to implement).

The lock LOCK[1] is associated with root of the tree, and if it is not a leaf, the node associated with the lock LOCK[x] has two children associated with the locks LOCK[2x] and LOCK[2x + 1].

According to its identity *i*, each process  $p_i$  starts competing with a single other process  $p_i$  to obtain a lock that is a leaf of the tree. Then, when it wins, the process

```

operation acquire_mutex(i) is

(1) node\_id \leftarrow i + (n-1);

(2) for level from 1 to k do \% k = \lceil \log_2 n \rceil \%

(3)

p\_id[level] \leftarrow node\_id \mod 2;

node\_id \leftarrow |node\_id/2|;

(4)

(5)

LOCK[node_id].acquire_lock(p_id[level])

(6)

end for;

(7)

return()

end operation.

operation release_mutex(i) is

(8) node\_id \leftarrow 1;

(9) for level from k to 1 do

LOCK[node_id].release_lock(p_id[level]);

(10)

node\_id \leftarrow 2 \times node\_id + p\_id[level]

(11)

(12) end for;

(13) return()

end operation.

```

Fig. 2.11 Tournament-based mutex algorithm (code for  $p_i$ )

$p_i$  proceeds to the next level of the tree to acquire the lock associated with the node that is the father of the node currently associated with  $p_i$  (initially the leaf node associated with  $p_i$ ). Hence, a process competes to acquire all the locks on the path from the leaf it is associated with until the root node.

As (a) the length of such a path is  $\lceil \log_2 n \rceil$  and (b) the cost to obtain a lock associated with a node is O(1) in contention-free scenarios, it is easy to see that the number of accesses to atomic registers in these scenarios is  $O(\log_2 n)$  (it is exactly  $4 \log_2 n$  when each lock is implemented with Peterson's two-process algorithm).

**The tournament-based mutex algorithm** This algorithm is described in Fig. 2.11. Each process  $p_i$  manages a local variable  $node_id$  such that  $LOCK[node_id]$  is the lock currently addressed by  $p_i$  and a local array  $p_id[1..k]$  such that  $p_id[\ell]$  is the identity (0 or 1) used by  $p_i$  to access  $LOCK[node_id]$  as indicated by the labels on the arrows in Fig. 2.10. (For a process  $p_i$ ,  $p_id[\ell]$  could be directly computed from the values *i* and  $\ell$ ; a local array is used to simplify the presentation.)

When a process  $p_i$  invokes acquire\_mutex(*i*) it first considers that it has successfully locked a fictitious lock object LOCK[i + (n - 1)] that can be accessed only by this process (line 1). Process  $p_i$  then enters a loop to traverse the tree, level by level, from its starting leaf until the root (lines 2–6). The starting leaf of  $p_i$  is associated with the lock  $LOCK[\lfloor(i + (n - 1))/2\rfloor]$  (lines 1 and 4). The identity used by  $p_i$  to access the lock  $LOCK[node_id]$  (line 5) is computed at line 3 and saved in  $p_id[level]$ .

When it invokes release\_mutex(*i*), process  $p_i$  releases the *k* locks it has locked starting from the lock associated with the root (*LOCK*[1]) until the lock associated

with its starting leaf  $LOCK[\lfloor (i + (n - 1))/2 \rfloor]$ . When it invokes  $LOCK[node_id]$ . release\_lock( $p_id[level]$ ) (line 10), the value of the parameter  $p_id[level]$  is the identity (0 or 1) used by  $p_i$  when it locked that object. This identity is also used by  $p_i$  to compute the index of the next lock object it has to unlock (line 11).

**Theorem 3** Assuming that each two-process lock object satisfies mutual exclusion and deadlock-freedom (or starvation-freedom), the algorithm described in Fig. 2.11 satisfies mutual exclusion and deadlock-freedom (or starvation-freedom).

*Proof* The proof of the mutex property is by contradiction. If  $p_i$  and  $p_j$  ( $i \neq j$ ) are simultaneously in the critical section, there is a lock object  $LOCK[node_id]$  such that  $p_i$  and  $p_j$  have invoked acquire\_lock() on that object and both have been simultaneously granted the lock. (If there are several such locks, let  $LOCK[node_id]$  be one at the lowest level in the tree.) Due to the specification of the lock object (that grants the lock to a single process identity, namely 0 or 1), it follows that both  $p_i$  and  $p_j$  have invoked  $LOCK[node_id]$ .acquire\_lock() with the same identity value (0 or 1) kept in their local variable  $p_id[level]$ . But, due to the binary tree structure of the set of lock objects and the way the processes compute  $p_id[level]$ , this can only happen if i = j (on the lowest level on which  $p_i$  and  $p_j$  share a lock), which contradicts our assumption and completes the proof of the mutex property.

The proof of the starvation-freedom (or deadlock-freedom) property follows from the same property of the base lock objects. We consider here only the starvationfreedom property. Let us assume that a process  $p_i$  is blocked forever at the object  $LOCK[node_id]$ . This means that there is another process  $p_j$  that competes infinitely often with  $p_i$  for the lock granted by  $LOCK[node_id]$  and wins each time. The proof follows from the fact that, due to the starvation-freedom property of  $LOCK[node_id]$ , this cannot happen.

**Remark** Let us consider the case where each algorithm implementing an underlying two-process lock object uses a bounded number of bounded atomic registers (which is the case for Peterson's two-process algorithm). In that case, as the tournament-based algorithm uses (n-1) lock objects, it follows that it uses a bounded number of bounded atomic registers.

Let us observe that this tournament-based algorithm has better time complexity than Peterson's *n*-process algorithm.

#### 2.1.6 A Concurrency-Abortable Algorithm

When looking at the number of accesses to atomic registers issued by acquire\_mutex() and release\_mutex() for a single use of the critical section in a contention-free scenario, the cost of Peterson's *n*-process mutual exclusion

algorithm is  $O(n^2)$  while the cost of the tournament tree-based algorithm is  $O(\log_2 n)$ . Hence, a natural question is the following: Is it possible to design a *fast n*-process mutex algorithm, where *fast* means that the cost of the algorithm is constant in a contention-free scenario?

The next section of this chapter answers this question positively. To that end, an incremental presentation is adopted. A simple one-shot operation is first presented. Each of its invocations returns a value r to the invoking process, where r is the value *abort* or the value *commit*. Then, the next section enriches the algorithm implementing this operation to obtain a deadlock-free fast mutual exclusion algorithm due to L. Lamport (1987).

**Concurrency-abortable operation** A *concurrency-abortable* (also named *contention-abortable* and usually abbreviated *abortable*) operation is an operation that is allowed to return the value *abort* in the presence of concurrency. Otherwise, it has to return the value *commit*. More precisely, let conc\_abort\_op() be such an operation. Assuming that each process invokes it at most once (one-shot operation), the set of invocations satisfies the following properties:

- Obligation. If the first process which invokes conc\_abort\_op() is such that its invocation occurs in a concurrency-free pattern (i.e., no other process invokes conc\_abort\_op() during its invocation), this process obtains the value *commit*.

- At most one. At most one process obtains the value commit.

An *n*-process concurrency-abortable algorithm Such an algorithm is described in Fig. 2.12. As in the previous algorithms, it assumes that all the processes have distinct identities, but differently from them, the number n of processes can be arbitrary and remains unknown to the processes.

This algorithm uses two MWMR atomic registers denoted X and Y. The register X contains a process identity (its initial value being arbitrary). The register Y contains a process identity or the default value  $\perp$  (which is its initial value). It is consequently assumed that these atomic registers are made up of  $\lceil \log_2(n+1) \rceil$  bits.

```

operation conc_abort_op(i) is

X \leftarrow i;

(1)

(2)

if (Y \neq \bot)

(3)

then return(abort_1)

(4)

else Y \leftarrow i;

(5)

if (X = i)

(6)

then return(commit)

(7)

else return(abort_2)

(8)

end if

(9)

end if

end operation.

```

**Fig. 2.12** An *n*-process concurrency-abortable operation (code for  $p_i$ )

When it invokes conc\_abort\_op(), a process  $p_i$  first deposits its identity in X (line 1) and then checks if the current value of Y is its initial value  $\perp$  (line 2). If  $Y \neq \perp$ , there is (at least) one process  $p_j$  that has written into Y. In that case,  $p_i$  returns *abort*<sub>1</sub> (both *abort*<sub>1</sub> and *abort*<sub>2</sub> are synonyms of *abort*; they are used only to distinguish the place where the invocation of conc\_abort\_op() is "aborted"). Returning *abort*<sub>1</sub> means that (from a concurrency point of view)  $p_i$  was late: there is another process that wrote into Y before  $p_i$  reads it.

If  $Y = \bot$ , process  $p_i$  writes its identity into Y (line 4) and then checks if X is still equal to its identity *i* (line 5). If this is the case,  $p_i$  returns the value *commit* at line 6 (its invocation of conc\_abort\_op(*i*) is then successful). If  $X \neq i$ , another process  $p_j$  has written its identity *j* into X, overwriting the identity *i* before  $p_i$  reads X at line 5. Hence, there is contention and the value *abort*<sub>2</sub> is returned to  $p_i$  (line 7). Returning *abort*<sub>2</sub> means that, among the competing processes that found  $y = \bot$ ,  $p_i$ was not the last to have written its name into X.

**Remark** Let us observe that the only test on *Y* is  $Y \neq \bot$  (line 2). It follows that *Y* could be replaced by a flag with the associated domain  $\{\bot, \top\}$ . Line 4 should then be replaced by  $Y \leftarrow \top$ .

Using such a flag is not considered here because we want to keep the notation consistent with that of the fast mutex algorithm presented below. In the fast mutex algorithm, the value of Y can be either  $\perp$  or any process identifier.

**Theorem 4** The algorithm described in Fig. 2.12 guarantees that (a) at most one process obtains the value commit and (b) if the first process that invokes conc\_abort\_op() executes it in a concurrency-free pattern, it obtains the value commit.

*Proof* The proof of property (b) stated in the theorem is trivial. If the first process (say  $p_i$ ) that invokes conc\_abort\_op() executes this operation in a concurrency-free context, we have  $Y = \bot$  when it reads Y at line 2 and X = i when it reads X at line 5. It follows that it returns *commit* at line 6.

Let us now prove property (a), i.e., that no two processes can obtain the value *commit*. Let us assume for the sake of contradiction that a process  $p_i$  has invoked conc\_abort\_op(*i*) and obtained the value *commit*. It follows from the text of the algorithm that the pattern of accesses to the atomic registers X and Y issued by  $p_i$  is the one described in Fig. 2.13 (when not considering the accesses by  $p_j$  in that figure). There are two cases.

• Let us first consider the (possibly empty) set Q of processes  $p_j$  that read Y at line 2 after this register was written by  $p_i$  or another process (let us notice that, due to the atomicity of the registers X and Y, the notion of after/before is well defined). As Y is never reset to  $\bot$ , it follows that each process  $p_j \in Q$  obtains a non- $\bot$  value from Y and consequently executes return(*abort*<sub>1</sub>) at line 3.

Fig. 2.13 Access pattern to X and Y for a successful conc\_abort\_op() invocation by process  $p_i$

• Let us now consider the (possibly empty) set Q' of processes  $p_j$  distinct from  $p_i$  that read  $\perp$  from Y at line 2 concurrently with  $p_i$ . Each  $p_j \in Q'$  writes consequently its identity j into Y at line 4.

As  $p_i$  has read *i* from *X* (line 5), it follows that no process  $p_j \in Q'$  has modified *X* between the execution of line 1 and line 5 by  $p_i$  (otherwise  $p_i$  would not have read *i* from *X* at line 5, see Fig. 2.13). Hence any process  $p_j \in Q'$  has written *X* (a) either before  $p_i$  writes *i* into *X* or (b) after  $p_i$  has read *i* from *X*. But, observe that case (b) cannot happen. This is due to the following observation. A process  $p_k$  that writes *X* (at line 1) after  $p_i$  has read *i* from this register (at line 5) necessarily finds  $Y \neq \bot$  at line 4 (this is because  $p_i$  has previously written *i* into *Y* at line 4 before reading *i* from *X* at line 5). Consequently, such a process  $p_k$  belongs to the set *Q* and not to the set *Q'*. Hence, the only possible case is that each  $p_j \in Q'$  has written *j* into *X* before  $p_i$  writes *i* into *X*. It follows that  $p_i$  is the last process of  $Q' \cup \{p_i\}$  which has written its identity into *X*.

We conclude from the previous observation that, when a process  $p_j \in Q'$  reads X at line 5, it obtains from this register a value different from j and, consequently, its invocation conc\_abort\_op(j) returns the value *abort*<sub>2</sub>, which concludes the proof of the theorem.

The next corollary follows from the proof of the previous theorem.

**Corollary 1**  $(Y \neq \bot) \Rightarrow a \text{ process has obtained the value commit or several processes have invoked conc_abort_op().$

**Theorem 5** Whatever the number of processes that invoke conc\_abort\_op(), any of these invocations costs at most four accesses to atomic registers.

*Proof* The proof follows from a simple examination of the algorithm.  $\Box$

**Remark: splitter object** When we (a) replace the value *commit*, *abort*<sub>1</sub>, and *abort*<sub>2</sub> by *stop*, *right*, and *left*, respectively, and (b) rename the operation

$conc_abort_op(i)$  as direction(*i*), we obtain a one-shot object called a *splitter*. A one-shot object is an object that provides processes with a single operation and each process invokes that operation at most once.

In a run in which a single process invokes direction(), it obtains the value *stop*. In any run, if m > 1 processes invoke direction(), at most one process obtains the value *stop*, at most (m - 1) processes obtain *right*, and at most (m - 1) processes obtain *left*. Such an object is presented in detail in Sect. 5.2.1.

#### 2.1.7 A Fast Mutex Algorithm

**Principle and description** This section presents L. Lamport's fast mutex algorithm, which is built from the previous one-shot concurrency-abortable operation. More specifically, this algorithm behaves similarly to the algorithm of Fig. 2.12 in contention-free scenarios and (instead of returning *abort*) guarantees the deadlock-freedom liveness property when there is contention.

The algorithm is described in Fig. 2.14. The line numbering is the same as in Fig. 2.12: the lines with the same number are the same in both algorithms, line N0 is new, line N3 replaces line 3, lines N7.1–N7.5 replace line 7, and line N10 is new.

To attain its goal (both fast mutex and deadlock-freedom) the algorithm works as follows. First, each process  $p_i$  manages a SWMR flag FLAG[i] (initialized to down)

```

operation acquire_mutex(i) is

FLAG[i] \leftarrow up;

(N0)

(1)

X \leftarrow i;

(2)

if (Y \neq \bot)

then FLAG[i] \leftarrow down; wait (Y = \bot); restart at line N0

(N3)

else Y \leftarrow i;

(4)

(5)

if (X = i)

then return()

(6)

(N7.1)

else FLAG[i] \leftarrow down;

for each j do wait (FLAG[j] = down) end for;

(N7.2)

if (Y = i) then return()

(N7.3)

else wait (Y = \bot); restart at line N0

(N7.4)

(N7.5)

end if

end if

(8)

(9)

end if

end operation.

operation release_mutex(i) is

(N10) Y \leftarrow \bot; FLAG[i] \leftarrow down; return()

end operation.

```

Fig. 2.14 Lamport's fast mutex algorithm (code for  $p_i$ )

that  $p_i$  sets to up to indicate that it is interested in the critical section (line N0). This flag is reset to *down* when  $p_i$  exits the critical section (line N10). As we are about to see, it can be reset to *down* also in other parts of the algorithm.

According to the contention scenario in which a process  $p_i$  returns *abort* in the algorithm of Fig. 2.12, there are two cases to consider, which have been differentiated by the values *abort*<sub>1</sub> and *abort*<sub>2</sub>.

• Eliminating *abort*<sub>1</sub> (line N3).

In this case, as we have seen in Fig. 2.12, process  $p_i$  is "late". As captured by Corollary 1, this is because there are other processes that currently compete for the critical section or there is a process inside the critical section. Line 3 of Fig. 2.12 is consequently replaced by the following statements (new line N3):

- Process  $p_i$  first resets its flag to *down* in order not to prevent other processes from entering the critical section (if no other process is currently inside it).

- According to Corollary 1, it is useless for  $p_i$  to retry entering the critical section while  $Y \neq \bot$ . Hence, process  $p_i$  delays its request for the critical section until  $Y = \bot$ .

- Eliminating *abort*<sub>2</sub> (lines N7.1–N7.5).

In this case, as we have seen in the base contention-abortable algorithm (Fig. 2.12), several processes are competing for the critical section (or a process is already inside the critical section). Differently from the base algorithm, one of the competing processes has now to be granted the critical section (if no other process is inside it). To that end, in order not to prevent another process from entering the critical section, process  $p_i$  first resets its flag to *down* (line N7.1). Then,  $p_i$  tries to enter the critical section. To that end, it first waits until all flags are down (line N7.2). Then,  $p_i$  checks the value of Y (line N7.3). There are two cases:

- If Y = i, process  $p_i$  enters the critical section. This is due to the following reason.

Let us observe that, if Y = i when  $p_i$  reads it at line N7.3, then no process has modified Y since  $p_i$  set it to the value *i* at line 4 (the write of Y at line 4 and its reading at line N7.3 follow the same access pattern as the write of X at line 1 and its reading at line 5). Hence, process  $p_i$  is the last process to have executed line 4. It then follows that, as it has (asynchronously) seen each flag equal to *down* (line 7.2), process  $p_i$  is allowed to enter the critical section (return() statement at line N7.3).

- If  $Y \neq i$ , process  $p_i$  does the same as what is done at line N3. As it has already set its flag to *down*, it has only to wait until the critical section is released before retrying to enter it (line N7.4). (Let us remember that the only place where Y is reset to  $\perp$  is when a process releases the critical section.)

**Fast path and slow path** The *fast* path to enter the critical section is when  $p_i$  executes only the lines N0, 1, 2, 4, 5, and 6. The fast path is open for a process  $p_i$

if it reads i from X at line 5. This is the path that is always taken by a process in contention-free scenarios.

The cost of the fast path is five accesses to atomic registers. As release\_mutex() requires two accesses to atomic registers, it follows that the cost of a single use of the critical section in a contention-free scenario is seven accesses to atomic registers.

The *slow* path is the path taken by a process which does not take the fast path. Its cost in terms of accesses to atomic registers depends on the current concurrency pattern.

**A few remarks** A register *FLAG*[*i*] is set to *down* when  $p_i$  exits the critical section (line N10) but also at line N3 or N7.1. It is consequently possible for a process  $p_k$  to be inside the critical section while all flags are down. But let us notice that, when this occurs, the value of *Y* is different from  $\perp$ , and as already indicated, the only place where *Y* is reset to  $\perp$  is when a process releases the critical section.

When executed by a process  $p_i$ , the aim of the **wait** statement at line N3 is to allow any other process  $p_j$  to see that  $p_i$  has set its flag to *down*. Without such a **wait** statement, a process  $p_i$  could loop forever executing the lines N0, 1, 2 and N3 and could thereby favor a livelock by preventing the other processes from seeing FLAG[i] = down.

**Theorem 6** Lamport's fast mutex algorithm satisfies mutual exclusion and deadlock-freedom.

*Proof* Let us first consider the mutual exclusion property. Let  $p_i$  be a process that is inside the critical section. Trivially, we have then  $Y \neq \bot$  and  $p_i$  returned from acquire\_mutex() at line 6 or at line N7.3. Hence, there are two cases. Before considering these two cases, let us first observe that each process (if any) that reads Y after it was written by  $p_i$  (or another process) executes line N3: it resets its flag to *down* and waits until  $Y = \bot$  (i.e., at least until  $p_i$  exits the critical section, line N10). As the processes that have read a non- $\bot$  value from Y at line 2 cannot enter the critical section, it follows that we have to consider only the processes  $p_j$  that have read  $\bot$ from Y at line 2.

• Process  $p_i$  has executed return() at line 6.

In this case, it follows from a simple examination of the text of the algorithm that FLAG[i] remains equal to up until  $p_i$  exits the critical section and executes line N10.

Let us consider a process  $p_j$  that has read  $\perp$  from Y at line 2. As process  $p_i$  has executed line 6, it was the last process (among the competing processes which read  $\perp$  from Y) to have written its identity into X (see Fig. 2.13) and consequently  $p_j$  cannot read j from X. As  $X \neq j$  when  $p_j$  reads X at line 5, it follows that process  $p_j$  executes the lines N7.1–N7.5. When it executes line N7.2,  $p_j$  remains blocked until  $p_i$  resets its flag to *down*, but as we have seen,  $p_i$  does so only when it exits the critical section. Hence,  $p_j$  cannot be inside the critical section simultaneously with  $p_i$ . This concludes the proof of the first case.

• Process  $p_i$  has executed return() at line N7.3.

In this case, the predicate Y = i allowed  $p_i$  to enter the critical section. Moreover, the atomic register Y has not been modified during the period starting when it was assigned the identity *i* at line 4 by  $p_i$  and ending at the time at which  $p_i$  read it at line N7.3. It follows that, among the processes that read  $\perp$  from Y (at line 2),  $p_i$  is the last one to have updated Y.

Let us observe that  $X \neq j$ , otherwise  $p_j$  would have entered the critical section at line 6, and in that case (as shown in the previous item)  $p_i$  could not have entered the critical section.

As Y = i, it follows from the test of line N7.3 that  $p_j$  executes line N7.4 and consequently waits until  $Y = \bot$ . As Y is set to  $\bot$  only when a process exits the critical section (line N10), it follows that  $p_j$  cannot be inside the critical section simultaneously with  $p_i$ , which concludes the proof of the second case.

To prove the deadlock-freedom property, let us assume that there is a non-empty set of processes that compete to enter the critical section and, from then on, no process ever executes return() at line 6 or line N 7.3. We show that this is impossible.

As processes have invoked acquire\_mutex() and none of them executes line 6, it follows that there is among them at least one process  $p_x$  that has executed first line N0 and line 1 (where it assigned its identity x to X) and then line N3. This assignment of x to X makes the predicate of line 5 false for the processes that have obtained  $\perp$  from Y. It follows that the flag of these processes  $p_x$  are eventually reset to *down* and, consequently, these processes cannot entail a permanent blocking of any other process  $p_i$  which executes line N7.2.

When the last process that used the critical section released it, it reset Y to  $\perp$  (if there is no such process, we initially have  $Y = \perp$ ). Hence, among the processes that have invoked acquire\_mutex(), at least one of them has read  $\perp$  from Y. Let Q be this (non-empty) set of processes. Each process of Q executes lines N7.1–N7.5 and, consequently, eventually resets its flag to *down* (line N7.1). Hence, the predicate evaluated in the **wait** statement at line N7.2 eventually becomes satisfied and the processes of Q which execute the lines N7.1–N7.5 eventually check at line N7.3 if the predicate Y = i is satisfied. (Due to asynchrony, it is possible that the predicate used at N7.2 is never true when evaluated by some processes. This occurs for the processes of Q which are slow while another process of Q has entered the critical section and invoked acquire\_mutex() again, thereby resetting its flag to up. The important point is that this can occur only if some process entered the critical section, hence when there is no deadlock.)

As no process is inside the critical section and the number of processes is finite, there is a process  $p_j$  that was the last process to have modified Y at line 4. As (by assumption)  $p_j$  has not executed return() at line 6, it follows that it executes line N7.3 and, finding Y = j, it executes return(), which contradicts our assumption and consequently proves the deadlock-freedom property.

#### 2.1.8 Mutual Exclusion in a Synchronous System

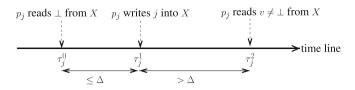

**Synchronous system** Differently from an asynchronous system (in which there is no time bound), a synchronous system is characterized by assumptions on the speed of processes. More specifically, there is a bound  $\Delta$  on the speed of processes and this bound is known to them (meaning that  $\Delta$  can be used in the code of the algorithms). The meaning of  $\Delta$  is the following: two consecutive accesses to atomic registers by a process are separated by at most  $\Delta$  time units.

Moreover, the system provides the processes with a primitive delay(d), where *d* is a positive duration, which stops the invoking process for a finite duration greater than *d*. The synchrony assumption applies only to consecutive accesses to atomic registers that are not separated by a delay() statement.

**Fischer's algorithm** A very simple mutual exclusion algorithm (due to M. Fischer) is described in Fig. 2.15. This algorithm uses a single atomic register X (initialized to  $\perp$ ) that, in addition to  $\perp$ , can contain any process identity.

When a process  $p_i$  invokes acquire\_mutex(*i*), it waits until  $X = \bot$ . Then it writes its identity into X (as before, it is assumed that no two processes have the same identity) and invokes delay( $\Delta$ ). When it resumes its execution, it checks if X contains its identity. If this is the case, its invocation acquire\_mutex(*i*) terminates and  $p_i$  enters the critical section. If  $X \neq i$ , it re-executes the loop body.

**Theorem 7** Let us assume that the number of processes is finite and all have distinct identities. Fischer's mutex algorithm satisfies mutual exclusion and deadlock-freedom.

*Proof* To simplify the statement of the proof we consider that each access to an atomic register is instantaneous. (Considering that such accesses take bounded duration is straightforward.)

Proof of the mutual exclusion property. Assuming that, at some time, processes invoke acquire\_mutex(), let *C* be the subset of them whose last read of *X* returned  $\perp$ . Let us observe that the ones that read a non- $\perp$  value from *X* remain looping in the

```

operation acquire_mutex(i) is

(1) repeat wait (X = \bot);

(2) X \leftarrow i;

(3) delay(\Delta)

(4) until (X = i) end repeat;

(5) return()

end operation.

operation release_mutex(i) is

(6) X \leftarrow \bot; return()

end operation.

```

Fig. 2.15 Fischer's synchronous mutex algorithm (code for  $p_i$ )

**Fig. 2.16** Accesses to X by a process  $p_i$

wait statement at line 1. By assumption, C is finite. Due to the atomicity of the register X and the fact that all processes in C write into X, there is a last process (say  $p_i$ ) that writes its identity into X.

Given any process  $p_i$  of C let us define the following time instants (Fig. 2.16):

- $\tau_i^0$  = time at which  $p_j$  reads the value  $\perp$  from X (line 1),

- $\tau_i^1$  = time at which  $p_j$  writes its identity j into X (line 2), and

- $\tau_i^2$  = time at which  $p_i$  reads X (line 4) after having executed the delay( $\Delta$ ) statement (line 3).

Due to the synchrony assumption and the delay() statement we have  $\tau_j^1 \le \tau_j^0 + \Delta$ (P1) and  $\tau_j^2 > \tau_j^1 + \Delta$  (P2). We show that, after  $p_i$  has written *i* into *X*, this register remains equal to *i* until  $p_i$  resets it to  $\perp$  (line 6) and any process  $p_j$  of *C* reads *i* from X at line 4 from which follows the mutual exclusion property. This is the consequence of the following observations:

- τ<sup>1</sup><sub>j</sub> + Δ < τ<sup>2</sup><sub>j</sub> (property P2),

τ<sup>0</sup><sub>i</sub> < τ<sup>1</sup><sub>j</sub> (otherwise p<sub>i</sub> would not have read ⊥ from X at line 1),

- 3.  $\tau_i^0 + \Delta < \tau_i^1 + \Delta$  (adding  $\Delta$  to both sides of the previous line),

- 4.  $\tau_i^1 \le \tau_i^0 + \Delta < \tau_j^1 + \Delta < \tau_j^2$  (from P1 and the previous items 1 and 3).

It then follows from the fact that  $p_i$  is the last process which wrote into X and  $\tau_i^2 > \tau_i^1$ that  $p_i$  reads i from X at line 4 and consequently does enter the **repeat** loop again and waits until  $X = \bot$ . The mutual exclusion property follows.

Proof of the deadlock-freedom property. This is an immediate consequence of the fact that, among the processes that have concurrently invoked the operation acquire\_mutex(), the last process that writes  $X(p_i \text{ in the previous reasoning})$  reads its own identity from X at line 4.

**Short discussion** The main property of this algorithm is its simplicity. Moreover, its code is independent of the number of processes.

#### 2.2 Mutex Based on Specialized Hardware Primitives

The previous section presented mutual exclusion algorithms based on atomic read/ write registers. These algorithms are important because understanding their design and their properties provides us with precise knowledge of the difficulty and subtleties

that have to be addressed when one has to solve synchronization problems. These algorithms capture the essence of synchronization in a read/write shared memory model.

Nearly all shared memory multiprocessors propose built-in primitives (i.e., atomic operations implemented in hardware) specially designed to address synchronization issues. This section presents a few of them (the ones that are the most popular).

#### 2.2.1 Test&Set, Swap, and Compare&Swap

The test&set()/reset() primitives This pair of primitives, denoted test&set() and reset(), is defined as follows. Let X be a shared register initialized to 1.

- *X*.test&set() sets *X* to 0 and returns its previous value.

- *X*.reset() writes 1 into *X* (i.e., resets *X* to its initial value).

Given a register X, the operations X.test&set() and X.reset() are atomic. As we have seen, this means that they appear as if they have been executed sequentially, each one being associated with a point of the time line (that lies between its beginning and its end).

As shown in Fig. 2.17 (where r is local variable of the invoking process), solving the mutual exclusion problem (or equivalently implementing a lock object), can be easily done with a test&set register. If several processes invoke simultaneously X.test&set(), the atomicity property ensures that one and only of them wins (i.e., obtains the value 1 which is required to enter the critical section). Releasing the critical section is done by resetting X to 1 (its initial value). It is easy to see that this implementation satisfies mutual exclusion and deadlock-freedom.

**The** swap() **primitive** Let X be a shared register. The primitive denoted X.swap(v) atomically assigns v to X and returns the previous value of X.

Mutual exclusion can be easily solved with a swap register X. Such an algorithm is depicted in Fig. 2.18 where X is initialized to 1. It is assumed that the invoking process

```

\begin{array}{l} \textbf{operation} \ \texttt{acquire\_mutex}() \ \textbf{is} \\ \textbf{repeat} \ r \leftarrow X.\texttt{test}\&\texttt{set}() \ \textbf{until} \ (r=1) \ \textbf{end} \ \textbf{repeat}; \\ \texttt{return}() \\ \textbf{end operation}. \\ \textbf{operation} \ \texttt{release\_mutex}() \ \textbf{is} \\ X.\texttt{reset}(); \ \texttt{return}() \\ \textbf{end operation}. \end{array}

```

Fig. 2.17 Test&set-based mutual exclusion

```

\begin{array}{l} \textbf{operation} \ \texttt{acquire\_mutex}() \ \textbf{is} \\ r \leftarrow 0; \\ \textbf{repeat} \ r \leftarrow X.\texttt{swap}(r) \ \textbf{until} \ (r=1) \ \textbf{end repeat}; \\ \texttt{return}() \\ \textbf{end operation}. \\ \textbf{operation release\_mutex}() \ \textbf{is} \\ X.\texttt{swap}(r); \ \texttt{return}() \\ \textbf{end operation}. \end{array}

```

Fig. 2.18 Swap-based mutual exclusion

does not modify its local variable *r* between acquire\_mutex() and release\_mutex() (or, equivalently, that it sets *r* to 1 before invoking release\_mutex()). The test&set-based algorithm and the swap-based algorithm are actually the very same algorithm.

Let  $r_i$  be the local variable used by each process  $p_i$ . Due to the atomicity property and the "exchange of values" semantics of the swap() primitive, it is easy to see the swap-based algorithm is characterized by the invariant  $X + \sum_{1 \le i \le n} r_i = 1$ .

**The** compare&swap() **primitive** Let X be a shared register and *old* and *new* be two values. The semantics of the primitive X.compare&swap(*old*, *new*), which returns a Boolean value, is defined by the following code that is assumed to be executed atomically.

X.compare&swap(old, new) is if (X = old) then X  $\leftarrow$  new; return(true) else return(false) end if.

The primitive compare&swap() is an atomic conditional write; namely, the write of *new* into X is executed if and only if X = old. Moreover, a Boolean value is returned that indicates if the write was successful. This primitive (or variants of it) appears in Motorola 680x0, IBM 370, and SPARC architectures. In some variants, the primitive returns the previous value of X instead of a Boolean.

A compare&swap-based mutual exclusion algorithm is described in Fig.2.19 in which X is an atomic compare&swap register initialized to 1. (no-op means "no operation".) The **repeat** statement is equivalent to **wait** (*X*.compare&swap (1, 0)); it is used to stress the fact that it is an active waiting. This algorithm is nearly the same as the two previous ones.

#### 2.2.2 From Deadlock-Freedom to Starvation-Freedom

**A problem due to asynchrony** The previous primitives allow for the (simple) design of algorithms that ensure mutual exclusion and deadlock-freedom. Said differently, these algorithms do not ensure starvation-freedom.

```

operation acquire_mutex() is

repeat r \leftarrow X.compare&swap(1,0) until (r) end repeat;

return()

end operation.

operation release_mutex() is

X \leftarrow 1; return()

end operation.

```

Fig. 2.19 Compare&swap-based mutual exclusion

As an example, let us consider the test&set-based algorithm (Fig. 2.17). It is possible that a process  $p_i$  executes X.test&set() infinitely often and never obtains the winning value 1. This is a simple consequence of asynchrony: if, infinitely often, other processes invoke X.test&set() concurrently with  $p_i$  (some of these processes enter the critical section, release it, and re-enter it, etc.), it is easy to construct a scenario in which the winning value is always obtained by only a subset of processes not containing  $p_i$ . If X infinitely often switches between 1 to 0, an infinite number of accesses to X does not ensure that one of these accesses obtains the value 1.

**From deadlock-freedom to starvation-freedom** Considering that we have an underlying lock object that satisfies mutual exclusion and deadlock-freedom, this section presents an algorithm that builds on top of it a lock object that satisfies the starvation-freedom property. Its principle is simple: it consists in implementing a round-robin mechanism that guarantees that no request for the critical section is delayed forever. To that end, the following underlying objects are used:

- The underlying deadlock-free lock is denoted *LOCK*. Its two operations are *LOCK*.acquire\_lock(*i*) and *LOCK*.release\_lock(*i*), where *i* is the identity of the invoking process.

- An array of SWMR atomic registers denoted *FLAG*[1..*n*] (*n* is the number of processes, hence this number has to be known). For each *i*, *FLAG*[*i*] is initialized to *down* and can be written only by *p<sub>i</sub>*. In a very natural way, process *p<sub>i</sub>* sets *FLAG*[*i*] to *up* when it wants to enter the critical section and resets it to *down* when it releases it.

- *TURN* is an MWMR atomic register that contains the process which is given priority to enter the critical section. Its initial value is any process identity.

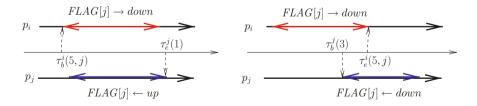

Let us notice that accessing FLAG[TURN] is not an atomic operation. A process  $p_i$  has first to obtain the value v of TURN and then address FLAG[v]. Moreover, due to asynchrony, between the read by  $p_i$  first of TURN and then of FLAG[v], the value of TURN has possibly been changed by another process  $p_i$ .

The behavior of a process  $p_i$  is described in Fig. 2.20. It is as follows. The processes are considered as defining a logical ring  $p_i$ ,  $p_{i+1}$ , ...,  $p_n$ ,  $p_1$ , ...,  $p_i$ . At any time,

```

operation acquire_mutex(i) is

(1) FLAG[i] \leftarrow up;

(2) wait (TURN = i) \lor (FLAG[TURN] = down);

(3) LOCK.acquire_lock(i);

(4) return()

end operation.

operation release_mutex(i) is

(5) FLAG[i] \leftarrow down;

(6) if (FLAG[TURN] = down) then TURN \leftarrow (TURN \mod n) + 1 end if;

(7) LOCK.release_lock(i);

(8) return()

end operation.

```

**Fig. 2.20** From deadlock-freedom to starvation-freedom (code for  $p_i$ )

the process  $p_{TURN}$  is the process that has priority and  $p_{(TURN \mod n)+1}$  is the next process that will have priority.

- When a process  $p_i$  invokes acquire\_mutex(i) it first raises its flag to inform the other processes that it is interested in the critical section (line 1). Then, it waits (repeated checks at line 2) until it has priority (predicate TURN = i) or the process that is currently given the priority is not interested (predicate FLAG[TURN] = down). Finally, as soon as it can proceed, it invokes LOCK.acquire\_lock(i) in order to obtain the underlying lock (line 3). (Let us remember that reading FLAG[TURN] requires two shared memory accesses.)

- When a process  $p_i$  invokes release\_mutex(*i*), it first resets its flag to *down* (line 5). Then, if (from  $p_i$ 's point view) the process that is currently given priority is not interested in the critical section (i.e., the predicate *FLAG*[*TURN*] = *down* is satisfied), then  $p_i$  makes *TURN* progress to the next process (line 6) on the ring before releasing the underlying lock (line 7).

**Remark 1** Let us observe that the modification of *TURN* by a process  $p_i$  is always done in the critical section (line 6). This is due to the fact that  $p_i$  modifies *TURN* after it has acquired the underlying mutex lock and before it has released it.

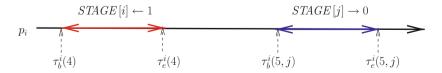

**Remark 2** Let us observe that a process  $p_i$  can stop waiting at line 2 because it finds TURN = i while another process  $p_j$  increases TURN to  $((i + 1) \mod n)$  because it does not see that FLAG[i] has been set to up. This situation is described in Fig. 2.21.

**Theorem 8** Assuming that the underlying mutex lock LOCK is deadlock-free, the algorithm described in Fig. 2.20 builds a starvation-free mutex lock.

*Proof* We first claim that, if at least one process invokes acquire\_mutex(), then at least one process invokes *LOCK*.acquire\_lock() (line 3) and enters the critical section.

Fig. 2.21 A possible case when going from deadlock-freedom to starvation-freedom

Proof of the claim. Let us first observe that, if processes invoke *LOCK*.acquire\_lock(), one of them enters the critical section (this follows from the fact that the lock is deadlock-free). Hence, *X* being the non-empty set of processes that invoke acquire\_mutex(), let us assume by contradiction that no process of *X* terminates the **wait** statement at line 2. It follows from the waiting predicate that *TURN*  $\notin$  *X* and *FLAG*[*TURN*] = *up*. But, *FLAG*[*TURN*] = *up* implies *TURN*  $\in$  *X*, which contradicts the previous waiting predicate and concludes the proof of the claim.

Let  $p_i$  be a process that has invoked acquire\_mutex(). We have to show that it enters the critical section. Due to the claim, there is a process  $p_k$  that holds the underlying lock. If  $p_k$  is  $p_i$ , the theorem follows, hence let  $p_k \neq p_i$ . When  $p_k$  exits the critical section it executes line 6. Let TURN = j when  $p_k$  reads it. We consider two cases:

1. FLAG[j] = up. Let us observe that  $p_j$  is the only process that can write into FLAG[j] and that it will do so at line 5 when it exits the critical section. Moreover, as TURN = j,  $p_j$  is not blocked at line 2 and consequently invokes LOCK.acquire\_lock() (line 3).

We first show that eventually  $p_j$  enters the critical section. Let us observe that all the processes which invoke acquire\_mutex() after *FLAG*[*j*] was set to *up* and *TURN* was set to *j* remain blocked at line 2 (Observation OB). Let *Y* be the set of processes that compete with  $p_j$  for the lock with y = |Y|. We have  $0 \le y \le n - 1$ . It follows from observation OB and the fact that the lock is deadlock-free that the number of processes that compete with  $p_j$  decreases from *y* to y - 1, y - 2, etc., until  $p_j$  obtains the lock and executes line 5 (in the worst case,  $p_j$  is the last of the *y* processes to obtain the lock).

If  $p_i$  is  $p_j$  or a process that has obtained the lock before  $p_j$ , the theorem follows from the previous reasoning. Hence, let us assume that  $p_i$  has not obtained the lock. After  $p_j$  has obtained the lock, it eventually executes lines 5 and 6. As TURN = j and  $p_j$  sets FLAG[j] to down, it follows that  $p_j$  updates the register TURN to  $\ell = (j \mod n) + 1$ . The previous reasoning, where k and j are replaced by j and  $\ell$ , is then applied again. 2. *FLAG*[*j*] = *down*. In this case,  $p_k$  updates *TURN* to  $\ell = (j \mod n) + 1$ . If  $\ell = i$ , the previous reasoning (where  $p_j$  is replaced by  $p_i$ ) applies and it follows that  $p_i$  obtains the lock and enters the critical section.

If  $\ell \neq i$ , let  $p_{k'}$  be the next process that enters the critical section (due to the claim, such a process does exist). Then, the same reasoning as in case 1 applies, where k is replaced by k'.

As no process is skipped when *TURN* is updated when processes invoke release\_mutex(), it follows from the combination of case 1 and case 2 that eventually case 1 where  $p_j = p_i$  applies and consequently  $p_i$  obtains the deadlock-free lock.

**Fast starvation-free mutual exclusion** Let us consider the case where a process  $p_i$  wants to enter the critical section, while no other process is interested in entering it. We have the following:

- The invocation of acquire\_mutex(*i*) requires at most three accesses to the shared memory: one to set the register *FLAG*[*i*] to *up*, one to read *TURN* and save it in a local variable *turn*, and one to read *FLAG*[*turn*].

- Similarly, the invocation by  $p_i$  of release\_mutex(*i*) requires at most four accesses to the shared memory: one to reset *FLAG*[*i*] to *down*, one to read *TURN* and save it in a local variable *turn*, one to read *FLAG*[*turn*], and a last one to update *TURN*.

It follows from this observation that the stacking of the algorithm of Fig. 2.20 on top of the algorithm described in Fig. 2.14 (Sect. 2.1.7), which implements a deadlock-free fast mutex lock, provides a fast starvation-free mutex algorithm.

#### 2.2.3 Fetch&Add

Let *X* be a shared register. The primitive *X*.fetch&add() atomically adds 1 to *X* and returns the new value. (In some variants the value that is returned is the previous value of *X*. In other variants, a value *c* is passed as a parameter and, instead of being increased by 1, *X* becomes X + c.)

Such a primitive allows for the design of a simple starvation-free mutex algorithm. Its principle is to use a fetch&add atomic register to generate tickets with consecutive numbers and to allow a process to enter the critical section when its ticket number is the next one to be served.