### Control-flow Integrity for Real-time Embedded Systems

by

Nicholas Brown

A Thesis

#### Submitted to the Faculty

of the

### WORCESTER POLYTECHNIC INSTITUTE

In partial fulfillment of the requirements for the

Degree of Master of Science

$\mathrm{in}$

Computer Science

by

May 2017

APPROVED:

Professor Robert J. Walls, Major Thesis Advisor

Professor Craig A. Shue, Thesis Reader

Professor Craig E. Wills, Head of Department

#### Abstract

As embedded systems become more connected and more ubiquitous in mission- and safety-critical systems, embedded devices have become a high-value target for hackers and security researchers. Attacks on real-time embedded systems software can put lives in danger and put our critical infrastructure at risk. Despite this, security techniques for embedded systems have not been widely studied. Many existing software security techniques for general purpose computers rely on assumptions that do not hold in the embedded case. This thesis focuses on one such technique, control-flow integrity (CFI), that has been vetted as an effective countermeasure against control-flow hijacking attacks on general purpose computing systems. Without the process isolation and fine-grained memory protections provided by a general purpose computer with a rich operating system, CFI cannot provide any security guarantees. This thesis explores a way to use CFI on ARM Cortex-R devices running minimal real-time operating systems. We provide techniques for protecting runtime structures, isolating processes, and instrumenting compiled ARM binaries with CFI protection.

# Contents

| 1        | Intr               | roduction 1                                |

|----------|--------------------|--------------------------------------------|

|          | 1.1                | Outline                                    |

| <b>2</b> | Bac                | kground and Related Works 3                |

|          | 2.1                | ARM Architecture                           |

|          |                    | 2.1.1 ARM/Thumb/Thumb2 Instruction Sets    |

|          |                    | 2.1.2 Processing Modes                     |

|          |                    | 2.1.3 Memory                               |

|          | 2.2                | Control-Flow Integrity                     |

|          |                    | 2.2.1 Threat Model                         |

|          |                    | 2.2.2 How CFI Works                        |

|          |                    | 2.2.3 CFI Variations                       |

|          |                    | 2.2.4 Existing CFI Implementations         |

|          |                    | 2.2.5 Limitations of CFI                   |

|          | 2.3                | Real-Time Operating Systems                |

|          |                    | 2.3.1 FreeRTOS                             |

| 3        | Cor                | ntrol-Flow Integrity on ARM Cortex-R 17    |

|          | 3.1                | Design Goals                               |

|          | 3.2                | System Model                               |

|          | 3.3                | Threat Model         18                    |

|          | 3.4                | Approach                                   |

|          | 0                  | 3.4.1 Binary Instrumentation               |

|          |                    | 3.4.2 Shadow Stack                         |

| 4        | CFI                | I Integration into FreeRTOS 25             |

| -        | 4.1                | Design Goals                               |

|          | 4.2                | System Model                               |

|          | 4.3                | Threat Model     26                        |

|          | 4.4                | Approach                                   |

|          |                    | 4.4.1         Shadow Stacks         27     |

|          |                    | 4.4.2         FreeRTOS Tasks         28    |

|          |                    | 4.4.3         Context Switching         28 |

| 5        | Fue                | luation 31                                 |

| J        | <b>ь</b> vа<br>5.1 | Security Evaluation                        |

|          | 0.1                | 5.1.1 Basic Exploitation Test (BET)        |

|          | 5.2                | -                                          |

|          | 0.2                | Performance Impact                         |

|     | 5.2.1  | CPU Benchmarks          | 34 |

|-----|--------|-------------------------|----|

|     | 5.2.2  | FreeRTOS Performance    | 35 |

|     | 5.2.3  | Additional Resource Use | 36 |

| 5.3 | Discus | sion                    | 37 |

|     | 5.3.1  | Limitations             | 37 |

|     | 5.3.2  | Future Work             | 38 |

|     |        |                         |    |

**40**

## 6 Conclusion

# **List of Figures**

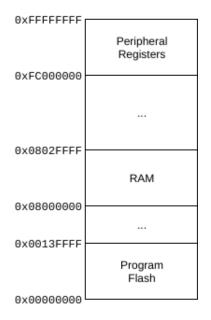

| 2.1 | Simplified memory map for RM46L852 processor [1]                                  | 6  |

|-----|-----------------------------------------------------------------------------------|----|

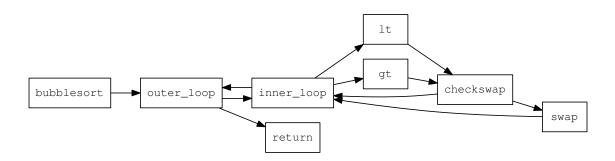

| 2.2 | Example CFG of a sorting function                                                 | 9  |

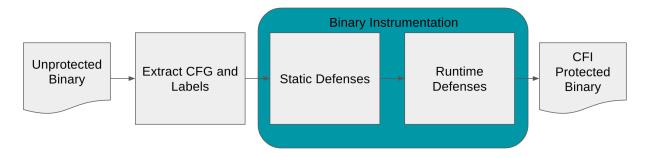

| 3.1 | Overview of our CFI system                                                        | 19 |

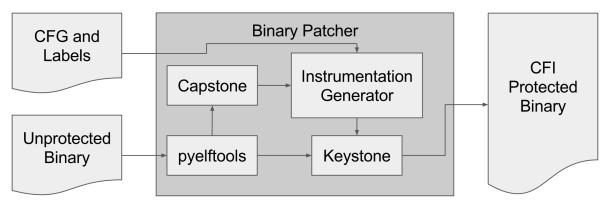

| 3.2 | Overview of binary patching system                                                | 19 |

| 3.3 | Input and output of the binary patching program                                   | 23 |

| 3.4 | Connection between the new .text section and the .cfi section                     | 23 |

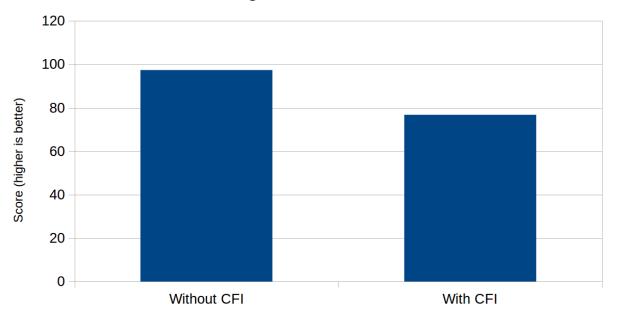

| 5.1 | CoreMark results with and without CFI. Default settings, 1000 iterations          | 35 |

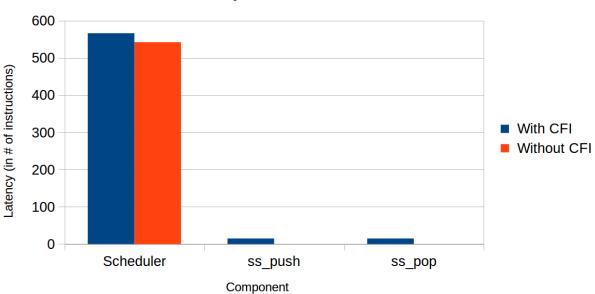

| 5.2 | Latency (in number of instructions) of CFI critical sections in FreeRTOS with two |    |

|     | running tasks                                                                     | 36 |

# **List of Tables**

| 2.1 | ARM processors and their features $[2]$          | 4  |

|-----|--------------------------------------------------|----|

| 2.2 | Register sets for ARM processing modes [3]       | 5  |

| 2.3 | Different indirect jump operations in ARM        | 9  |

| 2.4 | Different CFI implementations and their features | 12 |

# **List of Listings**

| 3.1 | C function to instrument                                     | 20 |

|-----|--------------------------------------------------------------|----|

| 3.2 | Selected portions of disassembly for foo() function          | 20 |

| 3.3 | Rewritten version of foo() function                          | 21 |

| 3.4 | Function prologue instrumentation                            | 21 |

| 3.5 | Indirect call instrumentation                                | 21 |

| 3.6 | Function epilogue instrumentation                            | 22 |

| 3.7 | Supervisor call handler                                      | 23 |

| 3.8 | Shadow stack type definition                                 | 24 |

| 3.9 | Shadow stack operations                                      | 24 |

| 4.1 | C type definition and declaration for multiple shadow stacks | 27 |

| 4.2 | FreeRTOS Task Control Block definition                       | 28 |

| 4.3 | FreeRTOS save context routine with shadow stack              | 29 |

| 4.4 | FreeRTOS restore context routine with shadow stack           | 30 |

| 5.1 | General format of indirect call instrumentation              | 33 |

| 5.2 | Function prologue and epilogue instrumentation               | 34 |

## Chapter 1

## Introduction

Modern real-time embedded systems have countless applications, varying in complexity. There are simple devices like thermostats or coffee makers, more complex systems like smartphone radios, and highly complex health and safety critical systems like jet engine controllers or automotive braking controllers. In safety critical systems especially, there is great risk when manufacturers release faulty devices. Failures in these systems can cause injury, and the designers of the system will be held liable [4]. Often these faults are in software and can be exploited by an intelligent adversary [5,6].

The most pernicious type of attack allows an attacker to execute arbitrary code on a device. Such attacks, commonly called control-flow hijacking, manipulate the execution of a program by redirecting control-flow transfers to either attacker-supplied code (e.g., stack smashing [7]) or useful code sequences already in the program (e.g., return-oriented programming [8]). State-of-the-art defenses against control-flow hijacking are largely based on the concept of control-flow integrity (CFI) [9]. Intuitively, CFI compares the behavior of a running program to a predefined model. If the program's behavior deviates from what is expected, an error is thrown. In particular, CFI monitors control-flow transfers and only allows a transfer if it is accepted by a precomputed controlflow graph (CFG) of the program. CFI is a subset of a larger category of security techniques called memory safety. While full memory safety is possible, the performance overhead (nearly 200% in some cases) makes it impractical for most applications [10,11]. CFI is an approach to memory safety on a small subset of memory, namely code pointers, which allows for significantly lower overhead as opposed to full memory safety.

While myriad CFI implementations exist for general-purpose systems (e.g., desktops and smartphones), real-time embedded systems present several unique challenges for CFI. First, many embedded systems do not have the hardware or software support for task isolation. Such isolation is common in general-purpose systems and relied upon by existing CFI solutions. Second, the scheduler in a real-time operating system (RTOS) can interrupt any instruction and can return to any arbitrary instruction. This makes the scheduler a high degree node in the CFG, which Carlini et al. have shown severely weakens the effectiveness of CFI [12]. Third, the majority of existing CFI solutions are for x86-based hardware, while embedded systems are commonly ARM-based, an architecture which has several challenges for CFI, such as multiple instruction sets and the lack of a dedicated function return instruction. Finally, real-time embedded systems generally have limited resources and strict timing requirements, limiting the amount of storage available for runtime structures required for CFI (e.g., shadow stacks). CFI instrumentation must adhere to the timing constraints in place by the real-time system.

We propose a CFI scheme for real-time embedded systems that addresses these challenges and prevents control-flow hijacking attacks. For our initial efforts, we focus on ARM-based systems running the FreeRTOS real-time operating system, but we anticipate that our system will be portable to any RTOS running on an ARM microcontroller, since the majority of the implementation is designed to be operating system agnostic. Existing approaches to CFI on embedded systems, such as C-FLAT [13] and TrackOS [14], move away from the traditional CFI approach but introduce new time-of-check to time-of-use vulnerabilities. Traditional approaches depend on process isolation in the presence of multiple threads, but most embedded systems do not have this isolation. Our work takes a more traditional approach to CFI, while adding the necessary protections to support multiple threads without true isolation using virtual memory. The contributions of this work are:

- Protection mechanisms for runtime data structures used by CFI. We protect the instrumentation required for CFI as well as the shadow stack, which is used to augment the CFG at runtime.

- **Binary instrumentation for ARM.** We create a reference implementation for ARM-based embedded systems running the FreeRTOS real-time operating system.

- Technique for process isolation on ARM systems without virtual memory. We devise a low-overhead method for isolating critical parts of a process on ARM systems where all processes run in the same address space.

- A binary patching implementation for ARM. We create a binary patching framework that allows scripting modification of precompiled ARM binaries to add features like CFI.

## 1.1 Outline

The remainder of this thesis is formatted as follows. Chapter 2 contains background information about ARM, CFI, and real-time operating systems. Chapter 3 describes our reference implementation for single-threaded, bare metal ARM systems. Chapter 4 describes the modifications made to FreeRTOS to support our bare metal implementation across multiple processes in the same address space. Chapter 5 evaluates the security and performance overhead of our CFI schemes. Finally, Chapter 6 summarizes this work and concludes the thesis.

## **Chapter 2**

## **Background and Related Works**

Before we can discuss the low-level details of control-flow integrity instrumentation on embedded ARM processors, we discuss the relevant background and related works which this thesis builds upon. We start with a brief overview of the embedded real-time ARM architecture, Cortex-R. Then, we discuss control-flow integrity, its variants, and its limitations. Finally, we explore some of the basic principles of real-time operating systems (RTOS), specifically FreeRTOS and the relevant differences between FreeRTOS and general purpose operating system kernels like Linux.

### 2.1 ARM Architecture

The ARM architecture is unique in how flexible it is. There are ARM chips designed for general purpose systems called the Application Profile (Cortex-A), high performance real-time systems called the Real-time Profile (Cortex-R), and low-power embedded systems called the Microcontroller Profile (Cortex-M). While all three of these profiles share a similar instruction set architecture (ISA), the underlying hardware is different to support different requirements. Cortex-A systems are often multi-core with high clock speeds, and they have all of the necessary hardware to efficiently run general purpose operating systems. Cortex-R processors are generally single core (although the more expensive models are multi-core), and they have special interrupt controllers and caching mechanisms to support the low-latency required by real-time systems. Cortex-M processors are single-core, with hardware designed for minimal power usage and security.

Table 2.1 highlights more of the differences between the different ARM lineups. In addition to belonging to ARM Cortex-A/R/M, ARM processors can be refined further based on the version of the architecture they support. At the time of this writing, modern ARM cores are either ARMv7 or ARMv8, with ARMv8 being widely adopted for Cortex-A models, while the ARMv8 versions of Cortex-R and Cortex-M processors have been announced. ARMv8 for Cortex-R (abbreviated ARMv8-R) introduces a new hypervisor mode that allows use of multiple real-time operating systems as well as efficient process isolation. While this feature could be highly beneficial for security purposes, these processors have not been made available yet, the remainder of this paper will be focusing on the ARMv7-R architecture. When ARMv8-R becomes more widely available, we believe

| Architecture | Bit-width | Profile         | Features                                                                                                                        |

|--------------|-----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------|

| ARMv7-A      | 32        | Application     | Multiple cores, MMU, TrustZone                                                                                                  |

| ARMv8-A      | 32/64     | Application     | Multiple cores, 64-bit support, MMU, TrustZone, hardware-accelerated cryptography                                               |

| ARMv7-R      | 32        | Real-time       | Single- or multi-core, tightly coupled caching, MPU, real-time clock                                                            |

| ARMv8-R      | 32        | Real-time       | Single- or multi-core, tightly coupled caching, MPU,<br>real-time clock, optional virtual memory, bare-metal<br>hypervisor mode |

| ARMv7-M      | 32        | Microcontroller | Single-core, low-power, Thumb2 ISA only, MPU                                                                                    |

| ARMv8-M      | 32        | Microcontroller | Single-core, low-power, Thumb2 ISA only, MPU, TrustZone-M                                                                       |

Table 2.1: ARM processors and their features [2]

that the hypervisor mode will strengthen the security benefits this work provides (see Section 5.3.1 for more details).

Even after the release of ARMv8-R, the current ARMv7-R devices will still be in use. It would be impractical and expensive for manufacturers to replace all existing ARMv7-R hardware. Firmware updates, on devices that support them, are a much more practical way to add new features or fix bugs.

#### 2.1.1 ARM/Thumb/Thumb2 Instruction Sets

Unlike other common architectures, ARM chips can operate on several different instruction sets. Most modern ARM cores support the ARM, Thumb, Thumb2, and ThumbEE ISAs. Some older ARM cores also support the Jazelle DBX (Direct Bytecode eXectution), which provides hardware support for executing Java bytecode. Additionally, ARM provides a standard interface for interacting with coprocessors such as hardware floating point units and the ARM Memory Protection Unit (MPU). Because our work exists mostly at the assembly language and machine code level, we need an understanding of the low level details of the ARM instruction set.

All ARM devices have 16 32-bit registers (R0-R15) and two status registers. Of the 16 32-bit registers, 4 have special purposes. R15 is reserved for use as the program counter (PC), R14 is the link register (LR), R13 is the stack pointer (SP), and R12 is the intra-procedure-call scratch register (IP). By convention, R0-R3 are used for function arguments, R4-R11 are used for temporary variables, and R0 is used for function return values. Registers R0-R7 are called the *Lo* registers, and R8-R15 are called the *Hi* registers. The Hi registers cannot be accessed by most 16-bit Thumb instructions, but they can be accessed by 32-bit Thumb instructions. All registers can be accessed from the ARM instruction set. The current program status register (CPSR) contains flags representing the current processing mode and status bits for conditional operations. The saved program status register (SPSR) is used during exception handling to restore the CPSR upon returning to normal processing.

| Mode          | Shared Registers | <b>Banked Registers</b> |

|---------------|------------------|-------------------------|

| System & User | R0-R15, CPSR     | None                    |

| FIQ           | R0-R7, CPSR      | R8-R15, SPSR            |

| Supervisor    | R0-R12, CPSR     | R13-R14, SPSR           |

| Abort         | R0-R12, CPSR     | R13-R14, SPSR           |

| IRQ           | R0-R12, CPSR     | R13-R14, SPSR           |

| Undefined     | R0-R12, CPSR     | R13-R14, SPSR           |

Table 2.2: Register sets for ARM processing modes [3]

The ARM Procedure Call Standard [15] dictates that ARM subroutines must preserve the values of R4-R11 and LR. This means that if the subroutine calls any other subroutines using the branch-and-link instruction, it must push LR to the stack before the subroutine call.

#### 2.1.2 Processing Modes

ARM processors can have up to nine different processing modes. On Cortex-R processors, there are only seven processing modes: User, System, Supervisor, Interrupt, Fast Interrupt, Abort, and Undefined. User and System modes are normal processing modes, while the other five modes are different types of exception states. In this section, we describe the main characteristics of these modes. Many of the registers are shared between modes, but there are some exceptions where the processing mode has its own banked registers that do not interfere with the registers in other modes. The banked registers for each mode are shown in Table 2.2. Our work depends on various ARM processing modes to perform operations at different privilege levels. Specifically, we use User, System, Supervisor, and IRQ mode.

User and System mode are similar, except System mode runs in a privileged state, allowing it to access regions of memory marked as privileged-only by the MPU. Unlike the other states, the majority of processing should be performed in either User or System mode.

When an ARM processor boots, the first code that executes is the reset routine. In the reset routine, the processor mode is set to Supervisor mode, which is a privileged mode that is designed for use as kernel mode for an operating system. Additionally, supervisor mode is used when handling a software interrupt (svc) instruction. This instruction can be used to implement system calls that need elevated privileges. Supervisor mode, along with all of the other exception modes, has a banked stack pointer register (SP\_svc), link register (LR\_svc), and saved program status register (SPSR\_svc). These allow Supervisor mode to have its own stack, while also preventing it from modifying the previous mode's link register. The banked registers cannot be accessed by other processing modes. The SPSR is used to restore the previous program status upon exiting the exception state.

When external hardware generates an interrupt request, the processor will handle the interrupt in either Interrupt or Fast Interrupt Mode. Like Supervisor mode, both interrupt modes have banked SP, LR, and SPSR registers. The main difference between FIQ and IRQ modes is that FIQ

Figure 2.1: Simplified memory map for RM46L852 processor [1]

mode also has its own banked R8-R12, which means the FIQ service routine can use these registers for processing without saving them to the stack first. This allows FIQ requests to be handled much faster, which has various uses for fast data transfers or other tasks that need low latency responses. FIQ mode is also the only mode that can interrupt IRQ mode by default.

There are two kinds of aborts in ARM, prefetch aborts and data aborts. Prefetch aborts occur when the processor attempts to execute an instruction after a failed instruction fetch. This will occur when the processor tries to fetch an instruction from memory that is not executable, such as peripheral registers or regions marked non-executable by the MPU. Data aborts occur when the processor attempts to read or write data to memory that the memory system does not allow. In particular, this would include an attempt to write to flash memory from the CPU or an attempt to write to privileged memory from User Mode. In a general purpose operating system, an abort would likely result in a segmentation fault. In an embedded context, the default action is to enter an infinite loop or reset the CPU. Abort mode can be used in debugging, since the default handler will allow the developer to view the register state, while LR\_abt will indicate which instruction caused the abort.

The final mode that ARMv7-R processors can use is Undefined mode. This mode is entered when the processor attempts to execute an opcode that it does not recognize. The intuition behind this exception state is to allow developers to implement instructions entirely in software, albeit at a high performance cost. For example, if a compiler does not support a certain coprocessor, the Undefined exception could allow the programmer to still use that coprocessor in a generic way.

#### 2.1.3 Memory

All modern ARMv7 processors have a 32-bit address space. The layout of this memory is manufacturer and processor dependent, but in general, there are three important sections: non-volatile flash memory, volatile RAM, and memory-mapped peripheral registers. Flash memory stores program code and constants, and it may be used for non-volatile storage of data between reboots, although special procedures are required to write to flash memory. RAM is used for all volatile storage and may be used for executable code, if allowed by the Memory Protection Unit (MPU). The peripheral registers are used to configure various hardware on the chip, such as timers, analog-to-digital converters, and direct memory access controllers. All of these regions of memory exist in the same address space. Without protections, these regions could be exploited by an attacker to perform arbitrary read and write operations.

The reference system used for this work is a Texas Instruments Hercules RM46L852, an ARM Cortex-R4F processor. The full memory map for this processor is shown in Figure 2.1. We can see that this processor has 1.25 MB of non-volatile program flash, 192 KB of RAM, and an additional 64 KB of flash for emulated EEPROM storage. These three sections of actual memory do not fill up the entire 32-bit address space. Some of the additional sections include memory-mapped peripherals, mirrored images of flash, and reserved sections that may be used internally by the processor or not used at all.

Each of the sections of this address space has hardware limitations as to whether or not they can be written, read, or executed. Some sections will cause aborts, while others may just have no effect when trying to read or write. For more fine-grained memory permissions, most ARM Cortex-M and Cortex-R processors come with a Memory Protection Unit (MPU). The MPU enables setting up permissions for up to 12 regions of memory. For each region, there are three sets of permissions to be set: user mode access, privileged mode access, and execute permissions. For example, a region can be configured to be read-only for user mode, read and write for privileged mode, and non-executable (in any mode). Our work depends heavily on the MPU to create some isolation between privileged and non-privileged modes. MPU regions can be split into 8 subregions, where each subregion can be selectively disabled or enabled. Additionally, the main regions can overlap; the overlapped region will take on the permissions of the highest priority region. MPU violations result in a data abort, allowing the processor to reset or perform some kind of error correction. While not as powerful as a full memory management unit, the MPU can be used to set up some separation between user mode and kernel mode, although it was designed more as a safety feature than a security feature.

## 2.2 Control-Flow Integrity

Control-flow integrity (CFI) defends against control-flow hijacking attacks by ensuring that a given program follows a precomputed model of execution, called a control-flow graph (CFG). The intuition behind CFI is that if we are able to protect indirect control flow transfers, that is, any change in control flow computed at runtime, we prevent arbitrary code execution. Unlike other memory safety techniques [10,11], CFI is fast and each CFI check runs in constant time. In the remainder of this section, we discuss the intricacies of CFI, including the general implementation details and existing variants of CFI.

#### 2.2.1 Threat Model

CFI schemes attempt to prevent exploitation under a powerful attacker model. The attacker is able to modify anything in writeable memory, including any data on the stack, heap, or in global memory. The attacker cannot, however, modify any read-only memory. Specifically, the attacker cannot modify program code, which is a common assumption, since most operating systems mark the program code section as being only readable and executable. Additionally, for CFI to be secure, an attacker must not be able to execute from any writeable memory.

The attacker's goal is to subvert the expected control flow of a program by modifying *code pointers* stored in memory or registers. A code pointer is any pointer that points to executable code. A function pointer is a type of code pointer. By modifying a code pointer, the attacker is modifying the target of an *indirect branch* instruction, which is any branch instruction where the target is calculated at runtime, rather than being statically inserted by the compiler. In ARM, an indirect branch is one of two kinds of instructions: (1) a branch instruction with a register operand, or (2) any operation with the program counter (PC) register as the destination. These instructions are enumerated in Table 2.3.

### 2.2.2 How CFI Works

All CFI schemes depend on two components: a control-flow graph (CFG) and binary instrumentation. Additionally, secure CFI schemes require a protected shadow call stack [12]. CFI implementations must accomplish three tasks:

- 1. From the CFG, extract a labeling scheme for all indirect jump targets.

- 2. At each indirect jump target in the binary, insert a label.

- 3. At each indirect jump instruction, insert instrumentation that ensures the jump target contains the expected label.

Assume for now that we have a CFG (we will discuss generating the CFG later). The CFG is a directed graph where the nodes represent basic blocks in a program, and the edges represent legal control-flow transfers from one basic block to another. Most of the nodes will be the source of one or two edges, since the majority of control-flow modifying instructions are direct calls or conditional branches, which have one or two possible targets. However, when a basic block ends in an indirect call or branch, there are often many possible targets for that control-flow transfer. The CFG generation algorithm will hopefully have reduced the total number of possible targets for that instruction. Each of the targets for that indirect branch are considered equal in the labeling scheme.

| Mnemonic                            | Instruction                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bx Rm                               | Branch and exchange             | Branch to target address <i>Rm</i> , and exchange in-<br>struction set based on least significant bit (LSB)<br>of <i>Rm</i> . If LSB is set, switch to Thumb mode, else<br>switch to ARM mode                                                                                                                                                                                                                                         |

| blx <i>Rm</i>                       | Branch, link, and ex-<br>change | Branch to target address <i>Rm</i> , set link register, and exchange instruction set based on LSB of <i>Rm</i>                                                                                                                                                                                                                                                                                                                        |

| <pre>ldm{mode} Rm{!}, reglist</pre> | Load multiple                   | Load into registers in <i>reglist</i> , starting at address<br>in <i>Rm</i> . If <i>Rm</i> ! is specified, write back the final<br>address into <i>Rm</i> . Mode specifies the addressing<br>order: <i>ia</i> (increment after), <i>ib</i> (increment before),<br><i>da</i> (decrement after), <i>db</i> (decrement before). The<br>pseudo instruction ldmfd is for loading from a<br>full-descending stack. It is the same as ldmia. |

| pop reglist                         | Pop from stack                  | Same as ldmfd sp!, reglist                                                                                                                                                                                                                                                                                                                                                                                                            |

| rfe <i>Rn</i> { <i>!</i> }          | Return from exception           | Pop PC and CPSR off of the stack pointer spec-<br>ified by $Rn$ to return from an exception state. If<br>Rn! is specified, write back new stack top to $Rn$ .                                                                                                                                                                                                                                                                         |

Table 2.3: Different indirect jump operations in ARM

Figure 2.2: Example CFG of a sorting function

In general, a unique label is selected for each set of targets that has the same set of sources. This effectively results in a more permissive enforced CFG, but many CFI schemes take this approach because it offers improved performance, allowing label checks to be performed in constant time.

For example, imagine a sorting function that takes as an argument a pointer to a function that will perform the comparison between two elements. A possible CFG for this function is shown in Figure 2.2. The inner loop will call either the 1t or gt function. Since these two blocks have the same source block, they would be given the same label for CFI instrumentation.

There are two goals to CFI instrumentation: (1) inserting label checks at all indirect control-

flow transfers, and (2) labeling all possible indirect jump targets. To do this, every indirect jump is replaced with a few assembly instructions that attempt to read a label from some constant offset from the branch target address. The instrumentation then compares the label read from memory with a hardcoded label. If the labels match, the instrumentation continues with the original branch. If they do not match, then the code either jumps to some error handling code or exits, depending on the use case. In the case of an embedded system, the crash would be a good opportunity to safely shut down the system, preventing a control-flow violation from resulting in damage to an entity in the physical world.

The labels for CFI instrumentation must be chosen carefully. If the label appears coincidentally anywhere else in memory (except for a valid jump target), an attacker could circumvent CFI by overwriting a code pointer with an address that is the correct offset from the location where the label appears. Since an indirect jump may have multiple legal targets, this means that even a correct stateless CFI implementation may allow jumps that were not intended by the programmer. We will discuss this limitation further in Section 2.2.5. The other condition that each label must satisfy is that it should be side-effect free. Since the label is stored in executable code, the instrumentation should either ensure that the label is never executed, or it should be a side-effect free instruction. In the original CFI implementation, the x86 prefetch instruction was used to encode the label [9].

Another indirect jump that CFI instrumentation needs to handle differently is function returns. Unlike indirect calls, where there may be multiple targets, most functions should always return to their callsite. With a few exceptions, return addresses are stored on the stack, and can be overwritten by buffer overflows or other memory corruption techniques. To combat this, we instead store return addresses in a separate shadow stack in protected memory. The shadow stack should not be writeable except during the function prologue and epilogue. Unlike the other components of CFI, the shadow stack is not static. It is a dynamic component that enhances the precision of the CFG at runtime.

This section described the basic concepts behind implementing CFI. For a more concrete implementation example for ARM processors, see Chapter 3.

#### 2.2.3 CFI Variations

Since the original CFI publication in 2005, several variations of CFI have emerged. Some of these variations trade security for speed, while others may forgo exploit prevention to increase the probability of exploit detection.

The original CFI design can be described as *forward-edge CFI* with a shadow stack. Forwardedge CFI refers to the instrumentation of indirect calls and branches to constrain the number of possible targets. A purely forward-edge CFI approach would either ignore function returns (the backward-edge), or it would treat each return like another indirect branch. In the former case, all return address corruption attacks would be possible. In the latter case, an attacker would be able to use a function called from multiple locations as a way to make the control-flow jump between the various callsites of the function. The shadow stack ensures that functions return to their callsite, although this can degrade performance by adding a dynamic element to CFI.

Apart from choosing how to protect the backward-edge, another way that CFI implementations can vary is in their control-flow graph. CFG generation in the presence of indirect branches is an unsolved problem, since resolving indirect branches is believed to be as hard as pointer analysis. As a result, CFGs used to create the labeling scheme for CFI are imprecise. Because of this, and for performance reasons, some CFI approaches use a *coarse-grained* CFG. Instead of attempting to resolve all indirect branches targets, a coarse-grained CFG may adopt a simple policy for branch targets. For example, a coarse-grained policy for return instructions would be that the instruction preceding the return address is a call instruction. For function calls, a coarse-grained policy could be that the function at the target address matches the return type and argument types of the function pointer. While coarse-grained CFGs are simpler to generate and can make instrumentation faster, is has been shown that coarse-grained policies are not secure [12].

*Fine-grained* CFGs, by contrast, attempt to resolve indirect jumps to the smallest set of legal jump targets. Due to the difficulty of pointer analysis, fine-grained approaches, we cannot construct a *fully-precise* CFG. A fully-precise CFG is both complete and sound. For an individual node in the CFG, a complete analysis will not include any branch targets that are not actually taken by the program, and a sound analysis will always accept a legal branch target. In other words, completeness refers to eliminating false positives, while soundness refers to eliminating false negatives. False positives reduce security, while false negatives could break program functionality.

The CFG is a static component of CFI. Because it is precomputed and stateless, it makes CFI instrumentation faster and more deterministic with good cache locality. Unfortunately, even if we could create a fully-precise CFG, the overall precision of CFI could still be increased with knowledge of program state. This is where dynamic elements like shadow stacks can be used to enhance the security guarantees of CFI, at the cost of performance. While shadow stacks are a simple solution to protect function returns, normal indirect branches with a large target set could be exploited to branch to an unexpected location given the current program state. These kinds of branches are called *dispatchers* and they could allow attackers to perform return-oriented programming (ROP) attacks, where useful sequences of existing instructions are chained together by return instructions and a maliciously crafted stack. Each sequence of instructions is called a gadget, and gadgets are linked together in ROP chains to perform more complex computation. Some of the proposed CFI schemes reduce the effectiveness of dispatchers by using more program context. For example, some schemes record multiple control flow transfers, and periodically compare the resulting paths against the CFG. While this can result in a more precise measurement of control flow, it can allow an exploit to occur before detection, which may be undesirable depending on the application.

With all of these variations in mind, the theoretical golden standard of CFI is fully-precise CFI with a shadow stack. If we were able to create a sound and complete CFG, this variation would provide the best tradeoff between security and performance, since control flow cannot be exploited, label checks and the shadow stack have low overhead compared to more dynamic approaches.

|                 | Original CFI [9] | binCFI [16] | Modular CFI [17] | MoCFI [18] | KCoFI [19]  | C-FLAT [13] | TrackOS [14] |

|-----------------|------------------|-------------|------------------|------------|-------------|-------------|--------------|

| Prevent Exploit | Y                | Y           | Y                | Y          | Y           | Ν           | N            |

| Detect Exploit  | Y                | Y           | Y                | Y          | Y           | Y           | Y            |

| Forward-edge    | Inline           | Inline      | Inline           | Inline     | Inline      | Record      | Record       |

| Backward-edge   | Shadow stack     | Inline      | Inline           | Inline     | Inline      | Record      | Record       |

| Granularity     | Fine             | Fine        | Fine             | Fine       | Coarse      | Fine        | Fine         |

| Static/Dynamic  | Both             | Static      | Static           | Both       | Static      | Dynamic     | Dynamic      |

| Architecture    | x86              | x86         | x86              | ARM        | x86         | ARM         | AVR          |

| AIR             | 99.13% [16]      | 98.86% [16] | 99.99% [17]      | Unknown    | 98.18% [19] | Unknown     | Unknown      |

Table 2.4: Different CFI implementations and their features

#### 2.2.4 Existing CFI Implementations

All of the variations discussed in Section 2.2.3 have been used in one or more CFI implementations. Table 2.4 highlights some of the CFI schemes relevant to this work and shows some of the defining features.

The original CFI proposal is a fine-grained approach with a shadow stack. Much of the theory behind CFI has not changed, and the original proposal remains one of the most secure and efficient variants today. The reference implementation actually took more of a coarse-grained approach, but the researchers identified that a more restrictive CFG would be more secure. This scheme was originally developed for 32-bit Windows XP, and has since been adopted by Microsoft as a compiler option called Control Flow Guard, which was introduced in Windows 8.1.

More recent CFI schemes are designed to work on precompiled binaries in the presence of dynamic linking. One of these implementations, binCFI [16], achieves similar security to the original CFI implementation without relying on relocation information from the compiler. One of the important outcomes of that work was a new metric for describing the precision of the control-flow graph: average indirect target reduction (AIR). The intuition behind the metric is that without CFI, an indirect branch can target any instruction, and the CFG reduces the size of the target set for each indirect branch. Equation 2.1 shows how AIR is calculated, where n is the number of indirect branches,  $T_j$  is the set of calculated targets for indirect branch j, and S is the number of possible targets in an unprotected program.

$$\frac{1}{n}\sum_{j=1}^{n}\left(1-\frac{|T_{j}|}{S}\right)$$

(2.1)

While AIR is not a perfect metric for evaluating CFI, it provides us with a quantitative measurement that gives us a way to sanity check our implementation. Acceptable AIR values are usually around 99% for a fine-grained practical implementation, while an extremely coarse-grained implementation (such as limiting indirect branches to any valid instruction boundary), could see an AIR of about 80%, depending on the architecture.

The majority of CFI schemes were developed for the x86 architecture. With mobile devices becoming more ubiquitous, some security research efforts, including CFI research, moved towards targeting the ARM architecture. Two of the first CFI schemes for ARM, MoCFI [18] and Controlflow Restrictor [20] were developed for Apple iOS devices. These CFI schemes identified and overcame some of the challenges associated with developing a CFI scheme on an ARM-based system. The main architectural challenges for CFI on ARM include:

- No dedicated return instruction

- Instructions can operate on the program counter

- Multiple instruction sets in a single binary

The original ARM CFI implementations only targeted iOS smartphones, but with the rise of the Internet of Things, ARM devices with no operating systems became more relevant. These embedded systems have qualities that make CFI a good potential hardening technique. For example, programs running without an operating system have no dynamic linking, which simplifies CFG generation. Additionally, some of the newer ARM Cortex-A and Cortex-M devices are shipping with a trusted execution environment called TrustZone, which could be used for measurement and attestation. Control Flow Attestation (C-FLAT) does exactly this; it leverages ARM TrustZone to implement a CFI scheme designed for embedded systems without operating systems [13]. Unlike traditional CFI, C-FLAT's instrumentation does not perform jump target checking. Rather, it records control-flow events, and periodically verifies the validity of each path from within a secure environment. Unfortunately, this dynamic approach introduces time-of-use to time-of-check vulnerabilities. C-FLAT will detect a control-flow violation, but it may not detect it until after malicious code has executed.

As we move on to discuss CFI on real-time ARM systems in Chapters 3 and 4, we are most interested in providing a better solution than C-FLAT and TrackOS, while taking a more traditional CFI approach. These two systems sacrifice some important safety-oriented security qualities of traditional CFI to avoid interfering with real-time functionality.

#### 2.2.5 Limitations of CFI

As we have alluded to in previous sections, CFI is not a perfect defense against control-flow hijacking attacks. There are some vulnerabilities that depend on the implementation details. Additionally, recent research has shown that even against fully-precise CFI with a shadow stack, certain types of gadgets are available and can be used to completely subvert CFI.

In coarse-grained CFI, few unique labels are used in the instrumentation, and a specific indirect branch may have many incorrect targets in its target set. It is possible that the branch may only have one or two intended targets, but the coarse-grained policy gave it ten targets. This means that the majority of targets should not be legal, but an attacker would be able to execute the eight or nine unintended targets in the target set. In fact, while coarse-grained policies do decrease the number of possible ROP gadgets, a control-flow hijacking attack is still trivial.

Dynamic CFI implementations that rely on recording control-flow events suffer from a *time-of-use to time-of-check* vulnerability. Because these systems only periodically attest that the control-flow events followed the CFG, they can allow an exploit to occur before detecting it. If an attacker

exploits a buffer overflow, the system will record the return to the corrupted address, and then continue executing. Only when it runs its verification task will it detect that an illegal control-flow event occurred. By that point, however, the damage will have been done, since the exploit already executed.

Even with fully-precise CFI with a shadow stack, programs can be vulnerable to *control-flow* bending, a type of attack that includes a new exploitation technique called *printf-oriented pro*gramming [12]. In this kind of attack, the attacker must be able to corrupt the arguments to a function like printf. It turns out that by controlling the arguments to a format string function, an attacker can gain Turing-complete computation without ever violating the CFG. This kind of vulnerability can be generalized as an *argument-corruptible indirect call site (ACICS)* gadget [21]. By being able to control the arguments to the function being called indirectly, it is possible for an attacker to gain arbitrary execution, especially if the ACICS gadget allows a call to system or the exec family of functions.

### 2.3 Real-Time Operating Systems

Often the main purpose of an embedded system is to monitor or control physical systems. For example, an embedded system may be controlling an electric motor in an automobile or it could be working alongside an application processor to provide some low-level communication protocol. In these cases, certain procedures must be performed in *real-time*, meaning that after an event occurs, the processor must perform the appropriate computation by a certain deadline. There are two kinds of real-time systems, *soft real-time* and *hard real-time*, where the former can tolerate missing some deadlines, while the latter cannot. In hard real-time systems, a missed deadline puts the entire system into an unknown—and often unsafe— state. To facilitate writing software with real-time requirements, embedded system designers often use a *real-time operating system (RTOS)*.

Depending on the processor being used, RTOSs can vary greatly in their complexity. On more powerful hardware, like ARM Cortex-A processors, real-time processing can be facilitated by using Linux compiled with SCHED\_DEADLINE or SCHED\_RT, which replace Linux's Completely Fair Scheduler (CFS) with real-time schedulers. On processors designed for embedded use, like the Cortex-R4F used for this work, the hardware often fails to meet the minimum requirements for Linux. For reference, in 2014, a minimally configured Linux kernel still required at least 8 MB of program flash and 1.6MB of RAM [22], which clearly will not work on our 1.25 MB of flash and 192 KB of RAM. The alternative to real-time Linux is using an embedded RTOS such as FreeRTOS, VxWorks, or  $\mu$ C/OS, which are designed to run on devices with storage space and memory on the scale of kilobytes, rather than megabytes or gigabytes.

In an embedded RTOS, processes are referred to as *tasks*. Tasks are most similar to a system service or daemon in a general purpose operating system; they generally do not exit and they execute periodically, often sleeping until they are signalled to do some work. Depending on the RTOS, there are different ways that the OS can schedule tasks. Often there is some flexibility

in choosing the type of scheduling; the most significant option being choosing between preemptive and nonpreemptive scheduling. In preemptive scheduling, the scheduler will run periodically during a timer interrupt, allowing tasks to be switched out at any time. In nonpreemptive scheduling, a task must willingly yield to the scheduler. The benefit of nonpreemptive scheduling is that it makes it much easier to reason about the schedulability properties of the system. A real-time system designer may use modeling software to prove that the system will not miss deadlines, and it is much simpler to model the system if the scheduler only runs at deterministic points in the application.

#### 2.3.1 FreeRTOS

One of the most common real-time operating systems is FreeRTOS. Designed to be as minimal as possible, this free and open source RTOS can fit in as small as 5 KB of program flash and can fit in under 1 KB of RAM, depending on the features used [23]. FreeRTOS is highly portable, with architecture specific ports existing for most major architectures. FreeRTOS, while minimal in nature, provides a few rich features such as mutexes, semaphores, shared queues, and software timers.

#### **Tasks and Memory Layout**

Tasks in FreeRTOS can be viewed as lightweight threads sharing the same address space and heap, but separate stacks. The kernel views tasks as an array of circular doubly linked lists of Task Control Blocks (TCBs), which each list containing all tasks of a certain priority. The TCB for each task maintains information including the pointer to the top of its stack, priority, and task state (ready, blocked, suspended). Optionally, this structure can include information about synchronization objects (e.g. mutexes) in use by the task, or it could maintain tracing information, if enabled.

At boot time, FreeRTOS only allocates a few global variables and a heap. When tasks are created, the TCB and task stacks are allocated in the FreeRTOS heap, which is shared between all tasks by default. Since the libc-provided alloc family of functions is not appropriate for real-time use, FreeRTOS provides its own dynamic memory allocation scheme. While this dynamic allocation can be used, static allocation is preferred since it is deterministic and does not require a critical section to access the shared heap.

#### Porting

The majority of FreeRTOS is written in architecture independent C code, but each port to a new architecture requires a few special files to be implemented. Since we will be discussing modifying FreeRTOS in Chapter 4, we will briefly look at these files now. There are three files that are required: portmacro.h, port.c, and portasm.S.

The first file that the FreeRTOS core depends upon is a C header file called portmacro.h, which creates the type abstractions and a few macros for architecture-specific actions like disabling and enabling interrupts. The type abstractions include defining StackType\_t and BaseType\_t, which represent the stack element type and word size, respectively. Additionally, this file defines some constants like the stack growth direction and addresses of peripheral registers.

The second file is a C source file called port.c. This C file must define important procedures like the stack initialization for a task, the real-time clock configuration, and the real-time tick interrupt. Even within one type of processor like the Cortex-R4, different vendors may have different ways to configure hardware peripherals.

The last file is portasm.S, which contains port-specific assembly code. Two of the most important parts of this file (which we will be discussing modifying in Chapter 4) are the portSAVE\_CONTEXT and portRESTORE\_CONTEXT assembly macros. The scheduler uses both of these macros to switch context between tasks. Since this procedure requires modifying specific registers, it must be implemented in assembly language rather than C.

## **Chapter 3**

## **Control-Flow Integrity on ARM Cortex-R**

Before implementing a CFI scheme on an ARM-based real-time operating system, the logical first step is creating a working CFI system on a bare metal ARM program. Since the existing ARM implementations either require an operating system or are unable to handle both Thumb and ARM, we implement our own instrumentation and shadow stack. The rest of this chapter outlines the design goals, system model, threat model, and approach to our implementation. The evaluation of our implementation is detailed in Chapter 5.

### **3.1 Design Goals**

The main goal of any CFI scheme is to make it difficult or impossible for an attacker to achieve arbitrary code execution. Our main design goal is to develop CFI instrumentation for the ARM and Thumb2 instruction sets that restricts control flow to prevent arbitrary code execution. As with previous work, we do not protect against arbitrary memory corruption vulnerabilities; rather we focus on preventing the exploitation of code pointer corruption. Our system will focus on the static label checks and runtime additions that CFI provides, rather than focusing on the CFG generation aspect of CFI. While it is shown that a CFI scheme is only as secure as its CFG is precise [12,16,21,24], we look to the literature for control flow graph generation [17,25,26], since CFG generation is beyond the scope of this project.

Performance and resource utilization are important aspects for any security software, but they are especially critical for embedded software. Performance overhead should be kept to a minimum, but most importantly, performance overhead should be deterministic. Embedded devices often have tight time constraints where guarantees about meeting these constraints are dependent on deterministic, bounded execution time. On general purpose computers, resource utilization is often overlooked; resources like disk space and RAM are abundant, so security software can often add significant resource usage without much penalty. On embedded devices, however, limited code storage and RAM means we need to take special care to minimize the additional code and runtime memory requirements for CFI.

There have been various theoretical and practical attacks against fine-grained CFI, including

Control Jujutsu [21] and Control-flow Bending [12]. While we recognize these attacks, we do not attempt to prevent them. Due to differences in programming paradigms for embedded systems, we believe that the likeliness of these attacks being possible on the majority of embedded devices is low. We discuss this more in Section 5.3.1.

### 3.2 System Model

The system that we are targeting with this work is the ARM Cortex-R processor, unlike previous work which targets the Cortex-A architecture [13,18,20]. The real-time features of the Cortex-R mean that it does not have virtual memory, and all memory protections are limited to the MPU hardware. Additionally, we assume that the application running on the processor can contain both ARM and Thumb instructions, and apart from any initialization code, any processing outside of an interrupt context is in User mode. Finally, as a requirement for CFI, at least two regions of the MPU will be used to disable writing to executable code while also preventing execution of writeable memory. The remaining regions can be used for any special memory protections required by CFI (e.g. shadow stack).

## 3.3 Threat Model

We assume the normal threat model for CFI implementations. We assume a powerful attacker model; without protections, the attacker can arbitrarily read and write to any memory at any time. This means that to meet the minimum requirements for CFI, we first need to apply memory protections. After memory protections are applied, the attacker is still able to read and write arbitrary memory at any time, but attempts to access to privileged-only memory from user mode will cause the device to crash. Since there are only two privilege levels, any code running in privileged mode must be critical to CFI and must not be vulnerable to memory corruption attacks. On general purpose systems this would be near-impossible to verify since privileged (i.e. kernel) code contains millions of lines of code, but in embedded systems, these sections of code are generally small, manually verifiable, and do not accept arbitrary external inputs. These sections are primarily used for handling hardware interrupts. While we cannot entirely discount vulnerabilities in privileged sections of code, it is much more likely that the bug causing the vulnerability would be fixed due to faults occuring without any malicious intent.

### 3.4 Approach

As discussed in Section 2.2, CFI implementations have two major parts: CFG generation and binary instrumentation. Since sound and precise CFG generation is believed to be undecideable [21], we do not attempt to improve upon existing CFG generation algorithms such as those presented in [25, 26], and instead focus on the binary instrumentation aspect of CFI. Our binary instrumentation

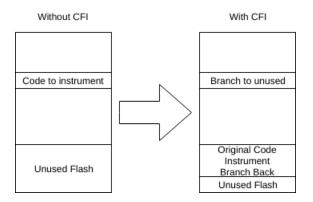

Figure 3.1: Overview of our CFI system

Figure 3.2: Overview of binary patching system

comprises two parts: static defenses and runtime defenses. The overview and workflow of this system is shown in Figure 3.1.

#### 3.4.1 Binary Instrumentation

One of the major design choices for this CFI implementation is the instrumentation type. There are two options: modify the compiler and add instrumentation at compile time or patch the binary after compilation. While the compiler-based approach would likely have better performance, the patching approach is able to add CFI to a compiled binary without needing source code. One benefit of being able to instrument a compiled binary is that we can retrofit security to an existing device that may never receive updates. We chose the patching approach due to the vast numbers of proprietary embedded systems that ship with precompiled firmware without source code available for recompilation. An overview of our binary patcher is shown in Figure 3.2

To perform the binary instrumentation required for CFI, we use the binary patching approach. In this approach, the main idea is to instrument instructions by replacing them with trampolines to new code appended to the unused flash memory section. The naive version of this algorithm is shown in Algorithm 1.

Unfortunately, real ARM machine code has some properties that make this patching more difficult depending on the instructions being patched. There are two main cases where patching

| Algorithm 1 | 1: | Patel | hing | al | lgorithm |

|-------------|----|-------|------|----|----------|

|-------------|----|-------|------|----|----------|

**input** : A binary *B*, Address to instrument  $A_i$ , target address  $A_t$ , instrumentation code *I* **output**: Patched binary with added trampoline and instrumentation

| 1 instruction $\leftarrow B[A_i];$      | // Save binary instruction at instrumentation address |

|-----------------------------------------|-------------------------------------------------------|

| 2 $I \leftarrow instruction + I;$       | // Prepend saved instruction to instrumentation       |

| 3 $B[A_i] \leftarrow$ branch to $A_t$ ; | // Insert branch at instrumentation address           |

| $4 \ B[A_t] \leftarrow I;$              | // Insert instrumentation at target address           |

becomes more complicated. The first is when the instruction being instrumented is a 16-bit Thumb instruction. The branch address required by the trampoline procedure has to be 32-bits, since ARM branches are PC-relative and we need to be able to encode a large offset to the unused flash section. The second case is when the instrumented instruction contains a PC-relative operation, since the new location of the instruction will have a different PC value.

To show how to handle these cases, we look to following toy example. Imagine we are trying to instrument the foo() shown in Listing 3.1. We want to instrument the function prologue, the indirect call, and the function epilogue. Looking at the disassembly of foo() when compiled in Thumb mode, we identify the instructions we need to instrument, shown in Listing 3.2.

Listing 3.1: C function to instrument

| 1 | <pre>int foo(int a, int b) {</pre>                |

|---|---------------------------------------------------|

| 2 | <pre>int (*func[2])(int, int) = {add, sub};</pre> |

| 3 | <pre>static unsigned int i = 0;</pre>             |

| 4 | <b>return</b> func[i++ % 2](a, b);                |

| 5 | }                                                 |

Listing 3.2: Selected portions of disassembly for foo() function

| 1 | 0x192: | <pre>push {r4, r7, lr}</pre> | #                           |

|---|--------|------------------------------|-----------------------------|

| 2 | 0x194: | <b>sub sp,</b> 20            | # Function Prologue         |

| 3 | 0x196: | add r7, sp, 0                | #                           |

| 4 |        |                              |                             |

| 5 | 0x1e6: | add r3, r3, r4               | #                           |

| 6 | 0x1e8: | blx r3                       | # Indirect Call             |

| 7 |        |                              |                             |

| 8 | 0x1f0: | mov sp, r7                   | #                           |

| 9 | Ox1f2: | <pre>pop {r4, r7, pc}</pre>  | # Function Epilogue / Retur |

|   |        |                              |                             |

In the function prologue, CFI requires that we push the return address to the shadow stack as well as embed a label according to the CFG. We need to replace 6 bytes of the function to encode both a 32-bit branch and a 16-bit label, as shown in Listing 3.3. We branch to the code shown in Listing 3.4, which modifies the original stack push operation to remove the link register from the

'n

Listing 3.3: Rewritten version of foo() function

| 1 | 0x192: | b.w 0x13f60     | New prologue branches to CFI section                |  |

|---|--------|-----------------|-----------------------------------------------------|--|

| 2 |        |                 |                                                     |  |

| 3 | 0x196: | <label></label> | Insert label after branch                           |  |

| 4 |        |                 |                                                     |  |

| 5 | 0x1e6: | bl 0x13f80      | Replace indirect call and previous instruction with |  |

| 6 |        |                 | branch to CFI section to do label checking          |  |

| 7 |        |                 |                                                     |  |

| 8 | 0x1f0: | b.w 0x13f98     | New epilogue branches to CFI section                |  |

|   |        |                 |                                                     |  |

register list, pushes the link register to the shadow stack, and returns to the instruction following the label placed in the original function prologue.

Listing 3.4: Function prologue instrumentation

| 1 | 0x13f60: | <pre>push {r4, r7}</pre> | <pre># Copy instructions from original prologue, but</pre>         |

|---|----------|--------------------------|--------------------------------------------------------------------|

| 2 | 0x13f62: | <b>sub sp,</b> 20        | <pre># remove link register from the push register list</pre>      |

| 3 | 0x13f64: | add r7, sp, 0            |                                                                    |

| 4 | 0x13f66: | <pre>push {r0}</pre>     | # Push r0 since we will need it                                    |

| 5 | 0x13f68: | mov r0, lr               | # Copy link register value into r0                                 |

| 6 | 0x13f6a: | svc 0                    | <pre># Call ss_push from supervisor mode (system call)</pre>       |

| 7 | 0x13f6c: | <pre>pop {r0}</pre>      | # Restore r0 value                                                 |

| 8 | 0x13f6e: | <b>b.w</b> 0x198         | <pre># Branch back to original function, skipping over label</pre> |

|   |          |                          |                                                                    |

Listing 3.5: Indirect call instrumentation

```

0x13f80: add r3, r3, r4

# Copy instruction from before branch

1

0x13f82: push {r0, r1}

# Push r0 and r1 since we will need them

2

0x13f84: ldrh r0, [r3, 3] # Load the label (halfword) from 3 bytes after branch target

3

0x13f86: movw r1, <label> # Load the expected label into r1

4

0x13f88: cmp r0, r1

# Compare r0 and r1

5

error:

6

0x13f8a: bne error

# If not equal, enter infinite loop

7

0x13f8c: pop {r0, r1}

# Restore r0 and r1

8

0x13d8e: bx r3

9

# Perform indirect jump

```

The indirect jump at address 0x1e8 in Listing 3.2 is a branch-link-and-exchange instruction with a register operand. This is a 16-bit indirect call, so we replace it and the preceding instruction with a direct branch-and-link operation. By using the branch-and-link operation, we ensure that the return address is copied into the link register for use by the called function. In the instrumentation code shown in Listing 3.5, we perform a label checking operation based on the target of the indirect call. If the labels match, we continue with the indirect call, but if not, we enter an infinite loop.

The function epilogue needs to reverse the operations done by the function prologue. Namely,

we need to restore registers pushed to the stack previously, and we need to restore the return address from the shadow stack. To do this, we again replace the two 16-bit instructions with a 32-bit branch instruction. In the instrumentation shown in Listing 3.6, we start by popping the return address off the shadow stack and moving it into the link register. We then modify the original pop instruction to remove copying of the link register into the program counter (since we removed pushing the link register in the prologue). Finally, we return using a branch-and-exchange to the link register.

Listing 3.6: Function epilogue instrumentation

| 2<br>3<br>4 | 0x13f9a:<br>0x13f9c: | mov lr, r0            | <pre># Perform pre-return operation that we overwrote # Push r0 so we can use it for return address # Call ss_pop from supervisor mode (system call) # Copy return value from ss_pop to link register # Restore r0</pre> |

|-------------|----------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | 0x13fa2:<br>0x13fa4: | pop {r4, r7}<br>bx lr | <pre># Perform original pop operation, without popping into pc # New return instruction</pre>                                                                                                                            |

|             |                      |                       |                                                                                                                                                                                                                          |

To implement this instrumentation, we use the Capstone<sup>1</sup> disassembly engine, the pyelftools<sup>2</sup> ELF file parser, and the Keystone<sup>3</sup> assembler. Capstone provides a powerful disassembly and instruction decomposition framework that makes it easy to identify the registers modified by any instruction. We search the executable for indirect branches and instructions that indirectly modify the program counter register (such as a load multiple operation where PC is a destination register). After enumerating the instructions that need instrumentation, we follow the simple procedure outlined in Algorithm 1 to generate the instrumentation. Finally, we use the Keystone assembler to compile the instrumentation code to machine code, and write the patched code to the binary file. We follow the same procedure for function prologues, epilogues, and indirect branch targets until we have a fully instrumented binary.

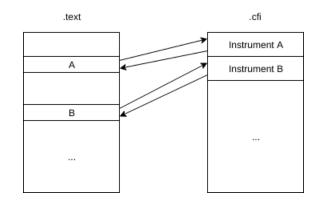

At a high level, the resulting binary follows the format shown in Figure 3.3. The code being instrumented is in the .text section, and the instrumentation goes into a new section called .cfi, as shown in Figure 3.4. Both of these sections are stored in flash memory, and are not modifiable at runtime.

#### 3.4.2 Shadow Stack

To implement a shadow stack, there are only two main requirements: a block of free memory and a way to protect this memory from unwanted access. On ARM Cortex-R, the best way to protect this memory is to make it inaccessible from the User processing mode, but allow read and write from the Supervisor mode. The procedure to perform shadow stack essentially requires creating a

<sup>&</sup>lt;sup>1</sup>http://www.capstone-engine.org/

<sup>&</sup>lt;sup>2</sup>https://github.com/eliben/pyelftools

<sup>&</sup>lt;sup>3</sup>http://www.keystone-engine.org/

Figure 3.3: Input and output of the binary patching program

Figure 3.4: Connection between the new .text section and the .cfi section

system call interface using the ARM Supervisor call (svc) instruction.

The Supervisor call instruction takes one operand, an immediate value representing the function number. When it executes, the svc instruction triggers an interrupt on the processor. The handler for this interrupt must determine the function number by reading the opcode of the software interrupt instruction. The ARM assembly code function to do this is shown in Listing 3.7.

| 1  | do_syscall:      |                                 |                                                               |

|----|------------------|---------------------------------|---------------------------------------------------------------|

| 2  | stmfd            | <pre>sp!, {r9,r10,r12,lr}</pre> | # Store registers                                             |

| 3  | mrs              | r9, spsr                        | <i># Move SPSR into general purpose register</i>              |

| 4  | tst              | r9, 0x20                        | # Occurred in Thumb state                                     |

| 5  | ldrneh           | r9, [lr, -2]                    | # Yes: load halfword and                                      |

| 6  | bicne            | r9, r9, 0xFF00                  | # extract function number field.                              |

| 7  | ldreq            | r9, [lr, -4]                    | # No: load word and                                           |

| 8  | biceq            | <b>r9, r9,</b> 0xFF000000       | # extract function number field.                              |

| 9  |                  |                                 | # r9 now contains SWI number                                  |

| 10 | cmp              | r9, 2                           | # Range check                                                 |

| 11 | ldr r            | 10, table                       | <pre># Load address of table</pre>                            |

| 12 | ldrls            | pc, [r10, r9, lsl 2]            | # Jump to the appropriate routine.                            |

| 13 | b                | <pre>svc_out_of_range</pre>     | <pre># Branch to error condition if number out of range</pre> |

| 14 |                  |                                 |                                                               |

| 15 | table:           |                                 |                                                               |

| 16 | .word jump_table |                                 |                                                               |

| 17 |                  |                                 |                                                               |

| 18 | jump_table:      |                                 |                                                               |

| 19 | .word ss_push    |                                 |                                                               |

| 20 | .word ss_pop     |                                 |                                                               |

|    |                  |                                 |                                                               |

#### Listing 3.7: Supervisor call handler

The actual shadow stack implementation is simple. We declare an array of bytes, ensuring that it is aligned to the size of an MPU region. For our reference implementation, we use a 256 byte shadow stack. The C definition of the shadow stack is shown in Listing 3.8. Upon system startup, the MPU is configured to make the shadow stack readable and writeable by privileged code, and not accessible at all by User mode code. Additionally, the shadow stack is set non-executable, like the rest of RAM. Shadow stack operations require a system call to switch to Supervisor mode, which is the mode for handling a software interrupt exception. Depending on the function required, we either perform a simple stack push or stack pop operation, and return to user mode. The short ARM assembly code functions for the shadow stack operations are shown in Listing 3.9.

#### Listing 3.8: Shadow stack type definition

```

1 typedef struct shadow_stack {

2     void *stack_top;

3     void *stack_base;

4     uint32_t size;

5     } shadow_stack;

6

7     volatile shadow_stack *current_ss;

```

#### Listing 3.9: Shadow stack operations

```

# Input: r0 containing value to push to shadow stack

1

2

# Returns: void

.type ss_push, %function

3

4

ss_push:

ldr r9, current_ss_const

# Load current shadow stack pointer

5

ldr r10, [r9]

# Load shadow stack top

6

stmfd r10!, {r0}

# Push r0 to shadow stack

7

str r10, [r9]

# Store new top of shadow stack

8

exit_syscall

# Syscall exit macro

9

10

# Input: void

11

# Returns: value at top of shadow stack -> r0

12

.type ss_pop, %function

13

ss_pop:

14

ldr r9, current_ss_const

# Load current shadow stack pointer

15

# Load shadow stack top

ldr r10, [r9]

16

ldmfd r10!, {r0}

# Pop from shadow stack to r0

17

str r10, [r9]

# Store new shadow stack top

18

exit_syscall

# Syscall exit macro

19

20

# Constant pointer reference to current_ss

21

.word current_ss

current_ss_const

22

```