# Cours d'électronique numérique

Maryam Siadat & Camille Diou

Version du 2 novembre 2004

# [ Notes sur cet ouvrage ]

Ce document est à la date d'aujourd'hui (2 novembre 2004) toujours en phase d'écriture. Il est donc nécessairement incomplet et peut même encore comporter des erreurs qui n'auraient pas été détectées.

Ce document doit notamment s'enrichir à l'avenir des points suivants (dans le désordre) :

- la logique mixte

- compléter la simplification des fonctions logiques

- méthode de Quine/McCluskey

- diagrammes de Venn, Johnston et Caroll

- familles logiques et spécifications électriques

- étude des systèmes programmables évolués (en complément du chapitre actuel)

- synthèse des systèmes séquentiels synchrones

- machines d'états (Moore, Huffman, Mealey)

- synthèse des systèmes séquentiels asynchrones

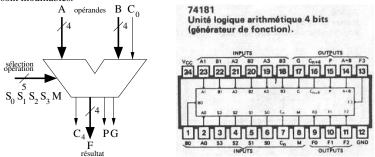

- arithmétique binaire et opérateurs arithmétiques

- compléter les exercices et corrigés

Ce document a été réalisé à l'aide des logiciels TEX et LATEX sous les environnements TEXLive et TeTEX. Les diagrammes sont réalisés à l'aide de Xy-pic. Une partie des schémas électronique est réalisée à l'aide du paquetage CIRC ...

La police utilisée pour le texte principale est Fourier.

Les descriptions bibliographiques/historiques présentes dans les entêtes de chapitres sont composée en DayRoman.

L'extrait du texte de Blaise Pascal du chapitre II est également composé dans la police DayRoman, mais dotée – notament – de la ligature & et du S long (s).

# Première partie Les nombres

# GChapitre I⊌

# Les systèmes de numération

Gottfried Wilhelm von Leibnitz ★ jui. 1646, Allemagne † 1716

Ce philosophe d'origine Allemande est l'inventeur d'une machine permettant de calculer directement les 4 opérations de base. Il est aussi celui qui a introduit la notion de binaire en Occident.

# I.1 La représentation polynomiale

Si nous manipulons les nombres de manière intuitive, c'est la plupart du temps dans la base décimale, naturelle et universelle. Mais cela ne doit pas masquer la nature même de la numération qui peut prendre plusieurs formes, parmi lesquelles on trouve la théorie des ensembles et la représentation polynomiale.

La représentation polynomiale d'un nombre est sa représentation sous la forme suivante :

$$a_{n-1}b^{n-1}$$

$a_{n-2}b^{n-2}$   $a_{n-3}b^{n-3}$   $\cdots$   $a_2b^2$   $a_1b$   $a_0$   $a_{-1}b^{-1}$   $a_{-2}b^{-2}$   $\cdots$   $a_{-m}b^{-m}$  où  $b$  est appelée la base.

Si la base 10 nous est familière, d'autres bases existent et les bases les plus utilisées en informatique sont les bases 10, 2, 8 et 16 appelées respectivement « décimale », « binaire », « octale » et « hexadécimale ».

Si la base 10 nous est familière, d'autres bases existent et les bases les plus utilisées en informatique sont les bases 10, 2, 8 et 16 appelées respectivement « décimale », « binaire », « octale » et « hexadécimale ».

# I.2 Le système binaire

#### I.2.1 Introduction

Le système décimal est malheureusement difficile à adapter aux mécanismes numériques, car il est difficile de concevoir du matériel électronique fonctionnant sur dix plages de tensions différentes.

On lui préférera donc le système binaire :

- base B=2;

- 2 symboles : {0,1} appelés « éléments binaires » ou « bits » (bit=Binary digIT);

- le système binaire est pondéré par 2 : les poids sont les puissances de 2 ;

les différentes puissances de 2 sont :

- un ensemble de 8 bits est appelé « octet » (ou byte).

# I.2.2 Comptage binaire

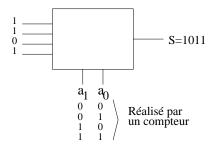

On présente les nombres binaires en général avec un nombre fixe de bits, nombre imposé par les circuits mémoires utilisés pour représenter ces nombres.

Suite des nombres binaires à 4 bits :

| Poids: | $2^{3}$ | $2^{2}$ | $2^1$ | $2^{0}$ | B10 |

|--------|---------|---------|-------|---------|-----|

|        | 0       | 0       | 0     | 0       | 0   |

|        | 0       | 0       | 0     | 1       | 1   |

|        | 0       | 0       | 1     | 0       | 2 3 |

|        | 0       | 0       | 1     | 1       | 3   |

|        | 0       | 1       | 0     | 0       | 4   |

|        | 0       | 1       | 0     | 1       | 5   |

|        | 0       | 1       | 1     | 0       | 6   |

|        | 0       | 1       | 1     | 1       | 7   |

|        | 1       | 0       | 0     | 0       | 8   |

|        | 1       | 0       | 0     | 1       | 9   |

|        | 1       | 0       | 1     | 0       | 10  |

|        | 1       | 0       | 1     | 1       | 11  |

|        | 1       | 1       | 0     | 0       | 12  |

|        |         |         |       |         |     |

Le bit le plus significatif – le bit le plus à gauche – est appelé « bit de poids fort » ou MSB (*Most Significant Bit*).

Le bit le moins significatif – le bit le plus à droite – est appelé « bit de poids faible » ou LSB (Less Significant Bit).

Si on utilise N bits, on peut représenter  $2^N$  valeurs différentes de  $2^0$  à  $2^{N-1}$

#### ⊳ Exemple 1.2

#### ► Remarque 1.1

Comme l'on traite souvent en micro-informatique de nombres à 8 ou 16 éléments binaires (e.b.), on se sert des systèmes :

- octal: à base 8;

- hexadécimal : à base 16.

# I.3 Le système octal

- base B=8;

- 8 symboles : {0,1,2,3,4,5,6,7};

L'intérêt de ce système est que la base 8 est une puissance de 2 (8  $2^3$ ), donc les poids sont aussi des puissances de 2.

Chaque symbole de la base 8 est exprimé sur 3 e.b. :  $(a_i)_8 \ b_{i_2} b_{i_1} b_{i_0}$

#### ⊳ Exemple 1.3

$(52,3)_8$  101 010,011

# I.4 Le système hexadécimal

- base B=16;

- 15 symboles : {0,1,2,...,9,*A*,*B*,*C*,*D*,*E*,*F*} appelés « digits » ;

- chaque symbole est exprimé en binaire sur 4 bits ;

#### ⊳ Exemple 1.4

$$(F3D,2)_{16}$$

1111 0111 1101,0010

# I.5 Conversion d'un système de numération à un autre

#### I.5.1 Base B vers base 10

$$(a_n \dots a_0)_B \ a_n B^{-n} \dots a_0 B^0 \ (a'_m \dots a'_0)_{10}$$

#### ⊳ Exemple 1.5

$$\begin{array}{c} (1001,1)_2 \ 1.2^3 \ 0.2^2 \ 0.2^1 \ 1.2^0 \ 1.2^{-1} \ 8 \ 0 \ 0 \ 1 \ 0,5 \ 9,5 \\ (A12)_{16} \ A.16^2 \ 1.16^1 \ 2.16^0 \ 2560 \ 16 \ 2 \ 2578 \end{array}$$

## I.5.2 Base 10 vers base B

#### I.5.2.a Première méthode

Elle consiste à soustraire successivement la plus grande puissance de B

#### ⊳ Exemple 1.6

100 1.2<sup>6</sup> 36

36 1.2<sup>5</sup> 4 }

$$\rightarrow$$

(100)<sub>10</sub> (1100100)<sub>2</sub>

4 1.2<sup>2</sup> 0

#### I.5.2.b Deuxième méthode

Elle consiste à diviser par *B* autant de fois que cela est nécessaire pour obtenir un quotient nul. Ensuite on écrit les restes dans l'ordre inverse de celui dans lequel ils ont été obtenus.

Pour la partie fractionnaire on multiplie par B (résultat nul ou selon la précision demandée)

#### ⊳ Exemple 1.7

$$(20,4)_{10}$$

(?)<sub>2</sub>

Partie entière:

Partie fractionnaire:

Le résultat est donc 10100,0110.

# I.5.3 Base $2^n$ vers base 2

Chaque symbole de la base  $B 2^n$  peut être représenté par n e.b.

#### ⊳ Exemple 1.8

$$\begin{array}{c} (3A9)_{16} \ (0011\ 1010\ 1001)_2 \\ (742,5)_8 \ (111\ 100\ 010,101)_2 \end{array}$$

## I.5.4 Base 2 vers base $2^n$

Il suffit de regrouper les e.b. par paquets de n e.b.

#### ⊳ Exemple 1.9

$$(1011011)_{2} \qquad \underbrace{(001)}_{1} \underbrace{011}_{3} \underbrace{011}_{3})_{2} \qquad (133)_{8}$$

$$\underbrace{(0101)}_{5} \underbrace{1011}_{B})_{2} \qquad (5B)_{16}$$

# I.5.5 Base i vers base j

- si i et j sont des puissances de 2, on utilise la base 2 comme relais;

- ⊳ Exemple 1.10

base

$$8 \rightarrow base 2 \rightarrow base 16$$

- sinon, on utilise la base 10 comme relais.

- ⊳ Exemple 1.11

base

$$5 \rightarrow$$

base  $10 \rightarrow$  base 2

# "Chapitre II<sub>⊌</sub>

# Codage des nombres dans les machines numériques

Blaise Pascal ★ 19 juin 1623, Clermont, France † 19 août 1662, Paris, France

« Ami lecteur, cet avertissement servira pour te faire savoir que j'expose au public une petite machine de mon invention, par le moyen de laquelle seul tu pourras, sans peine quelconque, faire toutes les opérations de l'arithmétique, et te soulager du travail qui t'a souvent fatigué l'esprit, lorsque tu as opéré par le jeton ou par la plume : je puis, sans présomption, espérer qu'elle ne te déplaira pas, après que Monseigneur le Chancelier l'a honorée de son estime, et que, dans Paris, ceux qui sont les mieux versés aux mathématiques ne l'ont pas jugée indigne de leur approbation. Néanmoins, pour ne pas paraître négligent à lui faire acquérir aussi la tienne, j'ai cru être obligé de t'éclairer sur toutes les difficultés que j'ai estimées capables de choquer ton sens lorsque tu prendras la peine de la considérer. »

(Blaife Pascal, Avis nécessaire à ceux qui auront curiosité de voir la machine d'arithmétique, et de s'en servir, 1645).

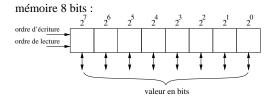

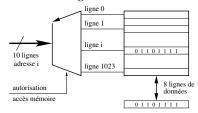

Les systèmes logiques sont constitués de mécanismes qui ne permettent de noter que 2 états : « 0 » ou « 1 ». Une mémoire élémentaire est donc une unité contenant « 0 » ou « 1 ». Plusieurs de ces unités sont assemblées pour représenter un nombre binaire.

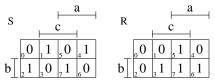

#### ⊳ Exemple 2.1

Ces mémoires sont indissociables et l'ordre d'assemblage donne le poids de chaque bit.

# II.1 Représentation des nombres entiers positifs

Les nombres sont représentés en binaire sur n bits : n = nombre d'unités mémoires  $(n \ 8.16.32.64...)$

On peut représenter des nombres allant de  $0 \ge 2^n - 1$ .

## II.2 Représentation binaire des entiers signés

Traditionnellement on met un signe « - » pour représenter les nombres négatifs. Mais les systèmes logiques ne permettent de présenter qu'un des deux symboles « 0 » et « 1 », il faut chercher une convention pour remplacer le « - ».

# II.2.1 Représentation module et signe

Solution la plus simple : on ajoute un e.b. à gauche du module pour le signe. Ainsi, un nombre commençant par un « 0 » sera positif, alors qu'un nombre commençant par un « 1 » sera négatif : {  $0 \leftrightarrow 0$  }

#### ⊳ Exemple 2.2

avec 4 e.b. Les valeurs vont de -7 à 7

| Signe | Module | Valeur | Signe | Module | Valeur |

|-------|--------|--------|-------|--------|--------|

| 1     | 111    | -7     | 0     | 111    | 7      |

| 1     | 110    | -6     | 0     | 110    | 6      |

| 1     | 101    | -5     | 0     | 101    | 5      |

| 1     | 100    | -4     | 0     | 100    | 4      |

| 1     | 011    | -3     | 0     | 011    | 3      |

| 1     | 010    | -2     | 0     | 010    | 2      |

| 1     | 001    | -1     | 0     | 001    | 1      |

| 1     | 000    | 0      | 0     | 000    | 0      |

**Problème :** on a ici deux représentations différentes pour le zéro : '00...0' et '10...0'.

# II.2.2 Représentation en complément restreint (complément à 1)

-A  $\overline{A}$ : pour prendre l'inverse d'un nombre, il suffit de le complémenter (inversion de tous ses bits). Comme dans le cas précédent, la nature du premier bit donnera le signe :  $\{ \begin{array}{c} 0 \leftrightarrow \\ 1 \leftrightarrow - \end{array} \}$

#### ⊳ Exemple 2.3

avec 4 e.b. :

$$\begin{cases} 5 \rightarrow 0101 \\ -5 \rightarrow 1010 \end{cases}$$

**Problème**: de nouveau, on a deux représentations différentes pour le zéro.

# II.2.3 Représentation en complément vrai (complément à 2)

C'est la représentation la plus utilisée. Le bit le plus à gauche est encore le bit de signe : {  $0\leftrightarrow 1\leftrightarrow -$

$$\begin{array}{ccc}

-A & \overline{A} & 1 \\

\overline{A} & \overline{a_{n-1}} \, \overline{a_{n-2}} \cdots \overline{a_0}^1 \\

A & 1 & 1 \cdots & 1 \\

1 & \overline{A} & A & 1 \leftarrow \underbrace{0 0 \dots 0}_{0}^2

\end{array}$$

$\Rightarrow$  -A  $\overline{A}$  1 est appelé compément à 2

#### ► Remarque 2.1

- pour passer d'une valeur négative à une valeur positive, on applique aussi le complément à 2;

- une seule représentation pour le zéro;

- avec des mots de n e.b., on obtient  $2^n$  valeurs différentes, de 0 à  $2^{n-1}$  1 pour les valeurs positives, et de -1 à  $-2^{n-1}$  pour les valeurs négatives ;

<sup>&</sup>lt;sup>1</sup>on complémente chaque coefficient

$<sup>^{2}</sup>$ car on représente sur *n* bits seulement

#### ⊳ Exemple 2.4

$$n \ 8 \Rightarrow \{ \begin{array}{l} \text{nb } 0 \text{ de } 0 \text{ à } 127 \\ \text{nb } 0 \text{ de } -1 \text{ à } -128 \end{array}$$

- $nb \ge 0 \rightarrow bit \ de \ signe \ 0 \ nb \ 0 \rightarrow bit \ de \ signe \ 1$

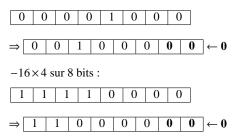

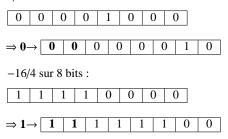

- pour représenter un nombre positif sur une mémoire de taille donnée, on complète les cases vides de gauche par des 0; pour représenter un nombre négatif sur une mémoire de taille donnée, on complète les cases vides de gauche par des 1;

#### ⊳ Exemple 2.5

+13 sur 8 bits : 00001101, -13 sur 8 bits : 11110011

# II.2.4 Représentation en code relatif à $2^{n-1}$

Les nombres x sont représentés par  $2^{n-1} x$ .

On constate ici que le bit de signe est inversé par rapport aux représentations précédentes : ce code est en fait identique au codage en complément à 2 avec le bit de signe complémenté.

On calcul l'inverse d'un nombre en relatif à  $2^{n-1}$  comme en complément à 2 en complémentant le nombre puis en ajoutant 1.

# II.3 Représentation des nombres réels dans un calculateur

Dans un calculateur, un nombre est toujours écrit sous forme d'1 bloc de n e.b. (considéré comme un entier N).

Pour représenter les nombres fractionnaires il est nécessaire de définir la position de la virgule : pour ce faire, il existe deux méthodes.

## II.3.1 La représentation en virgule fixe

On décide que la virgule est toujours à une position donnée (un entier peut être représentatif d'un nombre fractionnaire si on connaît la place de la virgule).

#### ⊳ Exemple 2.6

Virgule au rang K (K chiffres après la virgule):

La valeur N écrite en mémoire aura les poids suivants :

$$N \ 2^{N-1-K} \cdots 2^0 \ 2^{-1} \ 2^{-K}$$

$0 \le N \le (2^n-1)2^{-K}$

Virgule au rang 0:

$$N \ 2^{N-1} \cdots 2^{0}$$

$$0 \le N \le 2^N - 1$$

#### Inconvénient de la méthode :

problème de gestion de la virgule notamment dans les multiplications (pour les additions et soustractions pas de problème, la position de la virgule ne change pas);

#### ⊳ Exemple 2.7

Si on décide 2 symboles pour les parties entières et 2 symboles pour les parties fractionnaires, on ne peut plus écrire 256,1.

utilisation limitée lorsqu'on traite des données de grandeurs différentes, car on doit prendre un grand nombre de bit de part et d'autre de la virgule pour pouvoir représenter des grandeurs très faibles et des grandeurs très importantes.

# II.3.2 La représentation en virgule flottante simplifiée

#### II.3.2.a Introduction [WWW01]

Il arrive dans de nombreux domaines que l'intervalle des valeurs numériques pertinentes soit particulièrement étendu. L'astronomie en est un exemple extrême puisque certains calculs peuvent faire intervenir simultanément la masse du soleil  $(2.10^{30} \text{ kg})$  et la masse de l'électron  $(9.10^{-31} \text{kg})$ . Ces deux nombres diffèrent de plus de 60 ordres de grandeur  $(10^{60})$ !

Des calculs faisant intervenir ces nombres pourraient s'effectuer en précision multiple, avec par exemple des nombres de 62 digits. Tous les opérandes et tous les résultats seraient représentés par des nombres de 62 digits. Cependant, la masse du soleil n'est connue qu'avec une précision de 5 digits, et il n'y a en physique pratiquement aucune mesure que l'on puisse réaliser avec une précision de 62 digits. Une solution serait alors d'effectuer les calculs avec une précision de 62 digits et de laisser tomber 50 ou 60 d'entre eux avant d'annoncer les résultats, mais ceci est coûteux à la fois en espace mémoire et en temps de calcul.

En fait, ce qu'il faut est un système permettant de représenter des nombres, tel que la taille de l'intervalle des nombres "exprimables" soit indépendante du nombre de digits significatifs.

#### II.3.2.b Principe de la représentation en virgule flottante

Le nombre N est représenté sous la forme :

| exposant | mantisse |

|----------|----------|

#### 1ère approche

Soit

$$N \ a_3 \ a_2 \ a_1 \ a_0$$

,  $a_{-1} \ a_{-2} \ a_{-3} : N$  peut se noter :

$$\underbrace{(a_6 a_5 a_4 a_3 a_2 a_1 a_0)}_{\text{mantisse}}.\underbrace{2^{-3}}_{\text{exp}}$$

$$\Rightarrow \{ \begin{array}{ll} \text{exposant} = & -3 \\ \text{mantisse} = & a_6 a_5 a_4 a_3 a_2 a_1 a_0 \end{array}$$

Les valeurs de la mantisse et l'exposant seront notés en complément à 2 en mémoire du calculateur

#### ⊳ Exemple 2.8

Soit la mémoire de taille suivante :

| 4 bits   | 12 bits  |

|----------|----------|

| exposant | mantisse |

Coder la valeur 26,75 en virgule flottante.

$$(26,75)_{10}$$

$(11010,110)_2$

$$(11010,11)_2$$

$(11010110).2^{-3}$

$$\Rightarrow \{ \begin{array}{ll} exposant = & -3 \\ mantisse = & 11010110 \end{array}$$

#### 2ème approche

Méthode inverse  $\rightarrow$  on considère que le bit le plus à gauche de la mantisse à pour poids  $2^{-1}$ .

Soit:

$$N \ a_3 \ a_2 \ a_1 \ a_0$$

,  $a_{-1} \ a_{-2} \ a_{-3}$

N peut aussi se noter

$$(0, \underbrace{a_{-1} \, a_{-2} \, a_{-3} \, a_{-4} \, a_{-5} \, a_{-6} \, a_{-7}}_{\text{mantisse}})$$

.  $\underbrace{2^4}_{\text{exp}}$

#### ⊳ Exemple 2.9

Même exemple que précédemment :

$(26,75)_{10} (11010,110)_2 \longrightarrow (0,11010110).2^5$

0101 110101100000

#### ► Remarque 2.2

Les ordinateurs utilisent cette représentation avec 32 bits pour la mantisse et 8 bits pour l'exposant. En général, on utilise la représentation inverse, avec le bit le plus à gauche = 1, soit une mantisse normalisée  $\Rightarrow$  0,5  $\leq$  M 1

# II.3.3 La représentation IEEE 754 [WWW01]

#### II.3.3.a Présentation

Le standard IEEE 754 définit trois formats : les nombres en simple précision sur 32 bits, les nombres en double précision sur 64 bits, et les nombres en représentation intermédiaire sur 80 bits. La représentation sur 80 bits est principalement utilisée en interne par les processeurs pour minimiser les erreurs d'arrondi.

Un nombre N de 32 bits est représenté sous la forme :

| S | exposant | mantisse |

|---|----------|----------|

où le signe « s » est codé sur 1 bit, l'exposant est codé sur 8 bits en code relatif à 127 (cf. §II.2.4 page 16), et la mantisse sur 23 bits.

Un nombre de 64 bits (double précision) utilise la même représentation à ceci près que la taille de l'exposant est portée à 11 bits en code relatif à 1023, et celle de la mantisse à 52 bits.

Une mantisse normalisée commence toujours par un bit 1, suivi par la virgule, puis par le reste de la mantisse. Le bit initial, toujours présent et toujours à 1 dans une mantisse normalisée est implicite et non représenté. La valeur de la mantisse est appelée « significande » ; le significande a donc une valeur implicite  $1 \le x \ 2$ .

#### ⊳ Exemple 2.10

$$-12^{0}\times(10)$$

Le bit de signe sera 0, l'exposant, en code relatif à 127 sera représenté par 127 = 01111111, et le significande vaut 1, ce qui résulte en une mantisse dont tous les bits sont à 0. La représentation IEEE simple precision IEEE 754 du nombre 1 est donc :

Code(1) =

$$\begin{bmatrix} 0 & 0.01111111 & 0.000...0 \\ s & e & m \end{bmatrix}$$

= 3F800000

- 0.5 2<sup>-1</sup>×(1 0)

Le bit de signe est 0, l'exposant, en code relatif à 127 est représenté par 127 - 1 = 01111110, et le significande vaut 1, ce qui résulte en une mantisse

dont tous les bits sont à 0. La représentation IEEE simple précision IEEE 754 du nombre 0.5 est donc :

Le bit de signe est 0, l'exposant, en code relatif à 127 est représenté par 127 = 01111111, et le significande vaut 1.1, ce qui résulte en une mantisse dont le premier bit est à 1 et les 22 suivants à 0. La représentation IEEE simple precision IEEE 754 du nombre 1.5 est donc :

#### II.3.3.b Nombres spéciaux

En arithmétique à virgule flottante on peut obtenir un résultat valable, ou alors rencontrer un problème de dépassement par valeur supérieure (*overflow*) lorsque le résultat est trop grand pour pouvoir être représenté, ou par valeur inférieure (*underflow*) lorsque le résultat est trop petit.

#### Dépassement par valeur inférieure

Cette situation arrive lorsqu'un résultat est trop petit pour pouvoir être représenté. Le standard IEEE 754 résout partiellement le problème en autorisant dans ce cas une représentation dénormalisée. Une représentation dénormalisée est caractérisée par le fait d'avoir un code d'exposant complètement nul, ce qui est interprété comme une indication du fait que le bit de poids fort de la mantisse, implicite, est cette fois à 0 au lieu d'être à 1. De cette facon, le plus petit nombre « exprimable » est :  $2^{-127} \times 2^{-23}$   $2^{-150} \sim 10^{-45}$ .

Cependant, il faut remarquer que plus le nombre représenté est petit, moins sa mantisse comportera de bits significatifs. Ce schéma permet une approche « douce » du phénomène de dépassement par valeur inférieure, en sacrifiant la précision lorsqu'un résultat est trop petit pour admettre une représentation normalisée.

#### Zéro

Zéro est représenté sous la forme d'un nombre dénormalisé. Ceci résulte en deux représentations possibles pour zéro : l'une pour 0, l'autre pour -0. Ces représentations sont caractérisées par un bit de signe suivi par 31 zéros.

#### Dépassement par valeurs supérieures

Le dépassement par valeurs supérieures ne peut pas être traité comme le dépassement par valeurs inférieures, et est indiqué par un code d'exposant dont tous les bits sont à 1, suivi par une mantisse dont tous les bits sont à 0. Ceci est interprété comme représentant l'infini. L'infini peut être positif ou négatif, en fonction de la valeur du bit de signe. L'infini peut être utilisé dans les calculs et les résultats correspondent au sens commun:  $\infty \infty \infty$ ;  $\chi/\infty 0$ ;  $\chi/0 \infty$ .

#### Not a Number (NaN)

Cependant, certaines opérations peuvent ne conduire à aucun résultat exprimable, comme  $\infty/\infty$ ? ou  $0 \times \infty$ ?.

Le résultat de telles opération est alors indiqué par un autre code spécial : le code d'exposant a tous les bits à 1, suivi par une mantisse non nulle. Le « nombre » correspondant est appelé NaN (*Not a Number*) : c'est un non-nombre.

| Nombre             | Signe | Exposant | Mantisse    |

|--------------------|-------|----------|-------------|

| nombre normalisé   | 0/1   | 01 à FE  | quelconque  |

| nombre dénormalisé | 0/1   | 00       | quelconque  |

| zéro               | 0/1   | 00       | 0           |

| ∞                  | 0/1   | FF       | 0           |

| NaN                | 0/1   | FF       | tout sauf 0 |

| IEEE 754           | Simple précision                      | Double précision                        |

|--------------------|---------------------------------------|-----------------------------------------|

| exposant           | -126 à 127                            | $-10^{22} \text{ à } 10^{23}$           |

| mantisse           | 1 à $2-2^{-23}$                       | 1 à $2-2^{-52}$                         |

| + pt # normalisé   | 2-126                                 | 2-1022                                  |

| + gd # normalisé   | presque 2 <sup>128</sup>              | presque 2 <sup>1024</sup>               |

| intervalle utile   | $\approx 10^{-38} \text{ à } 10^{38}$ | $\approx 10^{-308} \text{ à } 10^{308}$ |

| + pt # dénormalisé | $2^{-150} \approx 10^{-45}$           | $2^{-1074} \approx 10^{-324}$           |

# II.4 Arithmétique binaire

#### II.4.1 Addition

L'addition en binaire se fait avec les mêmes règles qu'en décimal : on commence par additionner les bits de poids faibles; on a des retenues lorsque la somme de deux bits de même poids dépasse la valeur de l'unité la plus grande (dans le cas du binaire : 1); cette retenue est reportée sur le bit de poids plus fort suivant.

La table d'addition binaire est la suivante :

| Α |   | В |   | C | retenue | (carry) |

|---|---|---|---|---|---------|---------|

| 0 | + | 0 | = | 0 | 0       | •       |

| 0 | + | 1 | = | 1 | 0       |         |

| 1 | + | 0 | = | 1 | 0       |         |

| 1 | + | 1 | = | 0 | 1       |         |

#### ⊳ Exemple 2.11

Addition des nombres de 4 bits :

|   | 0 | 0 | 1 | 1 |   |   | 3  |              |

|---|---|---|---|---|---|---|----|--------------|

| + | 1 | 0 | 1 | 0 |   |   | -6 |              |

| = | 1 | 1 | 0 | 1 | • |   | -3 |              |

|   | 0 | 1 | 1 | 1 | , | 1 | 1  | 7,75<br>5,25 |

| + | 0 | 1 | 0 | 1 | , | 0 | 1  | 5,25         |

| = | 1 | 1 | 0 | 1 |   | 0 | 0  | -3,00        |

La retenue de la deuxième opération indique un dépassement de capacité (*overflow*) : le bit de signe est à 1 alors qu'il aurait dû être à 0 (addition de deux nombres positifs).

Conditions de dépassement lors de l'addition de deux nombres A et B de 16 bits :

| a <sub>15</sub> | $b_{15}$ | r <sub>15</sub> | opérandes |            | résultat | R | D   |

|-----------------|----------|-----------------|-----------|------------|----------|---|-----|

| 0               | 0        | 0               | a 0       | <i>b</i> 0 | r 0      | 0 | non |

| 0               | 0        | 1               | a 0       | $b \ 0$    | r = 0    | 0 | oui |

| 0               | 1        | 0               | a 0       | $b \ 0$    | r = 0    | 1 | non |

| 0               | 1        | 1               | a 0       | $b \ 0$    | r = 0    | 0 | non |

| 1               | 0        | 0               | a 0       | $b \ 0$    | r = 0    | 1 | non |

| 1               | 0        | 1               | a 0       | $b \ 0$    | r = 0    | 0 | non |

| 1               | 1        | 0               | a 0       | $b \ 0$    | r = 0    | 1 | oui |

| 1               | 1        | 1               | a 0       | $b \ 0$    | r = 0    | 1 | non |

R: retenue; D: dépassement

Ce tableau nous permet de déterminer la condition de dépassement (OF : *overflow flag*) : OF  $\overline{a_{15}}.\overline{b_{15}}.r_{15}$   $a_{15}.b_{15}.\overline{r_{15}}$ .

- si OF est à 0, le bit de poids fort (r<sub>15</sub>) donne le signe du résultat dont la valeur est disponible sur les 15 bits de poids faible.

- si OF est à 1, l'indicateur de retenue (C) donne le signe du résultat qui est luimême sur 16 bits. Dans ce dernier cas, le bit de poids fort ne donne pas le signe du résultat!

#### II.4.2 Soustraction

Dans la soustraction binaire, on procède comme en décimal. Quand la quantité à soustraire est supérieure à la quantité dont on soustrait, on emprunte 1 au voisin de gauche. En binaire, ce 1 ajoute 2 à la quantité dont on soustrait, tandis qu'en décimal il ajoute 10.

La table de soustraction binaire est la suivante :

| Α |   | В |   | C | retenue | (borrow) |

|---|---|---|---|---|---------|----------|

| 0 | - | 0 | = | 0 | 0       |          |

| 0 | - | 1 | = | 1 | 1       |          |

| 1 | - | 0 | = | 1 | 0       |          |

| 1 | _ | 1 | = | 0 | 0       |          |

#### ⊳ Exemple 2.12

#### ► Remarque 2.3

On peut utiliser le complément à 2 de la valeur à soustraire puis on additionne. Dans ce cas, il faut complémenter le retenue (carry) pour obtenir la retenue soustractive (borrow). Cela se passe de cette manière dans certains calculateurs.

#### ⊳ Exemple 2.13

On ne tient pas compte de la retenue.

# II.4.3 Multiplication

La table de multiplication en binaire est très simple :

| Α |   | В |   | C |

|---|---|---|---|---|

| 0 | X | 0 | = | 0 |

| 0 | X | 1 | = | 0 |

| 1 | X | 0 | = | 0 |

| 1 | X | 1 | = | 1 |

La multiplication se fait en formant un produit partiel pour chaque digit du multiplieur (seul les bits non nuls donneront un résultat non nul). Lorsque le bit du multiplieur

est nul, le produit partiel est nul, lorsqu'il vaut un, le produit partiel est constitué du multiplicande décalé du nombre de positions égal au poids du bit du multiplieur.

#### ⊳ Exemple 2.14

#### ► Remarque 2.4

La multiplication binaire par  $2^N$ , se résume à un décalage de N bits vers la gauche. On introduira donc à droite N zéro.

#### ⊳ Exemple 2.15

#### II.4.4 Division

La table de division binaire est la suivante :

| Α |   | В |   | C          |

|---|---|---|---|------------|

| 0 | / | 0 | = | impossible |

| 0 | / | 1 | = | 0          |

| 1 | / | 0 | = | impossible |

| 1 | / | 1 | = | 1          |

La division binaire s'effectue à l'aide de soustractions et de décalages, comme la division décimale, sauf que les digits du quotient ne peuvent être que 1 ou 0. Le bit du quotient est 1 si on peut soustraire le diviseur, sinon il est 0.

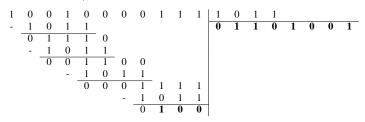

#### ⊳ Exemple 2.16

Division du nombre  $(10010000111)_2$  par  $(1011)_2$   $(1101001)_2$  reste  $(100)_2$ ,

c'est-à-dire 1159/11 105, reste 4.

#### ► Remarque 2.5

La division binaire par  $2^N$ , se résume à un décalage de N bits vers la droite. En arithmétique signée, il faut penser à recopier à gauche le bit de signe autant de fois que nécessaire.

#### ⊳ Exemple 2.17

#### II.5 En résumé

La valeur d'un nombre est indépendant de la base dans laquelle il est noté.

- Un nombre binaire peut avoir plusieurs valeurs différentes selon le système de représentation. Soit le nombre binaire  $a_n a_{n-1} \dots a_1 a_0$ . Ce nombre vaut :

- $a_n.2^n \ a_{n-1}.2^{n-1} \dots a_1.2 \ a_0$  en représentation non signée

- $\ensuremath{\mathscr{G}} -a_n.2^n \ a_{n-1}.2^{n-1} \ \dots \ a_1.2 \ a_0$  en représentation signée complément à 2

- $\gg 1 a_n.2^n \ a_{n-1}.2^{n-1} \dots a_1.2 \ a_0$  en représentation signée complément à 1

- Les opérations arithmétiques obéissent en binaire aux mêmes règles qu'en décimal, il suffit juste de se rappeler que la base de numération est 2 et non plus 10.

#

# Les codes numériques

Richard Wesley Hamming ★ 11 fév. 1915 à Chicago, E.-U. † 7 jan. 1998 à Monterey, E.-U.

« Indeed, one of my major complaints about the computer field is that whereas Newton could say, "If I have seen a little farther than others, it is because I have stood on the shoulders of giants," I am forced to say, "Today we stand on each other's feet." Perhaps the central problem we face in all of computer science is how we are to get to the situation where we build on top of the work of others rather than redoing so much of it in a trivially different way. Science is supposed to be cumulative, not almost endless duplication of the same kind of things. »

(Richard W. Hamming, One Man's View of Computer Science, 1968, Turing Award Lecture)

**Codage :** opération qui établit une correspondance entre un ensemble source (nombre, caractère, symbole) vers un ensemble but contenant des combinaisons de 0 et de 1.

# III.1 Codes numériques pondérés

### III.1.1 Code binaire pur

→ code pondéré par des puissances de 2. Utilisé en arithmétique binaire. Ses dérivées sont le code octal et le code hexadécimal.

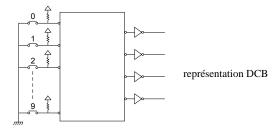

# III.1.2 Code DCB (Décimal Codé Binaire)

→ chaque chiffre décimal (0,1,...,9) est codé en binaire avec 4 e.b. Code pondéré avec les poids 1,2,4,8,10,20,40,80,100,... Plus facile pour coder des grands nombre, il est surtout utilisé pour l'affichage des nombres.

#### ► Remarque 3.1

Ne pas confondre DCB et code binaire pur : quand on code selon le code binaire pur on prend le nombre dans son intégralité et on le convertit; par contre, quand on code en DCB on code chaque chiffre indépendamment les uns des autres.

#### ⊳ Exemple 3.1

$$(137)_{10}$$

$(010001001)_2$   $(001011111)_{DCB}$

#### III.1.2.a Addition en DCB

L'addition de deux nombres codés en DCB ne pose pas de problème tant que le résultat est inférieur ou égal à 9 :

| 0000 0010 | 02 |

|-----------|----|

| 0000 0101 | 05 |

| 0000 0111 | 07 |

Par contre, dès que le résultat est supérieur à 9, il faut apporter une correction en additionnant 6, de manière à obtenir une réponse valide :

|  | 0000 0110 |  | 06 |         |

|--|-----------|--|----|---------|

|  | 0000 0100 |  | 04 |         |

|  | 0000 1010 |  | 0? | erreur! |

|  | 0000 0110 |  | 06 |         |

|  | 0001 0000 |  | 10 |         |

La correction est ici évidente, puisque la valeur obtenue est invalide en codage DCB. L'exemple suivant est moins évident :

| 0000 1001     |  | 09 |         |

|---------------|--|----|---------|

| 0000 1000     |  | 08 |         |

| <br>0001 0001 |  | 11 | erreur! |

| 0000 0110     |  | 06 |         |

| <br>0001 0111 |  | 17 |         |

Dans ce dernier exemple, la correction est due au fait qu'il a eu débordement sur la 4 bits de poids faible du mot DCB : il faut donc apporter une correction sur ces 4 bits de poids faible.

#### ⊳Note 3.1

- lorsque le résultat de l'addition est inférieur à 9, on ne change pas le résultat ;

- lorsque le résultat de l'addition est supérieur à 9, on ajoute 6 au résultat pour obtenir la valeur exacte;

- lorsqu'il y a une retenue auxiliaire (ou décimale) (auxiliary ou decimal carry), on ajoute également 6 au résultat obtenu, même si la valeur est inférieure à 9.

Les propriétés énoncées ci-dessus pour les chiffres des unités sont évidemment valables pour les dizaines, les centaines, etc. La correction à apporter sera alors – selon les circonstances – 6, 60, 66, etc.

#### III.1.2.b Soustraction en DCB

La soustraction en DCB se comporte exactement comme l'addition, au signe près.

#### ⊳Note 3.2

- lorsque le résultat de la soustraction est inférieur à 9, on ne change pas le résultat :

- lorsque le résultat de la soustraction est supérieur à 9, on soustrait 6 au résultat pour obtenir la valeur exacte;

- lorsqu'il y a une retenue soustractive (borrow), on soustrait également 6 au résultat obtenu, même si la valeur est inférieure à 9.

#### III.1.3 Code binaire de Aiken

Pondéré par 2421, c'est un code autocomplémentaire. (les représentations de 2 chiffres dont la somme est 9 sont complémentaires l'une de l'autre.

Il peut être constitué par les règles suivantes :

- de 0 à 4 on code en binaire pur;

- de 5 à 9 on ajoute 6 et on code en binaire pur. (c.à.d.  $5 \rightarrow 5$  6  $11, 6 \rightarrow 6$  6 12, ...)

#### ⊳ Exemple 3.2

| décimal | Aiken |   |   | déc | imal | Aiken |     |     |   |

|---------|-------|---|---|-----|------|-------|-----|-----|---|

|         | 2     | 4 | 2 | 1   |      | 1     | 2 4 | 1 2 | 1 |

| 0       | 0     | 0 | 0 | 0   |      | 5 .   | 1 ( | ) 1 | 1 |

| 1       | 0     | 0 | 0 | 1   | (    | 6     | 1 1 | 0   | 0 |

| 2       | 0     | 0 | 1 | 0   | ,    | 7 :   | 1 1 | 0   | 1 |

| 3       | 0     | 0 | 1 | 1   | ;    | 8 :   | 1 1 | 1   | 0 |

| 4       | 0     | 1 | 0 | 0   | 9    | 9 :   | 1 1 | 1   | 1 |

Ce code est utilisé dans certains calculateurs pour effectuer des soustractions par additions de la forme complémentaire.

# III.1.4 Les codes biquinaires

C'est un code composé d'un groupe de n bits (en général 5) dont un seul parmi n progresse à la fois, et d'un groupe de m bits (1 à 2) assurant la distinction entre n 5 et  $n \ge 5$ .

#### ⊳ Exemple 3.3

| décimal | S | O | 4 | 3 | 2 | 1 | 0 |

|---------|---|---|---|---|---|---|---|

| 0       | 0 | 1 | 0 | 0 | 0 | 0 | 1 |

| 1       | 0 | 1 | 0 | 0 | 0 | 1 | 0 |

| 2       | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 3       | 0 | 1 | 0 | 1 | 0 | 0 | 0 |

| 4       | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 5       | 1 | 0 | 0 | 0 | 0 | 0 | 1 |

| 6       | 1 | 0 | 0 | 0 | 0 | 1 | 0 |

| 7       | 1 | 0 | 0 | 0 | 1 | 0 | 0 |

| 8       | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 9       | 1 | 0 | 1 | 0 | 0 | 0 | 0 |

Chaque combinaison a un nombre pair de 1 : sécurité de transmission.

Ce code est utilisé dans les calculatrices.

# III.2 Codes numériques non pondérés

## III.2.1 Code majoré de trois (excédant de neuf)

On prend chaque chiffre décimal +3, puis on convertit en binaire. On a parfois recours à ce code en raison de la facilité avec laquelle on peut faire certains calculs arithmétiques. La valeur d'un mot en code majoré de trois est en fait égale au code DCB auquel on a ajouté 3.

#### ⊳ Exemple 3.4

## III.2.2 Code de Gray (binaire réfléchi)

Un seul bit change entre deux nombres consécutifs (notion d'adjacence).

Ce code est utilisé dans les tableaux de Karnaugh (cf. section V.1.1.c page 61, dans des circuits d'entrée/sortie, et dans certains convertisseurs analogique/numérique.

Il ne convient pas pour l'arithmétique binaire.

#### ⊳ Exemple 3.5

| Décimal | Gray |   |   |   |  |  |  |

|---------|------|---|---|---|--|--|--|

| 0       | 0    | 0 | 0 | 0 |  |  |  |

| 1       | 0    | 0 | 0 | 1 |  |  |  |

| 2 3     | 0    | 0 | 1 | 1 |  |  |  |

| 3       | 0    | 0 | 1 | 0 |  |  |  |

| 4 5     | 0    | 1 | 1 | 0 |  |  |  |

| 5       | 0    | 1 | 1 | 1 |  |  |  |

| 6       | 0    | 1 | 0 | 1 |  |  |  |

| 7       | 0    | 1 | 0 | 0 |  |  |  |

| 8       | 1    | 1 | 0 | 0 |  |  |  |

| 9       | 1    | 1 | 0 | 1 |  |  |  |

| 10      | 1    | 1 | 1 | 1 |  |  |  |

| 11      | 1    | 1 | 1 | 0 |  |  |  |

| 12      | 1    | 0 | 1 | 0 |  |  |  |

| 13      | 1    | 0 | 1 | 1 |  |  |  |

| 14      | 1    | 0 | 0 | 1 |  |  |  |

| 15      | 1    | 0 | 0 | 0 |  |  |  |

| 16      | 0    | 0 | 0 | 0 |  |  |  |

Le code présente 4 symétries miroir. Il est cyclique : il se referme sur lui-même.

Pour convertir un nombre en code binaire naturel (CBN) vers un nombre en code binaire réfléchi (CBR), il faut ajouter le CBN trouvé à lui-même décalé d'un rang vers la gauche, sans tenir compte de l'éventuelle retenue et en abandonnant dans le résultat le bit de poids faible.

#### ⊳ Exemple 3.6

Soit le nombre décimal 87 ; sa valeur binaire est 1010111. Donc :

1010111 +10101110

11111001

L'équivalent en code binaire réfléchi de (87)<sub>10</sub> est 1111100

III.2.2.a Conversion du code binaire naturel vers binaire réfléchi

|    | E                     | Binaire | nature | el    | B  | inaire | réflécl               | ni                    |

|----|-----------------------|---------|--------|-------|----|--------|-----------------------|-----------------------|

|    | <i>n</i> <sub>3</sub> | $n_2$   | $n_1$  | $n_0$ | 83 | 82     | <i>g</i> <sub>1</sub> | <i>g</i> <sub>0</sub> |

| 0  | 0                     | 0       | 0      | 0     | 0  | 0      | 0                     | 0                     |

| 1  | 0                     | 0       | 0      | 1     | 0  | 0      | 0                     | 1                     |

| 2  | 0                     | 0       | 1      | 0     | 0  | 0      | 1                     | 1                     |

| 3  | 0                     | 0       | 1      | 1     | 0  | 0      | 1                     | 0                     |

| 4  | 0                     | 1       | 0      | 0     | 0  | 1      | 1                     | 0                     |

| 5  | 0                     | 1       | 0      | 1     | 0  | 1      | 1                     | 1                     |

| 6  | 0                     | 1       | 1      | 0     | 0  | 1      | 0                     | 1                     |

| 7  | 0                     | 1       | 1      | 1     | 0  | 1      | 0                     | 0                     |

| 8  | 1                     | 0       | 0      | 0     | 1  | 1      | 0                     | 0                     |

| 9  | 1                     | 0       | 0      | 1     | 1  | 1      | 0                     | 1                     |

| 10 | 1                     | 0       | 1      | 0     | 1  | 1      | 1                     | 1                     |

| 11 | 1                     | 0       | 1      | 1     | 1  | 1      | 1                     | 0                     |

| 12 | 1                     | 1       | 0      | 0     | 1  | 0      | 1                     | 0                     |

| 13 | 1                     | 1       | 0      | 1     | 1  | 0      | 1                     | 1                     |

| 14 | 1                     | 1       | 1      | 0     | 1  | 0      | 0                     | 1                     |

| 15 | 1                     | 1       | 1      | 1     | 1  | 0      | 0                     | 0                     |

Les équation logiques pour un mot de 4 bits sont :

- $\mathcal{F}$   $g_0$   $a_1 \oplus a_0$

- $\mathcal{F}$   $g_1$   $a_2 \oplus a_1$

- $\mathcal{F}$   $g_2$   $a_3 \oplus a_2$

- ☞ g<sub>3</sub> a<sub>3</sub>

Pour un mot binaire de format n on a donc :

- $\mathscr{F}$   $g_i \ a_{i1} \oplus a_i$ , pour  $n-2 \ge i \ge 0$

- $\mathscr{F}$   $g_{n-1}$   $a_{n-1}$

On peut également exprimer  $g_n$  de manière récursive :

- $\mathcal{F}$   $g_0$   $g_3 \oplus g_2 \oplus g_1 \oplus a_0$

- $\mathcal{F}$   $g_1$   $g_3 \oplus g_2 \oplus g_1$

- $\mathcal{F}$   $g_2$   $g_3 \oplus g_2$

- ☞ g<sub>3</sub> a<sub>3</sub>

|    | B                     | inaire                | réflécl               | ni                    | E                     | Binaire | nature | el    |

|----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|---------|--------|-------|

|    | <i>g</i> <sub>3</sub> | <i>g</i> <sub>2</sub> | <i>g</i> <sub>1</sub> | <i>g</i> <sub>0</sub> | <i>n</i> <sub>3</sub> | $n_2$   | $n_1$  | $n_0$ |

| 0  | 0                     | 0                     | 0                     | 0                     | 0                     | 0       | 0      | 0     |

| 1  | 0                     | 0                     | 0                     | 1                     | 0                     | 0       | 0      | 1     |

| 2  | 0                     | 0                     | 1                     | 1                     | 0                     | 0       | 1      | 0     |

| 3  | 0                     | 0                     | 1                     | 0                     | 0                     | 0       | 1      | 1     |

| 4  | 0                     | 1                     | 1                     | 0                     | 0                     | 1       | 0      | 0     |

| 5  | 0                     | 1                     | 1                     | 1                     | 0                     | 1       | 0      | 1     |

| 6  | 0                     | 1                     | 0                     | 1                     | 0                     | 1       | 1      | 0     |

| 7  | 0                     | 1                     | 0                     | 0                     | 0                     | 1       | 1      | 1     |

| 8  | 1                     | 1                     | 0                     | 0                     | 1                     | 0       | 0      | 0     |

| 9  | 1                     | 1                     | 0                     | 1                     | 1                     | 0       | 0      | 1     |

| 10 | 1                     | 1                     | 1                     | 1                     | 1                     | 0       | 1      | 0     |

| 11 | 1                     | 1                     | 1                     | 0                     | 1                     | 0       | 1      | 1     |

| 12 | 1                     | 0                     | 1                     | 0                     | 1                     | 1       | 0      | 0     |

| 13 | 1                     | 0                     | 1                     | 1                     | 1                     | 1       | 0      | 1     |

| 14 | 1                     | 0                     | 0                     | 1                     | 1                     | 1       | 1      | 0     |

| 15 | 1                     | 0                     | 0                     | 0                     | 1                     | 1       | 1      | 1     |

III.2.2.b Conversion du code binaire naturel vers binaire réfléchi

Les équation logiques pour un mot de 4 bits sont :

a<sub>3</sub> g<sub>3</sub>

$\Rightarrow a_2 g_3 \oplus g_2$

$\mathcal{F}$   $a_1$   $g_3 \oplus g_2 \oplus g_1$

$\Rightarrow a_0 g_3 \oplus g_2 \oplus g_1 \oplus g_0$

Pour un mot binaire de format n on a donc :

$\mathcal{F}$   $a_{n-1}$   $g_{n-1}$

$$\mathscr{T} a_i \oplus \sum_{j=1}^{n-1} g_i \ a_{j1} \oplus g_i, \text{ pour } n-2 \ge i \ge 0$$

# III.3 Codes détecteurs d'erreurs et autocorrecteurs

Ces codes sont utilisés pour contrôler la transmission des données.

Souvent, on utilise un nombre de bits supérieur à celui strictement nécessaire pour coder l'information elle-même.

# III.3.1 Codes biquinaires

Cf. III.1.4 page 30.

# III.3.2 Les codes p parmi n

Ce sont des codes autovérificateurs (détecteurs d'erreurs mais pas autocorrecteurs). Ces codes possèdent n e.b. dont p sont à 1 ; la position des « 1 » permet de reconnaître un élément codé. Le nombre de combinaisons répondant à cette définition est :

$$C_n^p \frac{n!}{p!(n-p)!}$$

#### ⊳ Exemple 3.7

Pour transmettre l'information numérique dans les centraux téléphoniques (*cross bar*), on utilise un code 2 parmi 5 (ou code 74210) pour représenter les chiffres décimaux.

Il existe 10 combinaisons:

| Déc. |   |   | parm |   | • | Déc. | 2 parmi 5 |   |   |   |   |

|------|---|---|------|---|---|------|-----------|---|---|---|---|

|      | 7 | 4 | 2    | 1 | 0 |      | 7         | 4 | 2 | 1 | 0 |

| 1    | 0 | 0 | 0    | 1 | 1 | 6    | 0         | 1 | 1 | 0 | 0 |

| 2    | 0 | 0 | 1    | 0 | 1 | 7    | 1         | 0 | 0 | 0 | 1 |

| 3    | 0 | 0 | 1    | 1 | 0 | 8    | 1         | 0 | 0 | 1 | 0 |

| 4    | 0 | 1 | 0    | 0 | 1 | 9    | 1         | 0 | 1 | 0 | 0 |

| 5    | 0 | 1 | 0    | 1 | 0 | 0    | 1         | 1 | 0 | 0 | 0 |

# III.3.3 Les codes à contrôle de parité

Dans ces codes, on ajoute un e.b. de sorte que l'ensemble des bits à transmettre (ou le mot) ait un nombre pair (parité paire) ou impaire (parité impaire) de « 1 ».

#### ⊳ Exemple 3.8

$$0101 \longrightarrow \mathbf{0}0101$$

$$0111 \longrightarrow 10111$$

#### ► Remarque 3.2

Dans l'application de la méthode de la parité, l'émetteur et le récepteur se mettent d'accord à l'avance sur la parité à surveiller (paire ou impaire).

#### ► Remarque 3.3

Pour détecter la place d'un e.b. faux, il faut coder dans 2 dimensions selon les lignes et les colonnes.

#### ⊳ Exemple 3.9

Ce code détecte les erreurs simples à condition que l'e.b. de parité ne soit pas erroné.

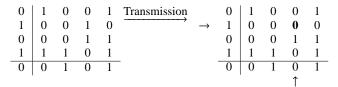

# III.3.4 Code de Hamming

Ce code est utilisé dans les transmissions de données. Il localise et corrige les chiffres erronnés (en ajoutant des e.b. supplémentaires aux e.b. de l'information).

Le nombre binaire d'information effective est : N ABCD 4

Le nombre binaire d'information transmise est : N abcdefg 7

avec

$$a$$

$A \oplus B \oplus C \oplus D$

$b$   $A \oplus C \oplus D$

$c$   $A$

$d$   $B \oplus C \oplus D$

$e$   $B$

$f$   $C$

$g$   $D$

## III.4 Les codes alphanumériques

Ils servent à coder des chiffres, des lettres, des signes de ponctuations et des caractères spéciaux (26 caractères minuscules, 26 caractères majuscules, 7 signes, 20 à 40 caractères spéciaux comme  $+,|,\neq,\%,...\rangle$

# III.4.1 Le code ASCII (American Standard Code for Information Interchange)

C'est le plus répandu. On le retrouve pratiquement dans tous les ordinateurs et leurs organes périphériques, pour leurs dialogues et la représentation des textes en mémoire.

Chaque symbole (caractère d'imprimerie) est codé par 7 e.b. (un  $8^{\rm ème}$  e.b. peut servir de parité) :  $2^7$  128 combinaisons différentes.

# [ Exercices sur les nombres ]

### ▶Exercice 1.1

Convertir en binaire, octal et hexadécimal les nombres décimaux suivants : 43 ; 154 ; 25740

### ▶Exercice 1.2

Convertir en décimal et hexadécimal les nombres suivants : (10010101)<sub>DCB</sub>; (1101110)<sub>2</sub>; (75)<sub>8</sub>; (587)<sub>8</sub>

### ▶Exercice 1.3

Convertir en binaire et hexadécimal les nombres suivants :  $(166,25)_{10}$ ;  $(126,34)_8$ ;  $(231,1)_4$

### ⊳Exercice 1.4

Convertir en binaire le nombre décimal suivant : 24537

### ▶Exercice 1.5

Convertir en décimal les nombres suivants :  $(10010101)_{DCB}$ ;  $(D9,4)_{H}$ ;  $(576)_{8}$

### ▶Exercice 1.6

Que peuvent représenter les octets suivants ? 01111001; 10100100; 01101010; 10010111

### ▶Exercice 1.7

En parité impaire, quel est le bit de parité à associer aux octets suivants ? EC; F1; 69; A3

### ▶Exercice 1.8

En parité paire, quel est le bit de parité à associer aux octets suivants ? CD; 6E; B8; A4

### ⊳Exercice 1.9

On effectue les opérations suivantes sur des octets signés (représentation en complément à 2). Donner les résultats en discutant leur validité. Vérifier en prenant les équivalents décimaux.

5F+6D; E8+C7; 9A-17; 5B-C4; A4-62

### ⊳Exercice 1.10

Une mémoire contient des octets stockés entre les adresses  $(9400)_H$  et  $(B3FF)_H$ . Combien d'octets contient-elle ? Quelle est la capacité totale en kbits ?

### ⊳Exercice 1.11

Une mémoire contient 2k octets stockés à partir de l'adresse (700)<sub>H</sub>. Quelle est la dernière adresse ?

# Deuxième partie La logique combinatoire

##

# Algèbre booléenne et opérateurs logiques

George Boole ★ 2 nov. 1815, Lincoln, R.-U. † 8 déc. 1864, Ballintemple, Irlande

« Une proposition peut être vraie ou fausse, mais ne peut pas être vraie et fausse. » (Aristote ■ 384, † 322 av. J.-C.)

### IV.1 Introduction

Les sytèmes logiques fonctionnent en mode binaire  $\longrightarrow$  les variables d'entrée et de sortie ne prennent que deux valeurs : « 0 » ou « 1 ». Ces valeurs (états) « 0 » et « 1 » correspondent à des plages définies à l'avance.

### ⊳ Exemple 4.1

- Technologie électrique TTL:

- $\ll 1 \Rightarrow \leftrightarrow 2.4 \text{ à 5 V}$

- <0  $> \leftrightarrow 0$  à 0.8 V

- Technologie pneumatique:

- « 1 » ↔ présence de pression

- $< 0 > \leftrightarrow absence de pression$

Les valeurs « 0 » et « 1 » ne représentent pas des nombres réels mais plutôt l'état d'une variable (logique) — on les appelle donc « niveaux logiques ».

# IV.1.1 Convention de nommage des synonymes des « 0 » et « 1 » :

Ces deux valeurs peuvent être nommées de différentes façons :

- Niveau logique « 1 » : Vrai, Fermé, Marche, Haut, Allumé, Oui :

- Niveau logique « 0 » : Faux, Ouvert, Arrêt, Bas, Éteint, Non.

### IV.1.2 Types de logiques

On définit deux types de logiques :

- Logique positive :

- niveau haut → état logique « 1 » (5V)

- niveau bas → état logique « 0 » (0V)

- Logique négative :

- niveau haut → état logique « 0 » (0V)

- niveau bas → état logique « 1 » (5V)

La logique binaire basée sur l'algèbre de Boole permet de décrire dans un modèle mathématique les manipulations et traitement des informations binaires, et d'analyser les systèmes numériques.

Il existe 3 fonctions élémentaires dans l'algèbre de Boole :

- addition logique : appelée OU, symbolisée par un plus : « »;

- multiplication logique : appelée ET, symbolisée par un point : « . »;

- complémentation : appelée NON, symbolisée par un surlignement : « »

- → tout circuit numérique peut être défini à l'aide d'une fonction logique (expression logique) qui représente la variable de la sortie en fonction des variables d'entrée.

### Variables logiques (binaires) IV.1.3

Ce sont des variables ne pouvant prendre que deux valeurs distinctes : « 0 » ou « 1 ». Une variable binaire peut représenter n'importe quel dispositif binaire (contact, lampe, électro-vanne...)

### IV.1.4 Convention:

Tout appareil est schématisé à l'état de repos. Dans tous les cas, l'action sur un appareil sera notée  $a, b, \dots$  et la non action  $\overline{a}, \overline{b}, \dots$

### ⊳ Exemple 4.2

Bouton poussoir ---- contact repos et contact travail.

1<sup>er</sup> cas : schéma d'un contact ouvert au repos dit « contact travail ».

2<sup>è</sup> cas : schéma d'un contact fermé au repos dit « contact repos ».

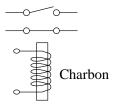

### ⊳ Exemple 4.3

Relais : c'est un interrupteur opérant de façon électromagnétique ; lorsqu'un courant approprié passe dans le charbon, une force magnétique déplace les armatures imposant l'ouverture ou la fermeture des contacts. Il est présenté dans sa position non alimentéee (au repos).

Ils peuvent être fermés ou ouverts au repos.

Symbole d'un relais double normalement ouvert et fermé

### IV.2 Propriétés de l'algèbre booléenne

### IV.2.1 Présentation

L'algèbre booléenne définit un cadre mathématique d'étude de propositions logiques portant sur des ensembles *E* d'éléments.

### Définition 4.1

**Algèbre booléenne :** un ensemble E d'éléments (a,b,c,...) associé à deux opérations binaires et . constitue une algèbre booléenne si et seulement si les postulats suivants sont satisfaits :

- P1 Les opérations sont commutatives ;

- P2 Chacune des opérations est distributive sur l'autre;

- **P4** Pour chaque élément a ∈ E, il existe un élément  $\overline{a} ∈ E$  tel que :  $a \overline{a} 1$  et  $a.\overline{a} 0$ .

À partir de ces postulats, il est possible de démontrer les théorèmes d'idempotence (cf. §IV.4.3), de l'élément nul, d'involution (cf. §IV.4.5), d'absorption (cf. §IV.5.6), d'associativité ainsi que la loi de De Morgan (cf. §IV.7). Tous ces théorèmes seront présentés plus loin.

Le lecteur attentif aura remarqué après la lecture des quatre postulats ci-dessus qu'il n'est jamais fait mention du nombre d'éléments dans l'ensemble *E*, ni encore moins que ce nombre d'éléments est limité à deux !

L'algèbre booléenne n'est pas restreinte aux ensembles binaires.

En fait, le nombre d'éléments dans E peut être infini, mais doit au moins comporter les éléments 0 et 1. Ainsi l'algèbre binaire, qui ne contient que les éléments 0 et 1, constitue l'algèbre booléenne la plus simple.

### ⊳ Exemple 4.4

Algèbre booléenne portant sur 4 éléments :  $E \{0, a, b, 1\}$

|   | 0 | a | b | 1 |

|---|---|---|---|---|

| 0 | 0 | a | b | 1 |

| a | a | a | 1 | 1 |

| b | b | 1 | b | 1 |

| 1 | 1 | 1 | 1 | 1 |

|   | 0 | a | b | 1 |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| a | 0 | a | 0 | a |

| b | 0 | 0 | b | b |

| 1 | 0 | a | b | 1 |

### IV.3 Algèbre binaire ou algèbre de commutation

### IV.3.1 Postulats de base

Le domaine de définition  $B_2$  de l'algèbre de commutation comprend donc deux éléments 0 et 1 ( $B_2$  {0, 1}).

Si a est une variable logique on a :

- P1 a 0 si et seulement si  $a \neq 1$

- $P1^* a$  1 si et seulement si  $a \neq 0$

L'opération NON(ou complément), notée « - » est définie par :

- **P2** 0 1

- **P2\*** 1 0

L'opération OU(ou disjonction), notée « + » est définie par :

- **☞ P3** 1110011

- **☞ P4** 000

L'opération ET(ou intersection), notée « . » est définie par :

- **☞ P3**\* 0.0 0.1 1.0 0

- **☞ P4**\* 1.1 1

L'algèbre de commutation est le système algébrique constitué de l'ensemble {0,1} et des opérateurs ET, OU, NON.

À partir de ces quatre postulats, on peut construire les différents théorèmes présentés dans les sections §IV.4 page suivante et §IV.5 page 48.

### IV.3.2 Hiérarchie des opérations

Dans une expression sans parenthèses, on effectue d'abord les opérations ET et, par la suite, les OU.

### IV.3.3 Induction parfaite

Dans le domaine linéaire, il n'est pas possible de prouver une équation en la vérifiant pour toutes les valeurs des variables.

En logique binaire, puisque les variables sont limitées à deux états, on peut prouver une relation en la vérifiant pour toutes les combinaisons de valeurs pour les variables d'entrée. Ainsi, toutes les propriétés présentés dans les sections §IV.4 de la présente page et §IV.5 page suivante peuvent être démontrées par induction parfaite.

On notera qu'il n'est pas évident de démontrer ces relations par induction parfaite en algèbre booléenne de plus de deux variables. La preuve de de ces théorèmes peut être consultée notamment dans [WHI61].

### IV.4 Théorèmes monovariables

### IV.4.1 Identité

À chaque opérateur correspond un élément neutre qui, lorsqu'il est opéré avec une variable quelconque A, donne un résultat identique à cette variable.

$A \ 0 \ A$   $A.1 \ A$

### IV.4.2 Élément nul

À chaque opérateur correspond un élément nul qui, lorsqu'il est opéré avec une variable quelconque A, donne un résultat identique à cet élément nul.

$A 1 1 \qquad A.0 0$

### IV.4.3 Idempotence

Le résultat d'une opération entre une variable A et elle-même est égal à cette variable.

A A A A A.A A

### IV.4.4 Complémentation

$A \overline{A} 1$   $A.\overline{A} 0$

### IV.4.5 Involution

Le complément d'une variable A est égal à cette variable.

$\overline{\overline{A}}$  A

### IV.5 Théorèmes multivariables

### IV.5.1 Équivalence

Deux fonctions sont équivalentes si on peut leur faire correspondre la même table de vérité

Si  $F \overline{A.B}$  et  $G \overline{A} \overline{B}$ , alors F G, et on dit que F est équivalente à G.

### IV.5.2 Complémentarité

Deux fonctions sont dites complémentaires si l'une est l'inverse de l'autre pour toutes les combinaisons d'entrées possibles.

Si  $F \ \overline{A}.\overline{B}$  et G A B, alors  $F \ \overline{G}$ , et on dit que F et G sont complémentaires.

### IV.5.3 Associativité

Les opérations , ., et ⊕ sont associatives :

A B C (A B) C A (B C)

A.B.C (A.B).C A.(B.C)

$A \oplus B \oplus C \ (A \oplus B) \oplus C \ A \oplus (B \oplus C)$

### IV.5.4 Commutativité

Les opérations, ., et  $\oplus$  sont commutatives :

A B B A A.B B.A  $A \oplus B B \oplus A$

### IV 5.5 Distributivité

Chacune des opérations et . est distributive sur l'autre :

A.(BC) A.BA.C AB.C (AB).(AC)

On peut remarquer que ce théorème est particulier dans l'algèbre booléenne puisqu'ici les deux expressions sont vraies, alors que seule la première l'est dans l'algèbre ordinaire.

### IV.5.6 Absorption

Absorption 1: A(A.B)A A.(AY)AAbsorption 2:  $(A\overline{B}).BAB$   $(A.\overline{B})BAB$

Ce théorème est particulièrement intéressant pour la conception de circuits numériques puisqu'il permet d'éliminer les termes inutiles et par là-même de réduire la complexité du circuit.

### IV.5.7 Dualité

Deux expressions sont dites duales si l'on obtient l'une en changeant dans l'autre, les ET par des OU, les OU par des ET, les « 1 » par des « 0 » et les « 0 » par des « 1 ».

Si on sait que  $\overline{A.B}$   $\overline{A}$   $\overline{B}$ , alors, on saura que  $\overline{A+B}$   $\overline{A.B}$  par dualité.

### IV.5.8 Théorème de De Morgan

Le théorème de De Morgan est une expression du principe de dualité.

Première forme :  $\overline{A+B+C+\cdots}$   $\overline{A}.\overline{B}.\overline{C}.\cdots$ Deuxième forme :  $\overline{A.B.C.\cdots}$   $\overline{A}$   $\overline{B}$   $\overline{C}$   $\cdots$ *Cf.* §IV.7 page 55 pour plus de précisions.

# IV.5.9 Sommes de produits, produits de sommes et forme canonique

Les expressions booléennes peuvent être manipulées sous différentes formes, certaines d'entre elles étant nécessaires pour simplifier ces expressions :

somme de produits;

ex. : F(A, B, C, D) A.B A. $\overline{C}$ .D B.D

- produit de sommes;

ex.: F(A, B, C, D) (A B).(A  $\overline{C}$  D).(B D)

Une expression est sous sa forme canonique si tous les symboles qui représentent les variables apparaissent dans tous les termes qui la constitue. Lorsqu'une équation est écrite à partir de sa table de vérité, elle est dans sa forme canonique.

### IV.5.9.a Forme disjonctive et sommes de mintermes

Si une fonction est une somme de produits, on a une somme canonique ou forme disjonctive .

Exemple:  $F \overline{A}.B.C A.B.C A.\overline{B}.\overline{C} \overline{A}.\overline{B}.\overline{C}$

Une fonction booléenne peut être représentée sous forme d'une somme de produits utilisant les mintermes. Les mintermes sont représentés par des « 1 » dans une table de vérité

La table suivante donne les mintermes d'une fonction de trois variables :

|                  |   |   | $m_0$                                    | $m_1$                         | $m_2$                         | $m_3$               | $m_4$                         | $m_5$              | $m_6$              | $m_7$ |

|------------------|---|---|------------------------------------------|-------------------------------|-------------------------------|---------------------|-------------------------------|--------------------|--------------------|-------|

| $\boldsymbol{A}$ | B | C | $\overline{A}.\overline{B}.\overline{C}$ | $\overline{A}.\overline{B}.C$ | $\overline{A}.B.\overline{C}$ | $\overline{A}$ .B.C | $A.\overline{B}.\overline{C}$ | $A.\overline{B}.C$ | $A.B.\overline{C}$ | A.B.C |

| 0                | 0 | 0 | 1                                        | 0                             | 0                             | 0                   | 0                             | 0                  | 0                  | 0     |

| 0                | 0 | 1 | 0                                        | 1                             | 0                             | 0                   | 0                             | 0                  | 0                  | 0     |

| 0                | 1 | 0 | 0                                        | 0                             | 1                             | 0                   | 0                             | 0                  | 0                  | 0     |

| 0                | 1 | 1 | 0                                        | 0                             | 0                             | 1                   | 0                             | 0                  | 0                  | 0     |

| 1                | 0 | 0 | 0                                        | 0                             | 0                             | 0                   | 1                             | 0                  | 0                  | 0     |

| 1                | 0 | 1 | 0                                        | 0                             | 0                             | 0                   | 0                             | 1                  | 0                  | 0     |

| 1                | 1 | 0 | 0                                        | 0                             | 0                             | 0                   | 0                             | 0                  | 1                  | 0     |

| 1                | 1 | 1 | 0                                        | 0                             | 0                             | 0                   | 0                             | 0                  | 0                  | 1     |

### IV.5.9.b Forme conjonctive et produits de maxtermes

Si une fonction est un produit de somme, on a un produit canonique ou forme conjonctive .

Exemple :

$$G(\overline{A} B C).(A B C).(A \overline{B} \overline{C}).(\overline{A} \overline{B} \overline{C})$$

Une fonction booléenne peut être représentée sous forme d'un produit de sommes utilisant les maxtermes. Les maxtermes sont représentés par des « 0 » dans une table de vérité.

La table suivante donne les maxtermes d'une fonction de trois variables :

|                  |   |   | $M_0$ | $M_1$              | $M_2$              | $M_3$                         | $M_4$ | $M_5$ | $M_6$                             | $M_7$                                        |

|------------------|---|---|-------|--------------------|--------------------|-------------------------------|-------|-------|-----------------------------------|----------------------------------------------|

| $\boldsymbol{A}$ | B | C | A+B+C | $A+B+\overline{C}$ | $A+\overline{B}+C$ | $A+\overline{B}+\overline{C}$ |       |       | $\overline{A} + \overline{B} + C$ | $\overline{A} + \overline{B} + \overline{C}$ |

| 0                | 0 | 0 | 0     | 1                  | 1                  | 1                             | 1     | 1     | 1                                 | 1                                            |

| 0                | 0 | 1 | 1     | 0                  | 1                  | 1                             | 1     | 1     | 1                                 | 1                                            |

| 0                | 1 | 0 | 1     | 1                  | 0                  | 1                             | 1     | 1     | 1                                 | 1                                            |

| 0                | 1 | 1 | 1     | 1                  | 1                  | 0                             | 1     | 1     | 1                                 | 1                                            |

| 1                | 0 | 0 | 1     | 1                  | 1                  | 1                             | 0     | 1     | 1                                 | 1                                            |

| 1                | 0 | 1 | 1     | 1                  | 1                  | 1                             | 1     | 0     | 1                                 | 1                                            |

| 1                | 1 | 0 | 1     | 1                  | 1                  | 1                             | 1     | 1     | 0                                 | 1                                            |

| 1                | 1 | 1 | 1     | 1                  | 1                  | 1                             | 1     | 1     | 1                                 | 0                                            |

IV.5.9.c Représentations d'une fonction sous forme de mintermes et maxtermes

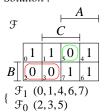

Soit la fonction  $\mathcal{F}$  telle que  $\mathcal{F}(A,B,C)$   $A.B \overline{B}.(\overline{A} \overline{C})$ .

Cette fonction peut être représentée sous sa :

- première forme canonique (somme de mintermes) : on developpe la fonction sous la forme d'une somme de produits puis on prend chaque terme avec pour variable manquante X et on applique un ET logique avec X  $\overline{X}$ ;

- deuxième forme canonique (produit de maxtermes) : on développe la fonction sous la forme d'un produit de sommes puis on prend chaque terme avec pour variable manquante X et on applique un OU logique avec  $X.\overline{X}$ ;

### ⊳ Exemple 4.5

Représentation sous forme de somme de mintermes :

$$\mathcal{F}(A,B,C) \ A.B \ \overline{B}.(\overline{A} \ \overline{C})$$

$$A.B \ \overline{A}.\overline{B} \ \overline{B}.\overline{C}$$

$$A.B.(C \ \overline{C}) \ \overline{A}.\overline{B}.(C \ \overline{C}) \ \overline{B}.\overline{C}.(A \ \overline{A})$$

$$\overline{A}.\overline{B}.\overline{C} \ \overline{A}.\overline{B}.C \ A.\overline{B}.\overline{C} \ A.B.\overline{C} \ A.B.\overline{C}$$

$$\sum m(0,1,4,6,7)$$

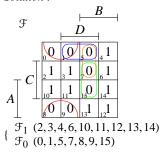

### ⊳ Exemple 4.6

Représentation sous forme de produit de maxtermes

$$\mathcal{F}(A,B,C) \ A.B \ \overline{B}.(\overline{A} \ \overline{C})$$

$$A.B \ \overline{A}.\overline{B} \ \overline{B}.\overline{C}$$

$$(A \ \overline{B}).(A \ \overline{B} \ \overline{C}).(\overline{A} \ B \ \overline{C}) \text{ par distributivit\'e}$$

$$(A \ \overline{B} \ C.\overline{C}).(A \ \overline{B} \ \overline{C}).(\overline{A} \ B \ \overline{C})$$

$$(A \ \overline{B} \ C).(A \ \overline{B} \ \overline{C}).(\overline{A} \ B \ \overline{C})$$

$$(A \ \overline{B} \ C).(A \ \overline{B} \ \overline{C}).(\overline{A} \ B \ \overline{C})$$

### IV.5.10 Résumé des propriétés des opérateurs OU et ET

| Propriété      | OU                                                        | ET                                             |

|----------------|-----------------------------------------------------------|------------------------------------------------|

| Identité       | a 0 a                                                     | a.1 a                                          |

| Élément neutre | a 0 a                                                     | a.1 a                                          |

| Élément absort | oant a 1 1                                                | a.0 0                                          |

| Idempotence    | ааа                                                       | a.a a                                          |

| Complémentat   | ion $a \overline{a} 1$                                    | $a.\overline{a} \ 0$                           |

| Involution     | $  $ $\bar{\bar{a}}$ $a$                                  | $\bar{a} a$                                    |

| Commutativité  | a b b a                                                   | a.b b.a                                        |

| Associativité  | a (b c)                                                   | a.(b.c)                                        |

|                | (a b) c                                                   | (a.b).c                                        |

| Distributivité | a (b.c)                                                   | a.(b c)                                        |

|                | (a b).(a c)                                               | (a.b)(a.c)                                     |

| Absorption 1   | a a.b a                                                   | a.(a b) a                                      |

| Absorption 2   | a a.b a b                                                 | $a.(\overline{a}\ b)\ a.b$                     |

| Consensus      | a.b a.c bc                                                | $(a b).(\overline{a} c).(b c)$                 |

|                | $a.b \overline{a}c$                                       | $(a\ b).(\overline{a}\ c)$                     |

|                | (a b).(                                                   | $\overline{a} \ b) \ (a.b) \ (\overline{a}.b)$ |

| De Morgan      | $\overline{a} \ \overline{b} \ \overline{a}.\overline{b}$ | $\overline{a.b} \ \overline{a} \ \overline{b}$ |

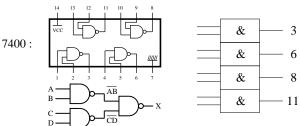

### IV.6 Opérateurs logiques élémentaires et composés

Les fonctions logiques sont conçues à partir d'un groupe d'opérateurs élémentaires appelés « portes ». Chaque opérateur est représenté par un symbole et sa fonction est définie par une table de vérité.

### IV.6.1 OUI : identité ou transfert

### IV.6.2 NON (NOT): complément « - »

$$\begin{array}{c|cccc}

A & S \overline{A} \\

\hline

0 & 1 \\

1 & 0

\end{array}$$

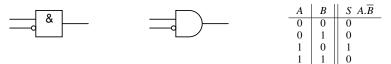

### IV.6.3 ET (AND): produit logique « . »

| $\boldsymbol{A}$ | В | S A.B |

|------------------|---|-------|

| 0                | 0 | 0     |

| 0                | 1 | 0     |

| 1                | 0 | 0     |

| 1                | 1 | 1     |

### Propriétés du ET:

a.1 a a.ā 0 a.0 0 a.a a

Élément neutre : 1 Élément absorbant : 0

### IV.6.4 OU (OR) : somme logique « »

| $\boldsymbol{A}$ | B | S A B |

|------------------|---|-------|

| 0                | 0 | 0     |

| 0                | 1 | 1     |

| 1                | 0 | 1     |

| 1                | 1 | 1     |

### Propriétés du OU:

$a \ 1 \ 1 \quad a \ \overline{a} \ 1 \quad a \ 0 \ a \quad a \ a \ a$

Élément neutre : 0 Élément absorbant : 1

### ► Remarque 4.1

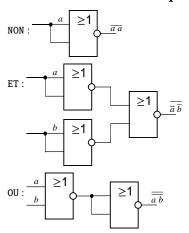

Les opérateurs {ET,OU,NON} permettent à eux trois de réaliser n'importe quelle fonction logique : on dit qu'ils forment un groupe complet.

Le théorème de De Morgan permet de dire que les groupes {ET, NON} et {OU, NON} sont également des groupes complets.

### IV.6.5 NON-OU (NOR) « $\downarrow$ »

Les deux opérateurs OU et NON peuvent être combinés en un seul opérateur NON-OU : NON-OU est donc un opérateur complet.

| $\boldsymbol{A}$ | В | $S \overline{A} \overline{B}$ |

|------------------|---|-------------------------------|

| 0                | 0 | 1                             |

| 0                | 1 | 0                             |

| 1                | 0 | 0                             |

| 1                | 1 | 0                             |

### IV.6.6 NON-ET (NAND) « $\uparrow$ »

Les deux opérateurs ET et NON peuvent être combinés en un seul opérateur NON-ET : NON-ET est donc un opérateur complet.

| $\boldsymbol{A}$ | В | $S \overline{A.B}$ |

|------------------|---|--------------------|

| 0                | 0 | 1                  |

| 0                | 1 | 1                  |

| 1                | 0 | 1                  |

| 1                | 1 | 0                  |

### IV.6.7 OUX (XOR) : ou exclusif ou dilemme « $\oplus$ »

| $\boldsymbol{A}$ | B | $S A \oplus B$ |

|------------------|---|----------------|

| 0                | 0 | 0              |

| 0                | 1 | 1              |

| 1                | 0 | 1              |

| 1                | 1 | 0              |

### Propriétés du OUX:

Le ou exclusif est commutatif et associatif  $a \oplus 0$  a  $a \oplus 1$   $\overline{a}$   $a \oplus \overline{a}$  1  $a \oplus a$  0

Élément neutre : 0Élément absorbant :  $a, \overline{a}$

### ► Remarque 4.2

Le ou exclusif est souvent utilisé dans les circuits numériques du fait de ses propriétés :

- le ou exclusif est l'opérateur somme modulo 2, on le retrouve donc dans les additionneurs ou la sortie S  $a \oplus b \oplus r$ ;

- il est également largement utilisé dans les circuits de correction d'erreurs (calcul de parité): b<sub>0</sub> ⊕b<sub>1</sub> ⊕b<sub>2</sub> ⊕···⊕b<sub>n</sub> est égal à 0 si le nombre de bits à 1 est pair, à 0 sinon;

- $-\hat{a} \oplus 1$   $\bar{a}$  et  $\hat{a} \oplus 0$   $\hat{a}$ :  $\bar{l}$   $\hat{e}$   $\hat{o}$   $\hat{u}$  exclusif peut être utilisé comme inverseur commandé.

Le ou exclusif n'est pas un opérateur complet, mais comme il peut être utilisé pour réaliser la complémentation, les groupes {OUX,ET} et {OUX,OU} sont des groupes complets.

### ► Remarque 4.3

Relations d'identité utilisables avec l'opérateur ou exclusif :

- 1.  $a \oplus b \ a\overline{b} \ \overline{a}b \ (a \ b).(\overline{a} \ \overline{b})$

- 2.  $\overline{(a \oplus b)} \ a \oplus \overline{b} \ \overline{a} \oplus b \ ab \ \overline{ab} \ (\overline{a} \ b)(a \ \overline{b})$

- 3.  $a \oplus a \ 0$  et  $a \oplus \overline{a} \ 1$

- 4.  $a \oplus 1 \overline{a}$  et  $a \oplus 0$  a

- 5.  $a(b \oplus z) ab \oplus az$

- 6.  $ab \ a \oplus b \oplus ab \ a \oplus \overline{a}b$

- 7.  $ab a \oplus b$  si ab 0

- 8.  $a \oplus b \ c \Rightarrow c \oplus b \ a$ ,  $c \oplus a \ b$ ,  $a \oplus b \oplus c \ 0$

- 9.  $a \oplus (a \ b) \overline{a}b$

- 10.  $a \oplus ab \ a\overline{b}$

# IV.6.8 NON-OUX (XNOR) : coïncidence ou équivalence « ⊙ »

| $\boldsymbol{A}$ | В | $S A \odot B$ |

|------------------|---|---------------|

| 0                | 0 | 1             |

| 0                | 1 | 0             |

| 1                | 0 | 0             |

| 1                | 1 | 1             |

### IV.6.9 IMP (IMP): implication $\ll \subset > ou \ll \supset >$

| $\boldsymbol{A}$ | В | $S A \overline{B}$ |

|------------------|---|--------------------|

| 0                | 0 | 1                  |

| 0                | 1 | 0                  |

| 1                | 0 | 1                  |

| 1                | 1 | 1                  |

### IV.6.10 INH (INIB): inhibition «/»

### IV.6.11 Résumé : les différents opérateurs

| Nom         | Symbole             | Valeur de xy |    |    | Expression |                                     |

|-------------|---------------------|--------------|----|----|------------|-------------------------------------|

|             | -                   | 00           | 01 | 10 | 11         | algébrique                          |

| Zéro        |                     | 0            | 0  | 0  | 0          | $F_0$ 0                             |

| Et          | x.y                 | 0            | 0  | 0  | 1          | $F_1$ x.y                           |

| Inhibition  | x/y                 | 0            | 0  | 1  | 0          | $F_2 x.\overline{y}$                |

| Transfert   |                     | 0            | 0  | 1  | 1          | $F_3 x$                             |

| Inhibition  | y/x                 | 0            | 1  | 0  | 0          | $F_4 \overline{x}.y$                |

| Transfert   |                     | 0            | 1  | 0  | 1          | F <sub>5</sub> y                    |

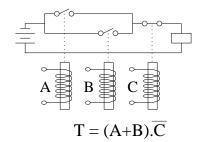

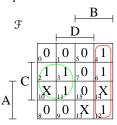

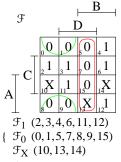

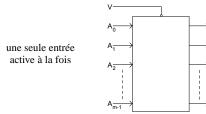

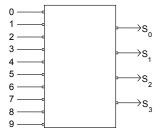

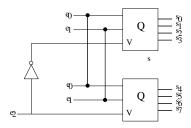

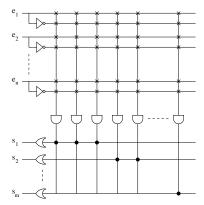

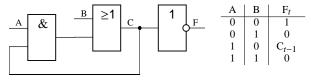

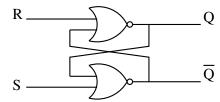

| Ou exclusif | <i>x</i> ⊕ <i>y</i> | 0            | 1  | 1  | 0          | $F_6 x \overline{y} \overline{x} y$ |