## CREATING RELIABLE AND MANUFACTURABLE RF DESIGNS

#### IEEE Boston Reliability Chapter, Lexington, MA Sept 13, 2017

- 1. Radio Frequency (RF) Applications

- 2. Design Trends

- 3. Need For Reliability

- 4. Design Considerations Device Physics

- 5. Additional Considerations Programmatic and Logistic Issues

- 6. Discussion

#### **EXPANDING ELECTRONICS MARKETS**

#### **Consumer, Industrial, Medical, Defense, Household & others**

- Wireless infrastructure, wearable and hand held devices

- Broadband communications, radios, Community Access Television (CATV)

- Security, monitoring, biometrics and screening

- Robotics and artificial Intelligence

- Internet of Things (IoT)

- Automobile and traffic management systems

- Satellite communication (SATCOM)

- Wild life management

- Medical treatment, imaging, telemedicine, instrumentation and devices

- Radars weather, aviation ....

- Electronic warfare systems surveillance, guidance ...

- This expansion has been possible with the affordable, smaller, lighter and have low power consumption solutions.

- Also known as SWAP-C (size, weight and power cost). All of these being lower.

System designers and manufacturers are responding to meet the ever expanding demand and market challenges through

- Developing highly integrated solutions

- Adding ever increasing functionality on semiconductor chips

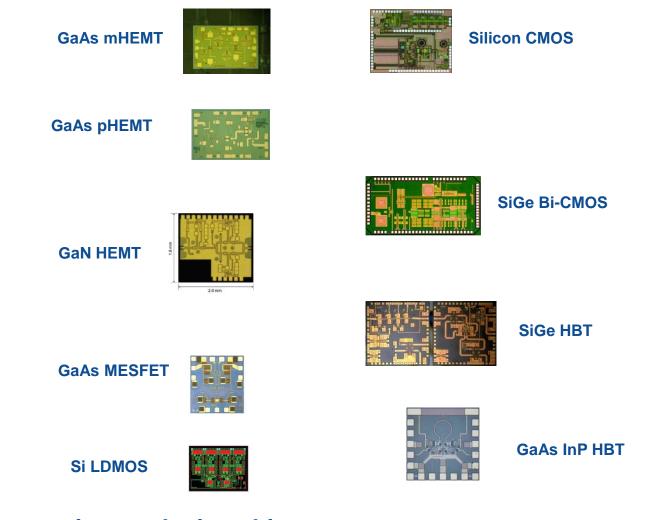

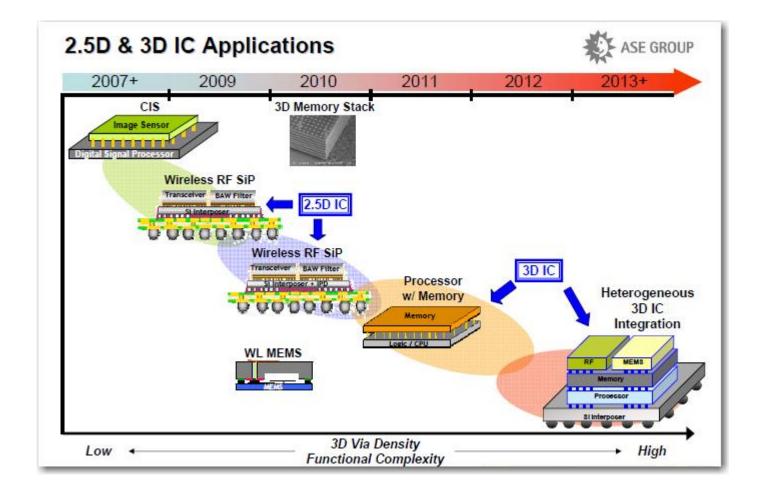

- Developing high density packages migrating to 2.5D and 3D concepts

- Very low pitch ball grid array (BGA) connections

- Monolithic integrated circuits in Silicon (Si), SiGe (Silicon Germanium), GaAs ( Gallium Arsenide), Gallium Nitride (GaN) otherwise known as chips.

- High level of small pitch interconnections, bumping and through vias

- High reliability

- These demands have led to the development of

- System on chip (SoC)

- System in package (SiP)

### **RF Semiconductor ICs**

#### Several companies producing chips

C. Gupta, IEEE Boston Reliability Chapter, Lexington, MA Sept 13, 2017

## 2.5D & 3D System in Package (SiP)

Reference: DARPA Website

TSV – Through Silicon Via

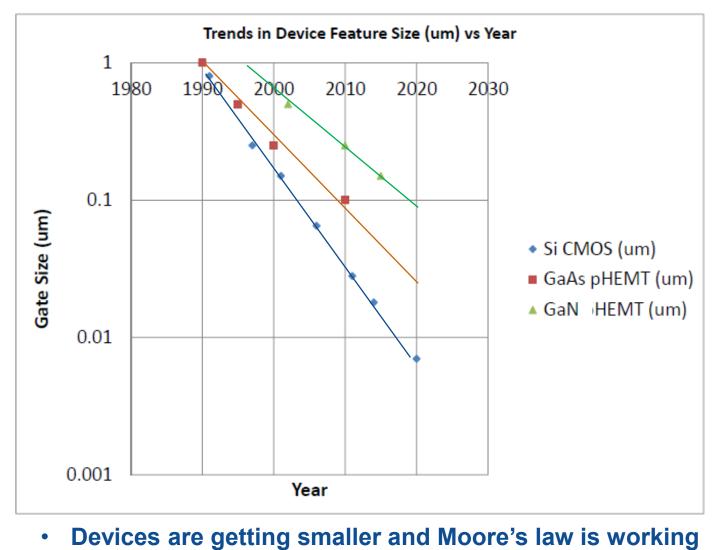

#### **SEMICONDUCTOR TRENDS**

• More functionality is possible on the same die size

- Designers and manufacturers provide cost effective and competitive solutions meeting the broad set of requirements

- Small and compact packages

- Ball grid arrays (BGAs) with micro pitches

- Small pads sizes, through silicon vias, bumps

- Bonds & contacts gold (Au), silver (Ag), copper (Cu) and aluminum (Al)

- Complex ICs consisting of a large number of transistors

- Multiple ICs in a package

#### We must also ensure that these solutions have satisfactory

- reliability

- availability

- maintainability

- **RAM Reliability, availability and maintainability**

- > Impacts on the total Life Cycle Costs (LCC) of a system.

- Stocking and spares

- Ability to perform the intended mission and affect overall mission success.

- Reliability probability of zero failures over a defined time interval

- Availability percentage of time a system is considered ready to use.

- Maintainability measure of time in which an equipment can be restored following a failure.

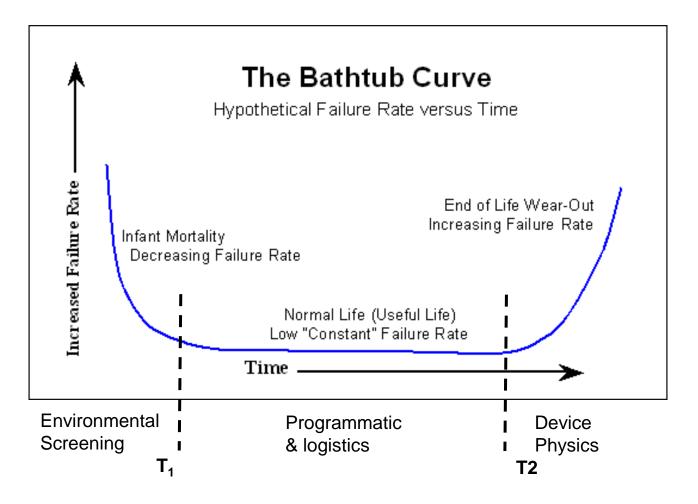

### **Failure Behavior**

Reference: C.Gupta, iMAPS Boxborough, MA May 2017

## **TYPICAL MODULES**

[1]

[3]

Reference: 1. informit.com 2. simple-electronics-projects.blogspot.com 3. CPI

## **DESIGN ELEMENTS**

### ELEMENTS.

| ELEMENT              | DESCRIPTION                                                                              |

|----------------------|------------------------------------------------------------------------------------------|

| Flasteinel Design    |                                                                                          |

|                      | Perform to the electrical performance requirements                                       |

| Mechanical<br>Design | Endure shock, vibration and other mechanical conditions                                  |

| Thermal Design       | Operation under all temperature conditions of use                                        |

| Device Physics       | Electro-Migration, Hot-Carrier Effects, Passivation Layer Breakdowns                     |

| Quality              | Latent Failures, Process Related Defects,                                                |

| Material             | Kirkendall, Galvanic and Whisker Growth Effects                                          |

| Processes            | Ensuring construction and measurements comply with the quality and customer requirements |

| Parts                |                                                                                          |

| Obsolescence         | Ensuring that the part can be repaired and/or replaced over the life                     |

| Stability            | Ability of the organization to service and stand behind the product                      |

| Supply Chain         | Smooth and uninterrupted flow of material and services                                   |

## **DESIGN CONSIDERATIONS**

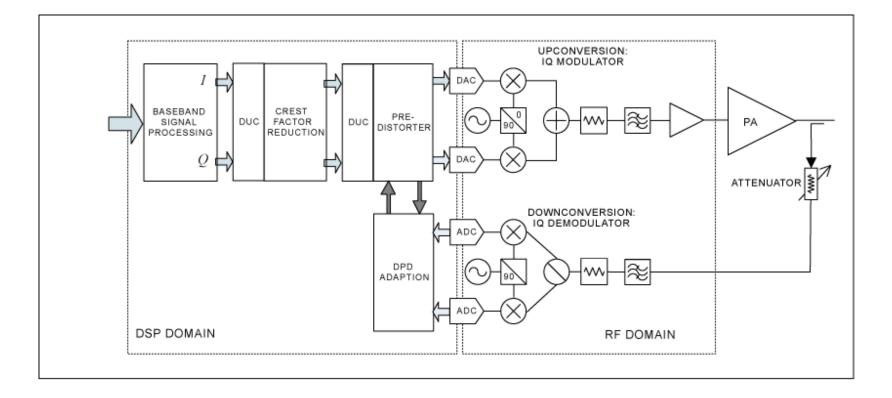

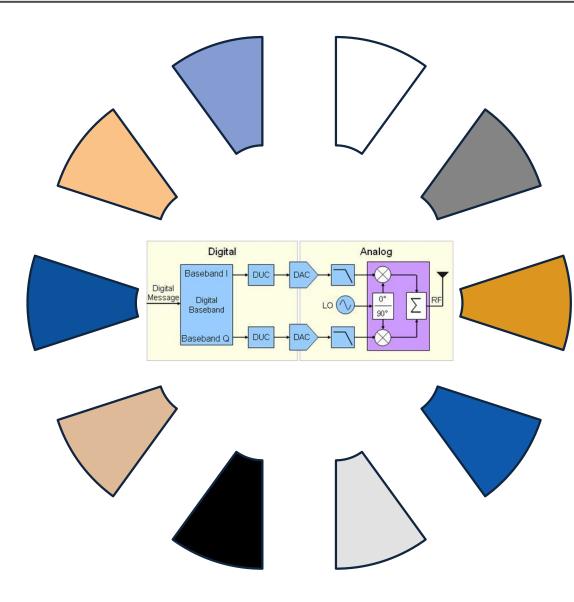

### **Transmitter Module**

Reference: maximintegrated.com

- 1. Electrical Design simulations and prototypes

- 2. Package Design

- 3. Mechanical and Thermal Design simulations and validations

- 4. Reliability Calculation MIL Handbook, Bellcore/Telecordia

- 5. Process Controls Coupon validations, SPC

- 6. Screening

- 7. Quality Compliance to Applicable Standards

- 8. Reduce and eliminate the end of life wear out failures during the operational life of systems.

#### **DEVICE PHYSICS CONSIDERATIONS**

#### These include

- 1. Required power on hours of operation

- 2. Device physics

- 1. Activation Energy

- 2. Electro migration

- 3. Hot carrier injection effect

- 4. Kirkendall Effects

- 5. Whisker Growth

- 3. Electro Static Discharge (ESD) & Electrical Over Stress (EOS)

Electromigration represents degradation in metal layers with time due to electron movements under full electrical field over long term.

The effect is important in microelectronics where high direct current densities are used.

As the size in integrated circuits (ICs) decreases, the significance of this effect increases.

### **ELECTROMIGRATION**

$MTTF = Aj^{-n}e^{\left(\frac{Q}{kT}\right)}$

A is a constant j is the current density n is a model parameter Q is the activation energy in eV (electron volts) k is Boltzmann constant T is the absolute temperature in K

- 1. Black's Equation models the mean time to failure (MTTF) due to electromigration.

- 2. Describes the failure rate dependence on the temperature, the electrical stress, and the specific technology and materials.

- 3. The values for *A*, *n*, and *Q* are found by fitting the model to experimental data.

- 4. Maps experimental data at elevated temperature and stress levels in short periods of time to expected component failure rates under actual operating conditions. HTOL testing.

Reference: Black, J.R. (1969). *IEEE Transaction on Electron Devices* (IEEE). ED-16 (4): 338.

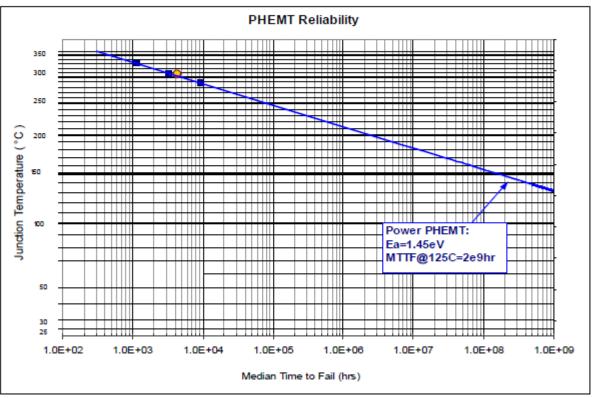

## **GaAs 0.5um PHEMT Reliability**

#### Example of PHEMT Reliability - Arrhenius Plot for Power PHEMT

Vds = 5-8V, Ids=135mA/mm

#### MTTF~2e9hr @ 125C with Ea=1.45eV

Reference: http://www.gcsincorp.com/dedicated\_pure-play\_wafer\_foundry/

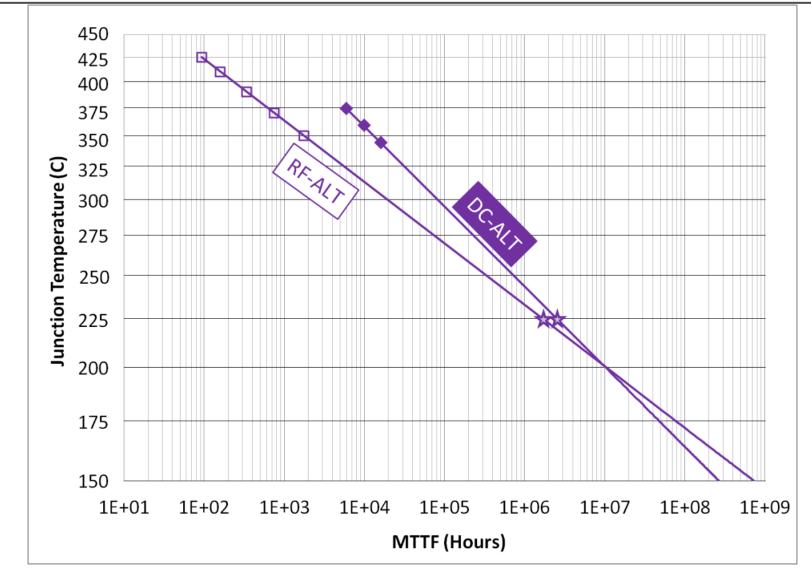

## **GaN 0.5um CREE Reliability**

ALT – Accelerated Life Test Reference: Gajewski et al, Wolfspeed – Cree, ROCS 2017

C. Gupta, IEEE Boston Reliability Chapter, Lexington, MA Sept 13, 2017

## **ARRHENIUS EQUATION**

Permits one to determine reliability with thermal-stress induced failures. Established through HTOL (high Temperature Operating Life) testing.

An equation used to calculate thermal acceleration factors for semiconductor device *time-to-failure distributions:*

$A_{\rm T} = \exp\left[(-E_{\rm aa}/k)(1/T_1 - 1/T_2)\right]$

where

$A_{\rm T}$  is the acceleration factor due to changes in temperature;  $E_{\rm aa}$  is the apparent activation energy (eV); k is Boltzmann's constant (8.62 × 10<sup>-5</sup> eV/K);  $T_1$  is the absolute temperature of the test (K);  $T_2$  is the absolute temperature of the system (K).

### **HOT CARRIER INJECTION EFFECT**

Hot carrier injection (HCI) is a phenomenon in solid state electronic devices where electrons or a holes gain sufficient energy to overcome a potential barrier necessary to break an interface state, resulting in loss of performance.

The term "hot" refers to the effective temperature used to model carrier density, not the overall temperature of the device.

Since the charge carriers can become trapped in the gate dielectric of a transistor, the switching characteristics of the transistor can be permanently changed.

Hot-carrier injection is one of the mechanisms that adversely affects the reliability.

Reference: John Keane, Chris H. Kim, Transistor Aging, IEEE Spectrum, May 2011

### WHISKER GROWTH

Tin whiskers are electrically conductive, crystalline structures of tin that sometimes grow from surfaces where tin (especially electroplated tin) is used as a final finish.

Tin whiskers have been observed to grow to lengths of several millimeters (mm) and in rare instances to lengths in excess of 10 mm. Numerous electronic system failures have been attributed to short circuits caused by tin whiskers that bridge closely-spaced circuit elements maintained at different electrical potentials.

Tin is only one of several metals that is known to be capable of growing whiskers. Other examples of metals that may form whiskers include some tin alloys, Zinc, Cadmium, Indium, Antimony, Silver among others .

Reference: nepp.nasa.gov/whiisker

### **KIRKENDALL EFFECT**

This effect occurs as a consequence of difference in diffusion rates of the meatal atoms.

Thermionic and wedge bonding process is used to make reliable interconnections between die bond pads and leads using thin gold and copper wires.

Under thermal aging, the fine pitch gold wire ball bonds (0.6- and 0.8-mil-diameter wires) show formation of voids apart from intermetallic compound growth known as Kikendall effect.

With 1- and 2-mil-diameter gold wire bonds, the void growth is less significant and reveals fine voids.

Studies also showed that void formation is absent in the case of thicker 3-mil wire bonds.

Reference: S. Murali, N. Srikanth, C. J. Vath III, Materials Letters, Volume 58, Issue 25, Pages 3089-3232 (October 2004)

### **ESD & EOS EFFECTS**

Electrostatic discharge (ESD) can occur in the manufacturing, shipping, receiving, and field handling of integrated circuits or computer boards with no visible signs of damage. A <u>malfunction</u> in these components or boards <u>can occur immediately or the apparatus may</u> <u>perform for weeks, months, or even years before an unpredictable and premature breakdown causes a field failure.</u>

Electrical Over Stress (EOS) Damage is caused by thermal overstress to a component's circuitry. The amount of damage caused by EOS depends on the magnitude and duration of electrical transient pulse widths. We can broadly classify the duration of pulse widths into long (>1 ms) and short (<100 us) types, and magnitude into exceeding an individual component's EOS threshold.

For short pulse widths the most common failure mode is junction spiking.

For long electrical pulse widths the most common failure modes are <u>melted metallization</u> and open bond wires.

## **PROGRAMMATIC & LOGISTICS**

- 1. Parts Obsolescence

- 2. Supplier Stability

- 3. Supply Chain Management

## DISCUSSION

## FACTORS TO INCLUDE

- Electrical Design

- Mechanical Design

- □ Thermal Design

- Reliability

- Device Physics

- Quality

- Material

- Processes

- □ Parts Obsolescence

- Stability

## DISCUSSION

- Device physics is vital to ensure that the wear out failures are outside the expected operational life of the system. Adequate margins need to be applied.

- In addition to all the design and manufacturing considerations covered here, other programmatic considerations must be managed and included in overall system deployment

- Parts Obsolescence

- Supply Chain Management

# THANK YOU Q&A