### JEPPIAAR ENGINEERING COLLEGE

**DEPARTMENT OF COMPUTER SCIENCE & ENGINEERING**

## CS8352– Digital Principles and system Design

# **Question Bank**

# II YEAR A & B / BATCH : 2017 - 2021

(common for CSE &IT)

#### Vision of Institution

To build Jeppiaar Engineering College as an Institution of Academic Excellence in Technical education and Management education and to become a World Class University.

#### **Mission of Institution**

| r | И1          | To excel in teaching and learning, research and innovation by promoting the principles of scientific analysis and creative thinking                                                                   |

|---|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| r | И2          | To participate in the production, <b>development and dissemination of knowledge</b> and interact with <b>national and international communities</b>                                                   |

| r | <b>/</b> 13 | To equip students with <b>values, ethics and life skills</b> needed to enrich their lives and enable them to meaningfully contribute to the <b>progress of society</b>                                |

| r | л4          | To prepare students for higher studies and lifelong learning, enrich them with the practical and entrepreneurial skills necessary to excel as future professionals and contribute to Nation's economy |

#### **Program Outcomes (POs)**

| Trogram | n Outcomes (105)                                                                        |

|---------|-----------------------------------------------------------------------------------------|

|         | Engineering Knowledge: Apply the Knowledge of mathematics, science, engineering         |

| PO1     | fundamentals, and an engineering specialization to the solution of complex engineering  |

|         | problems.                                                                               |

|         | Problem analysis: Identify, formulate, review research literature, and analyze complex  |

| PO2     | engineering problems reaching substantiated conclusions using first principles of       |

|         | mathematics, natural sciences, and engineering sciences.                                |

|         | Design/development of solutions: Design solutions for complex engineering problems      |

| 000     | and design system components or processes that meet the specified needs with            |

| PO3     | appropriate consideration for the public health and safety, and the cultural, societal, |

|         | and environmental considerations                                                        |

|         | Conduct investigations of complex problems: Use research-based Knowledge and            |

| PO4     | research methods including design of experiments, analysis and interpretation of data,  |

|         | and synthesis of the information to provide valid conclusions.                          |

| PO5     | Modern tool usage: Create, select, and apply appropriate techniques, resources, and     |

|         | modern engineering and IT tools including prediction and modeling to complex            |

|      | engineering activities with an understanding of the limitations.                        |

|------|-----------------------------------------------------------------------------------------|

|      | The engineer and society: Apply reasoning informed by the contextual Knowledge to       |

| PO6  | assess societal, health, safety, legal and cultural issues and the consequent           |

|      | responsibilities relevant to the professional engineering practice.                     |

|      | Environment and sustainability: Understand the impact of the professional engineering   |

| PO7  | solutions in societal and environmental contexts, and demonstrate the Knowledge of,     |

|      | and need for sustainable development.                                                   |

| PO8  | Ethics: Apply ethical principles and commit to professional ethics and responsibilities |

| r Uð | and norms of the engineering practice.                                                  |

| PO9  | Individual and team work: Function effectively as an individual, and as a member or     |

| 105  | leader in diverse teams, and in multidisciplinary settings.                             |

|      | Communication: Communicate effectively on complex engineering activities with the       |

| PO10 | engineering community and with society at large, such as, being able to comprehend      |

| 1010 | and write effective reports and design documentation, make effective presentations,     |

|      | and give and receive clear instructions.                                                |

|      | Project management and finance: Demonstrate Knowledge and understanding of the          |

| PO11 | engineering and management principles and apply these to one's own work, as a           |

| FOII | member and leader in a team, to manage projects and in multidisciplinary                |

|      | environments.                                                                           |

|      | Life-long learning: Recognize the need for, and have the preparation and ability to     |

| PO12 | engage in independent and life-long learning in the broadest context of technological   |

|      | change.                                                                                 |

#### Vision of Department

To emerge as a globally prominent department, developing ethical computer professionals, innovators and entrepreneurs with academic excellence through quality education and research.

#### **Mission of Department**

| M1 | To create <b>computer professionals</b> with an ability to identify and <b>formulate the engineering problems</b> and also to provide <b>innovative solutions</b> through <b>effective teaching learning process.</b> |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M2 | To <b>strengthen the core-competence</b> in computer science and engineering and to create an ability to <b>interact</b> effectively with industries.                                                                 |

| M3 | To produce engineers with good professional sKills, ethical values and life skills for the betterment of the society.                                                                                                 |

| M4 | To encourage students towards <b>continuous and higher level learning</b> on technological advancements and provide a platform for <b>employment and self-employment</b> .                                            |

**Program Educational Objectives (PEOs)**

| PEO1 | To address the real time complex engineering problems using innovative approach with     |  |  |  |  |  |  |  |

|------|------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|      | strong core computing skills.                                                            |  |  |  |  |  |  |  |

|      |                                                                                          |  |  |  |  |  |  |  |

| PEO2 | To apply core-analytical Knowledge and appropriate techniques and provide solutions to   |  |  |  |  |  |  |  |

|      | real time challenges of national and global society                                      |  |  |  |  |  |  |  |

| PEO3 | Apply ethical Knowledge for professional excellence and leadership for the betterment of |  |  |  |  |  |  |  |

|      | the society.                                                                             |  |  |  |  |  |  |  |

|      |                                                                                          |  |  |  |  |  |  |  |

| PEO4 | Develop life-long learning skills needed for better employment and entrepreneurship      |  |  |  |  |  |  |  |

#### **SYLLABUS**

#### **UNIT I BOOLEAN ALGEBRA AND LOGIC GATES 12**

Number Systems - Arithmetic Operations - Binary Codes- Boolean Algebra and Logic Gates - Theorems and Properties of Boolean Algebra - Boolean Functions - Canonical and Standard Forms - Simplification of Boolean Functions using Karnaugh Map - Logic Gates - NAND and NOR Implementations.

#### **UNIT II COMBINATIONAL LOGIC 12**

Combinational Circuits – Analysis and Design Procedures - Binary Adder-Subtractor - Decimal Adder - Binary Multiplier - Magnitude Comparator - Decoders – Encoders – Multiplexers - Introduction to HDL – HDL Models of Combinational circuits.

#### **UNIT III SYNCHRONOUS SEQUENTIAL LOGIC 12**

Sequential Circuits - Storage Elements: Latches , Flip-Flops - Analysis of Clocked Sequential Circuits - State Reduction and Assignment - Design Procedure - Registers and Counters - HDL Models of Sequential Circuits.

#### **UNIT IV ASYNCHRONOUS SEQUENTIAL LOGIC 12**

Analysis and Design of Asynchronous Sequential Circuits – Reduction of State and Flow Tables – Race-free State Assignment – Hazards.

#### **UNIT V MEMORY AND PROGRAMMABLE LOGIC 12**

RAM – Memory Decoding – Error Detection and Correction - ROM - Programmable Logic Array – Programmable Array Logic – Sequential Programmable Devices.

#### **TEXT BOOK:**

1. M. Morris R. Mano, Michael D. Ciletti, "Digital Design: With an Introduction to the Verilog HDL, VHDL, and SystemVerilog", 6th Edition, Pearson Education, 2017.

#### **REFERENCES:**

1. G. K. Kharate, Digital Electronics, Oxford University Press, 2010

2. John F. Wakerly, Digital Design Principles and Practices, Fifth Edition, Pearson Education, 2017.

3. Charles H. Roth Jr, Larry L. Kinney, Fundamentals of Logic Design, Sixth Edition, CENGAGE Learning, 2013

4. Donald D. Givone, Digital Principles and Designl, Tata Mc Graw Hill, 2003.

#### Course Outcomes (COs)

| CO202.1 | Simplify Boolean functions using KMap Design       |

|---------|----------------------------------------------------|

| CO202.2 | Analyze Combinational and Sequential Circuits      |

| CO202.3 | Implement designs using Programmable Logic Devices |

| CO202.4 | Write HDL code for combinational Circuits          |

| CO202.5 | Write HDL code for Sequential Circuits             |

#### BLOOM TAXANOMY LEVELS

BTL1: Creating., BTL2: Evaluating., BTL3: Analyzing., BTL4: Applying., BTL5: Understanding., BTL6: Remembering

### JEPPIAAR ENGINEERING COLLEGE

Jeppiaar Nagar, Rajiv Gandhi Salai – 600 119

#### DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING QUESTION BANK

#### SUBJECT: CS8351 DIGITAL PRINCIPLES AND SYSTEM DESIGN

#### YEAR /SEM: II/III

#### UNIT I BOOLEAN ALGEBRA AND LOGIC GATES

Number Systems - Arithmetic Operations - Binary Codes- Boolean Algebra and Logic Gates - Theorems and Properties of Boolean Algebra - Boolean Functions - Canonical and Standard Forms - Simplification of Boolean Functions using Karnaugh Map - Logic Gates – NAND and NOR Implementations.

|               | PART – A                                                                           |                              |                 |                  |

|---------------|------------------------------------------------------------------------------------|------------------------------|-----------------|------------------|

| CO            | Mapping : CO202.1                                                                  |                              |                 |                  |

| S.<br>N<br>o. | Question                                                                           | Blooms<br>Taxanom<br>y Level | Competenc<br>e  | РО               |

| 1             | Find the Octal equivalent of the hexadecimal numberDC.BA.(May/June 2016)           | BTL-5                        | Evaluating      | PO1, PO2,<br>PO3 |

| 2             | What is meant by multilevel gates networks?(May/June 2016)                         | BTL-1                        | Remember<br>ing | PO1              |

| 3             | Discuss the NOR operation with a truth table.<br>(Nov./Dec. 2015)                  | BTL-1                        | Remember<br>ing | PO1              |

| 4             | Write short notes on weighted binary codes. (Nov./Dec. 2015)                       | BTL-1                        | Remember<br>ing | PO1              |

| 5             | Convert (126) <sub>10</sub> to Octal number and binary number.<br>(Nov./Dec. 2015) | BTL-1                        | Remember<br>ing | PO1              |

| 6             | Prove the following using Demorgan' theorem<br>[(X+Y)'+(X+Y)']'= X+Y (May 2015)    | BTL-1                        | Remember<br>ing | PO1              |

| 7             | Convert (0.6875) <sub>10</sub> to binary. (May 2015)                               | BTL-1                        | Remember<br>ing | PO1              |

| 8             | Implement AND gate using only NOR gate (December 2014)                             | BTL-1                        | Remember<br>ing | PO1              |

| 9             | State the principle of duality (December 2014)                                     | BTL-1                        | Remember<br>ing | PO1              |

| 10 | State and prove the consensus theorem. (June 2014)                                                   | BTL-1 | Remember<br>ing   | PO1      |

|----|------------------------------------------------------------------------------------------------------|-------|-------------------|----------|

| 11 | Find the octal equivalent of hexadecimal numbers AB.CD. (June 2014)                                  | BTL-1 | Remember<br>ing   | PO1      |

| 12 | Realize XOR gate using only 4 NAND gates. (Dec 2013)                                                 | BTL-2 | Understan<br>ding | PO1, PO2 |

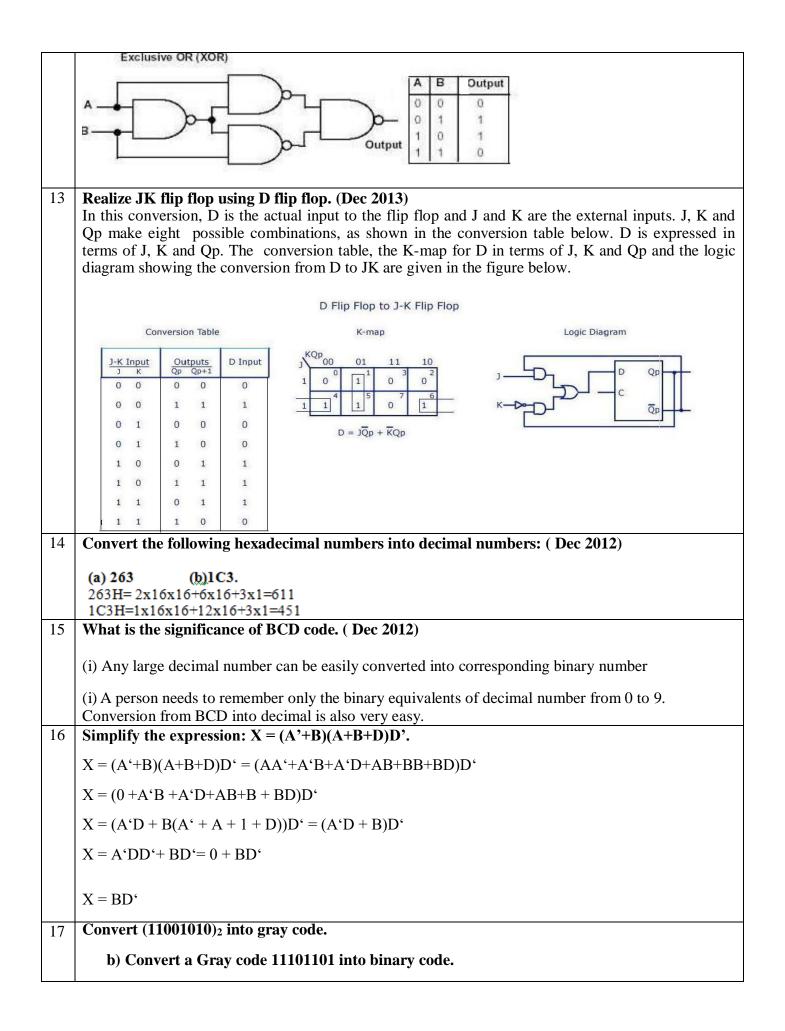

| 13 | Realize JK flip flop using D flip flop. (Dec 2013)                                                   | BTL-1 | Remember<br>ing   | PO1      |

| 14 | Convert the following hexadecimal numbers into<br>decimal numbers: ( Dec 2012)<br>a)263, b)1C3       | BTL-1 | Remember<br>ing   | PO1      |

| 15 | What is the significance of BCD code. ( Dec 2012)                                                    | BTL-1 | Remember<br>ing   | PO1      |

| 16 | Simplify the expression: X = (A'+B)(A+B+D)D'.                                                        | BTL-1 | Remember<br>ing   | PO1      |

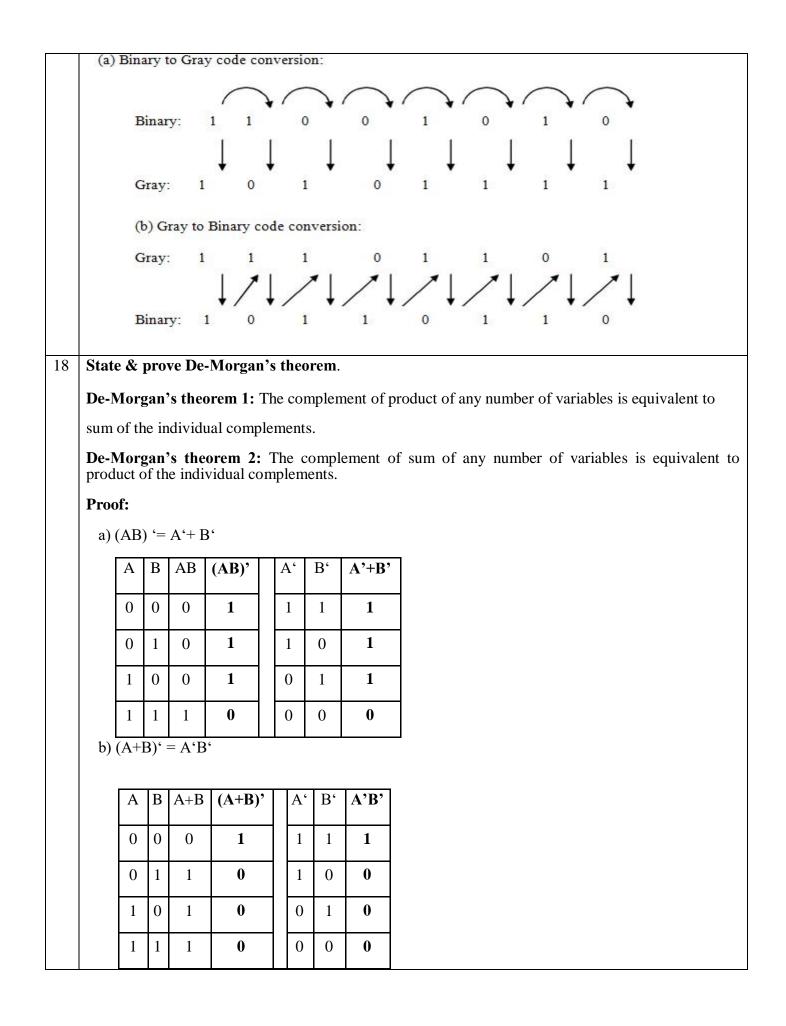

| 17 | Convert (11001010) <sub>2</sub> into gray code.<br>b) Convert a Gray code 11101101 into binary code. | BTL-1 | Remember<br>ing   | PO1      |

| 18 | State & prove De-Morgan's theorem.                                                                   | BTL-1 | Remember<br>ing   | PO1      |

| 19 | Describe the canonical forms of the Boolean function.                                                | BTL-1 | Remember<br>ing   | PO1      |

| 20 | Describe the importance of don't care conditions.                                                    | BTL-1 | Remember<br>ing   | PO1      |

| 21 | What is a prime implicant?                                                                           | BTL-1 | Remember<br>ing   | PO1      |

| 22 | Define the following: minterm and maxterm?                                                           | BTL-1 | Remember<br>ing   | PO1      |

| 23 | Minimize the function using K-map: $F=\sum m(1,2,3,5,6,7)$ .                                         | BTL-1 | Remember<br>ing   | PO1      |

| 24 | Define Karnaugh map.                                                                                 | BTL-1 | Remember<br>ing   | PO1      |

| 25 | Plot the expression on K-map: F (w,x,y) = $\sum m (0, 1, 3, 5, 6) + d (2, 4)$ .                      | BTL-1 | Remember<br>ing   | PO1      |

| 26 | Express x + yz as the sum of minterms                                                                | BTL-1 | Remember<br>ing   | PO1      |

| 27 | Simplify: a) $Y = AB'D + AB'D'$ b) $Z = (A'+B)(A+B)$ .                                               | BTL-1 | Remember<br>ing   | PO1      |

| 28 | What are Universal Gates? Why are they called so?                                                    | BTL-1 | Remember<br>ing   | PO1      |

| 29 | Implement OR using NAND only.                                                                        | BTL-1 | Remember ing      | PO1      |

| 30 | Implement NOR using NAND only.                                                                       | BTL-1 | Remember<br>ing   | PO1      |

| 1 | PART BReduce the expression using Quine McCluskey's method $F(x_1, x_2, x_3, x_4, x_5) = \sum m (0, 2, 4, 5, 6, 7, 8, 10, 14, 17, 18, 21, 29, 31) + \sum d (11, 20, 22)$ (May/June 2016)                                                                | BTL-6 | Creating    | PO1,<br>PO2,<br>PO3,<br>PO4 |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------|-----------------------------|

| 2 | Simplify the following switching functions using Quine McCluskey's tabulation method and realize expression using gates $F(A,B,C,D) = \Sigma(0,5,7,8,9,10, 11, 14,15)$ . (Nov/Dec 2015)                                                                 | BTL-5 | Evaluating  | PO1,<br>PO2,<br>PO3,<br>PO4 |

| 3 | Simplify the following switching functions using<br>Karnaugh map method and realize expression using gates<br>$F(A,B,C,D) = \Sigma(0,3,5,7,8,9,10,12,15)$ . (Nov/Dec<br>2015)                                                                           | BTL-1 | Remembering | PO1                         |

| 4 | <ul> <li>(a) Express the following function in sum of min-terms and product of max-terms F(X,Y,Z)=X+YZ (May 2015)</li> <li>(b) convert the following logic system into NAND gates only. (May 2015)</li> </ul>                                           | BTL-5 | Evaluating  | PO1,<br>PO2,<br>PO3,<br>PO4 |

| 5 | Simply the following Boolean expression in (i) sum of<br>product (ii) product of sum using k-map<br>AC'+B'D+A'CD+ABCD ( <b>May 2015</b> )                                                                                                               | BTL-5 | Evaluating  | PO1,<br>PO2,<br>PO3,<br>PO4 |

| 6 | Simplify the Boolean function in SOP and POS<br>$F(A,B,C,D)=\sum m(0,1,2,5,8,9,10)$ ( <b>Dec2014</b> )<br>(ii) plot the following Boolean function in k-map and<br>simplify it. $F(w,x,y,z) = \sum m(0,1,2,4,5,6,8,9,12,13,14)$ .<br>( <b>Dec2014</b> ) | BTL-5 | Evaluating  | PO1,<br>PO2,<br>PO3,<br>PO4 |

| 7 | Simply the function $F(w,x,y,z) = \sum m(2,3,12,13,14,15)$<br>using tabulation method .Implement the simplified using gates.( <b>Dec2014</b> )                                                                                                          | BTL-5 | Evaluating  | PO1,<br>PO2,<br>PO3,<br>PO4 |

| 8 | MinimizetheexpressionusingquineMccluskey(tabulation) $F=\sum m(0,1,9,15,24,29,30)$                                                                                                                                                                      | BTL-6 | Creating    | PO1,<br>PO2,                |

|    | $+\sum d(8,11,31)$ . method ( <b>June 2014</b> )                                                                                                                                                                                                                                                                                               |               |            | PO3,<br>PO4                 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------|-----------------------------|

| 9  | Simplify the following functions using K-map technique (June 2014) $G=\sum m$ (0,1,3,7,9,11) (ii) $f(w,x;y,z)=\sum m(0,7,8,9,10,12)+\sum d(2,5,13).$                                                                                                                                                                                           | BTL-5         | Evaluating | PO1,<br>PO2,<br>PO3,<br>PO4 |

| 10 | Simplify the given boolean function in POS form using K-<br>map and draw the logic diagram using Only NOR gates<br>$F(A,B,C,D) = \sum m  (0,1,4,7,8,10,12,15)+d(2,6,11,14).$<br>( <b>Dec2013</b> )<br>ii)Convert 78.5 <sub>10</sub> into binary.<br>iii)Find the dual and complement of the following Boolean<br>expression Xyz'+x'yz+z(xy+w). | BTL-5         | Evaluating | PO1,<br>PO2,<br>PO3,<br>PO4 |

| 11 | 3.Simplify the Boolean function using QuineMcCluskey met<br>F (A, B, C, D,E) = $\sum m (0,1,3,7,13,14,21,26,28) + \sum d(2,5,9,11,17,24)$ ( <b>Dec 2013</b> )                                                                                                                                                                                  | hod:<br>BTL-5 | Evaluating | PO1,<br>PO2,<br>PO3,<br>PO4 |

| 12 | Reduce the following function using K-map technique.<br>(Dec 2012)<br>i) f (A, B, C) = $\sum m (0,1,3,7) + \sum d (2,5)$<br>ii) F (w,x,y,z) = $\sum m (0,7,8,9,10,12) + \sum d (2,5,13)$                                                                                                                                                       | BTL-5         | Evaluating | PO1,<br>PO2,<br>PO3,<br>PO4 |

| 13 | Similify the following Boolean function F using Tabulation method.<br>i) F (A, B, C, D) = $\sum m (0,6,8,13,14)$ , d (A, B, C, D)= $\sum m (2,4,10)$ (Dec 2012)<br>ii) F (A, B, C, D) = $\sum m (1,3,5,7,9,15)$ , d (A, B, C, D)= $\sum m (4,6,12,13)$                                                                                         | BTL-5         | Evaluating | PO1,<br>PO2,<br>PO3,<br>PO4 |

#### UNIT II

#### **CCOMBINATIONAL LOGIC**

Combinational Circuits – Analysis and Design Procedures - Binary Adder-Subtractor - Decimal Adder - Binary Multiplier - Magnitude Comparator - Decoders – Encoders – Multiplexers - Introduction to HDL – HDL Models of Combinational circuits.

#### PART – A

CO Mapping : CO202. 2

| S.<br>N<br>o. | Question                                                                                                                                                                            | Blooms<br>Taxanom<br>y Level | Competence  | РО         |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------|------------|

| 1             | Design the combinational circuit with 3 inputs and 1<br>output. The output is 1 when the binary value of the<br>input is less than 3. The output is 0 otherwise.<br>(May/June 2016) | BTL-1                        | Remembering | PO1        |

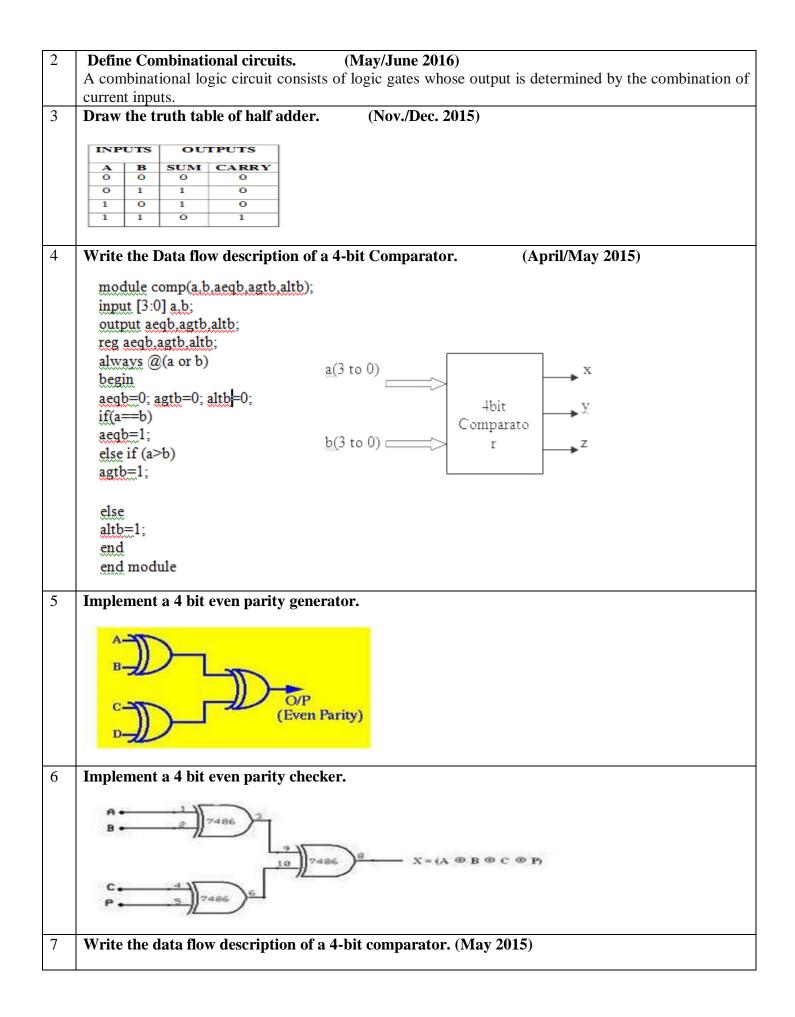

| 2             | Define Combinational circuits. (May/June 2016)                                                                                                                                      | BTL-1                        | Remembering | PO1        |

| 3             | Draw the truth table of half adder. (Nov./Dec.<br>2015)                                                                                                                             | BTL-1                        | Remembering | PO1        |

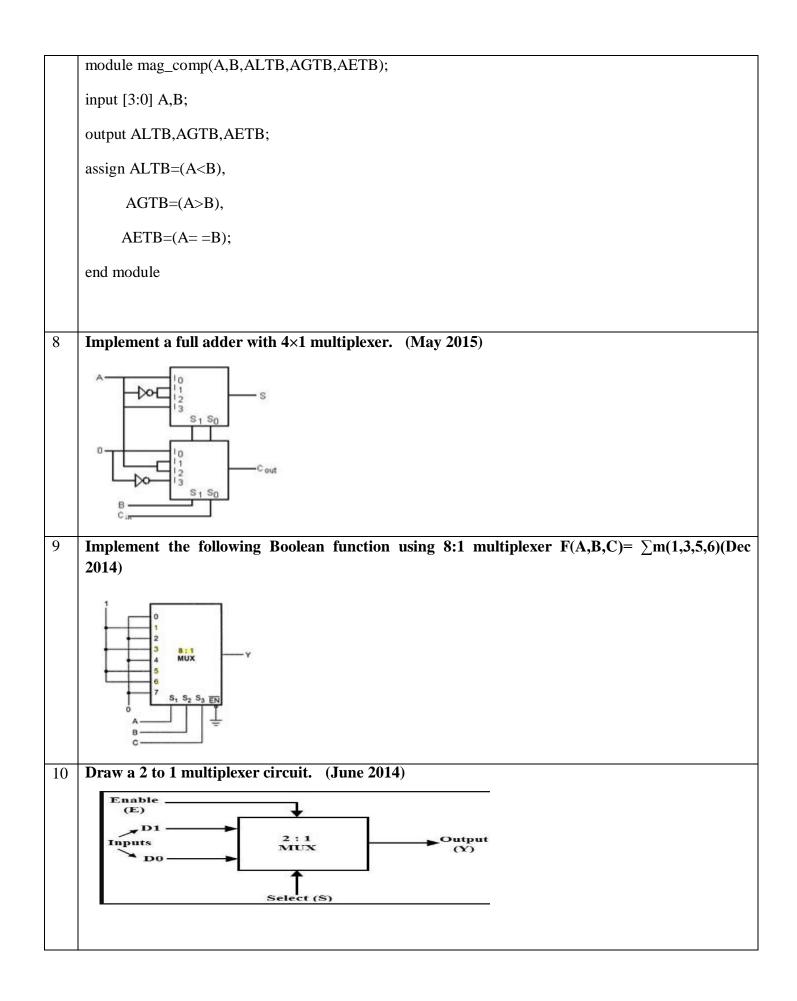

| 4             | Write the Data flow description of a 4-bit Comparator.<br>(April/May 2015)                                                                                                          | BTL-1                        | Remembering | PO1        |

| 5             | Implement a 4 bit even parity generator.                                                                                                                                            | BTL-1                        | Remembering | PO1        |

| 6             | Implement a 4 bit even parity checker.                                                                                                                                              | BTL-1                        | Remembering | PO1        |

| 7             | Write the data flow description of a 4-bit comparator.<br>(May 2015)                                                                                                                | BTL-1                        | Remembering | PO1        |

| 8             | Implement a full adder with 4×1 multiplexer. (May 2015)                                                                                                                             | BTL-1                        | Remembering | PO1        |

| 9             | Implement the following Boolean function using 8:1 multiplexer $F(A,B,C) = \sum m(1,3,5,6)(Dec 2014)$                                                                               | BTL-1                        | Remembering | PO1        |

| 10            | Draw a 2 to 1 multiplexer circuit. (June 2014)                                                                                                                                      | (June<br>2014)               | Remembering | PO1        |

| 11            | What is priority encoder? (Dec 2014)                                                                                                                                                | BTL-1                        | Remembering | PO1        |

| 12            | Draw the truth table and circuit diagram of 4 to 2 encoder. (Dec 2013)                                                                                                              | BTL-1                        | Remembering | PO1        |

| 13            | Obtain the truth table for BCD to Excess-3 code converter. (Dec 2013)                                                                                                               | BTL-1                        | Remembering | PO1        |

| 14            | Write the stimulus for 2 to 1 line MUX. (June 2012)                                                                                                                                 | BTL-1                        | Remembering | PO1        |

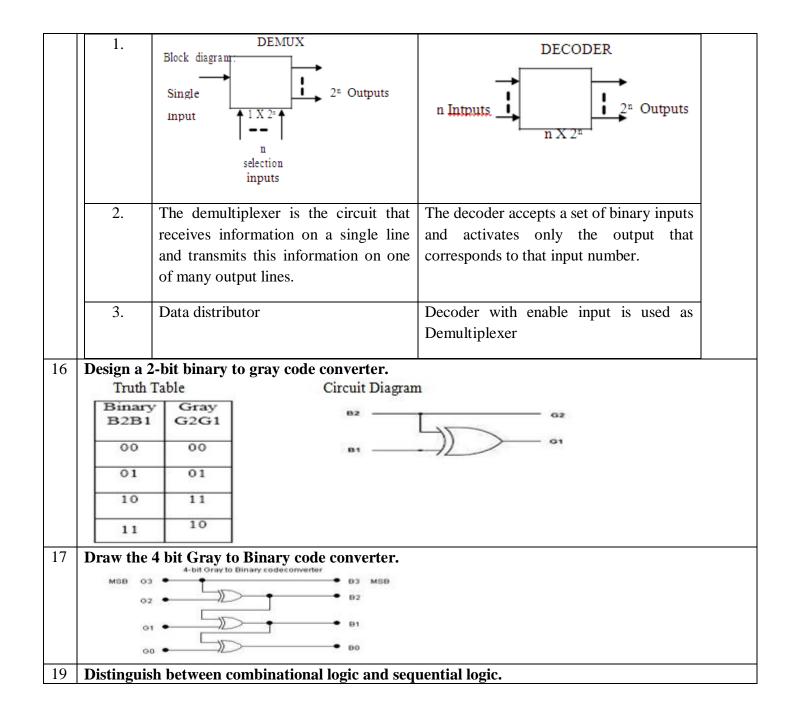

| 15            | Distinguish between a decoder and a demultiplexer.<br>(June 2012)                                                                                                                   | BTL-1                        | Remembering | PO1        |

| 16            | Design a 2-bit binary to gray code converter.                                                                                                                                       | BTL-1                        | Remembering | PO1        |

| 17            | Draw the 4 bit Gray to Binary code converter.                                                                                                                                       | BTL-1                        | Remembering | <b>PO1</b> |

| 18            | Draw the 4 bit Binary to Gray code converter.                                                                                                                                       | BTL-1                        | Remembering | <b>PO1</b> |

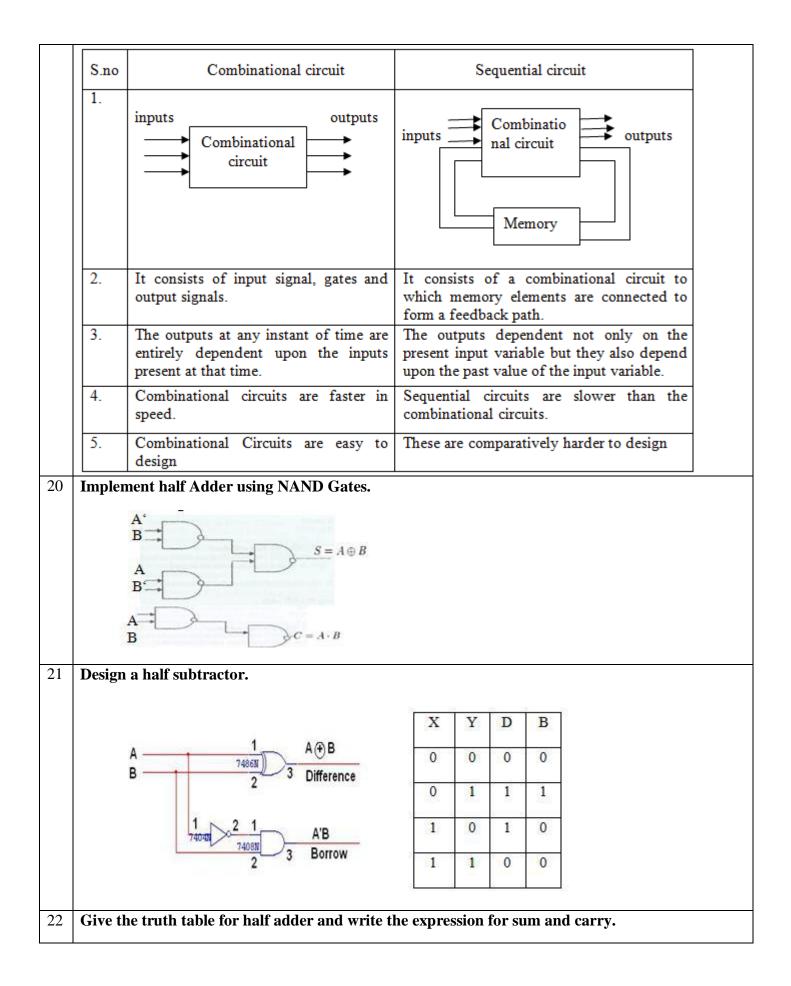

| 19            | Distinguish between combinational logic and sequential logic.                                                                                                                       | BTL-1                        | Remembering | PO1        |

| 20 | Implement half Adder using NAND Gates.                                                                                                                                                                                                                                                                                                                                                                                                               | BTL-1 | Remembering | PO1                         |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------|-----------------------------|

| 21 | Design a half subtractor.                                                                                                                                                                                                                                                                                                                                                                                                                            | BTL-1 | Remembering | PO1                         |

| 22 | Give the truth table for half adder and write the expression for sum and carry.                                                                                                                                                                                                                                                                                                                                                                      | BTL-5 | Evaluating  | PO1,<br>PO2,<br>PO3,<br>PO4 |

| 23 | Mention the different type of binary codes.                                                                                                                                                                                                                                                                                                                                                                                                          | BTL-1 | Remembering | PO1                         |

| 24 | What is meant by self-complementing code?                                                                                                                                                                                                                                                                                                                                                                                                            | BTL-1 | Remembering | <b>PO1</b>                  |

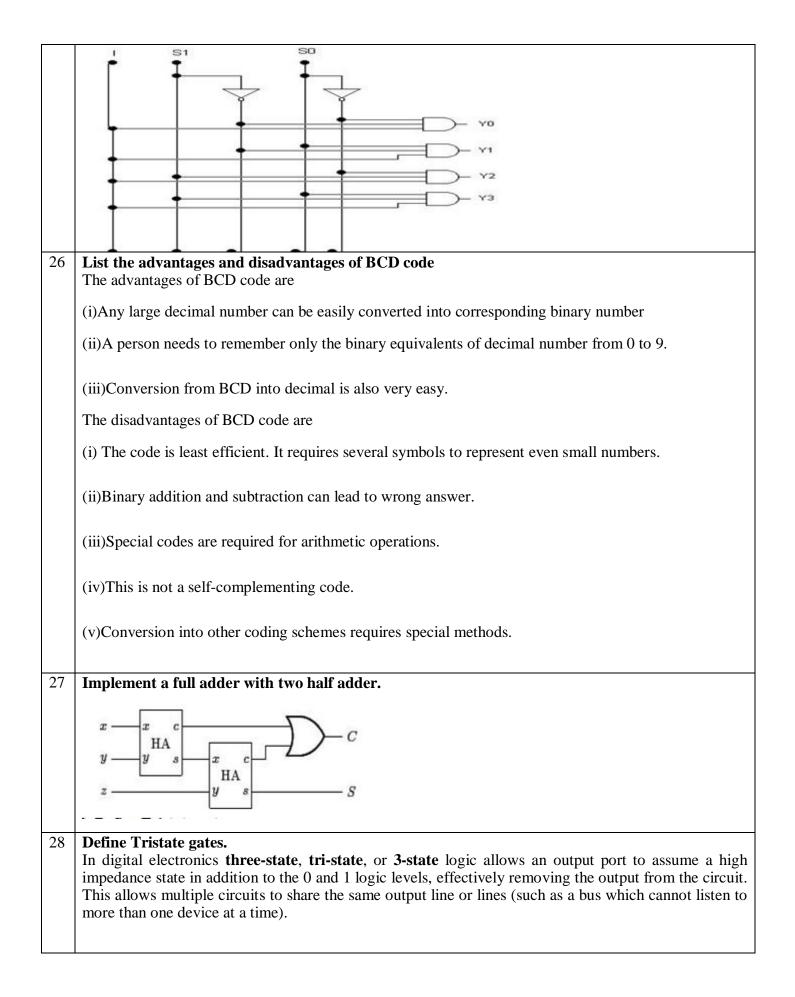

| 25 | Draw the logic diagram of a one to four line de-<br>multiplexer.                                                                                                                                                                                                                                                                                                                                                                                     | BTL-1 | Remembering | PO1                         |

| 26 | List the advantages and disadvantages of BCD code                                                                                                                                                                                                                                                                                                                                                                                                    | BTL-1 | Remembering | <b>PO1</b>                  |

| 27 | Implement a full adder with two half adder.                                                                                                                                                                                                                                                                                                                                                                                                          | BTL-1 | Remembering | PO1                         |

| 28 | Define Tristate gates.                                                                                                                                                                                                                                                                                                                                                                                                                               | BTL-5 | Evaluating  | PO4                         |

| 29 | Define logic synthesis and simulation.                                                                                                                                                                                                                                                                                                                                                                                                               | BTL-1 | Remembering | <b>PO1</b>                  |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |             |                             |

| 1  | PART BImplement the following Boolean function with 4 X 1                                                                                                                                                                                                                                                                                                                                                                                            |       |             |                             |

|    | multiplexer and external gates. Connect inputs A and B to<br>the selection lines. The input requiremnts for the four data<br>lines will be a function of variables C and D these values are<br>obatined by expressing F as a function of C and D for each<br>four cases when AB = 00, 01, 10 and 11. These functions<br>may have to be implemented with external gates. F(A, B, C,<br>D) = $\Sigma$ (1, 2, 5, 7, 8, 10, 11, 13, 15). (May/June 2016) | BTL-5 | Evaluating  | PO1,<br>PO2,<br>PO3,<br>PO4 |

| 2  | Design a full adder with x, y, z and two outputs S and C. The circuits performs x+y+z, z is the input carry, C is the output carry and S is the Sum. (May/June 2016)                                                                                                                                                                                                                                                                                 | BTL-6 | Creating    | PO1,<br>PO2,<br>PO3         |

| 3  | Design a code converter thet converts a 8421 to BCD code.<br>(Nov./Dec. 2015)                                                                                                                                                                                                                                                                                                                                                                        | BTL-5 | Evaluating  | PO1,<br>PO2,<br>PO3,<br>PO4 |

| 4  | (i) Explain the Analysis procedure. Analyze the following logic diagram. (April/May 2015)                                                                                                                                                                                                                                                                                                                                                            | BTL-5 | Evaluating  | PO1,<br>PO2,<br>PO3,<br>PO4 |

|    | (ii) With neat diagram explain the 4-bit adder with carry lookahead.                                                                                                                                                                                                                                                      |                                              |               |                             |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------|-----------------------------|

| 5  | <ul> <li>(a) Design 2-bit magnitude comparator and write a verilog HDL code. (Dec 2015)</li> <li>(b)Implement the following Boolean functions with a multiplexer: F(w,x,y,z)= ∑(2,3,5,6,11,14,15)</li> <li>(c) Construct a 5 to 32 line decoder using 3 to 8 line decoders and 2 to 4 line decoder. (May 2015)</li> </ul> | BTL-2                                        | Understanding | PO1,<br>PO2                 |

| 6  | Design and implement a 8241 to gray code converter.<br>Realize the converter using only NAND gates ( <b>Dec 2014</b> )                                                                                                                                                                                                    | BTL-5                                        | Evaluating    | PO1,<br>PO2,<br>PO3,<br>PO4 |

| 7  | Design a circuit that converts 8421 BCD code to Excess-3 (June 2014)<br>(b) Implement the following using 8 to 1 multiplexer.<br>(June 2014)                                                                                                                                                                              | BTL4                                         |               |                             |

| 8  | <ul> <li>(i).Realize 4 x 16 decoder using two 3 x 8 decoders with enable input.</li> <li>(ii) Implement the following functions using a multiplexer.</li> <li>F(W,X,Y,Z)=∑m (0,1,3,4,8,9,15). (Dec 2013)</li> </ul>                                                                                                       | BTL-2                                        | Understanding | PO1,<br>PO2                 |

| 9  | <ul> <li>5.(i).Design a combinational circuit to perform BCD addition.</li> <li>(ii).Design a 4-bit magnitude comparator with three outputs :A<b ,a="">B. (Dec 2013)</b></li> </ul>                                                                                                                                       | (Dec<br>2013)                                | Creating      | PO1,<br>PO2,<br>PO3         |

| 10 | Construct a 4 to 16 line decoder with an enable input using five 2 to 4 line decoders with enable inputs. ( <b>June 2012</b> )                                                                                                                                                                                            | $F(W,X,Y, Z) = \sum m \\ (0,1,3,4,8, 9,15).$ | Understanding | PO1,<br>PO2                 |

| 11 | Design a BCD to 7 segment decoder and implement it by using basic gates. (Dec 2012)                                                                                                                                                                                                                                       | BTL-6                                        | Creating      | PO1,<br>PO2,<br>PO3         |

| 12 | 1. Discuss the need and working principle of Carry Look ahead adder. (Dec 2012)                                                                                                                                                                                                                                           | BTL-5                                        | Evaluating    | PO1,<br>PO2,<br>PO3,<br>PO4 |

| 13 | Design a full adder using 2 half adders.                                                      | BTL-5 | Evaluating | PO1,<br>PO2,<br>PO3,<br>PO4 |

|----|-----------------------------------------------------------------------------------------------|-------|------------|-----------------------------|

| 14 | Design a logic circuit that accepts a 4 bit Gray code and converts it into 4 bit binary code. | BTL-5 | Evaluating | PO1,<br>PO2,<br>PO3,<br>PO4 |

UNIT III SYNCHRONOUS SEQUENTIAL LOGIC Sequential Circuits - Storage Elements: Latches , Flip-Flops - Analysis of Clocked Sequential Circuits -State Reduction and Assignment - Design Procedure - Registers and Counters - HDL Models of Sequential Circuits.

|          | PART – A                                                                                    |                              |             |                     |

|----------|---------------------------------------------------------------------------------------------|------------------------------|-------------|---------------------|

|          | Mapping : CO202. 3                                                                          | •                            | -           |                     |

| S.<br>No | Question                                                                                    | Blooms<br>Taxanom<br>y Level | Competence  | PO                  |

| 1        | State the excitation table of JK Flip Flop.<br>(May/June 2016)                              | BTL-1                        | Remembering | PO1                 |

| 2        | What is the minimum number of flip flops needed to build a counter of modulus 8? (May 2016) | BTL-1                        | Remembering | PO1                 |

| 3        | Write short notes on propagation delay. (Nov./Dec. 2015)                                    | BTL-1                        | Remembering | PO1                 |

| 4        | Draw the diagram of T flip flop and discuss its working.<br>(Nov./Dec. 2015)                | BTL-1                        | Remembering | PO1                 |

| 5        | Give the block diagram of master-slave D flip- flop.<br>(May 2015)                          | BTL-1                        | Remembering | PO1                 |

| 6        | What is ring counter? (May 2015)                                                            | BTL-1                        | Remembering | PO1                 |

| 7        | How many states are there in 3-bit ring counter? What are they? (Dec 2014)                  | BTL-5                        | Evaluating  | PO1,<br>PO2,<br>PO3 |

| 8        | With reference to a JK flip-flop, what is racing?<br>(June/Dec 2014)                        | BTL-1                        | Remembering | PO1                 |

| 9        | What are Mealy and Moor machines? (Dec 2014)                                                | BTL-1                        | Remembering | PO1                 |

| 10       | Write the characteristics table and equation of JK flip<br>flop. (June 2014)                | BTL-1                        | Remembering | PO1                 |

| 11       | Write any two applications of shift registers. (June 2014)                                  | BTL-1                        | Remembering | PO1                 |

| 12       | Write the HDL code for up-down counter using behavioral model. (Dec 2013)                   | BTL-1                        | Remembering | PO1                 |

| 13 | Show D flip-flop implementation from a J-K flip-flop.                                                       | BTL-1    | Remembering   | PO1                 |

|----|-------------------------------------------------------------------------------------------------------------|----------|---------------|---------------------|

| 14 | (Dec 2013)<br>Give the truth table for J-K flip-flop.                                                       | BTL-1    | Remembering   | PO1                 |

| 15 | Show the T-Flipflop implementation from SR flipflop.                                                        | BTL-1    | Remembering   | PO1                 |

| 16 | What is meant by triggering of Flip flop?                                                                   | BTL-1    | Remembering   | PO1                 |

| 17 | Why D FF is known as Delay FF?                                                                              | BTL-1    | Remembering   | PO1                 |

| 18 | What is the minimum number of flip-flops needed to build a counter of modulus 60?                           | BTL-1    | Remembering   | PO1                 |

| 19 | What is a universal shift register?                                                                         | BTL-1    | Remembering   | PO1                 |

| 20 | What is meant by triggering of Flip flop?                                                                   | BTL-1    | Remembering   | PO1                 |

| 21 | Differentiate between sequential and combinational circuits.                                                | BTL-1    | Remembering   | PO1                 |

| 22 | Give difference between latch and flip-flop.                                                                | BTL-1    | Remembering   | PO1                 |

| 23 | How race around condition can be eliminated?                                                                | BTL-1    | Remembering   | PO1                 |

| 24 | How many flip flops are required to realize MOD 50 counter? (Dec 2012)                                      | BTL-1    | Remembering   | PO1                 |

| 25 | What is a Mealy circuit?                                                                                    | BTL-2    | Understanding | PO1,<br>PO2         |

| 26 | What is a state diagram?                                                                                    | BTL-1    | Remembering   | PO1                 |

| 27 | What is finite state machine?                                                                               | BTL-5    | Evaluating    | PO1,<br>PO2,<br>PO3 |

| 28 | What do you meant by the term state reduction problem?                                                      | BTL-2    | Understanding | PO1,<br>PO2         |

|    | PART B                                                                                                      | <b>،</b> |               |                     |

| 1  | Design a modulo 5 synchronous counter using JK Flip Flop<br>and implement it. Construct its timing diagram. | BTL-6    | Creating      | PO1,<br>PO2,        |

|    | (May/June 2016)                                                                                             |          |               | PO3                 |

| - |                                                                                                                                                                                                                                                            |       |            |                     |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|---------------------|

|   | x=1 $x=0,x=1$ $b$ $0$ $b$ $b$ $b$ $b$ $b$ $c$ $x=0,x=1$                                                                                                                                                                                                    |       |            |                     |

| 2 | Design a binary counter using T flip flops to count in the following sequences:<br>(i) 000, 001, 010, 011, 100, 101, 111, 000                                                                                                                              | BTL-6 | Creating   | PO1,<br>PO2,<br>PO3 |

| 2 | (ii) 000, 100, 111, 010, 011, 000<br>(May/June 2016)                                                                                                                                                                                                       |       |            | POI                 |

| 3 | Design three bit synchronous counter with T flip flop and draw the diagram. (Nov./ Dec 2015)                                                                                                                                                               | BTL-5 | Evaluating | PO1,<br>PO2,<br>PO3 |

| 4 | Design a sequence detector that detects a sequence of three<br>or more consecutive 1's in a string of bits coming through<br>an input line and produces an output whenever this sequence<br>is detected. (Nov./ Dec 2015)                                  | BTL-6 | Creating   | PO1,<br>PO2,<br>PO3 |

| 5 | Consider the design of 4-bit BCD counter that counts in the following way: (April/May 2015)<br>0000,0010,0011,,1001 and back to 0000<br>(i) Draw the state diagram                                                                                         | BTL-5 | Evaluating | PO1,<br>PO2,<br>PO3 |

|   | <ul><li>(ii) List the next state table</li><li>(iii)Draw the logic diagram of the circuit</li></ul>                                                                                                                                                        |       |            |                     |

| 6 | <ul> <li>i) A sequential circuit with two D flip-flops A and B, one input x and one output z is specified by the following next-state and output equations:<br/>(April/May 2015)</li> </ul>                                                                | BTL-6 | Creating   | PO1,<br>PO2,<br>PO3 |

|   | A(t+1)= A'+B, B(t+1)=B'x, z=A+B'<br>(1) Draw the logic diagram of the circuit<br>(2) Draw the state table<br>(3) Draw the state diagram of the circuit<br>ii) Explain the difference between a state table,<br>characteristics table and excitation table. |       |            |                     |

| 7  | <ul> <li>(a) Design a MOD-10 synchronous counter using JK flipflops. Write execution table and state table. (Dec 2014)</li> <li>(b) i) A sequential circuit with two D flips- flops A and B, one input x, and one output z is specified by the following next state and output equations:</li> <li>A (t+1) = A'+B, B(t+1)= B'x, z=A+B'.</li> <li>(1) Draw the logic diagram of the circuit. (2) Derive the state table (3) Draw the state diagram of the circuit. (May 2015)</li> </ul> | BTL-6 | Creating   | PO1,<br>PO2,<br>PO3 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|---------------------|

| 8  | <ul> <li>(i)Design a shift register using JK flip flops .(May 2015)</li> <li>(ii) Explain the difference between a state table, characteristics table and an excitation table</li> </ul>                                                                                                                                                                                                                                                                                                | BTL-5 | Evaluating | PO1,<br>PO2,<br>PO3 |

| 9  | <ul> <li>(i) How race condition can be avoided in a flip flops? (Dec 2014)</li> <li>(ii) Realize the sequential circuit for the state diagram show below. (Dec 2014)</li> </ul>                                                                                                                                                                                                                                                                                                         | BTL-5 | Evaluating | PO1,<br>PO2,<br>PO3 |

| 10 | Design a synchronous counter that counts the sequence 000,001,010,011,100,101,110,111,000<br>Using D flipflop ( <b>June 2014</b> )                                                                                                                                                                                                                                                                                                                                                      | BTL-5 | Evaluating | PO1,<br>PO2,<br>PO3 |

| 11 | Implement T flipflop using D flipflop and JK flipflop using D flipflop. ( <b>June 2014</b> )                                                                                                                                                                                                                                                                                                                                                                                            | BTL-6 | Creating   | PO1,<br>PO2,<br>PO3 |

| 12 | Design a sequential circuit by the following state diagram<br>using T-flip flops. (Dec 2013)                                                                                                                                                                                                                                                                                                                                                                                            | BTL-5 | Evaluating | PO1,<br>PO2,<br>PO3 |

| 13            | Design a synchronous counter with the following sequence: 0,1,3,7,6,4 and repeats. ( <b>Dec 2013</b> )                                                                                                                                                                                                                                                   | BTL-5                                                  | Evaluatin                                                                                    | g PO1,<br>PO2,<br>PO3    |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------|

| 14            | <ul> <li>2. i) Write behavioural VHDL Description of 8 bit shift register with direct reset.</li> <li>ii)What is the difference serial and parallel transfer? Explain how to convert parallel data to serial and serial data to parallel. What type of register is needed? (Dec 2012)</li> </ul>                                                         | BTL-5                                                  | Evaluatin                                                                                    | g PO1,<br>PO2,<br>PO3    |

| 15            | Using D flip flops, design a synchronous counter which counts in the sequence, 000,001,010,011,100,101,110,111,000                                                                                                                                                                                                                                       | BTL-5                                                  | Evaluatin                                                                                    | g PO1,<br>PO2,<br>PO3    |

| 16            | Design synchronous mod 16 counter using JK flip flop.<br>(Dec 2012)                                                                                                                                                                                                                                                                                      | BTL-5                                                  | Evaluating                                                                                   | PO1,<br>PO2,<br>PO3      |

|               | UNIT IV                                                                                                                                                                                                                                                                                                                                                  |                                                        |                                                                                              |                          |

|               | COMBINATIONAL LOGI                                                                                                                                                                                                                                                                                                                                       | (C                                                     |                                                                                              |                          |

|               |                                                                                                                                                                                                                                                                                                                                                          |                                                        |                                                                                              |                          |

| CO<br>S.<br>N | PART – A<br>Mapping : CO202.4<br>Question                                                                                                                                                                                                                                                                                                                | Blooms<br>Taxanom                                      | Competenc<br>e                                                                               | РО                       |

| S.            | Mapping : CO202.4                                                                                                                                                                                                                                                                                                                                        |                                                        | -                                                                                            | PO<br>PO1                |

| S.<br>N       | Mapping :       CO202.4         Question         Define the critical race and non critical race. (May/June                                                                                                                                                                                                                                               | Taxanom<br>y Level                                     | e<br>Rememberi                                                                               |                          |

| S.<br>N       | Mapping :       CO202.4         Question         Define the critical race and non critical race. (May/June 2016)                                                                                                                                                                                                                                         | Taxanom<br>y Level<br>BTL-1                            | e<br>Rememberi<br>ng<br>Rememberi                                                            | PO1                      |

| S.<br>N       | Mapping :       CO202.4         Question         Define the critical race and non critical race. (May/June 2016)         What is lockout? How is avoided? (May/June 2016)         What is critical race condition? Give example.                                                                                                                         | Taxanom<br>y Level<br>BTL-1<br>BTL-1                   | e<br>Rememberi<br>ng<br>Rememberi<br>ng<br>Understand<br>ing<br>Rememberi                    | PO1<br>PO1               |

| S.<br>N       | Mapping :       CO202.4         Question         Define the critical race and non critical race. (May/June 2016)         What is lockout? How is avoided? (May/June 2016)         What is critical race condition? Give example. (APR/MAY 2015)                                                                                                          | Taxanom<br>y Level<br>BTL-1<br>BTL-1<br>BTL-2          | e<br>Rememberi<br>ng<br>Rememberi<br>ng<br>Understand<br>ing                                 | PO1<br>PO1<br>PO2        |

| S.<br>N       | Mapping :       CO202.4         Question         Define the critical race and non critical race. (May/June 2016)         What is lockout? How is avoided? (May/June 2016)         What is critical race condition? Give example. (APR/MAY 2015)         What is race condition? (Nov./Dec. 2015)         Define critical race in asynchronous sequential | Taxanom<br>y Level<br>BTL-1<br>BTL-1<br>BTL-2<br>BTL-2 | e<br>Rememberi<br>ng<br>Rememberi<br>ng<br>Understand<br>ing<br>Rememberi<br>ng<br>Rememberi | PO1<br>PO1<br>PO2<br>PO1 |

| What are the types of hazards?(May/June2014)                                          | BTL-2 | Understand<br>ing | PO2    |

|---------------------------------------------------------------------------------------|-------|-------------------|--------|

| What is a Hazard? (June 2012/Dec 2014)                                                | BTL-2 | Understand<br>ing | PO1    |

| Difference between fundamental mode circuits and pulse-mode circuits. (Dec 2013)      |       |                   |        |

| What is Primitive Flow table? (Dec 2013)                                              | BTL-1 | Rememberi<br>ng   | PO1    |

| What are cycles and races? (June 2012)                                                | BTL-1 | Rememberi<br>ng   | PO1    |

| What are the different types of shift type? (Dec 2012)                                |       | 0                 |        |

| What do you mean by Race condition? (Dec 2012/June 2014)                              | BTL-1 | Rememberi<br>ng   | PO1    |

| Why is the pulse mode operation of asynchronous sequential circuits not very popular? | BTL-2 | Understand ing    | PO1,PO |

| Differentiae Static & Dynamic Hazard                                                  | BTL-1 | Rememberi<br>ng   | PO1    |

| What is ASM chart?                                                                    | BTL-1 | Rememberi<br>ng   | PO1    |

| What is State Assignment?                                                             | BTL-1 | Rememberi<br>ng   | PO1    |

| Define Essential Hazard.                                                              | BTL-1 | Rememberi<br>ng   | PO1    |

| Define Flow table.                                                                    | BTL-1 | Rememberi<br>ng   | PO1    |

| Define Merger diagram.                                                                | BTL-2 | Understand<br>ing | PO2    |

| Explain Hazards in sequential circuits.                                               | BTL-2 | Understand<br>ing | PO2    |

| Explain Multiple row method.                                                          | BTL-2 | Understand<br>ing | PO2    |

| What is the reason for essential hazard to occur?                                     | BTL-1 | Rememberi<br>ng   | PO1    |

| Define the term Maximal compatible.                                                   | BTL-1 | Rememberi<br>ng   | PO1    |

| Define closed covering.                                                               | BTL-1 | Rememberi<br>ng   | PO1    |

| Explain Shared Row method.                                                            | BTL-2 | Understand<br>ing | PO2    |

| What is the need of state reduction in sequential circuit design?                     | BTL-2 | Understand<br>ing | PO2    |

| What is the use of flip-flop excitation table?                                        | BTL-1 | Rememberi<br>ng   | PO1    |

|   | List any two drawbacks of                                                                                                                                                                                                            | f asynchronous ci                    | rcuits.                           | BTL-1          | Rememberi<br>ng   | PO1             |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------------|----------------|-------------------|-----------------|

|   |                                                                                                                                                                                                                                      | PART B                               |                                   |                |                   |                 |

| 1 | Discuss in detail the proce<br>with an example. (Ma                                                                                                                                                                                  | dure for reducing y/June 2016)       | the flow table                    | BTL-5          | Evaluating        | PO1,PO2,<br>PO3 |

|   | Design an asynchronous se<br>and Y and with one output<br>transferred to Z. When Y is<br>any change in X. Use SR<br>circuit. (May/June 2016)                                                                                         | T Z Wherever Y is 0; the output does | s 1, input X is<br>not change for | BTL-5          | Evaluating        | PO1,PO2,<br>PO3 |

|   | Design a serial adder using<br>(Nov./Dec. 2                                                                                                                                                                                          |                                      | lip flop.                         | BTL-5          | Evaluating        | PO1,PO2,<br>PO3 |

|   | Explain about hazards in dig                                                                                                                                                                                                         | gital systems. ( <b>Ma</b>           | y 2015)                           | BTL-2          | Understand<br>ing | PO2             |

|   | Analyze the following cloc<br>the state equations and state<br>x<br>(Nov./Dec. 2/<br>(a) Explain the Page free                                                                                                                       | e diagram.                           |                                   | BTL-6<br>BTL-6 | Creating          | PO1,PO2,<br>PO3 |

|   | <ul> <li>(a) Explain the Race- free state assignment procedure.</li> <li>(b) Reduce the number of states in the following state diagram. Tabulated the reduced state table and Draw the reduced state diagram. (May 2015)</li> </ul> |                                      |                                   | D1L-0          | Creating          | PO1,PO2,<br>PO3 |

|   |                                                                                                                                                                                                                                      | x=0 x=1                              | x=0,x=1                           |                |                   |                 |

|   | a a                                                                                                                                                                                                                                  | b                                    | 0.0                               |                |                   |                 |

|    | b                                                                                                                                                                                                                                                                                        | c d                                                              | 0 0                                                               |       |            |                 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------|-------|------------|-----------------|

|    | с                                                                                                                                                                                                                                                                                        | a d                                                              | 0 0                                                               |       |            |                 |

|    | d                                                                                                                                                                                                                                                                                        | e f                                                              | 0 1                                                               |       |            |                 |

|    | e                                                                                                                                                                                                                                                                                        | a f                                                              | 0 1                                                               |       |            |                 |

|    | f                                                                                                                                                                                                                                                                                        | g f                                                              | 0 1                                                               |       |            |                 |

|    | g                                                                                                                                                                                                                                                                                        | a f                                                              | 0 1                                                               |       |            |                 |

| 5  | Explain the steps in circuits. (June 2014)                                                                                                                                                                                                                                               | designing asyncl                                                 | hronous sequential                                                | BTL-6 | Creating   | PO1,PO2,<br>PO3 |

| 6  | Implement the switching<br>by a static hazard free<br>(June 2014)                                                                                                                                                                                                                        |                                                                  |                                                                   | BTL-5 | Evaluating | PO1,PO2,<br>PO3 |

| 7  | (June 2014)A synchronous sequential circuit is described by the<br>following excitation and output functionY=X1X2+(X1+X2)Y, Z=Y. (i) Draw the logic diagram of<br>the circuit. (ii) derive the transition table and output map.(iii)<br>describe the behavior of the circuit. (Dec 2014) |                                                                  |                                                                   |       | Creating   | PO1,PO2,<br>PO3 |

| 8  | Design a synchronous of following sequence 7, 4                                                                                                                                                                                                                                          | U                                                                |                                                                   | BTL-6 | Creating   | PO1,PO2,<br>PO3 |

| 9  | Design an asynchrono<br>and x2 and one output<br>inputs are 0, output is e<br>z becomes 1. When se<br>output stays at 0 untr<br>( <b>Dec 2013</b> )                                                                                                                                      | z. Initially and at a<br>equal to 0. When x<br>cond input also b | any time if both the<br>al or x2 becomes 1,<br>ecomes 1, z=0; the | BTL-6 | Creating   | PO1,PO2,<br>PO3 |

| 10 | (i) What is the objective<br>circuit? Explain race-fr<br>( <b>Dec2013</b> )                                                                                                                                                                                                              |                                                                  |                                                                   | BTL-6 | Creating   | PO1,PO2,<br>PO3 |

|    | ii) Discuss about stati-<br>asynchronous sequentia                                                                                                                                                                                                                                       |                                                                  | essential hazards in                                              |       |            |                 |

| 11 | Give the design Proced circuit. ( <b>Dec 2012</b> )                                                                                                                                                                                                                                      | ure for asynchrono                                               | ous sequential                                                    | BTL-5 | Evaluating | PO1,PO2,<br>PO3 |

#### UNIT V MEMORY AND PROGRAMMABLE LOGIC

|    | PART – A                                                           |         |               |         |

|----|--------------------------------------------------------------------|---------|---------------|---------|

| CO | Mapping : CO202.5                                                  |         |               |         |

| S. | Question                                                           | Blooms  | Competence    | PO      |

| Ν  |                                                                    | Taxanom |               |         |

| 0. |                                                                    | y Level |               |         |

| 1  | Draw the waveforms showing static 1 hazard?<br>(May/June 2016)     | BTL-1   | Remembering   | PO1,PO2 |

| 2  | Write short notes on PLA. (Nov./Dec. 2015)                         | BTL-1   | Remembering   | PO1,PO2 |

| 3  | What is memory address register? (Nov./Dec. 2015)                  | BTL-1   | Remembering   | PO1,PO2 |

| 4  | How to detect double error and correct single error?<br>(May 2015) | BTL-2   | Understanding | PO1     |

| 5  | Differentiate between EEPROM and PROM. (May 2015)                  | BTL-2   | Understanding | PO1     |

| 6  | What is a volatile memory? Give example. (Dec 2014)                | BTL-1   | Remembering   | PO1,PO2 |

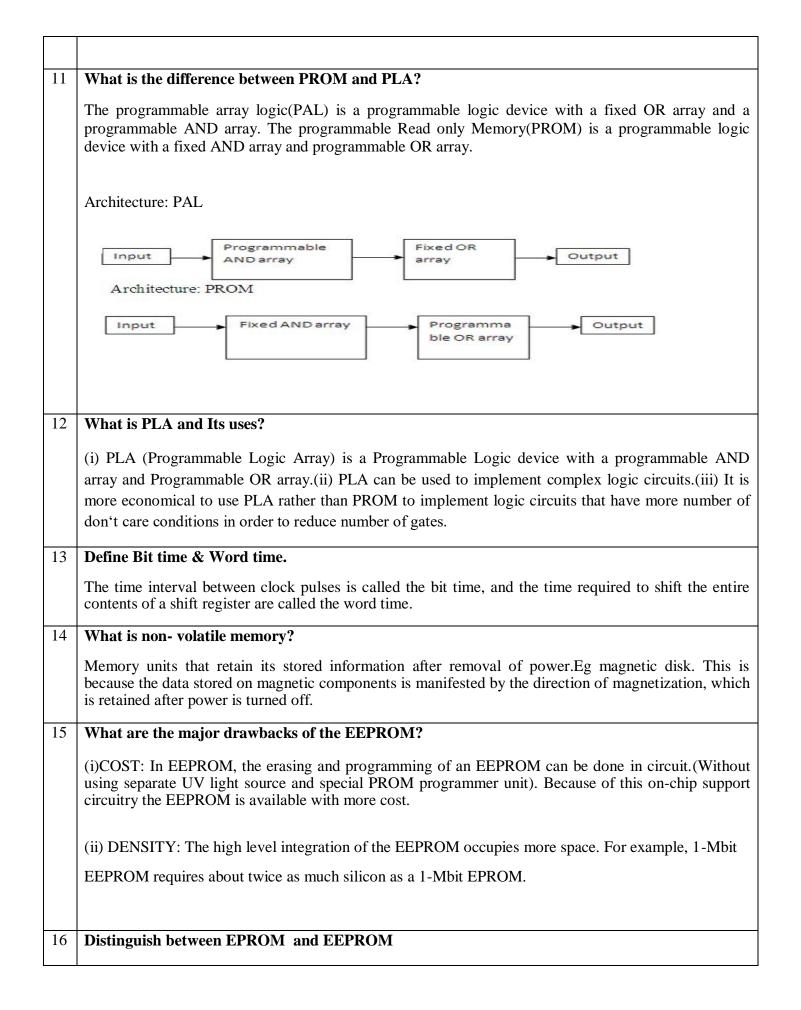

| 7  | What is memory decoding? (June 2014)                               | BTL-1   | Remembering   | PO1,PO2 |