# CSC 322: Computer Organization Lab

Lecture 3: Logic Design

Dr. Haidar M. Harmanani

# CSC 322: Computer Organization Lab

Part I: Combinational Logic

Dr. Haidar M. Harmanani

# Logical Design of Digital Systems

- Complex Combinational and Sequential networks (up to thousands of gates)

- Emphasis on combined datapath + Finite state machine designs for real time applications

- Modern CAD tool usage (schematic entry, simulation, technology mapping, timing analysis, synthesis)

- Logic Synthesis via Verilog

- Modern implementation technologies such as Field Programmable Gate Arrays (FPGAs)

CSC 322: Computer Organization Lab

3 LAU

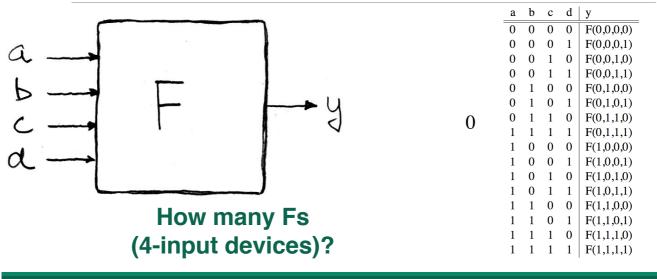

### **Truth Tables**

المالية المدينة المركمة المركمة

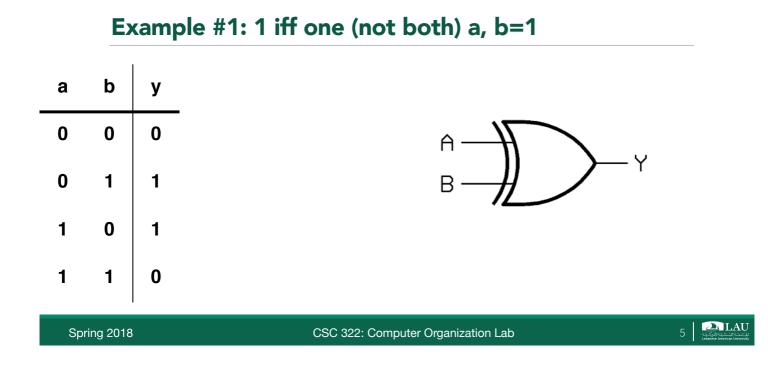

# How about a 3-input XOR Gate?

- Easy. Extend the truth table

- How about N-input XOR is the only one which isn't so obvious

- It's simple: XOR is a 1 iff the # of 1s at its input is odd

| a | b | с | У |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

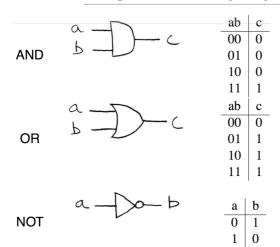

# Logic Gates (1/2)

Spring 2018

CSC 322: Computer Organization Lab

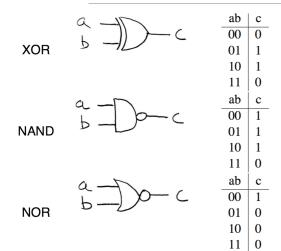

# Logic Gates (2/2)

Spring 2018

# Example 2: Design a 2-bit Unsigned Adder

| $ \begin{array}{c} A \\ 2 \\ 2 \\ + \\ 3 \\ C \end{array} $ | How<br>many<br>rows in<br>the truth<br>table? | $\begin{array}{c} A \\ a_1 a_0 \\ 00 \\ 00 \\ 00 \\ 01 \\ 01 \\ 01 \\ 01 \\ $ | $\begin{array}{c} B \\ b_1 b_0 \\ 00 \\ 01 \\ 10 \\ 11 \\ 00 \\ 01 \\ 10 \\ 11 \\ 00 \\ 01 \\ 11 \\ 00 \\ 01 \\ 11 \\ 10 \\ 11 \\ 11 \\ \end{array}$ | $\begin{array}{c} C \\ \hline c_2 c_1 c_0 \\ \hline 000 \\ 001 \\ 010 \\ 011 \\ 001 \\ 010 \\ 011 \\ 100 \\ 011 \\ 100 \\ 101 \\ 101 \\ 100 \\ 101 \\ 110 \\ 110 \\ \end{array}$ |

|-------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Spring 2018                                                 | CSC 322: Computer Organization Lab            |                                                                               |                                                                                                                                                      | 9                                                                                                                                                                                |

# Example 3: Design of a 32-bit adder

| А     | В     | C      |       |

|-------|-------|--------|-------|

| 000 0 | 000 0 | 000 00 |       |

| 000 0 | 000 1 | 000 01 | How   |

| •     | •     | •      | Many  |

| •     | •     | •      | Rows? |

| •     | •     | •      |       |

| 111 1 | 111 1 | 111 10 |       |

**D**LAU

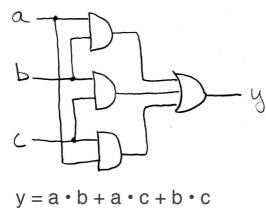

# **Example 5: Majority Function**

y = ab + ac + bc

Spring 2018

CSC 322: Computer Organization Lab

11

# Example 4: 3-input majority circuit

# **Boolean Algebra**

- George Boole, 19th Century mathematician

- Developed an *algebra* involving logic

later known as "Boolean Algebra"

- Primitive functions: AND, OR and NOT

- The power f Boolean Algebra is there's a one-to-one complete between circuits made up of AND, OR and NOT gates and equations.

CSC 322: Computer Organization Lab

13

### **Boolean algebra**

- Boolean algebra

- B = {0, 1}

- + is logical OR, is logical AND

- ' is logical NOT

- All algebraic axioms hold

### An Algebraic Structure

- An algebraic structure consists of

- a set of elements B

- binary operations { + , }

- and a unary operation { ' }

- such that the following axioms hold:

- 1. the set B contains at least two elements, a, b, such that a ° b

- 2. closure: a + b is in B  $a \bullet b$  is in B

- 3. commutativity: a + b = b + a  $a \bullet b = b \bullet a$

- 4. associativity:  $a + (b + c) = (a + b) + ca \bullet (b \bullet c) = (a \bullet b) \bullet c$

- 5. identity: a + 0 = a  $a \bullet 1 = a$

- 6. distributivity:  $a + (b \bullet c) = (a + b) \bullet (a + c)$   $a \bullet (b + c) = (a \bullet b) + (a \bullet c)$

- 7. complementarity: a + a' = 1  $a \bullet a' = 0$

Spring 2018

CSC 322: Computer Organization Lab

15

### **Axioms and Theorems of Boolean Algebra**

Identity

X + 0 = X

X • 1 = X

Null

X + 1 = 1

X • 0 = 0

Idempotency:

X + X = X

X • X = X

Involution:

(X')' = X

Complementarity:

X + Y = 1

X • Y = Y

Commutativity:

X + Y = Y + X 6D.

Y + Y = Y + X 6D.

Y + Y = Y + X + (Y + Z)

### Axioms and Theorems of Boolean Algebra (cont'd)

| 1 | Distributivity:<br>8. $X \bullet (Y + Z) = (X \bullet Y) + (X \bullet Z)$                            | 8D. $X + (Y \bullet Z) = (X + Y) \bullet (X + Z)$                          |

|---|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| • | uniting:<br>9. $X \bullet Y + X \bullet Y' = X$                                                      | 9D. $(X + Y) \bullet (X + Y') = X$                                         |

| • | absorption:<br>10. X + X • Y = X<br>11. (X + Y') • Y = X • Y                                         | 10D. $X \bullet (X + Y) = X$<br>11D. $(X \bullet Y') + Y = X + Y$          |

| • | factoring:<br>12. $(X + Y) \bullet (X' + Z) = X \bullet Z + X' \bullet Y$                            | 16D. $X \bullet Y + X' \bullet Z = (X + Z) \bullet (X' + Y)$               |

| 1 | consensus:<br>13. $(X \bullet Y) + (Y \bullet Z) + (X' \bullet Z) =$<br>$X \bullet Y + X' \bullet Z$ | 17D. $(X + Y) \bullet (Y + Z) \bullet (X' + Z) = (X + Y) \bullet (X' + Z)$ |

Spring 2018

CSC 322: Computer Organization Lab

17

### Axioms and Theorems of Boolean Algebra (cont'd)

- de Morgan's:

14. (X + Y + ...)' = X' Y' ... 12D. (X Y ...)' = X' + Y' + ...

- generalized de Morgan's:

15. f'(X1,X2,...,Xn,0,1,+,•) = f(X1',X2',...,Xn',1,0,•,+)

- Establishes relationship between and +

## Axioms and theorems of Boolean algebra (cont')

- Duality

- a dual of a Boolean expression is derived by replacing

- by +, + by •, 0 by 1, and 1 by 0, and leaving variables unchanged

- any theorem that can be proven is thus also proven for its dual!

- a meta-theorem (a theorem about theorems)

- duality:

16.  $X + Y + ... \Leftrightarrow X \bullet Y \bullet ...$

- generalized duality: 17. f (X1,X2,...,Xn,0,1,+,●) ⇔ f(X1,X2,...,Xn,1,0,●,+)

- Different than deMorgan's Law

- this is a statement about theorems

- this is not a way to manipulate (re-write) expressions

Spring 2018

CSC 322: Computer Organization Lab

19 LAU

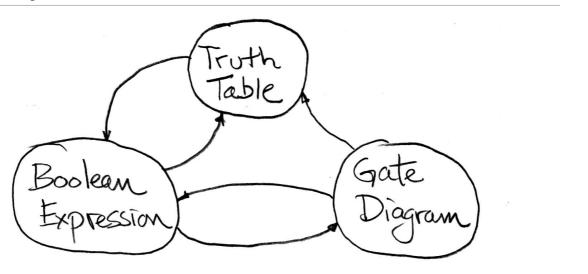

# Logic functions and Boolean algebra

Any logic function that can be expressed as a truth table can be written as an expression in Boolean algebra using the operators: ', +, and •

|      | Х     | Y     | X      | • Y   |                  | Х       | Y     | X'      | X' • Y                                                                                  |

|------|-------|-------|--------|-------|------------------|---------|-------|---------|-----------------------------------------------------------------------------------------|

|      | 0     | 0     | 0      |       |                  | 0       | 0     | 1       | 0                                                                                       |

|      | 0     | 1     | 0      |       |                  | 0       | 1     | 1       | 1                                                                                       |

|      | 1     | 0     | 0      |       |                  | 1       | 0     | 0       | 0                                                                                       |

|      | 1     | 1     | 1      |       |                  | 1       | 1     | 0       | 0                                                                                       |

|      |       |       | Ĩ      |       |                  |         |       |         | 1                                                                                       |

|      | Х     | Y     | X'     | Y'    | X • Y            | X' ● Y' | ( X ) | • Y ) + | - ( X' • Y' )                                                                           |

|      | 0     | 0     | 1      | 1     | 0                | 1       | 1     |         |                                                                                         |

|      | 0     | 1     | 1      | 0     | 0<br>0<br>0<br>1 | 0       | 0     |         |                                                                                         |

|      | 1     | 0     | 0      | 1     | 0                | 0       | 0     |         | $(X \bullet Y) + (X' \bullet Y') \equiv X = Y$                                          |

|      | 1     | 1     | 0      | 0     | 1                | 0       | 1     |         | $\sim$                                                                                  |

| Х, ` | Y are | Boole | an alg | jebra | variables        |         |       |         | expression that is true when the variables X<br>ave the same value and false, otherwise |

20 **المالية المركبة**

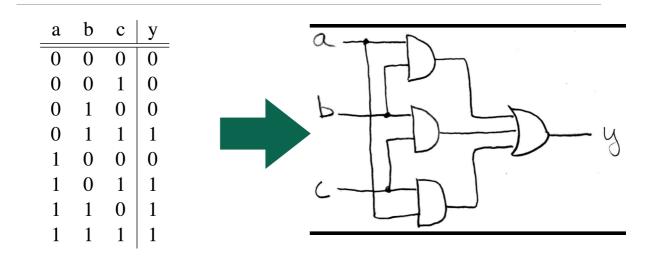

### Logic functions and Boolean algebra

- Thus, in order to implement an arbitrary logic function, the following procedure can be followed:

- Derive the truth table

- Create the product term that has a value of 1 for each valuation for which the output function f has to be 1

- Take the logical sum of these product terms to realize f

CSC 322: Computer Organization Lab

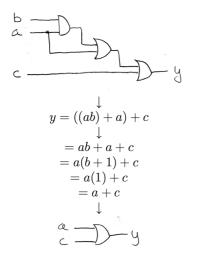

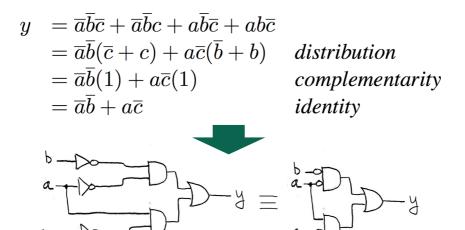

# **Example 5: Algebraic Simplification**

original circuit

equation derived from original circuit

algebraic simplification

*Boolean Algebra* also great for circuit <u>verification</u>Circ X = Circ Y? use *Boolean Algebra* to prove!

simplified circuit

CSC 322: Computer Organization Lab

# Example 6: Boolean Algebraic Simplification

$$y = ab + a + c$$

=  $a(b+1) + c$  distribution, identity

=  $a(1) + c$  law of 1's

=  $a + c$  identity

Spring 2018

CSC 322: Computer Organization Lab

23 Charles Contraction

### Canonical forms (1/2)

Spring 2018

24 Lebanse American University

# Canonical forms (2/2)

Spring 2018

Sprir

CSC 322: Computer Organization Lab

LAU

AU

25

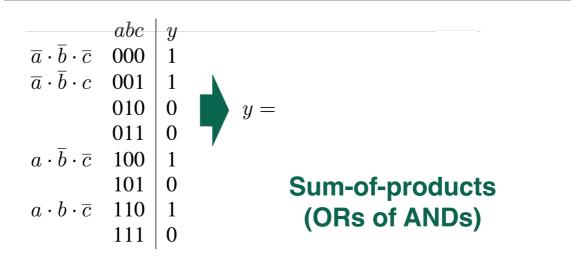

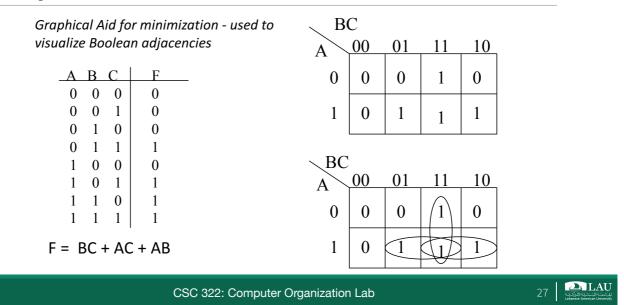

**Boolean Minimization**

- Reduce a Boolean equation to fewer terms hopefully, this will result in using less gates to implement the Boolean equation.

- Pencil-Paper: Algebraic techniques, K-maps or

| <ul> <li>Automated:</li> <li>A B C</li> </ul> | Many powerful algorithms exist                                        |

|-----------------------------------------------|-----------------------------------------------------------------------|

|                                               | F = A'BC + AB'C + ABC' + ABC                                          |

| 0 0 1                                         |                                                                       |

| 0 1 0                                         | 0                                                                     |

| 0 1 1                                         | 1 / /                                                                 |

| 1 0 0                                         | 0                                                                     |

| 1 0 1                                         |                                                                       |

| 1 1 0                                         | 1 $F = BC + AC + AB$                                                  |

| 1 1 1                                         | <sup>1</sup> Find Boolean adjacencies to minimize equation; eliminate |

|                                               | redundant term                                                        |

| ng 2018                                       | CSC 322: Computer Organization Lab 26                                 |

# K- maps

Spring 2018

# **CSC 322: Computer Organization Lab**

Part II: Combinatial Blocks

Dr. Haidar M. Harmanani

### Recap

Spring 2018

CSC 322: Computer Organization Lab

29

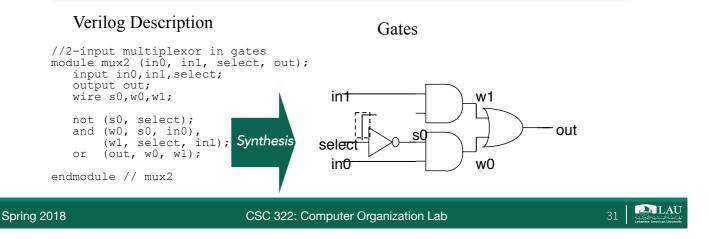

### **Technology Mapping**

Technology mapping maps a Boolean equation onto a given technology. The technology can affect what constraints are used when doing minimization for the function.

### **Logic Synthesis**

Logic Synthesis is the transformation a digital system described, at the logic level, in a Hardware Description Language (HDL) onto an implementation technology.

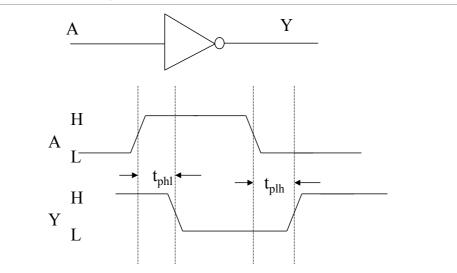

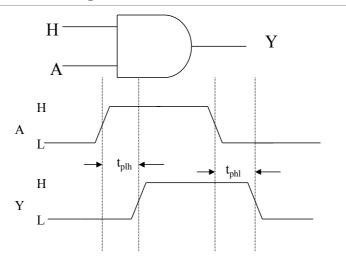

### **Propagation Delay**

# **Propagation Delay**

Spring 2018

CSC 322: Computer Organization Lab

33 LAU

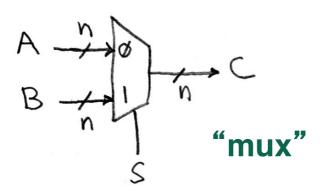

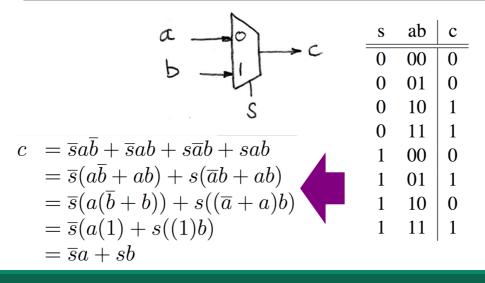

# 2-1 n-bit Data Multiplexor

### How many rows in TT of a 1-bit Mux?

Spring 2018

CSC 322: Computer Organization Lab

### How many rows in TT of a 1-bit Mux?

Spring 2018

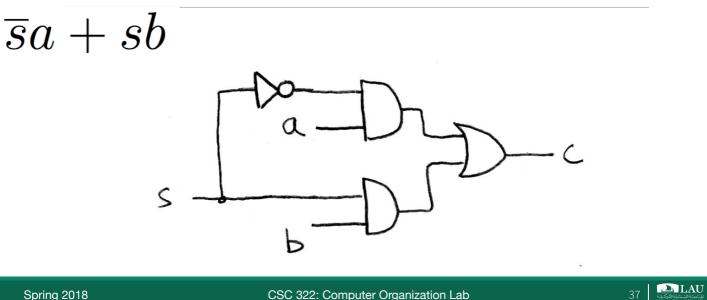

### How do we build a 1-bit-wide mux?

Spring 2018

CSC 322: Computer Organization Lab

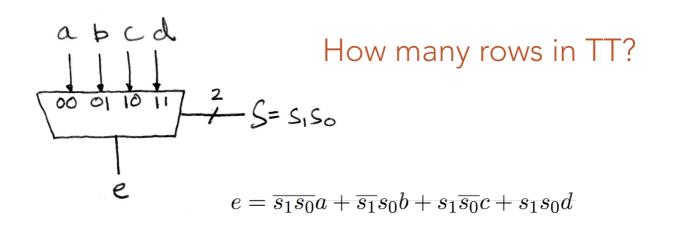

4-to-1 Multiplexor?

LAU Essection 38

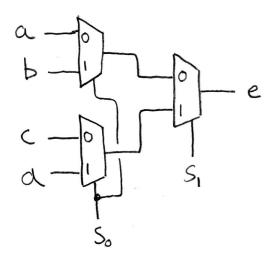

### Is there any other way to do it?

# Ans: Hierarchically!

Spring 2018

CSC 322: Computer Organization Lab

39 January Hand

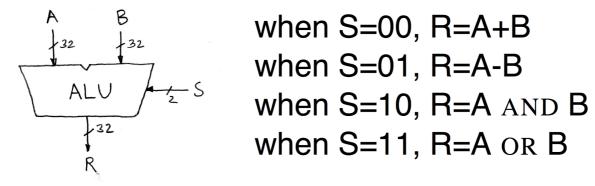

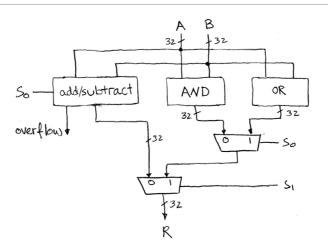

# **Arithmetic and Logic Unit**

- Most processors contain a special logic block called "Arithmetic and Logic Unit" (ALU)

- We'll show you an easy one that does ADD, SUB, bitwise AND, bitwise OR

# A Simple ALU

Spring 2018

CSC 322: Computer Organization Lab

41

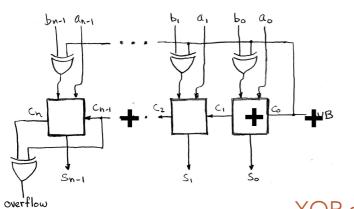

# Adder/Subtracter Design -- how?

- Truth-table, then determine canonical form, then minimize and implement as we've seen before

- Look at breaking the problem down into smaller pieces that we can cascade or hierarchically layer

|   |            |            |                |       | $\mathbf{a}_0$ | $b_0$            | <b>s</b> <sub>0</sub> | $\mathbf{c}_1$ |  |

|---|------------|------------|----------------|-------|----------------|------------------|-----------------------|----------------|--|

|   | $a_3$      | $a_2$      | $a_1$          | $a_0$ | 0              | 0                | 0                     | 0              |  |

| + | $b_3$      | $b_2$      | $b_1$          | $b_0$ | 0              | 0<br>1<br>0<br>1 | 1                     | 0              |  |

|   | <b>S</b> 3 | <b>S</b> 2 | $\mathbf{s}_1$ | Sn    | 1              | 0                | 1                     | 0              |  |

|   | U          |            | T              | 0     | 1              | 1                | 0                     | 1              |  |

$s_0 = a_0 ext{ XOR } b_0$  $c_1 = a_0 ext{ AND } b_0$

Spring 2018

CSC 322: Computer Organization Lab

43 **25.14U**

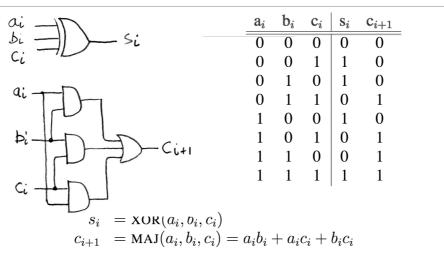

# Adder/Subtracter – One-bit adder (1/2)...

|   |            |       |                       |                |   | $\mathbf{a}_i$ | $\mathbf{b}_i$ | $\mathbf{c}_i$ | $\mathbf{s}_i$ | $c_{i+1}$ |

|---|------------|-------|-----------------------|----------------|---|----------------|----------------|----------------|----------------|-----------|

|   |            |       |                       |                |   | 0              | 0              | 0              | 0              | 0         |

|   |            |       | -                     |                |   | 0              | 0              | 1              | 1              | 0         |

|   | $a_3$      | $a_2$ | $a_1$                 | $\mathbf{a}_0$ |   | 0              | 1              | 0              | 1              | 0         |

| + | $b_3$      | $b_2$ | $b_1$                 | $b_0$          |   | 0              | 1              | 1              | 0              | 1         |

|   | <b>S</b> 3 | $s_2$ | <b>s</b> <sub>1</sub> | <b>S</b> 0     | - | 1              |                | 0              |                |           |

|   | 0          | 2     | -                     |                |   | 1              | 0              | 1              | 0              | 1         |

|   |            |       |                       |                |   | 1              | 1              | 0              | 0              | 1         |

|   |            |       |                       |                |   | 1              | 1              | 1              | 1              | 1         |

### Adder/Subtracter – One-bit adder (2/2)...

Spring 2018

CSC 322: Computer Organization Lab

45 Example

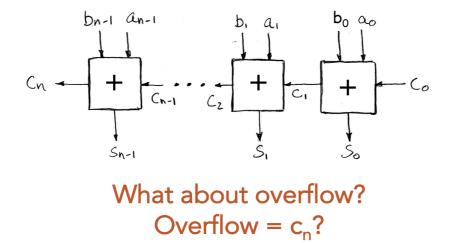

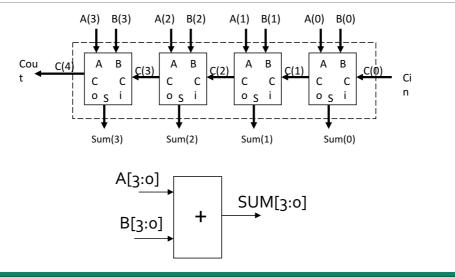

# N 1-bit adders $\Rightarrow$ 1 N-bit adder

Spring 2018

CSC 322: Computer Organization Lab

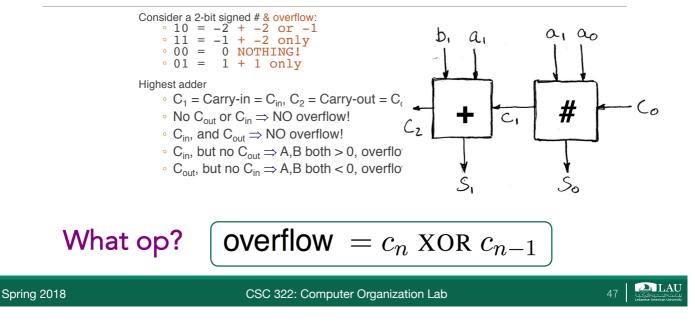

### What about overflow?

# 4 Bit Ripple Carry Adder

CSC 322: Computer Organization Lab

# **Extremely Clever Subtractor**

| х | у | XOR(x,y) |

|---|---|----------|

| 0 | 0 | 0        |

| 0 | 1 | 1        |

| 1 | 0 | 1        |

| 1 | 1 | 0        |

XOR serves as conditional inverter!

Spring 2018

CSC 322: Computer Organization Lab

49

# "And In conclusion..."

- Use muxes to select among input

- S input bits selects 2S inputs

- Each input can be n-bits wide, indep of S

- Can implement muxes hierarchically

- ALU can be implemented using a mux

Coupled with basic block elements

- N-bit adder-subtractor done using N 1-bit adders with XOR gates on input

- XOR serves as conditional inverter

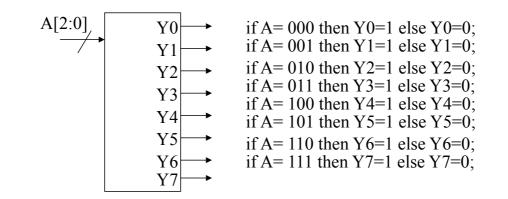

### Decoder

#### Spring 2018

CSC 322: Computer Organization Lab

51 LAU

### Making a Design Run Fast

- Speed is much more important than saving gates.

Speed of a gate directly affects the maximum clock speed of digital system

- Gate speed is TECHNOLOGY dependent

-0.35u CMOS process has faster gates than 0.8u CMOS process

- Implementation choice will affect Design speed

A Custom integrated circuit will be faster than an FPGA implementation.

- Design approaches will affect clock speed of system

Smart designers can make a big difference

Spring 2018

52 LAU

# CSC 322: Computer Organization Lab

Part III: Sequential Logic

Dr. Haidar M. Harmanani

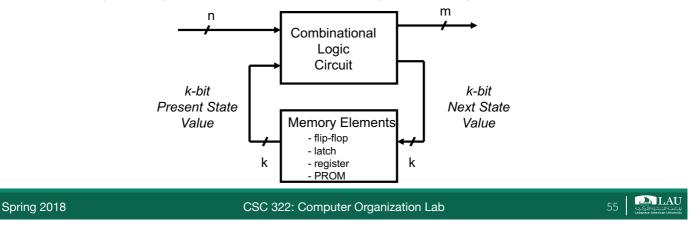

# **Sequential Systems Design**

- Combinational Network

- Output value only depends on input value

- Sequential Network

- Output Value depends on input value and present state value

- Sequential network must have some way of retaining state via memory devices.

- Use a clock signal in a synchronous sequential system to control changes between states

# Sequential System Diagram

- m outputs only depend on k PS bits Moore Machine

- **REMEMBER:** Moore is Less !!

- m outputs depend on k PS bits AND n inputs Mealy Machine

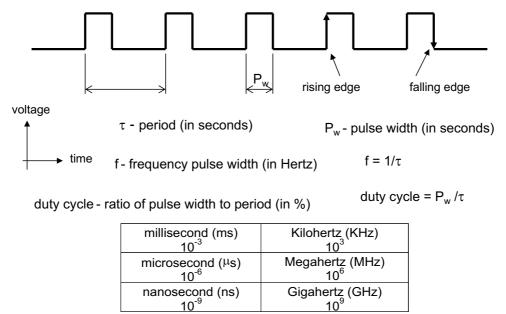

### **Clock Signal Review**

CSC 322: Computer Organization Lab

<u>10<sup>-9</sup></u>

2 LAU

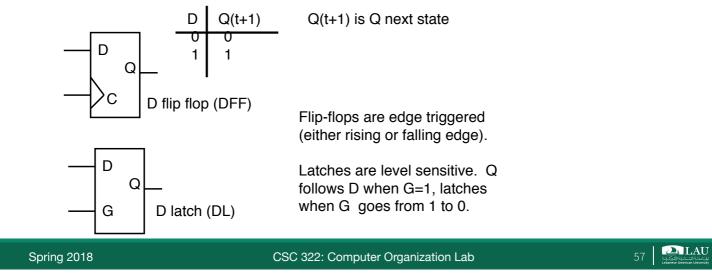

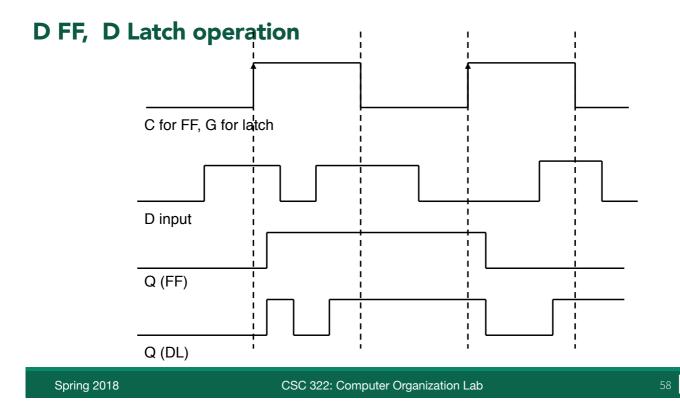

# **Memory Elements**

Memory elements used in sequential systems are flip-flops and latches.

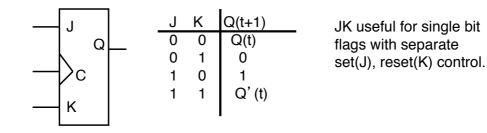

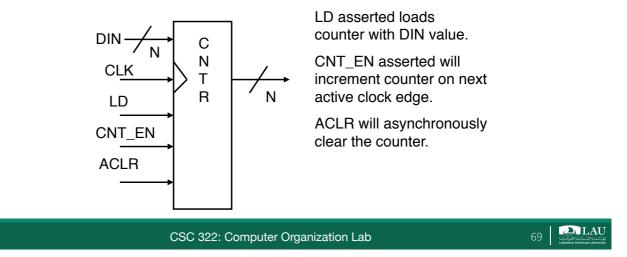

### **Other State Elements**

Useful for counter design.

Spring 2018

CSC 322: Computer Organization Lab

59

### DFFs are most common

- Most FPGA families only have DFFs

- DFF is fastest, simplest (fewest transistors) of FFs

- Other FF types (T, JK) can be built from DFFs

- We will use DFFs almost exclusively in this class

- Will always used edge-triggered state elements (FFs), not level sensitive elements (latches).

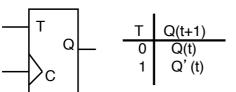

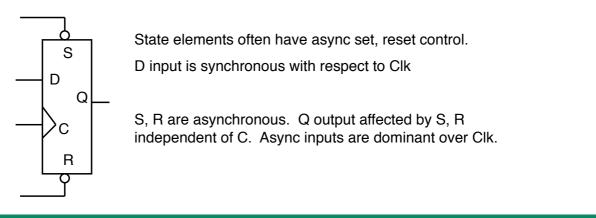

# Synchronous vs Asynchronous Inputs

Synchronous input: Output will change after active clock edge Asychronous input: Output changes independent of clock

Spring 2018

CSC 322: Computer Organization Lab

61 Called LAU

## **FF** Timing

- Propagation Delay

- C2Q: Q will change some propagation delay after change in C. Value of Q is based on D input for DFF.

- S2Q, R2Q: Q will change some propagation delay after change on S input, R input

- Note that there is NO propagation delay D2Q for DFF!

- D is a Synchronous INPUT, no prop delay value for synchronous inputs

CSC 322: Computer Organization Lab

63 Constant University

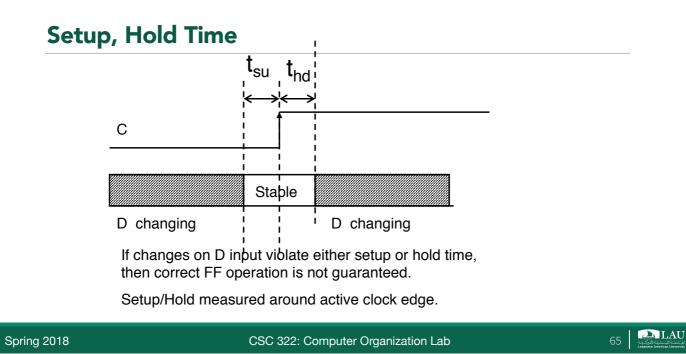

## Setup, Hold Times

- Synchronous inputs (e.g. D) have Setup, Hold time specification with respect to the CLOCK input

- Setup Time: the amount of time the synchronous input (D) must be stable before the active edge of clock

- Hold Time: the amount of time the synchronous input (D) must be stable after the active edge of clock.

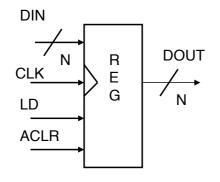

### Registers

The most common sequential building block is the register. A register is N bits wide, and has a load line for loading in a new value into the register.

Register contents do not change unless LD = 1 on active edge of clock.

A DFF is NOT a register! DFF contents change every clock edge.

ACLR used to asynchronously clear the register

66 66 **LAU**

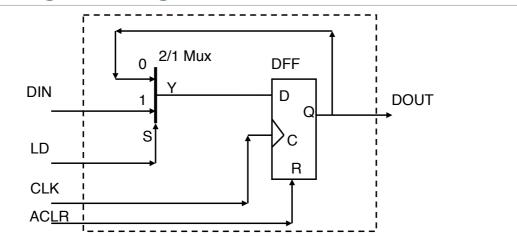

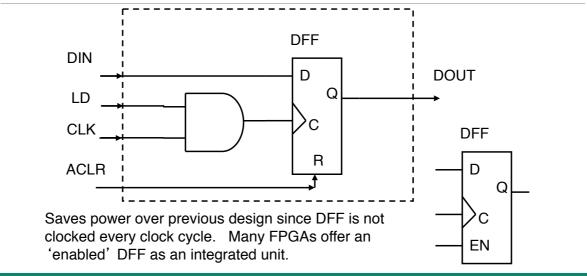

## 1 Bit Register using DFF, Mux

Note that DFF simply loads old value when LD = 0. DFF is loaded every clock cycle.

Spring 2018

CSC 322: Computer Organization Lab

67 LAU

### Counter

Very useful sequential building block. Used to generate memory addresses, or keep track of the number of times a datapath operation is performed.

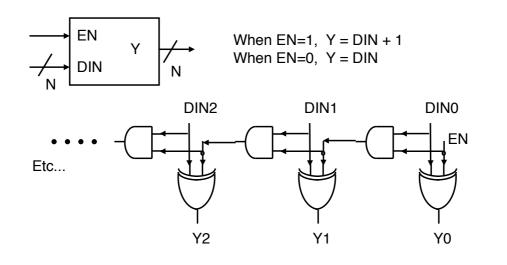

## **Incrementer: Combinational Building Block**

Spring 2018

CSC 322: Computer Organization Lab

# **Sequential System Description**

- The Q outputs of the flip-flops form a state vector

- A particular set of outputs is the Present State (PS)

- The state vector that occurs at the next discrete time (clock edge for synchronous designs) is the Next State (NS)

- A sequential circuit described in terms of state is a Finite State Machine (FSM)

- Not all sequential circuits are described this way; i.e., registers are not described as FSMs yet a register is a sequential circuit.

CSC 322: Computer Organization Lab

71

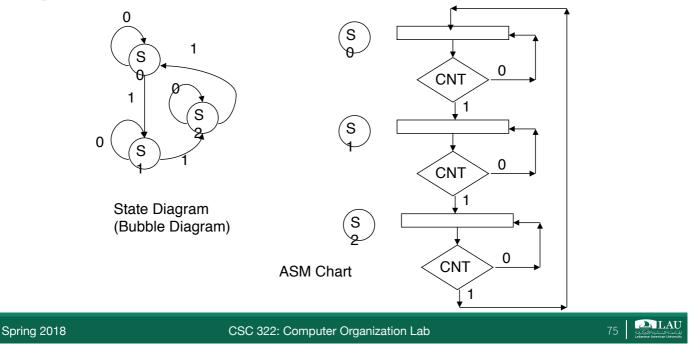

# **Describing FSMs**

- State Tables

- State Equations

- State Diagrams

- Algorithmic State Machine (ASM) Charts

Preferred method in this class

- Freiened method in this ci

- HDL descriptions

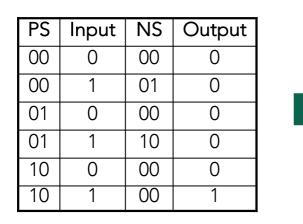

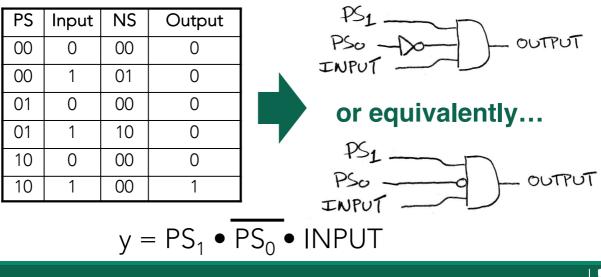

#### **Truth Table State Machine Example**

Spring 2018

CSC 322: Computer Organization Lab

73

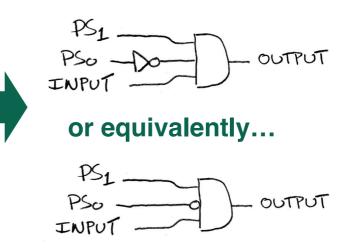

## Boolean Algebra (e.g., for FSM)

### **Example State Machine**

### **State Assignment**

- State assignment is the binary coding used to represent the states

- Given N states, need at least log<sub>2</sub>(N) FFs to encode the states

- (i.e. 3 states, need at least 2 FFs for state information).

S0 = 00, S1 = 01, S2 = 10 (FSM is now a modulo 3 counter)

- Do not always have to use the fewest possible number of FFs.

- A common encoding is One-Hot encoding use one FF per state.

-S0 = 001, S1 = 010, S2 = 100

State assignment affects speed, gate count of FSM

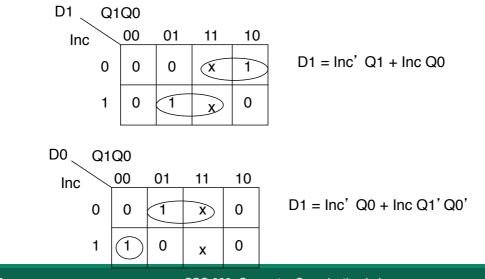

## **FSM Implementation**

• Use DFFs, State assignment: S0 = 00, S1 = 01, S2 = 10

|   | Inc | P<br>Q1 | S<br>Q0 | NS<br>Q1+ |   | D1 | D0 | State Table                   |

|---|-----|---------|---------|-----------|---|----|----|-------------------------------|

| _ | 0   | 0       | 0       | 0         | 0 | 0  | 0  |                               |

|   | 0   | 0       | 1       | 0         | 1 | 0  | 1  |                               |

|   | 0   | 1       | 0       | 1         | 0 | 1  | 0  | Equations                     |

|   | 0   | 1       | 1       | x         | Х | x  | х  | D1 = Inc' Q1Q0' + IncQ1' Q0   |

|   | 1   | 0       | 0       | 0         | 1 | 0  | 1  |                               |

|   | 1   | 0       | 1       | 1         | 0 | 1  | 0  |                               |

|   | 1   | 1       | 0       | 0         | 0 | 0  | 0  | D0 = lnc' Q1' Q0 + lncQ1' Q0' |

|   | 1   | 1       | 1       | x         | х | x  | х  |                               |

|   |     |         |         |           |   |    |    |                               |

|   |     |         |         |           |   |    |    |                               |

|   |     |         |         |           |   |    |    |                               |

Spring 2018

CSC 322: Computer Organization Lab

77 **الملا**

# Minimize Equations (if desired)

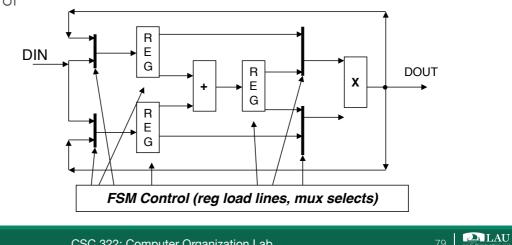

# **FSM Usage**

- Custom counters

- Datapath control

Spring 2018

CSC 322: Computer Organization Lab

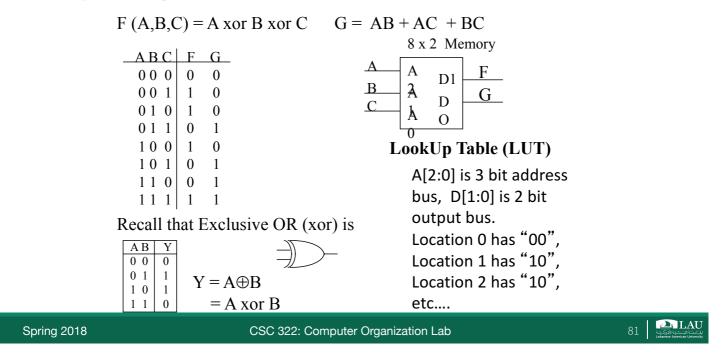

### **Memories**

- Memories are K x N devices, K is the # of locations, N is the number bits per location (16 x 2 would be 16 locations, each storing 2 bits)

- K locations require  $log_2(K)$  address lines for selecting a location (i.e. a 16 location memory needs 4 address lines)

- A memory that is K x N, can be used to implement N Boolean equations, which use log<sub>2</sub>(K) variables (the N Boolean equations must use the same variables).

- One address line is used for each *Boolean* variable, each bit of the output implements a different Boolean equation.

- The memory functions as a Look Up Table (LUT).

#### **Memory Example**

# A gated D latch in Verilog

module latch (D, clk, Q);

input D, clk;

output reg Q;

**always** @(D, clk) **if** (clk) Q <= D;

endmodule

## A D flip-flop.

module flipflop (D, Clock, Q);

input D, Clock;

output reg Q;

always @(posedge Clock) Q <= D;

endmodule

Spring 2018

CSC 322: Computer Organization Lab

83

### A D flip-flop with asynchronous reset

```

module flipflop_ar (D, Clock, Resetn, Q);

input D, Clock, Resetn;

output reg Q;

```

```

always @(posedge Clock, negedge Resetn)

if (Resetn == 0)

Q <= 0;

else

Q <= D;</pre>

```

endmodule

#### A D flip-flop with synchronous reset.

```

module flipflop_sr (D, Clock, Resetn, Q);

input D, Clock, Resetn;

output reg Q;

```

```

always @(posedge Clock)

if (Resetn == 0)

Q <= 0;

else

Q <= D;</pre>

```

endmodule

Spring 2018

CSC 322: Computer Organization Lab

85 LAU

## A four-bit register with asynchronous clear.

```

module reg4 (D, Clock, Resetn, Q);

input [3:0] D;

input Clock, Resetn;

output reg [3:0] Q;

always @(posedge Clock, negedge Resetn)

if (Resetn == 0)

Q <= 4'b0000;</pre>

```

else

Q <= D;

endmodule

Spring 2018

36 LAU

# An n-bit register with asynchronous clear and enable.

module regne (D, Clock, Resetn, E, Q);

parameter n = 4;

input [n-1:0] D;

input Clock, Resetn, E;

output reg [n-1:0] Q;

```

always @(posedge Clock, negedge Resetn)

if (Resetn == 0)

Q <= 0;

else if (E)

Q <= D;</pre>

```

endmodule

Spring 2018

CSC 322: Computer Organization Lab

87 EAU

## A three-bit shift register

module shift3 (w, Clock, Q);

input w, Clock;

output reg [1:3] Q;

```

always @(posedge Clock)

begin

Q[3] <= w;

Q[2] <= Q[3];

Q[1] <= Q[2];

end

```

endmodule

88 EAU

## Code for a four-bit counter

```

module count4 (Clock, Resetn, E, Q);

input Clock, Resetn, E;

output reg [3:0] Q;

```

```

always @(posedge Clock, negedge Resetn)

if (Resetn == 0)

Q <= 0;

else if (E)

Q <= Q + 1;</pre>

```

endmodule

Spring 2018

CSC 322: Computer Organization Lab

89

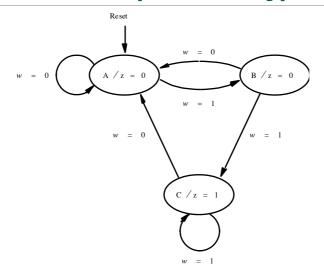

# State diagram of a simple Moore-type FSM

Spring 2018

CSC 322: Computer Organization Lab

90 Contraction University

```

module moore (Clock, w, Resetn, z);

input Clock, w, Resetn;

output z;

reg [1:0] y, Y;

parameter A = 2'b00, B = 2'b01, C = 2'b10;

Code for a Moore machine.

always @(w, y)

begin

case (y)

A: if (w = = 0) Y = A;

else Y = B;

B: if (w = = 0) Y = A;

else Y = C;

C: if (w = = 0) Y = A;

else Y = C;

default: Y = 2'bxx;

endcase

end

always @(posedge Clock, negedge Resetn)

begin

if (Resetn = = 0)

y <= A;

else

y <= Y;

end

assign z = (y = = C);

endmodule

```

```

Spring 2018

```

CSC 322: Computer Organization Lab

```

module moore (Clock, w, Resetn, z);

input Clock, w, Resetn;

output z;

reg [1:0] y;

parameter A = 2'b00, B = 2'b01, C = 2'b10;

always @(posedge Clock, negedge Resetn)

begin

if (Resetn = = 0)

y <= A;

else

case (y)

A: if (w = = 0) y <= A;

else y <= B;

B: if (w = = 0) y <= A;

else y <= C;

C: if (w = = 0) y <= A;

else y <= C;

default: y <= 2'bxx;</pre>

endcase

end

assign z = (y = = C);

endmodule

```

Alternative version of the code for a Moore machine.

```

Spring 2018

```

| <pre>module mealy (Clock,<br/>input Clock, w, Reset<br/>output reg z ;<br/>reg y, Y;<br/>parameter A = 1' b0,</pre>           | ;<br>Code for a Mealy machine         |

|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| always @(w, y)<br>case (y)<br>A: if (w = = 0)<br>begin<br>Y = A;<br>z = 0;<br>end<br>else<br>begin<br>Y = B;<br>z = 0;<br>end |                                       |

| B: if $(w == 0)$<br>begin<br>Y = A;<br>z = 0;<br>end<br>else<br>begin<br>Y = B;<br>z = 1;<br>end<br>endcase                   |                                       |

| if (Resetn = = 0)<br>y <= A;<br>else                                                                                          | ock , <b>negedge</b> Resetn)          |

| y <= Y;<br>Spring 2018 endmodule                                                                                              | CSC 322: Computer Organization Lab 93 |

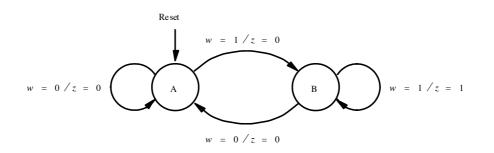

# State diagram of a Mealy-type FSM.

|             | module mealy (Clock, w, Res<br>input Clock, w, Resetn ;<br>output reg z ;<br>reg y, Y;<br>parameter A = 1' b0, B = 1'                                                                                                                                                                                                                 | (                      | Code for a Mealy mach | nine. |          |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|-------|----------|

|             | always @(w, y)<br>case (y)<br>A: if (w = = 0)<br>begin<br>Y = A;<br>z = 0;<br>end<br>else<br>begin<br>Y = B;<br>z = 0;<br>end<br>B: if (w == 0)<br>begin<br>Y = A;<br>z = 0;<br>end<br>B: if w == 0)<br>begin<br>Y = A;<br>z = 0;<br>end<br>B: if w == 0;<br>end<br>B: if w == 0;<br>end<br>A: we |                        |                       |       |          |

|             | end<br>endcase<br>always @(posedge Clock , i<br>if (Resetn = = 0)<br>y <= A;<br>else                                                                                                                                                                                                                                                  | <b>negedge</b> Resetn) |                       |       |          |

| Spring 2018 | y <= Y;<br>endmodule                                                                                                                                                                                                                                                                                                                  | CSC 322: Computer      | Organization Lab      |       | 95 BELAU |

| Verilog       |

|---------------|

| operators and |

| bit lengths.  |

| Category    | Examples                                                             | Bit Length                                          |

|-------------|----------------------------------------------------------------------|-----------------------------------------------------|

| Bitwise     | ~A, +A, -A<br>A & B, A   B, A ~ ^ B, A ^ ~ B                         | L( <i>A</i> )<br>MAX (L( <i>A</i> ), L( <i>B</i> )) |

| Logical     | !A, A && B, A II B                                                   | 1 bit                                               |

| Reduction   | &A, ~&A, IA, ~IA, ^~A, ~^A                                           | 1 bit                                               |

| Relational  | A = = B, A != B, A > B, A < B<br>A >= B, A <= B<br>A = = B, A != = B | 1 bit                                               |

| Arithmetic  | A + B, A – B, A * B, A/B<br>A % B                                    | MAX (L( <i>A</i> ), L( <i>B</i> ))                  |

| Shift       | A << B, A >> B                                                       | L(A)                                                |

| Concatenate | {A,,B}                                                               | $L(A) + \cdots + L(B)$                              |

| Replication | {B{A}}                                                               | B *L( <i>A</i> )                                    |

| Condition   | A ? B : C                                                            | MAX (L( <i>B</i> ), L( <i>C</i> ))                  |

CSC 322: Computer Organization Lab

96 LAU

# **Verilog Gates**

| Name   | Description                         | Usage                                            |

|--------|-------------------------------------|--------------------------------------------------|

| and    | $f = (a \cdot b \cdots)$            | and(f, a, b,)                                    |

| nand   | $f = \overline{(a \cdot b \cdots)}$ | <b>nand</b> ( <i>f</i> , <i>a</i> , <i>b</i> ,   |

| or     | $f=(a+b+\cdots)$                    | <b>or</b> ( <i>f</i> , <i>a</i> , <i>b</i> ,)    |

| nor    | $f=\overline{(a+b+\cdots)}$         | <b>nor</b> ( <i>f</i> , <i>a</i> , <i>b</i> , …) |

| xor    | $f=(a\oplus b\oplus \cdots)$        | <b>xor</b> ( <i>f</i> , <i>a</i> , <i>b</i> ,)   |

| xnor   | $f=(a\odot b\odot \cdots)$          | <b>xnor</b> ( <i>f</i> , <i>a</i> , <i>b</i> ,   |

| not    | $f = \overline{a}$                  | <b>not</b> ( <i>f</i> , <i>a</i> )               |

| buf    | f = a                               | <b>buf</b> ( <i>f</i> , <i>a</i> )               |

| notif0 | $f = (!e ? \overline{a} : `bz)$     | notif0(f, a, e)                                  |

| notif1 | $f = (e ? \overline{a} : `bz)$      | notif1( <i>f, a, e</i> )                         |

| bufif0 | f = (!e ? a : `bz)                  | bufif0( <i>f, a, e</i> )                         |

| bufif1 | f = (e ? a : `bz)                   | bufif1( <i>f, a, e</i> )                         |

|        |                                     |                                                  |

Spring 2018

CSC 322: Computer Organization Lab

\_