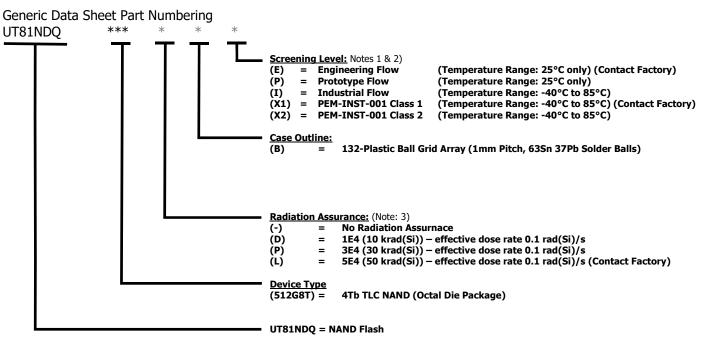

## UT81NDQ512G8T

#### Features

- Open NAND Flash Interface (ONFI) 4.0-compliant<sup>1</sup>

- JEDEC NAND Flash Interoperability (JESD230C) compliant<sup>2</sup>

- Triple-level cell (TLC)

- B17A Industrial die source

- Organization

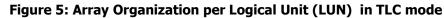

- Page size x8: 18,592 bytes (16,384 + 2208 bytes)

- Block size: 2304 pages, (36,864K + 4968K bytes)

- Plane size: 4 planes x 504 blocks

- Device size: 16128 blocks

- NV-DDR3 I/O performance<sup>3</sup>

- Up to NV-DDR3 timing mode 9

- Clock rate: 3ns (NV-DDR3)

- Read/write throughput per pin: 667 MT/s

- Tested over temperature in mode 9

- NV-DDR2 I/O performance<sup>4</sup>

- Up to NV-DDR2 timing mode 8

- Clock rate: 3.75ns (NV-DDR2)

- Read/write throughput per pin: 533 MT/s

- Tested over temperature in mode 6

- Asynchronous I/O performance<sup>4</sup>

- Up to asynchronous timing mode 5

- tRC/tWC: 20ns (MIN)

- Read/write throughput per pin: 50 MT/s

- Tested over temperature in mode 5

- TLC Array performance

- SNAP READ operation time without VPP: 51µs(TYP)

- Single-Plane READ PAGE operation time without/with VPP : 74/73µs (TYP)

- Multi-Plane READ PAGE operation time without VPP: 88µs(TYP)

- Effective Program page time without VPP : 1900µs(TYP)

- Erase block time: 15ms (TYP)

- Operating Voltage Range

- VCC: 2.7-3.6V

- VCCQ: 1.14-1.26V, 1.7-1.95V

- Command set: ONFI NAND Flash Protocol

- Data is required to be randomized by the external host prior to being inputted to the NAND device, see External Data Randomization in the User Manual

- First block (block address 00h) is valid when shipped from factory. For minimum required ECC, see Error Management in the User Manual<sup>5</sup>

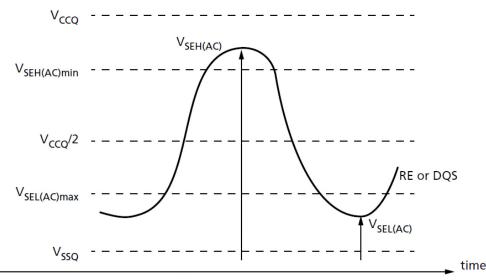

- RESET (FFh) required as first command after power-on

- Operation status byte provides software method for detecting

- Operation completion

## UT81NDQ512G8T

- Pass/fail condition

- Write-protect status

- Data strobe (DQS) signals provide a hardware method for synchronizing data DQ in the NV-DDR2/NVDDR3 interface

- Copyback operations supported within the plane from which data is read

- On-die Termination (ODT)<sup>6</sup>

- Quality and reliability<sup>7</sup>

- Testing methodology: JESD47

- Data retention: JESD47 compliant

- TLC Endurance: 3,000 PROGRAM/ERASE cycles

- SLC Endurance: 40,000 PROGRAM/ERASE cycles

- Package

- 132-ball BGA

- ΘJC : 2.68 °C/W

- 2000V HBM ESD

- 0.534 grams

#### Notes:

- 1) The ONFI 4.0 specification is available at <u>www.onfi.org</u>

- 2) The JEDEC specification is available at <u>www.jedec.org/standards-documents</u>

- 3) NV-DDR3 functionality is only available with 1.2V VCCQ

- 4) NV-DDR2 and Asynchronous functionality is only available with 1.8V VCCQ

- 5) ODT functionality is supported only in NVDDR2 and NV-DDR3 mode

- 6) READ RETRY and AUTO READ CALIBRATION operations are required to achieve specified endurance and for general array data integrity

- 7) For minimum required ECC, see External Data Randomization in the User Manual

- 8) Radiation testing is performed without VPP. VPP operations should not be used in a radiation environment. Devices using  $V_{PP}$  operations in a radiation environment will not be warrantied

#### **Operational Environment**

- Temperature Range: -40°C to +85°C

- Total Dose: 30 to 50 krad(Si)

- SEL Immune: ≤ 60 MeV-cm<sup>2</sup>/mg

#### Notes:

- 1. Radiation testing is performed without VPP. VPP operations should not be used in a radiation environment. Devices using  $V_{PP}$  operations in a radiation environment will not be warrantied

- 2. Contact supplier for bit error performance and availability of material at a specific SLC and TLC TID levels

#### 1 General Description

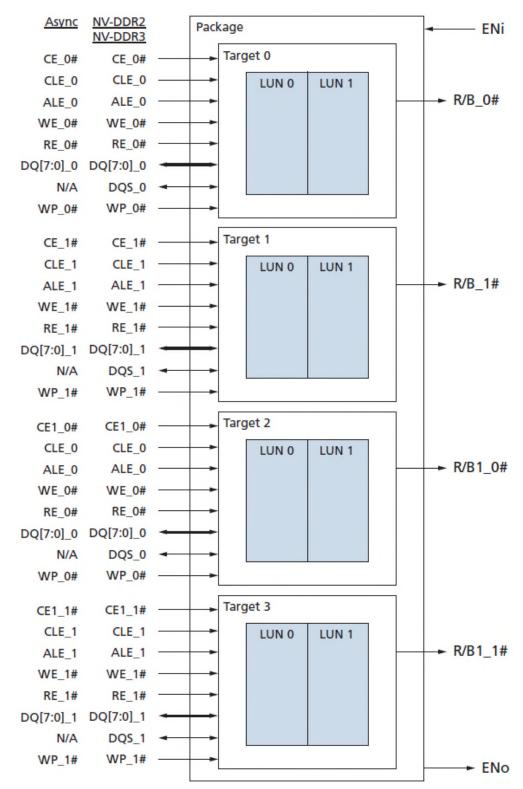

NAND Flash devices include an asynchronous data interface for I/O operations. These devices use a highly multiplexed 8-bit bus (DQx) to transfer commands, address, and data. There are five control signals used to implement the asynchronous data interface: CE#, CLE, ALE, WE#, and RE#. Additional signals control hardware write protection (WP#) and monitor device status (R/B#).

This NAND Flash device additionally includes a NV-DDR2, and/or a NV-DDR3 data interface for high-performance I/O operations. Data transfers include a bidirectional data strobe (DQS).

This hardware interface creates a low pin-count device with a standard pinout that remains the same from one density to another, enabling future upgrades to higher densities with no board redesign.

# 4Tb TLC NAND Flash UT81NDQ512G8T

A target is the unit of memory accessed by a chip enable signal. A target contains one or more NAND Flash die. A NAND Flash die is the minimum unit that can independently execute commands and report status. A NAND Flash die, in the ONFI specification, is referred to as a logical unit (LUN). For further details, see Device and Array Organization.

#### 2 Asynchronous, NV-DDR2, NV-DDR3 Signal Descriptions

#### Table 1: Asynchronous, NV-DDR2, and NV-DDR3 Signal Definitions

| Asynchronous<br>Signal <sup>1</sup> | NV-DDR2/NV-<br>DDR3 Signal <sup>1</sup> | Туре   | Description <sup>2</sup>                                                                                                                                                                                                                           |

|-------------------------------------|-----------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALE                                 | ALE                                     | Input  | <b>Address latch enable</b> : Loads an address from DQx into the address register.                                                                                                                                                                 |

| CE#                                 | CE#                                     | Input  | <b>Chip enable</b> : Enables or disables one or more die (LUNs) in a target.                                                                                                                                                                       |

| CLE                                 | CLE                                     | Input  | <b>Command latch enable</b> : Loads a command from DQx into the command register.                                                                                                                                                                  |

| DQx                                 | DQx                                     | I/O    | <b>Data inputs/outputs</b> : The bidirectional I/Os transfer address, data, and command information.                                                                                                                                               |

| -                                   | DQS, DQS_t                              | I/O    | <b>Data strobe</b> : Provides a synchronous reference for data input and output.                                                                                                                                                                   |

| -                                   | DQS_c                                   | I/O    | <b>Data strobe complement</b> : Provides a complementary signal to the data strobe signal optionally used in the NV-DDR2 or NV-DDR3 interface for synchronous reference for data input and output                                                  |

| ENi                                 | ENi                                     | Input  | <b>Enumerate input</b> : Input to a NAND device (if first NAND device on the daisy chain have as NC) from ENo of a previous NAND device to support CE# pin reduction functionality.                                                                |

| ENo                                 | ENo                                     | Output | <b>Enumerate output</b> : Output from a NAND device to the ENi of the next NAND device in the daisy chain to support CE# pin reduction functionality.                                                                                              |

| RE#                                 | RE#, RE_t                               | Input  | <b>Read enable and write/read</b> : RE# transfers serial data from the NAND Flash to the host system when the asynchronous interface is active.                                                                                                    |

| -                                   | RE_c                                    | Input  | <b>Read enable complement:</b> Provides a complementary signal to the read enable signal optionally used in the NV-DDR2 or NV-DDR3 interface for synchronous reference for data output.                                                            |

| WE#                                 | WE#                                     | Input  | <b>Write enable and clock</b> : WE# transfers commands,<br>addresses when the asynchronous, NV-DDR2, and NV-DDR3<br>interfaces are active, and serial data from the host system<br>to the NAND Flash when the asynchronous interface is<br>active. |

| WP#                                 | WP#                                     | Input  | <b>Write protect</b> : Enables or disables array PROGRAM and ERASE operations.                                                                                                                                                                     |

| R/B#                                | R/B#                                    | Output | <b>Ready/busy</b> : An open-drain, active-low output that requires an external pull-up resistor. This signal indicates target array activity.                                                                                                      |

## UT81NDQ512G8T

| Asynchronous<br>Signal <sup>1</sup> | NV-DDR2/NV-<br>DDR3 Signal <sup>1</sup> | Туре   | Description <sup>2</sup>                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------|-----------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc                                 | Vcc                                     | Supply | Vcc: Core power supply                                                                                                                                                                                                                                                                                                                                            |

| Vccq                                | Vccq                                    | Supply | Vccq: I/O power supply                                                                                                                                                                                                                                                                                                                                            |

| Vpp                                 | Vpp                                     | Supply | <b>V</b> <sub>PP</sub> : The V <sub>PP</sub> signal is an optional external high voltage power supply to the device. This high voltage power supply may be used to enhance operations (e.g., improved power efficiency). If V <sub>PP</sub> will not be utilized by a host system, that V <sub>PP</sub> signal location is then defined as a DNU signal location. |

| V <sub>SS</sub>                     | V <sub>SS</sub>                         | Supply | Vss: Core ground connection                                                                                                                                                                                                                                                                                                                                       |

| Vssq                                | Vssq                                    | Supply | Vssq: I/O ground connection                                                                                                                                                                                                                                                                                                                                       |

| -                                   | V <sub>REFQ</sub>                       | Supply | $\mathbf{V}_{REFQ}$ : Reference voltage used with NV-DDR2 and NV-DDR3 interfaces                                                                                                                                                                                                                                                                                  |

| ZQ                                  | ZQ                                      | -      | <b>Reference pin for ZQ calibration</b> : This is used on ZQ calibration. The ZQ signal shall be connected to Vss through $R_{ZQ}$ resistor                                                                                                                                                                                                                       |

| NC                                  | NC                                      | -      | <b>No connect</b> : NCs are not internally connected. They can be driven or left unconnected                                                                                                                                                                                                                                                                      |

| DNU                                 | DNU                                     | -      | <b>Do not use</b> : DNUs must be left unconnected.                                                                                                                                                                                                                                                                                                                |

| RFU                                 | RFU                                     | -      | Reserved for future use: RFUs must be left unconnected                                                                                                                                                                                                                                                                                                            |

- 1) See Device and Array Organization and Signal Assignment sections for detailed signal connections.

- See User Manual: Bus Operation Asynchronous Interface, Bus Operations NV-DDR2 Interface, and Bus Operation NV-DDR3 Interface for detailed Asynchronous, NV-DDR2, and NV-DDR3 interface signal descriptions

## UT81NDQ512G8T

#### **3** Signal Assignments

| <br>1 | 2                                                                       | 3                                               | 4         | 5                                               | 6 | 7                     | 8         | 9                                                        | 10                                                       | 11                                                       |  |

|-------|-------------------------------------------------------------------------|-------------------------------------------------|-----------|-------------------------------------------------|---|-----------------------|-----------|----------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|--|

| NC    | ) (NC)                                                                  | (NC)                                            |           |                                                 |   |                       |           | ( NC )                                                   | (NC)                                                     | (NC)                                                     |  |

| NC    | ) (NC)                                                                  | (NC)                                            |           |                                                 |   |                       |           | (NC)                                                     | (NC)                                                     | (NC)                                                     |  |

| R     | ) ( <mark>R</mark> )                                                    | $\left( \begin{array}{c} R \end{array} \right)$ |           |                                                 |   |                       |           | (R)                                                      | $\left( \begin{array}{c} R \end{array} \right)$          |                                                          |  |

| R     | ) (V <sub>cca</sub> )                                                   | (Vcca)                                          | (pa3_12)  | $(v_{ss})$                                      |   |                       | (pq4_12)  | (Vcca)                                                   | (Voca)                                                   | $\left( \begin{array}{c} \mathbf{R} \end{array} \right)$ |  |

| R     | $(v_{sso})$                                                             | (DQ2_12)                                        | (vssq)    | 005_1_1.2<br>(DQS_11.2)                         |   | (RE_1#2)<br>VRE_1_12  | (Vssq)    | (DQ5_12)                                                 | (V_SSQ)                                                  | $\left( \begin{array}{c} R \end{array} \right)$          |  |

|       | (DQ0_12)                                                                | (DQ1_12)                                        | (pas_1_e) | RE_1_0                                          |   | (WE_1# <sup>2</sup> ) | (REFQ_1)  | (DQ8_12)                                                 | (DQ7_12)                                                 |                                                          |  |

|       | (Vssa)                                                                  | (Vcca)                                          | (ALE_12)  | (CLE_12)                                        |   | (NC)                  | (NC)      | (Vcca)                                                   | (Vssa)                                                   |                                                          |  |

|       |                                                                         |                                                 | (WP_1#2)  | $\left( \begin{array}{c} R \end{array} \right)$ |   | (E1_1#4)              | (CE0_1#2) | (ZQ_1)<br>(DNU)                                          | $\left( \begin{array}{c} R \end{array} \right)$          |                                                          |  |

|       | $(v_{ss})$                                                              | $\left( \mathbf{v}_{cc} \right)$                | (R/B0_0#) | (R/B1_0#                                        |   | (R/B1_1#              | (R/B0_1#) | (Vcc)                                                    | $(v_{ss})$                                               |                                                          |  |

|       | (R)                                                                     | ZQ_0A                                           | (CE0_0#)  | (CE1_0#)                                        |   | (V <sub>PP</sub> )    | (WP_0#)   | $\left( \begin{array}{c} \mathbf{R} \end{array} \right)$ | $\left( \begin{array}{c} \mathbf{R} \end{array} \right)$ |                                                          |  |

|       | (Vssa)                                                                  | (Vcca)                                          | (NC)      | (NC)                                            |   | (CLE_0)               | (ALE_0)   | (Vcca)                                                   | (Vssa)                                                   |                                                          |  |

|       | (DQ7_0)                                                                 | (DQ8_0)                                         | VREFQ_0   | (WE_0#)                                         |   | RE_0_03               | (as_0_d.) | (DQ1_0)                                                  | (DQ0_0)                                                  |                                                          |  |

| R     | $(v_{sso})$                                                             | (DQ5_0)                                         | (Vssa)    | (RE_0#)                                         |   | Das_01                | (Vssa)    | (DQ2_0)                                                  | (Vssa)                                                   | $\left( \begin{array}{c} \mathbf{R} \end{array} \right)$ |  |

| R     | ) (V <sub>cca</sub> )                                                   | (Vcca)                                          | (DQ4_0)   | $\left( v_{cc} \right)$                         |   | (V <sub>ss</sub> )    | (DQ3_0)   | (Vcca)                                                   | (Voca)                                                   | $\left( \begin{array}{c} \mathbf{R} \end{array} \right)$ |  |

| R     | $\left( \left( \begin{array}{c} \mathbf{R} \end{array} \right) \right)$ | (R)                                             |           |                                                 |   |                       |           | $\left( \begin{array}{c} \mathbf{R} \end{array} \right)$ | (R)                                                      | (R)                                                      |  |

|       | ) (NC)                                                                  | (NC)                                            |           |                                                 |   |                       |           | (NC)                                                     | (NC)                                                     | (NC)                                                     |  |

| NC    | ) (NC)                                                                  |                                                 |           |                                                 |   |                       |           | ( NC )                                                   | ( NC )                                                   | (NC)                                                     |  |

#### Figure 1: 132-Ball BGA (Ball-Down, Top View)

#### Notes:

- 1) N/A: This signal is tri-stated when the asynchronous interface is active.

- 2) These signals are available on dual, quad, and octal die stacked die packages. They are NC for other configurations.

- 3) These signals are available when differential signaling is enabled.

- 4) These signals are available on quad die four CE# or octal die packages. They are NC for other configurations

DATASHEET

## UT81NDQ512G8T

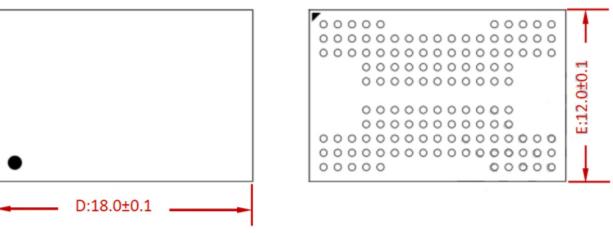

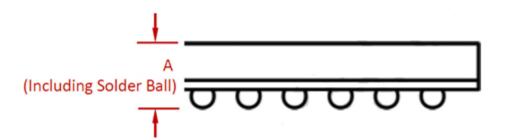

#### 4 Package Dimensions

| Symbol (Dimension)  | Min               | Norm  | Max   |  |  |  |

|---------------------|-------------------|-------|-------|--|--|--|

| A (Total Thickness) | 1.25              | 1.35  | 1.45  |  |  |  |

| D (Lenth)           | 17.90             | 18.00 | 18.10 |  |  |  |

| E (Width)           | 11.90 12.00 12.10 |       |       |  |  |  |

| Ball Pitch          | 1.0 mm Typical    |       |       |  |  |  |

| Ball Diameter       | 0.45 mm Typical   |       |       |  |  |  |

- 1) All Dimensions in mm

- 2) Solder ball material: Sn-Pb

- 3) Package Mass: 0.534 grams

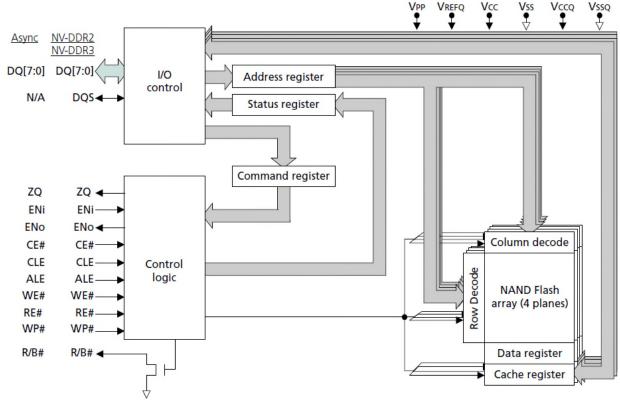

#### 5 Architecture

These devices use NAND Flash electrical and command interfaces. Data, commands, and addresses are multiplexed onto the same pins and received by I/O control circuits. The commands received at the I/O control circuits are latched by a command register and are transferred to control logic circuits for generating internal signals to control device operations. The addresses are latched by an address register and sent to a row decoder to select a row address, or to a column decoder to select a column address.

Data is transferred to or from the NAND Flash memory array, byte by byte, through a data register and a cache register.

The NAND Flash memory array is programmed and read using page-based operations and is erased using block-based operations. During normal page operations, the data and cache registers act as a single register. During cache operations, the data and cache registers operate independently to increase data throughput.

The status register reports the status of die (LUN) operations.

#### Notes:

1) N/A: This signal is tri-stated when the asynchronous interface is active.

### UT81NDQ512G8T

#### 6 Device and Array Organization

#### Figure 4: Device Organization for Eight-Die Package with Four CE# (132-ball BGA)

DATASHEET

## UT81NDQ512G8T

#### Table 2: Array Addressing for Logical Unit (LUN) in TLC mode

| Cycle  | DQ7                | DQ6               | DQ5               | DQ4               | DQ3               | DQ2  | DQ1  | DQ0              |

|--------|--------------------|-------------------|-------------------|-------------------|-------------------|------|------|------------------|

| First  | CA7                | CA6               | CA5               | CA4               | CA3               | CA2  | CA1  | CA0 <sup>2</sup> |

| Second | LOW                | CA14 <sup>3</sup> | CA13              | CA12              | CA11              | CA10 | CA9  | CA8              |

| Third  | PA7                | PA6               | PA5               | PA4               | PA3               | PA2  | PA1  | PA0              |

| Fourth | BA15               | BA14              | BA13 <sup>5</sup> | BA12 <sup>5</sup> | PA11 <sup>4</sup> | PA10 | PA9  | PA8              |

| Fifth  | LA0 <sup>6,7</sup> | BA22              | BA21              | BA20              | BA19              | BA18 | BA17 | BA16             |

#### Notes:

- CAx = column address, PAx = page address, BAx = block address, LAx = LUN address; the page address, block address, and LUN address are collectively called the row address. Consequently, the first and second cycles containing the column addresses are known as C1 and C2, and the third, fourth, fifth, and sixth cycles containing the row addresses cycles are known as R1, R2, R3, and R4 respectively.

- 2) When using the NV-DDR2/NV-DDR3 interface, CA0 is forced to 0 internally; one data cycle always returns one even byte and one odd byte.

- 3) CA [14:0] address column addresses 0 through 18,591 (16,384 + 2208) (489Fh), therefore column addresses 18,592 (48A0h) through 32,767(7FFFh) are invalid, out of bounds, do not exist in the device, and cannot be addressed.

- 4) PA [11:0] address page addresses 0 through 2303 (8FFh), therefore page addresses 2304 (900h) through 4095 (FFFh) are invalid, out of bounds, do not exist in the device, and cannot be addressed.

- 5) BA[13:12] are the plane-select bits:

- Plane 0: BA[13:12] = 00b

- Plane 1: BA[13:12] = 01b

- Plane 2: BA[13:12] = 10b

- Plane 3: BA[13:12] = 11b

- 6) LA0 is the LUN-select bit.

- LUN 0: LA0 = 0

LUN 1: LA0 = 1

7) Block addresses 2016 through 2047 and 4063 through 4095 are invalid, out of bounds, do not exist in the device, and cannot be addressed.

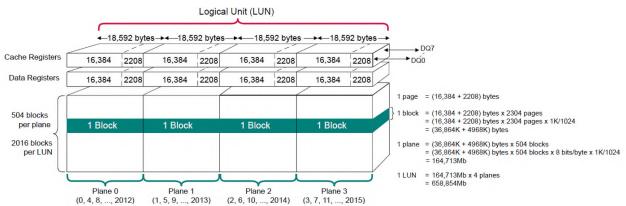

Table 3: Array Addressing for Logical Unit (LUN) in SLC mode

| Cycle  | DQ7                | DQ6               | DQ5               | DQ4               | DQ3  | DQ2  | DQ1  | DQ0              |

|--------|--------------------|-------------------|-------------------|-------------------|------|------|------|------------------|

| First  | CA7                | CA6               | CA5               | CA4               | CA3  | CA2  | CA1  | CA0 <sup>2</sup> |

| Second | LOW                | CA14 <sup>3</sup> | CA13              | CA12              | CA11 | CA10 | CA9  | CA8              |

| Third  | PA7                | PA6               | PA5               | PA4               | PA3  | PA2  | PA1  | PA0              |

| Fourth | BA15               | BA14              | BA13 <sup>5</sup> | BA12 <sup>5</sup> | LOW  | LOW  | PA9⁴ | PA8              |

| Fifth  | LA0 <sup>6,7</sup> | BA22              | BA21              | BA20              | BA19 | BA18 | BA17 | BA16             |

#### Notes:

- CAx = column address, PAx = page address, BAx = block address, LAx = LUN address; the page address, block address, and LUN address are collectively called the row address. Consequently, the first and second cycles containing the column addresses are known as C1 and C2, and the third, fourth, fifth, and sixth cycles containing the row addresses cycles are known as R1, R2, R3, and R4 respectively.

- 2) When using the NV-DDR2/NV-DDR3 interface, CA0 is forced to 0 internally; one data cycle always returns one even byte and one odd byte.

- 3) CA [14:0] address column addresses 0 through 18,591 (16,384 + 2208) (489Fh), therefore column addresses 18,592 (48A0h) through 32,767 (7FFFh) are invalid, out of bounds, do not exist in the device, and cannot be addressed.

- 4) PA [9:0] address page addresses 0 through 767 (2FFh), therefore page addresses 768 (300h) through 1023 (3FFh) are invalid, out of bounds, do not exist in the device, and cannot be addressed.

- 5) BA[13:12] are the plane-select bits:

- Plane 0: BA[13:12] = 00b

- Plane 1: BA[13:12] = 01b

- Plane 2: BA[13:12] = 10b

- Plane 3: BA[13:12] = 11b

- 6) LA0 is the LUN-select bit.

LUN 0: LA0 = 0

LUN 1: LA0 = 1

7) Block addresses 2016 through 2047 and 4063 through 4095 are invalid, out of bounds, do not exist in the device, and cannot be addressed.

DATASHEET

## UT81NDQ512G8T

#### 7 Command Definitions

| Command                                      | Command<br>Cycle #1 | Number<br>of Valid<br>Address<br>Cycles <sup>9</sup><br>#1 | Data<br>Input<br>Cycles | Command<br>Cycle #2 | Number<br>of Valid<br>Address<br>Cycles <sup>9</sup><br>#2 | Command<br>Cycle #3 | Valid<br>While<br>Selected<br>LUN Is<br>Busy <sup>1</sup> | Valid<br>While<br>Other<br>LUNs are<br>Busy <sup>2</sup> | Notes |

|----------------------------------------------|---------------------|------------------------------------------------------------|-------------------------|---------------------|------------------------------------------------------------|---------------------|-----------------------------------------------------------|----------------------------------------------------------|-------|

| Reset Operations                             |                     |                                                            |                         |                     |                                                            |                     |                                                           |                                                          |       |

| RESET                                        | FFh                 | 0                                                          | -                       | -                   | -                                                          | -                   | Yes                                                       | Yes                                                      |       |

| HARD RESET                                   | FDh                 | 0                                                          | -                       | -                   | -                                                          | -                   |                                                           | Yes                                                      |       |

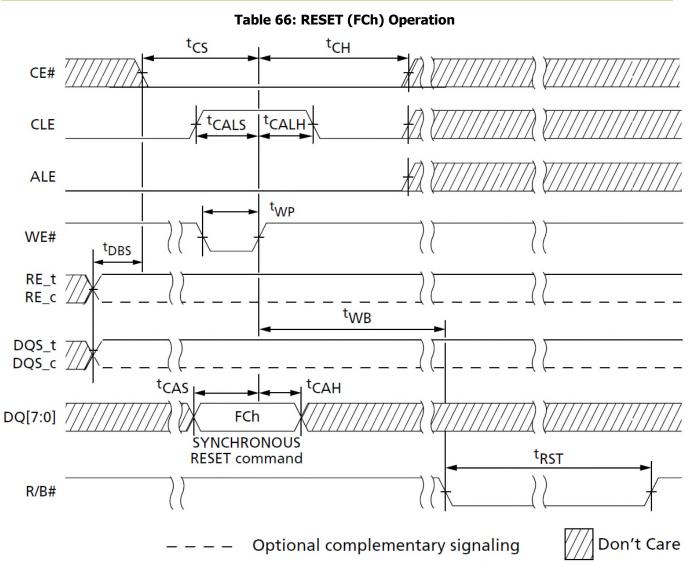

| SYNCHRONOUS<br>RESET                         | FCh                 | 0                                                          | -                       | -                   | -                                                          | -                   | Yes                                                       | Yes                                                      |       |

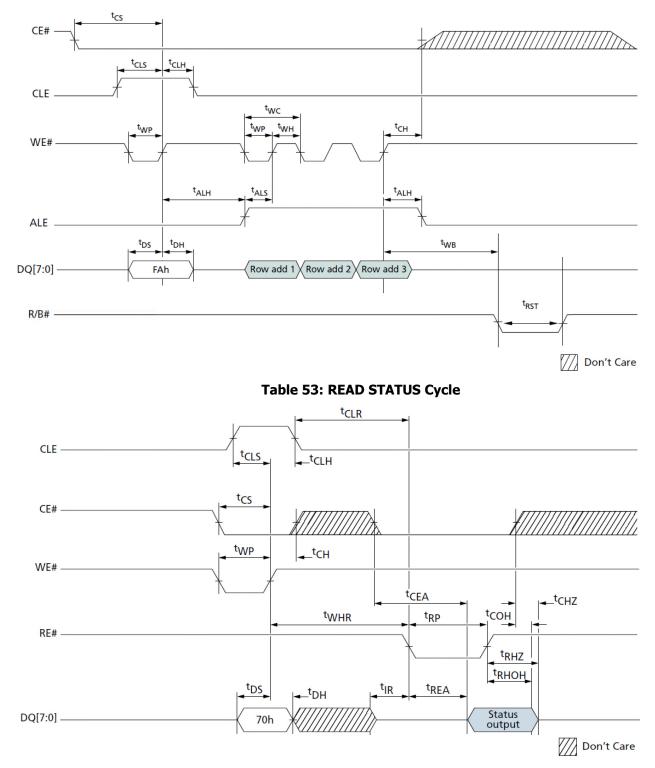

| RESET LUN                                    | FAh                 | 3/4                                                        | -                       | -                   | -                                                          | -                   | Yes                                                       | Yes                                                      |       |

| Identification Ope                           | erations            |                                                            |                         |                     |                                                            | •                   | •                                                         |                                                          |       |

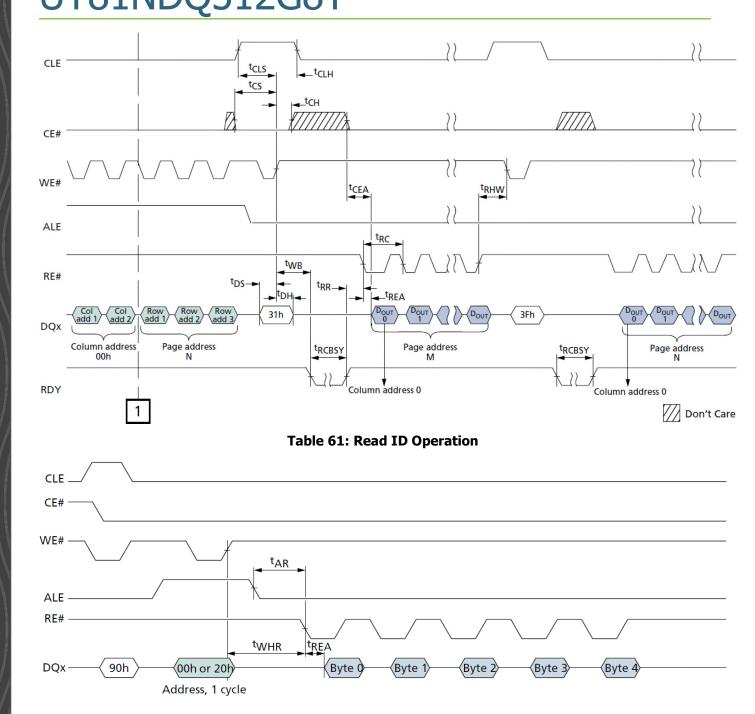

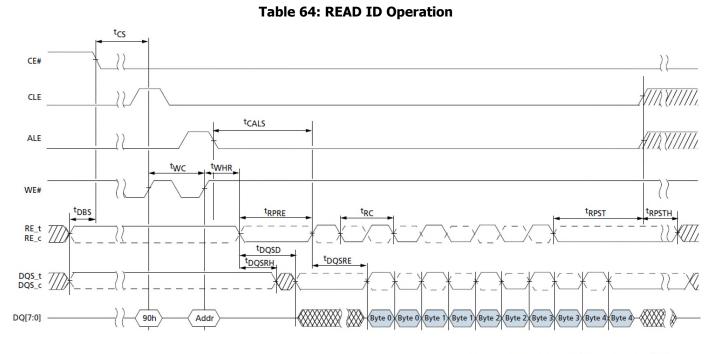

| READ ID                                      | 90h                 | 1                                                          | -                       | -                   | -                                                          | -                   |                                                           |                                                          | 3     |

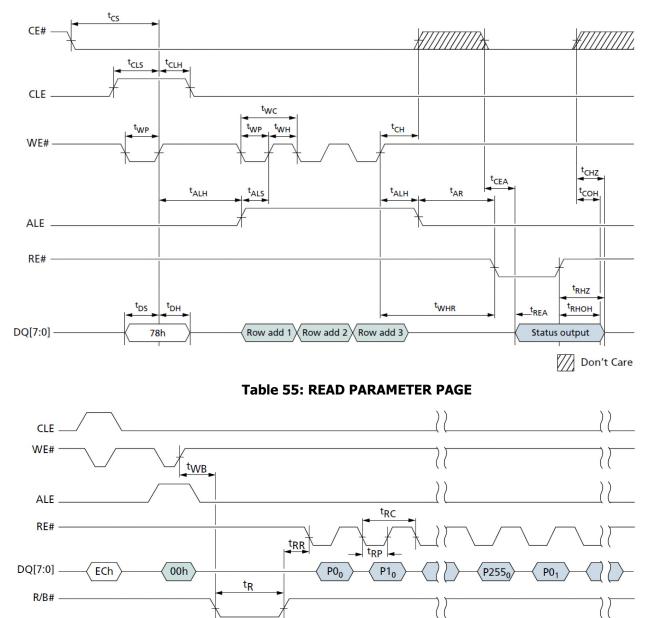

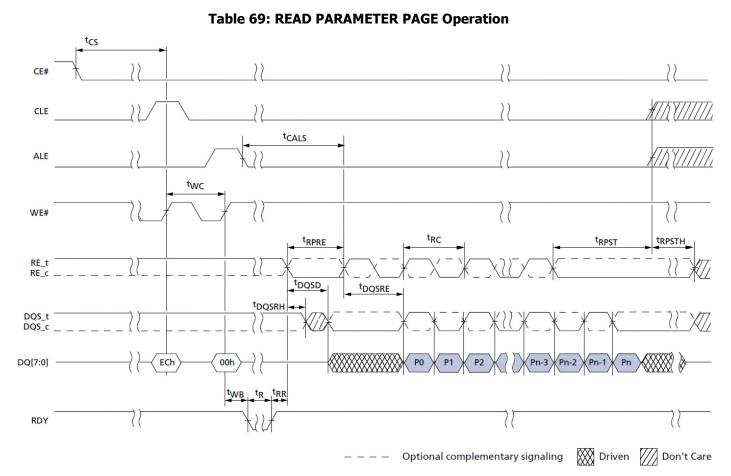

| READ<br>PARAMETER PAGE                       | ECh                 | 1                                                          | -                       | -                   | -                                                          | -                   |                                                           |                                                          |       |

| READ UNIQUE ID                               | EDh                 | 1                                                          | -                       | -                   | -                                                          | -                   |                                                           |                                                          |       |

| Configuration Op                             | erations            |                                                            |                         |                     |                                                            | •                   | •                                                         |                                                          |       |

| VOLUME SELECT                                | E1h                 | 1                                                          | -                       | -                   | -                                                          | -                   |                                                           |                                                          |       |

| ODT CONFIGURE                                | E2h                 | 1/2                                                        | 4                       | -                   | -                                                          | -                   |                                                           |                                                          |       |

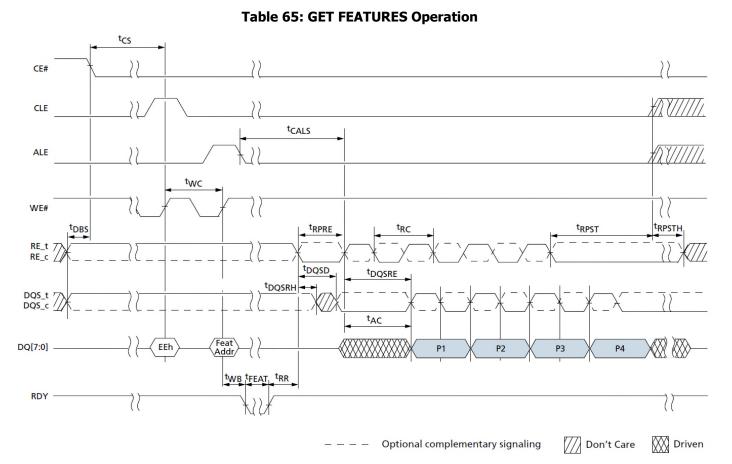

| GET FEATURES                                 | EEh                 | 1                                                          | -                       | -                   | -                                                          | -                   |                                                           |                                                          | 3     |

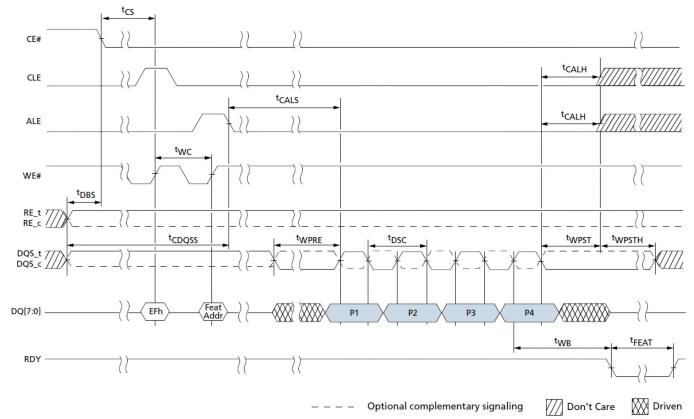

| SET FEATURE                                  | EFh                 | 1                                                          | 4                       | -                   | -                                                          | -                   |                                                           |                                                          | 4     |

| GET FEATURES<br>BY LUN                       | D4h                 | 2                                                          | -                       | -                   | -                                                          | -                   | -                                                         | Yes                                                      | 3     |

| SET FEATURES BY<br>LUN                       | D5h                 | 2                                                          | 4                       | -                   | -                                                          | -                   | -                                                         | Yes                                                      | 4     |

| ZQ CALIBRATION<br>LONG                       | F9h                 | 1                                                          | -                       | -                   | -                                                          | -                   |                                                           | Yes                                                      |       |

| ZQ CALIBRATION<br>SHORT                      | D9h                 | 1                                                          | -                       | -                   | -                                                          | -                   |                                                           | Yes                                                      |       |

| SLC MODE<br>ENABLE                           | DAh                 | 0                                                          | -                       | -                   | -                                                          | -                   |                                                           | Yes                                                      |       |

| SLC MODE<br>DISABLE                          | DFh                 | 0                                                          | -                       | -                   | -                                                          | -                   |                                                           | Yes                                                      |       |

| Status Operations                            | 5                   |                                                            |                         |                     |                                                            |                     |                                                           |                                                          |       |

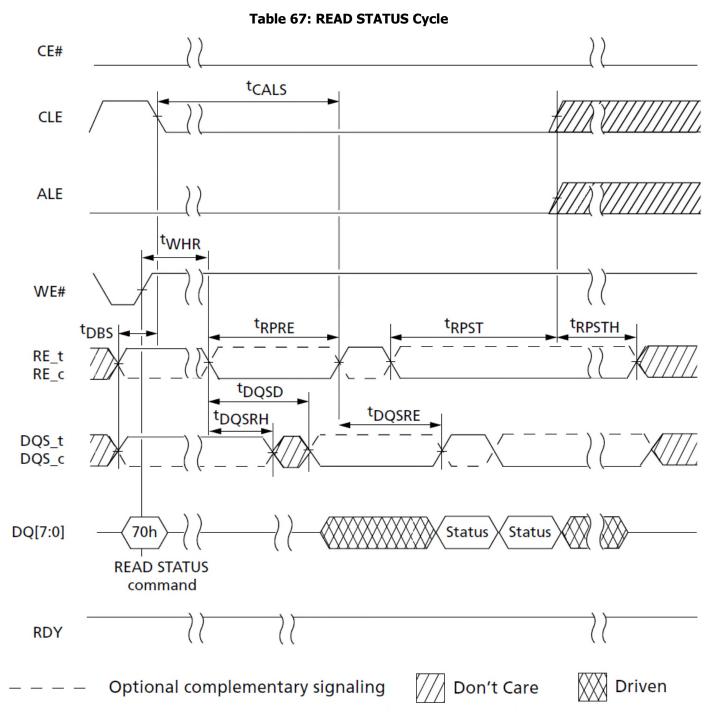

| READ STATUS                                  | 70h                 | 0                                                          | -                       | -                   | -                                                          | -                   | Yes                                                       |                                                          |       |

| FIXED ADDRESS<br>READ STATUS<br>ENHANCED     | 71h                 | 1                                                          | -                       | -                   | -                                                          | -                   | Yes                                                       | Yes                                                      |       |

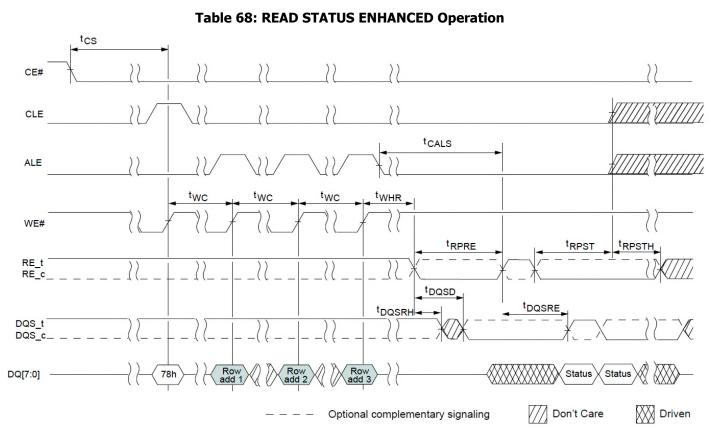

| READ STATUS<br>ENHANCED                      | 78h                 | 3/4                                                        | -                       | -                   | -                                                          | -                   | Yes                                                       | Yes                                                      |       |

| Column Address (                             | Operations          |                                                            |                         |                     |                                                            |                     |                                                           |                                                          |       |

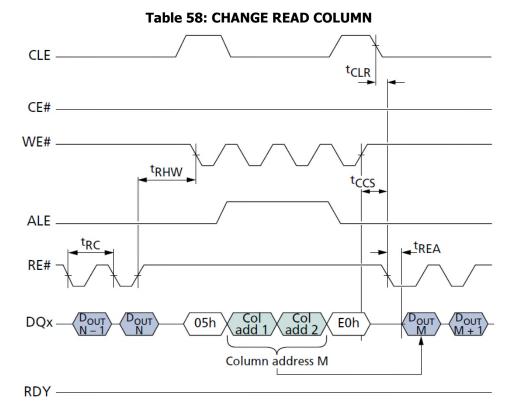

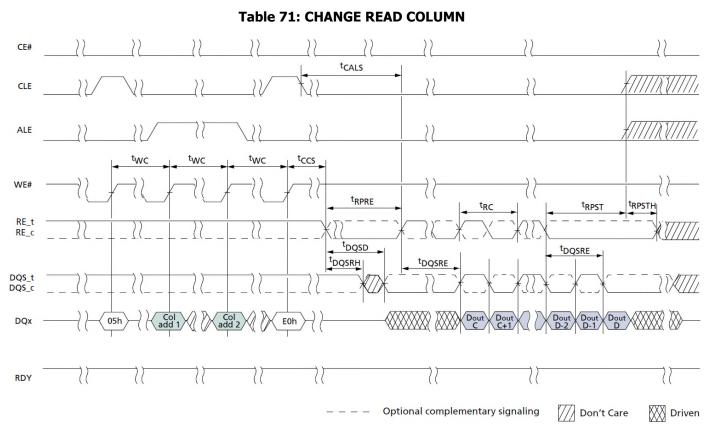

| Change Read<br>Column                        | 05h                 | 2                                                          | -                       | E0h                 | -                                                          | -                   |                                                           | Yes                                                      |       |

| CHANGE READ<br>COLUMN<br>ENHANCED<br>(ONFI)  | 06h                 | 5/6                                                        | -                       | E0h                 | -                                                          | -                   |                                                           | Yes                                                      |       |

| CHANGE READ<br>COLUMN<br>ENHANCED<br>(JEDEC) | 00h                 | 5/6                                                        | -                       | 05h                 | 2                                                          | E0h                 |                                                           | Yes                                                      |       |

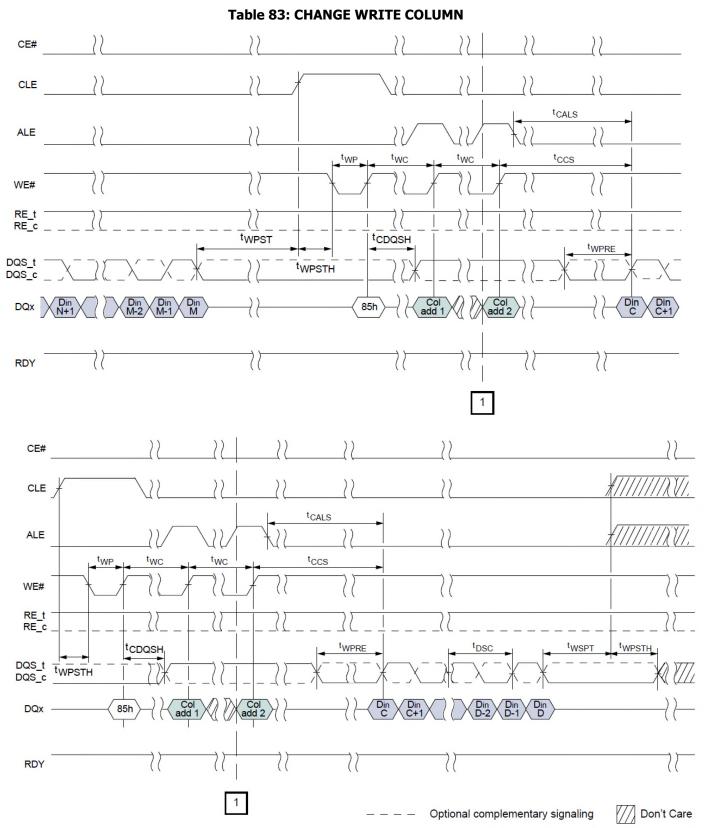

| Change Write<br>Column                       | 85h                 | 2                                                          | Optional                | -                   | -                                                          | -                   |                                                           | Yes                                                      |       |

## UT81NDQ512G8T

|                                                  |            | Number                         |               |                   | Number                         |          | Valid              | Valid             |       |

|--------------------------------------------------|------------|--------------------------------|---------------|-------------------|--------------------------------|----------|--------------------|-------------------|-------|

|                                                  |            | of Valid                       | Dete          |                   | of Valid<br>Address            |          | While              | While<br>Other    |       |

|                                                  | Command    | Address<br>Cycles <sup>9</sup> | Data<br>Input | Command           | Address<br>Cycles <sup>9</sup> | Command  | Selected<br>LUN Is | LUNs are          |       |

| Command                                          | Cycle #1   | #1                             | Cycles        | Cycle #2          | #2                             | Cycle #3 | Busy <sup>1</sup>  | Busy <sup>2</sup> | Notes |

| CHANGE ROW<br>ADDRESS                            | 85h        | 5/6                            | Optional      | 11h<br>(Optional) | -                              | -        |                    | Yes               | 5     |

| Read Operations                                  | <u> </u>   |                                | <u> </u>      |                   | L                              | <u> </u> | I                  | I                 |       |

| READ MODE                                        | 00h        | 0                              | -             | -                 | -                              | -        |                    | Yes               |       |

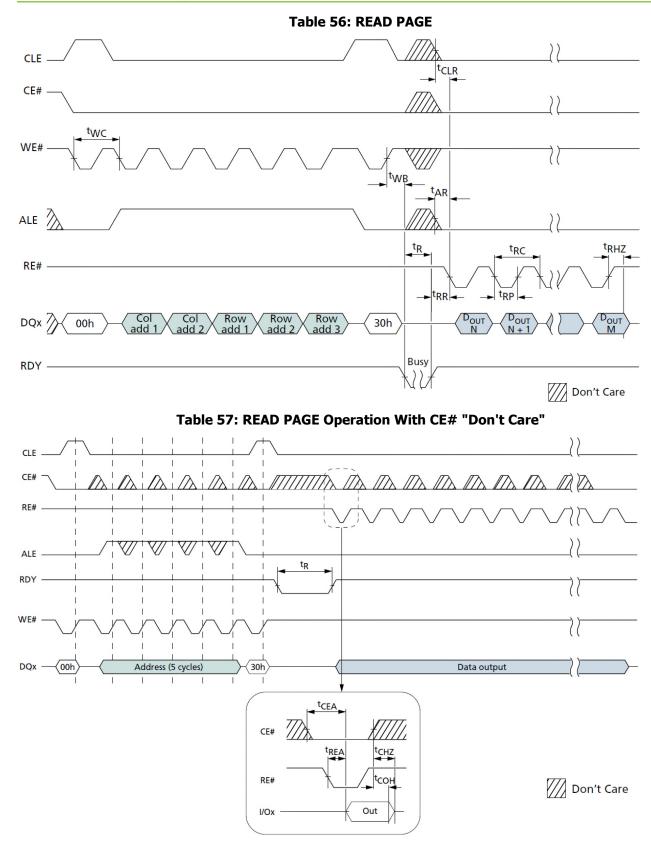

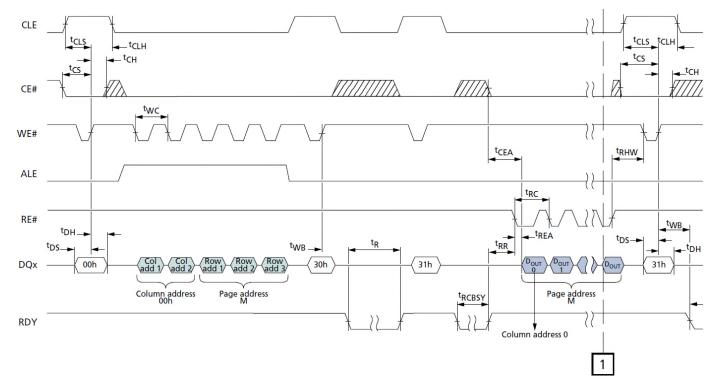

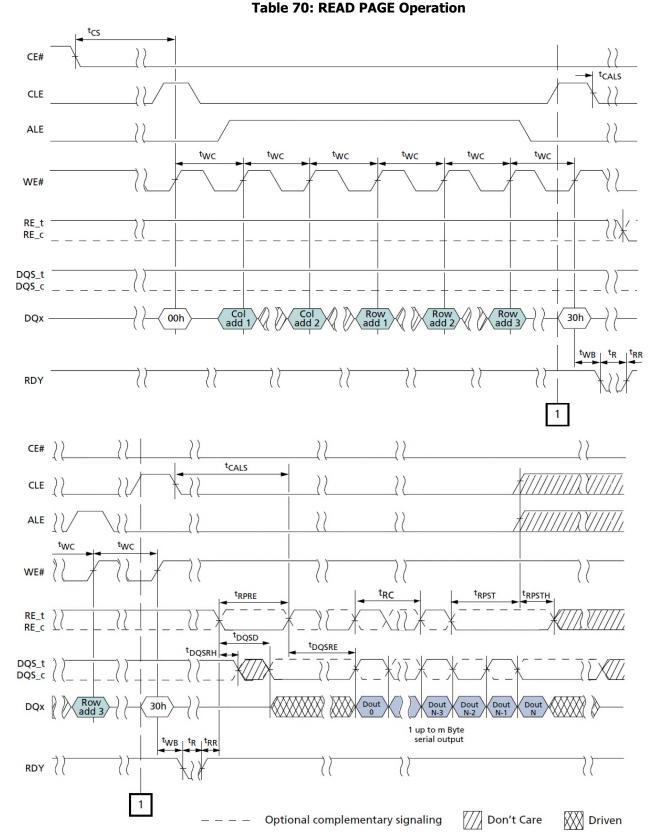

| READ PAGE                                        | 00h        | 5/6                            | -             | 30h               | -                              | -        |                    | Yes               | 6     |

| SNAP READ                                        | 00h        | 5/6                            | -             | 20h               | -                              | -        |                    | Yes               |       |

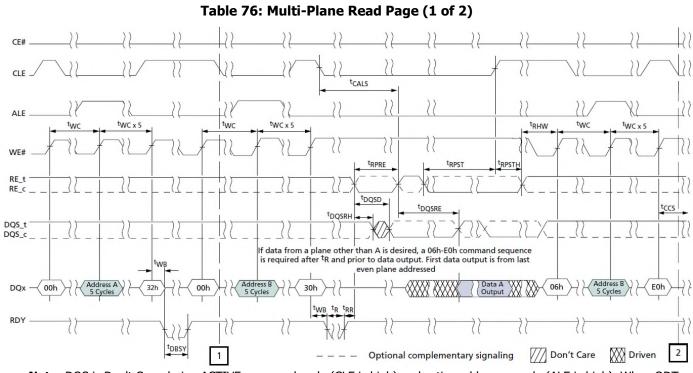

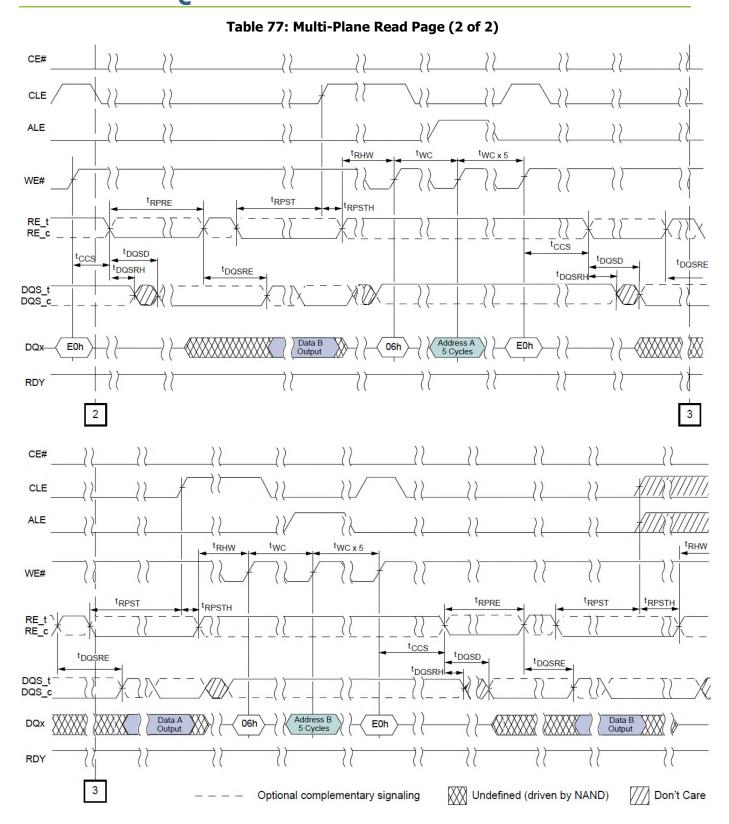

| READ PAGE MULI-<br>PLANE                         | 00h        | 5/6                            | -             | 32h               | -                              | -        |                    | Yes               |       |

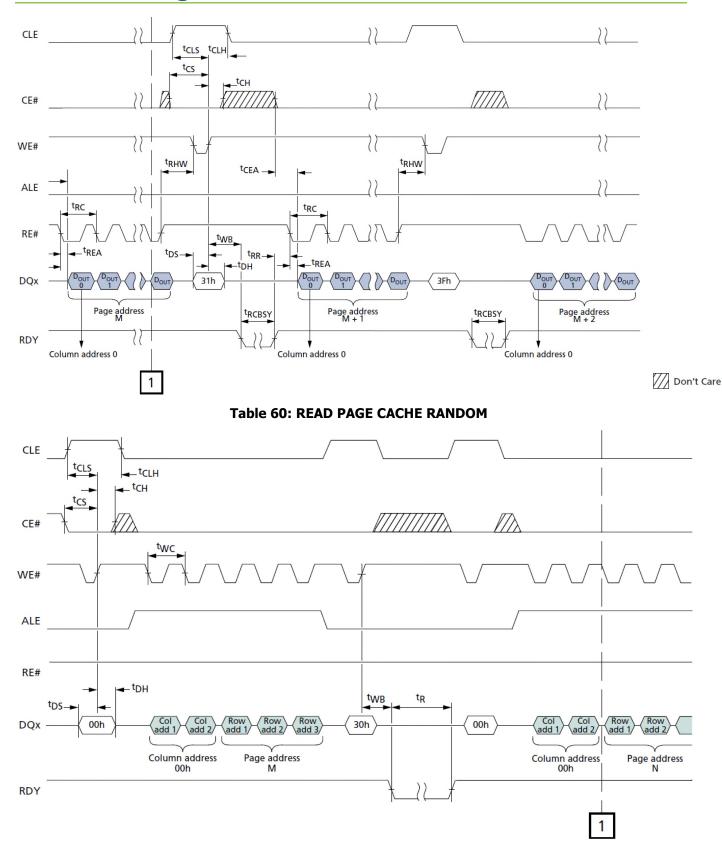

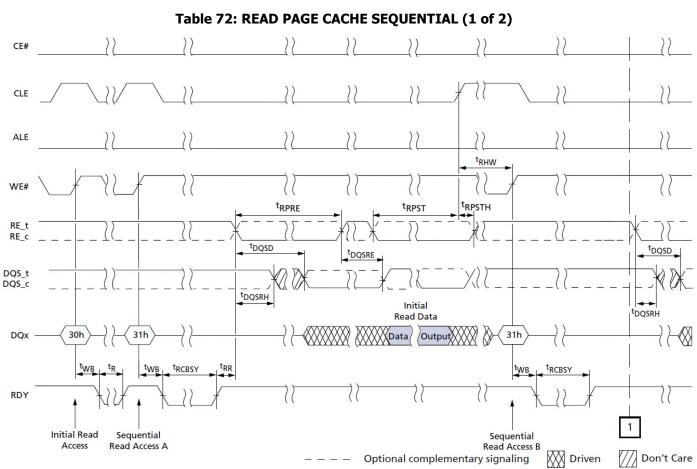

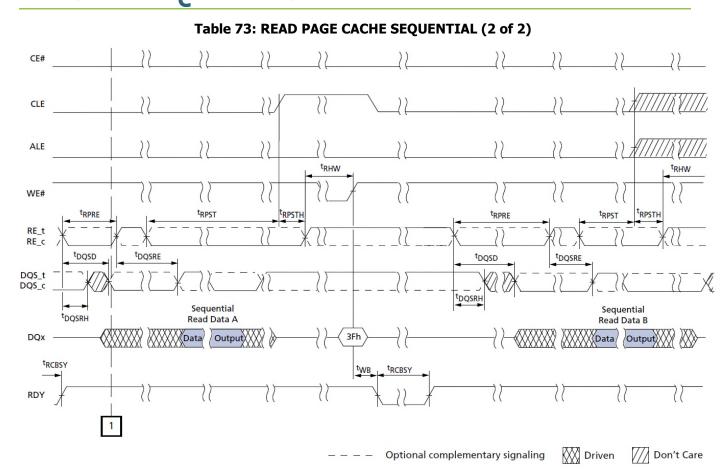

| READ PAGE<br>CACHE<br>SEQUENTIAL                 | 31h        | 0                              | -             | -                 | -                              | -        |                    | Yes               | 7     |

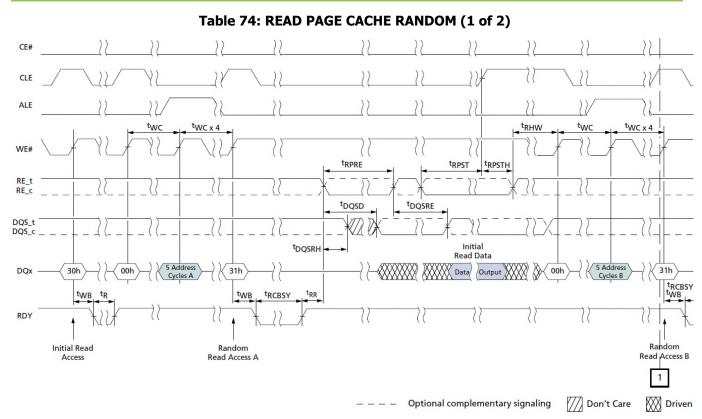

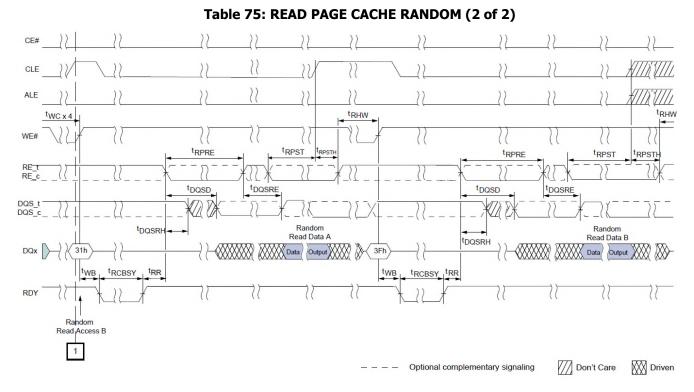

| READ PAGE<br>CACHE RANDOM                        | 00h        | 5/6                            | -             | 31h               | -                              | -        |                    | Yes               | 6, 7  |

| READ PAGE<br>CACHE LAST                          | 3Fh        | 0                              | -             | -                 | -                              | -        |                    | Yes               | 7     |

| READ PAGE WITH<br>SOFT<br>INFORMATION            | 33h        | 5/6                            | -             | 30h               | -                              | -        |                    | Yes               |       |

| SOFT<br>INFORMATION<br>READOUT                   | 36h        | 0                              | -             |                   | -                              | -        |                    | Yes               | 10    |

| SINGLE BIT SOFT<br>BIT READ PAGE                 | 00h        | 5/6                            | -             | 34h               | -                              | -        |                    | Yes               |       |

| SINGLE BIT SOFT<br>BIT READ PAGE<br>CACHE RANDOM | 00h        | 5/6                            | -             | 38h               | -                              | -        |                    | Yes               |       |

| Program Operation                                | ons        |                                |               |                   |                                |          |                    |                   |       |

| PROGRAM PAGE                                     | 80h        | 5/6                            | Yes           | 10h               | -                              | -        |                    | Yes               |       |

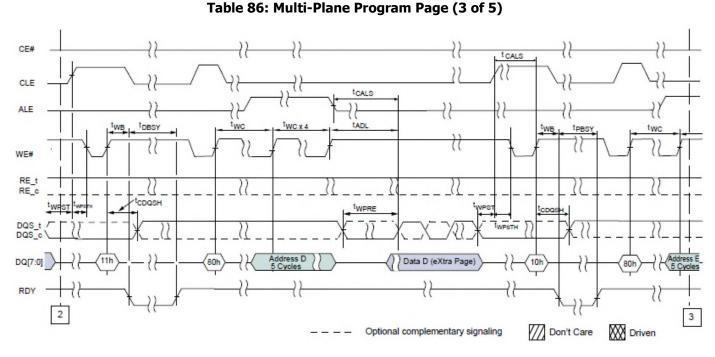

| PROGRAM PAGE<br>MULTI-PLANE                      | 80h or 81h | 5/6                            | Yes           | 11h               | -                              | -        |                    | Yes               |       |

| PROGRAM PAGE<br>CACHE                            | 80h        | 5/6                            | Yes           | 15h               | -                              | -        |                    | Yes               | 8     |

| PROGRAM<br>SUSPEND                               | 84h        | 5/6                            | -             | -                 | -                              | -        | Yes                | Yes               |       |

| PROGRAM<br>RESUME                                | 13h        | 5/6                            | -             | -                 | -                              | -        |                    | Yes               |       |

| Erase Operations                                 |            |                                |               |                   |                                |          |                    |                   |       |

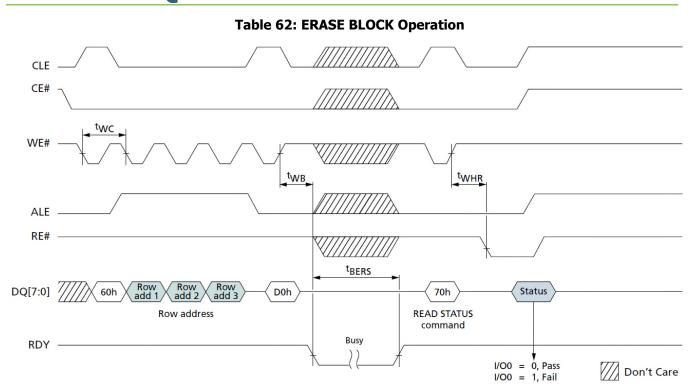

| ERASE BLOCK                                      | 60h        | 3/4                            | -             | D0h               | -                              | -        |                    | Yes               |       |

| ERASE BLOCK<br>MULTI-PLANE<br>(ONFI)             | 60h        | 3/4                            | -             | D1h               | -                              | -        |                    | Yes               |       |

## UT81NDQ512G8T

| Command                               | Command<br>Cycle #1 | Number<br>of Valid<br>Address<br>Cycles <sup>9</sup><br>#1 | Data<br>Input<br>Cycles | Command<br>Cycle #2 | Number<br>of Valid<br>Address<br>Cycles <sup>9</sup><br>#2 | Command<br>Cycle #3 | Valid<br>While<br>Selected<br>LUN Is<br>Busy <sup>1</sup> | Valid<br>While<br>Other<br>LUNs are<br>Busy <sup>2</sup> | Notes |

|---------------------------------------|---------------------|------------------------------------------------------------|-------------------------|---------------------|------------------------------------------------------------|---------------------|-----------------------------------------------------------|----------------------------------------------------------|-------|

| ERASE BLOCK<br>MULTI-PLANE<br>(JEDEC) | 60h                 | 3/4                                                        | -                       | 60h                 | 3                                                          | D0h                 |                                                           | Yes                                                      |       |

| ERASE SUSPEND                         | 61h                 | 3/4                                                        | -                       | -                   | -                                                          | -                   | Yes                                                       | Yes                                                      |       |

| ERASE RESUME                          | D2h                 | -                                                          | -                       | -                   | -                                                          | -                   |                                                           | Yes                                                      |       |

| Copyback Operati                      | ons                 | <u> </u>                                                   |                         |                     | <u> </u>                                                   |                     |                                                           |                                                          |       |

| COPYBACK READ                         | 00h                 | 5/6                                                        | -                       | 35h                 | -                                                          | -                   |                                                           | Yes                                                      | 6     |

| Copyback<br>Program                   | 85h                 | 5/6                                                        | Optional                | 10h                 | -                                                          | -                   |                                                           | Yes                                                      |       |

| COPYBACK<br>PROGRAM MULTI-<br>PLANE   | 85h                 | 5/6                                                        | Optional                | 11h                 | -                                                          | -                   |                                                           | Yes                                                      |       |

- 1) Busy means RDY = 0.

- 2) These commands can be used for interleaved die (multi-LUN) operations.

- The READ ID (90h), GET FEATURES (EEh), and GET FEATUERS by LUN (D4h) commands output identical data on rising and falling DQS edges.

- 4) The SET FEATURES (EFh) and SET FEATURES by LUN (D5h) commands requires data transition prior to the rising edge of DQS, with identical data for the rising and falling edges.

- 5) Command cycle #2 of 11h is conditional. See the User Manual, CHANGE ROW ADDRESS (85h) for more details.

- 6) This command can be preceded by READ PAGE MULTI-PLANE (00h-32h) command to accommodate a maximum simultaneous multi-plane array operation.

- 7) Issuing a READ PAGE CACHE-series (31h, 00h-31h, 00h-32h, 3Fh) command when the array is busy (RDY = 1, ARDY = 0) is supported if the previous command was a READ PAGE (00h-30h) or READ PAGE CACHE-series command; otherwise, it is prohibited.

- 8) Issuing a PROGRAM PAGE CACHE (80h-15h) command when the array is busy (RDY = 1, ARDY = 0) is supported if the previous command was a PROGRAM PAGE CACHE (80h-15h) command; otherwise, it is prohibited.

- 9) Refer to Device and Array Organization section for details of when the additional address cycles is required.

- 10) Refer to the User Manual, Soft Data Read Operations section for details of how this command is used.

#### 8 Output Drive Impedance

Because NAND Flash is designed for use in systems that are typically point-to-point connections, an option to control the drive strength of the output buffers is provided. Drive strength should be selected based on the expected loading of the memory bus. The three supported settings for the output drivers for the Asynchronous, and NVDDR2 interfaces are: 25 ohms, 35 ohms, and 50 ohms. The two supported settings for the output drivers for the NV-DDR3 interface are: 35 ohms and 50 ohms.

The 35 ohms output drive strength setting is the power-on default value in the Asynchronous, and NV-DDR2 interfaces. The 35 ohms output drive strength setting is the power-on default value in the NV-DDR3 interface. The host can select a different drive strength setting using the SET FEATURES (EFh) or SET FEATURES by LUN (D5h) command.

The output impedance range from minimum to maximum covers process, voltage, and temperature variations. Devices are not guaranteed to be at the nominal line.

| Range   | Process         | Voltage | Temperature          |

|---------|-----------------|---------|----------------------|

| Minimum | Fast-Fast       | 1.95V   | T <sub>A</sub> (MIN) |

| Nominal | Typical-Typical | 1.8V    | +25°C                |

| Maximum | Slow-Slow       | 1.7V    | T <sub>A</sub> (MAX) |

#### Table 4: Output Drive Strength Conditions (Vccq=1.7-1.95V)

|                    | -       | • •                  |         | -       | • •     | -    |

|--------------------|---------|----------------------|---------|---------|---------|------|

| Output<br>Strength | Rpd/Rpu | Vout to Vssq         | Minimum | Nominal | Maximum | Unit |

| 25 ohms            | Rpd     | $V_{CCQ} \times 0.2$ | 11.4    | 25.0    | 44.0    | ohms |

|                    |         | $V_{CCQ} \times 0.5$ | 15.0    | 25.0    | 44.0    | ohms |

|                    |         | $V_{CCQ} 	imes 0.8$  | 15.0    | 25.0    | 61.0    | ohms |

|                    | Rpu     | $V_{CCQ} \times 0.2$ | 15.0    | 25.0    | 61.0    | ohms |

|                    |         | $V_{CCQ} \times 0.5$ | 15.0    | 25.0    | 44.0    | ohms |

|                    |         | $V_{CCQ} \times 0.8$ | 11.4    | 25.0    | 44.0    | ohms |

| 35 ohms            | Rpd     | $V_{CCQ} \times 0.2$ | 16.0    | 35.0    | 61.0    | ohms |

|                    |         | $V_{CCQ} \times 0.5$ | 21.0    | 35.0    | 61.0    | ohms |

|                    |         | $V_{CCQ} 	imes 0.8$  | 21.0    | 35.0    | 85.3    | ohms |

|                    | Rpu     | $V_{CCQ} \times 0.2$ | 21.0    | 35.0    | 85.3    | ohms |

|                    |         | $V_{CCQ} \times 0.5$ | 21.0    | 35.0    | 61.0    | ohms |

|                    |         | $V_{CCQ} 	imes 0.8$  | 16.0    | 35.0    | 61.0    | ohms |

| 50 ohms            | Rpd     | $V_{CCQ} \times 0.2$ | 24.0    | 50.0    | 87.0    | ohms |

|                    |         | $V_{CCQ} \times 0.5$ | 30.0    | 50.0    | 87.0    | ohms |

|                    |         | $V_{CCQ} \times 0.8$ | 30.0    | 50.0    | 122.0   | ohms |

|                    | Rpu     | $V_{CCQ} \times 0.2$ | 30.0    | 50.0    | 122.0   | ohms |

|                    |         | $V_{CCQ} \times 0.5$ | 30.0    | 50.0    | 87.0    | ohms |

|                    |         | $V_{CCQ} \times 0.8$ | 24.0    | 50.0    | 87.0    | ohms |

#### Table 5: Output Drive Strength Impedance Values Without ZQ Calibration ( $V_{CCQ} = 1.7-1.95V$ )

#### Table 6: Output Drive Strength Impedance Values With ZQ Calibration ( $V_{CCQ} = 1.7 - 1.95V$ )

| Output<br>Strength | Rpd/Rpu | Vout <b>to</b><br>Vssq     | Minimum | Nominal | Maximum | Unit                 | Note |

|--------------------|---------|----------------------------|---------|---------|---------|----------------------|------|

| 25 ohms            | Rpd     | $V_{CCQ} \times 0.2$       | 11.4    | 20.0    | 32.0    | ohms                 | 1    |

|                    |         | $V_{CCQ} \times 0.5$       | 16.3    | 25.0    | 33.7    | ohms                 |      |

|                    |         | $V_{CCQ} \times 0.8$       | 20.0    | 31.0    | 49.0    | ohms                 |      |

|                    | Rpu     | $V_{CCQ} \times 0.2$       | 20.0    | 31.0    | 49.0    | ohms                 |      |

|                    |         | $V_{CCQ} \times 0.5$       | 16.3    | 25.0    | 33.7    | ohms                 |      |

|                    |         | $V_{\text{CCQ}} 	imes 0.8$ | 11.4    | 20.0    | 32.0    | ohms                 |      |

| 35 ohms            | Rpd     | $V_{CCQ} \times 0.2$       | 0.57    | 1       | 1.15    | R <sub>zQ</sub> /8.5 |      |

|                    |         | $V_{CCQ} \times 0.5$       | 0.85    | 1       | 1.15    | Rzq/8.5              |      |

|                    |         | $V_{CCQ} \times 0.8$       | 0.85    | 1       | 1.47    | Rzq/8.5              |      |

|                    | Rpu     | $V_{CCQ} \times 0.2$       | 0.85    | 1       | 1.47    | Rzq/8.5              |      |

|                    |         | $V_{CCQ} \times 0.5$       | 0.85    | 1       | 1.15    | Rzq/8.5              |      |

|                    |         | $V_{CCQ} \times 0.8$       | 0.57    | 1       | 1.15    | Rzq/8.5              |      |

| 50 ohms            | Rpd     | $V_{CCQ} \times 0.2$       | 0.57    | 1       | 1.15    | R <sub>zQ</sub> /6   |      |

|                    |         | $V_{CCQ} \times 0.5$       | 0.85    | 1       | 1.15    | R <sub>zQ</sub> /6   |      |

|                    |         | $V_{CCQ} \times 0.8$       | 0.85    | 1       | 1.47    | R <sub>zQ</sub> /6   |      |

|                    | Rpu     | $V_{CCQ} \times 0.2$       | 0.85    | 1       | 1.47    | Rzq/6                |      |

|                    |         | $V_{\text{CCQ}} 	imes 0.5$ | 0.85    | 1       | 1.15    | R <sub>ZQ</sub> /6   |      |

|                    |         | $V_{CCQ} \times 0.8$       | 0.57    | 1       | 1.15    | Rzq/6                |      |

- 1) The 25 ohms drive strength does not support ZQ CALIBRATION operations. If ZQ CALIBRATION operations are used when the 25 ohms drive strength is selected, the default NAND drive strength settings are still used.

- 2) Tolerance limits assume RZQ of 300 ohms ±1% and are applicable after proper ZQ calibration has been performed at a stable temperature and voltage.

- 3) Refer to Output Driver Sensitivity if either the temperature or the voltage changes after calibration.

- 4) The minimum values are derated by 6% when the device operates between -40°C and 0°C.

| <b>Table 7: Output Drive Strength</b> | <b>Conditions (V</b> <sub>CCQ</sub> =1.14-1.26V) |

|---------------------------------------|--------------------------------------------------|

|---------------------------------------|--------------------------------------------------|

| Range   | Process         | Voltage | Temperature          |

|---------|-----------------|---------|----------------------|

| Minimum | Fast-Fast       | 1.26V   | T <sub>A</sub> (MIN) |

| Nominal | Typical-Typical | 1.2V    | +25°C                |

| Maximum | Slow-Slow       | 1.14V   | T <sub>A</sub> (MAX) |

#### Table 8: Output Drive Strength Impedance Values Without ZQ Calibration (V<sub>CCQ</sub> = 1.14–1.26V)

| Output<br>Strength | Rpd/Rpu | Vout <b>to</b><br>Vssq | Minimum | Nominal | Maximum | Unit |

|--------------------|---------|------------------------|---------|---------|---------|------|

| 35 ohms            | Rpd     | $V_{CCQ} \times 0.2$   | 16.0    | 35.0    | 61.0    | ohms |

|                    |         | $V_{CCQ} \times 0.5$   | 21.0    | 35.0    | 61.0    | ohms |

|                    |         | $V_{CCQ} \times 0.8$   | 21.0    | 35.0    | 85.3    | ohms |

|                    | Rpu     | $V_{CCQ} \times 0.2$   | 21.0    | 35.0    | 85.3    | ohms |

|                    |         | $V_{CCQ} \times 0.5$   | 21.0    | 35.0    | 61.0    | ohms |

|                    |         | $V_{CCQ} \times 0.8$   | 16.0    | 35.0    | 61.0    | ohms |

| 50 ohms            | Rpd     | $V_{CCQ} \times 0.2$   | 24.0    | 50.0    | 87.0    | ohms |

|                    |         | $V_{CCQ} \times 0.5$   | 30.0    | 50.0    | 87.0    | ohms |

|                    |         | $V_{CCQ} \times 0.8$   | 30.0    | 50.0    | 122.0   | ohms |

|                    | Rpu     | $V_{CCQ} \times 0.2$   | 30.0    | 50.0    | 122.0   | ohms |

|                    |         | $V_{CCQ} \times 0.5$   | 30.0    | 50.0    | 87.0    | ohms |

|                    |         | $V_{CCQ} \times 0.8$   | 24.0    | 50.0    | 87.0    | ohms |

#### Table 9: Output Drive Strength Impedance Values With ZQ Calibration (V<sub>CCQ</sub> = 1.14–1.26V)

| Output<br>Strength | Rpd/Rpu | V <sub>OUT</sub> to<br>V <sub>SSQ</sub> | Minimum | Nominal | Maximum | Unit                 |

|--------------------|---------|-----------------------------------------|---------|---------|---------|----------------------|

| 35 ohms            | Rpd     | $V_{CCQ} \times 0.2$                    | 0.57    | 1       | 1.15    | Rzq/8.5              |

|                    |         | $V_{CCQ} \times 0.5$                    | 0.85    | 1       | 1.15    | Rzq/8.5              |

|                    |         | $V_{CCQ} \times 0.8$                    | 0.85    | 1       | 1.47    | Rzq/8.5              |

|                    | Rpu     | $V_{CCQ} \times 0.2$                    | 0.85    | 1       | 1.47    | R <sub>ZQ</sub> /8.5 |

|                    |         | $V_{CCQ} \times 0.5$                    | 0.85    | 1       | 1.15    | R <sub>ZQ</sub> /8.5 |

|                    |         | $V_{CCQ} \times 0.8$                    | 0.57    | 1       | 1.15    | Rzq/8.5              |

| 50 ohms            | Rpd     | $V_{CCQ} \times 0.2$                    | 0.57    | 1       | 1.15    | Rzq/6                |

|                    |         | $V_{CCQ} \times 0.5$                    | 0.85    | 1       | 1.15    | Rzq/6                |

|                    |         | $V_{CCQ} \times 0.8$                    | 0.85    | 1       | 1.47    | Rzq/6                |

|                    | Rpu     | $V_{CCQ} \times 0.2$                    | 0.85    | 1       | 1.47    | R <sub>zQ</sub> /6   |

|                    |         | $V_{CCQ} \times 0.5$                    | 0.85    | 1       | 1.15    | Rzq/6                |

|                    |         | $V_{CCQ} \times 0.8$                    | 0.57    | 1       | 1.15    | Rzq/6                |

#### Notes:

- 1) Tolerance limits assume RZQ of 300 ohms ±1% and are applicable after proper ZQ calibration has been performed at a stable temperature and voltage.

- 2) Refer to Output Driver Sensitivity if either the temperature or the voltage changes after calibration.

- 3) The minimum values are derated by 6% when the device operates between -40°C and 0°C.

If either the temperature or the voltage changes after the ZQ CALIBRATION operation, then output drive strength impedance tolerance limits can be expected to widen according to Table 10 and Table 11.

## UT81NDQ512G8T

#### Table 10: Output Drive Sensitivity With ZQ Calibration

| Output<br>Strength | Rpd/Rpu | V <sub>OUT</sub> to V <sub>SSQ</sub> | Minimum                                                        | Maximum                                                        | Unit                 |

|--------------------|---------|--------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|----------------------|

| 35 ohms            | Rpd     | $V_{CCQ} \times 0.2$                 | $0.57 - dR_{ON}dT \times \Delta T - dR_{ON}dV \times \Delta V$ | $1.15 + dR_{ON}dT \times \Delta T + dR_{ON}dV \times \Delta V$ | R <sub>ZQ</sub> /8.5 |

|                    |         | V <sub>CCQ</sub> × 0.5               | $0.85 - dR_{ON}dT \times \Delta T - dR_{ON}dV \times \Delta V$ | $1.15 + dR_{ON}dT \times \Delta T + dR_{ON}dV \times \Delta V$ | R <sub>ZQ</sub> /8.5 |

|                    |         | V <sub>CCQ</sub> × 0.8               | 0.85 – dRondT x ΔT–<br>dRondV x ΔV                             | $1.47 + dR_{ON}dT \times \Delta T + dR_{ON}dV \times \Delta V$ | R <sub>ZQ</sub> /8.5 |

|                    | Rpu     | V <sub>CCQ</sub> × 0.2               | $0.85 - dR_{ON}dT \times \Delta T - dR_{ON}dV \times \Delta V$ | $1.47 + dR_{ON}dT \times \Delta T + dR_{ON}dV \times \Delta V$ | R <sub>ZQ</sub> /8.5 |

|                    |         | V <sub>CCQ</sub> × 0.5               | $0.85 - dR_{ON}dT \times \Delta T - dR_{ON}dV \times \Delta V$ | $1.15 + dR_{ON}dT \times \Delta T + dR_{ON}dV \times \Delta V$ | Rzq/8.5              |

|                    |         | $V_{CCQ} \times 0.8$                 | $0.57 - dR_{ON}dT \times \Delta T - dR_{ON}dV \times \Delta V$ | $1.15 + dR_{ON}dT \times \Delta T + dR_{ON}dV \times \Delta V$ | R <sub>ZQ</sub> /8.5 |

| 50 ohms            | Rpd     | V <sub>CCQ</sub> × 0.2               | $0.57 - dR_{ON}dT \times \Delta T - dR_{ON}dV \times \Delta V$ | $1.15 + dR_{ON}dT \times \Delta T + dR_{ON}dV \times \Delta V$ | Rzq/6                |

|                    |         | V <sub>CCQ</sub> × 0.5               | $0.85 - dR_{ON}dT \times \Delta T - dR_{ON}dV \times \Delta V$ | $1.15 + dR_{ON}dT \times \Delta T + dR_{ON}dV \times \Delta V$ | Rzq/6                |

|                    |         | $V_{CCQ} \times 0.8$                 | $0.85 - dR_{ON}dT \times \Delta T - dR_{ON}dV \times \Delta V$ | $1.47 + dR_{ON}dT \times \Delta T + dR_{ON}dV \times \Delta V$ | R <sub>ZQ</sub> /6   |

|                    | Rpu     | V <sub>CCQ</sub> × 0.2               | $0.85 - dR_{ON}dT \times \Delta T - dR_{ON}dV \times \Delta V$ | $1.47 + dR_{ON}dT \times \Delta T + dR_{ON}dV \times \Delta V$ | Rzq/6                |

|                    |         | V <sub>CCQ</sub> × 0.5               | $0.85 - dR_{ON}dT \times \Delta T - dR_{ON}dV \times \Delta V$ | $1.15 + dR_{ON}dT \times \Delta T + dR_{ON}dV \times \Delta V$ | Rzq/6                |

|                    |         | $V_{CCQ} \times 0.8$                 | $0.57 - dR_{ON}dT \times \Delta T - dR_{ON}dV \times \Delta V$ | $1.15 + dR_{ON}dT \times \Delta T + dR_{ON}dV \times \Delta V$ | R <sub>ZQ</sub> /6   |

#### Table 11: Output Driver Voltage and Temperature Sensitivity With ZQ Calibration

| Change | Minimum | Maximum | Unit |

|--------|---------|---------|------|

| dRondT | 0       | 0.5     | %/°C |

| dRondV | 0       | 0.2     | %/mV |

#### Table 12: Output Driver Voltage and Temperature Sensitivity With ZQ Calibration

| Drive Strength | Minimum | Maximum | Unit | Notes |

|----------------|---------|---------|------|-------|

| 25 ohms        | 0       | 4.4     | ohms | 1, 2  |

| 35 ohms        | 0       | 6.2     | ohms | 1, 2  |

| 50 ohms        | 0       | 8.8     | ohms | 1, 2  |

- 1) Mismatch is the absolute value between pull-up and pull-down impedances. Both are measured at the same temperature and voltage.

- 2) Test conditions:  $V_{CCQ} = V_{CCQ}$  (MIN),  $V_{OUT} = V_{CCQ} \times 0.5$ ,  $T_{OPER}$ .

#### Table 13: Pull-Up and Pull-Down Output Impedance Mismatch With ZQ Calibration for NV-DDR2

| Drive Strength | Minimum | Maximum | Unit | Notes   |

|----------------|---------|---------|------|---------|

| 25 ohms        | 0       | 3.75    | ohms | 1, 2, 3 |

| 35 ohms        | 0       | 5.25    | ohms | 2, 3    |

| 50 ohms        | 0       | 7.5     | ohms | 2, 3    |

Notes:

- 1) The 25 ohms drive strength does not support ZQ CALIBRATION operations. If ZQ CALIBRATION operations are used when the 25 ohms drive strength is selected, the default NAND drive strength settings are still used.

- 2) Mismatch is the absolute value between pull-up and pull-down impedances. Both are measured at the same temperature and voltage.

- 3) Test conditions:  $V_{CCQ} = V_{CCQ}$  (MIN),  $V_{OUT} = V_{CCQ} \times 0.5$ ,  $T_{OPER}$ .

#### Table 14: Pull-Up and Pull-Down Output Impedance Mismatch Without ZQ calibration for NV-DDR3

| Drive Strength | Minimum | Maximum | Unit | Notes |

|----------------|---------|---------|------|-------|

| 35 ohms        | 0       | 6.2     | ohms | 1, 2  |

| 50 ohms        | 0       | 8.8     | ohms | 1, 2  |

Notes:

- 1) Mismatch is the absolute value between pull-up and pull-down impedances. Both are measured at the same temperature and voltage.

- 2) Test conditions:  $V_{CCQ} = V_{CCQ}$  (MIN),  $V_{OUT} = V_{CCQ} \times 0.5$ ,  $T_{OPER}$ .

#### Table 15: Pull-Up and Pull-Down Output Impedance Mismatch With ZQ calibration for NV-DDR3

| Drive Strength | Minimum | Maximum | Unit | Notes |

|----------------|---------|---------|------|-------|

| 35 ohms        | 0       | 5.25    | ohms | 1, 2  |

| 50 ohms        | 0       | 7.5     | ohms | 1, 2  |

Notes:

- 1) Mismatch is the absolute value between pull-up and pull-down impedances. Both are measured at the same temperature and voltage.

- 2) Test conditions:  $V_{CCQ} = V_{CCQ}$  (MIN),  $V_{OUT} = V_{CCQ} \times 0.5$ ,  $T_{OPER}$ .

DATASHEET

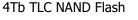

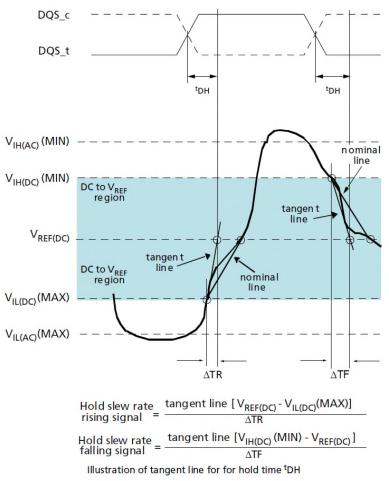

#### 9 AC overshoot/undershoot specifications

The supported AC overshoot and undershoot area depends on the timing mode selected by the host. NAND devices may have different maximum amplitude requirements for overshoot and undershoot than the host controller. If the host controller has more stringent requirements, termination or other means of reducing overshoot or undershoot may be required beyond the NAND requirements.

| Table 16: Asynchronous Over | rshoot/Undershoot Parameters |

|-----------------------------|------------------------------|

|-----------------------------|------------------------------|

|                                                     |   | Timing Mode |   |   |   |   |      |

|-----------------------------------------------------|---|-------------|---|---|---|---|------|

| Parameter                                           | 0 | 1           | 2 | 3 | 4 | 5 | Unit |

| Maximum peak amplitude provided for overshoot area  | 1 | 1           | 1 | 1 | 1 | 1 | V    |

| Maximum peak amplitude provided for undershoot area | 1 | 1           | 1 | 1 | 1 | 1 | V    |

| Maximum overshoot area above V <sub>CCQ</sub>       | 3 | 3           | 3 | 3 | 3 | 3 | V-ns |

| Maximum undershoot area below V <sub>SSQ</sub>      | 3 | 3           | 3 | 3 | 3 | 3 | V-ns |

#### Table 17: NV-DDR2 Overshoot/Undershoot Parameters

|                                                     |                   |   | Timing Mode |      |     |     |     |     |      |      |

|-----------------------------------------------------|-------------------|---|-------------|------|-----|-----|-----|-----|------|------|

| Parameter                                           | Signals           | 0 | 1           | 2    | 3   | 4   | 5   | 6   | 7    | Unit |

| Maximum peak amplitude provided for overshoot area  | -                 | 1 | 1           | 1    | 1   | 1   | 1   | 1   | 1    | V    |

| Maximum peak amplitude provided for undershoot area | -                 | 1 | 1           | 1    | 1   | 1   | 1   | 1   | 1    | V    |

| Maximum overshoot area                              | DQ[7:0], DQS, RE# | 3 | 3           | 2.25 | 1.8 | 1.5 | 1.1 | 0.9 | 0.75 | V-ns |

| above Vccq                                          | ALE, CLE, WE#     | 3 | 3           | 3    | 3   | 3   | 3   | 3   | 3    |      |

| Maximum undershoot area                             | DQ[7:0], DQS, RE# | 3 | 3           | 2.25 | 1.8 | 1.5 | 1.1 | 0.9 | 0.75 | V-ns |

| below V <sub>SSQ</sub>                              | ALE, CLE, WE#     | 3 | 3           | 3    | 3   | 3   | 3   | 3   | 3    |      |

#### Table 18: NV-DDR3 Overshoot/Undershoot Parameters

|                                                           |                      |     |     |      |     | Tir | ning | Mode |      |      |      |      |      |

|-----------------------------------------------------------|----------------------|-----|-----|------|-----|-----|------|------|------|------|------|------|------|

| Parameter                                                 | Signals              | 0   | 1   | 2    | 3   | 4   | 5    | 6    | 7    | 8    | 9    | 10   | Unit |

| Maximum peak<br>amplitude provided<br>for overshoot area  | -                    | 0.8 | 0.8 | 0.8  | 0.8 | 0.8 | 0.8  | 0.8  | 0.8  | 0.8  | 0.8  | 0.8  | V    |

| Maximum peak<br>amplitude provided<br>for undershoot area | -                    | 0.8 | 0.8 | 0.8  | 0.8 | 0.8 | 0.8  | 0.8  | 0.8  | 0.8  | 0.8  | 0.8  | V    |

| Maximum overshoot<br>area above V <sub>CCQ</sub>          | DQ[7:0],<br>DQS, RE# | 3   | 3   | 2.25 | 1.8 | 1.5 | 1.1  | 0.9  | 0.75 | 0.56 | 0.45 | 0.38 | V-ns |

|                                                           | ALE, CLE,<br>WE#     | 3   | 3   | 3    | 3   | 3   | 3    | 3    | 3    | 3    | 3    | 3    |      |

| Maximum undershoot<br>area below V <sub>SSQ</sub>         | DQ[7:0],<br>DQS, RE# | 3   | 3   | 2.25 | 1.8 | 1.5 | 1.1  | 0.9  | 0.75 | 0.56 | 0.45 | 0.38 | V-ns |

|                                                           | ALE, CLE,<br>WE#     | 3   | 3   | 3    | 3   | 3   | 3    | 3    | 3    | 3    | 3    | 3    |      |

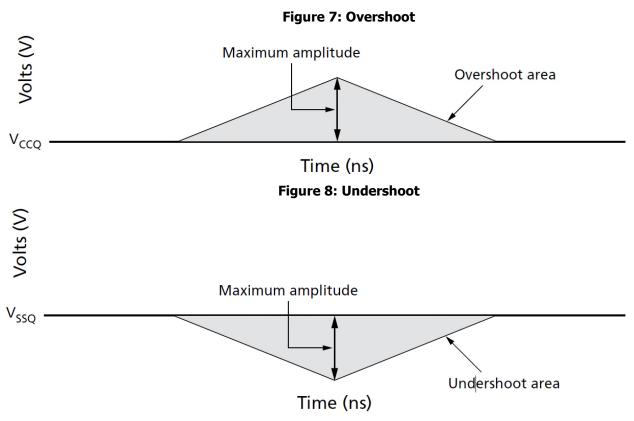

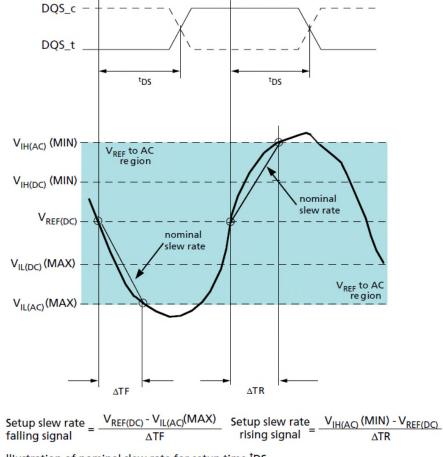

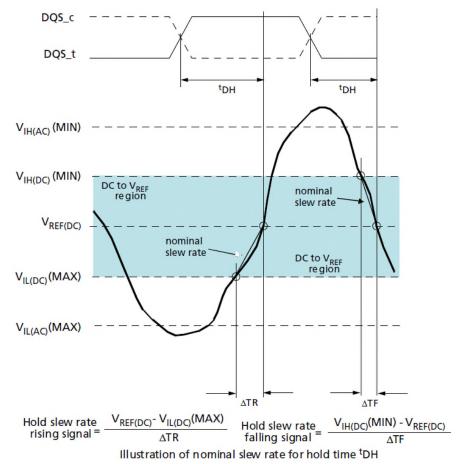

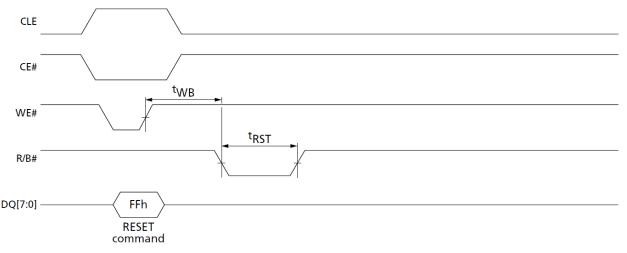

#### 10 Input slew rate

Though all AC timing parameters are tested with a nominal input slew rate of 1 V/ns, it is possible to run the device at a slower slew rate. The input slew rates shown below are sampled, and not 100% tested. When using slew rates slower than the minimum values, timing must be derated by the host.

| Parameter                 | Value                                                                                                                |

|---------------------------|----------------------------------------------------------------------------------------------------------------------|

| Rising edge for<br>setups | The last crossing of $V_{\text{REFQ(DC)}}$ and the first crossing of $V_{\text{IH(AC)}}$ min for NV-DDR2 and NV-DDR3 |

| Falling edge for setups   | The last crossing of $V_{\text{REFQ(DC)}}$ and the first crossing of $V_{\text{IL(AC)}}$ max for NV-DDR2 and NV-DDR3 |

| Rising edge for holds     | The first crossing of $V_{\rm IL(AC)}$ max and the first crossing of $V_{\rm REFQ(DC)}$ for NV-DDR2 and NV-DDR3      |

| Falling edge for<br>holds | The first crossing of $V_{\rm IH(AC)}$ min and the first crossing of $V_{\rm REFQ(DC)}$ for NV-DDR2 and NV-DDR3      |

| Temperature range         | T <sub>A</sub>                                                                                                       |

Table 19: Test Conditions for Input Slew Rate

The minimum and maximum input slew rate requirements that the device shall comply with below for NV-DDR2 and NV-DDR3 operations. If the input slew rate falls below the minimum value, then derating shall be applied.

## 4Tb TLC NAND Flash UT81NDQ512G8T

|                       |              | •            |      |

|-----------------------|--------------|--------------|------|

| Description           | Single Ended | Differential | Unit |

| Input slew rate (min) | 1.0          | 2.0          | V/ns |

| Input slew rate (max) | 4.5          | 9.0          | V/ns |

#### Table 20: NV-DDR2/NV-DDR3 Maximum and Minimum Input Slew Rate