## DESIGN OF A GIGABIT OPTICAL NETWORK INTERFACE CARD

## AND

## LAYOUT METHODOLOGY FOR HIGH-VOLTAGE DRIVERS IN LARGE ARRAYS FOR MODULATORS AND MEMS DEVICES

by

Premanand Chandramani

A dissertation submitted to the Faculty of the University of Delaware in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Engineering

Spring 2004

Copyright 2004 Premanand Chandramani All Rights Reserved

| Report Documentation Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                           |                              | Form Approved<br>OMB No. 0704-0188           |                                    |                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------|----------------------------------------------|------------------------------------|-----------------------------------------------------------------|

| Public reporting burden for the collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington Headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington VA 22202-4302. Respondents should be aware that notwithstanding any other provision of law, no person shall be subject to a penalty for failing to comply with a collection of information if it does not display a currently valid OMB control number. |                                           |                              |                                              |                                    | is collection of information,<br>Highway, Suite 1204, Arlington |

| 1. REPORT DATE         2. REPORT TYPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |                              | 3. DATES COVERED<br>00-00-2004 to 00-00-2004 |                                    |                                                                 |

| 4. TITLE AND SUBTITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |                              |                                              | 5a. CONTRACT NUMBER                |                                                                 |

| 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | it Optical Network<br>Jigh-Voltage Driver |                              | -                                            | 5b. GRANT NUMBER                   |                                                                 |

| Methodology For High-Voltage Drivers In Large Arrays For Modulators<br>And Mems Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                           |                              |                                              | 5c. PROGRAM ELEMENT NUMBER         |                                                                 |

| 6. AUTHOR(S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |                              | 5d. PROJECT NUMBER                           |                                    |                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                           |                              | 5e. TASK NUMBER                              |                                    |                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                           |                              | 5f. WORK UNIT NUMBER                         |                                    |                                                                 |

| 7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES)<br>University of Delaware,210 South College Avenue,Newark,DE,19716                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |                              | 8. PERFORMING ORGANIZATION<br>REPORT NUMBER  |                                    |                                                                 |

| 9. SPONSORING/MONITORING AGENCY NAME(S) AND ADDRESS(ES)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                           |                              | 10. SPONSOR/MONITOR'S ACRONYM(S)             |                                    |                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                           |                              | 11. SPONSOR/MONITOR'S REPORT<br>NUMBER(S)    |                                    |                                                                 |

| 12. DISTRIBUTION/AVAILABILITY STATEMENT Approved for public release; distribution unlimited                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                           |                              |                                              |                                    |                                                                 |

| 13. SUPPLEMENTARY NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13. SUPPLEMENTARY NOTES                   |                              |                                              |                                    |                                                                 |

| 14. ABSTRACT<br>See Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                           |                              |                                              |                                    |                                                                 |

| 15. SUBJECT TERMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                           |                              |                                              |                                    |                                                                 |

| 16. SECURITY CLASSIFICATION OF: 17. LIMITATION OF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                           | 17. LIMITATION OF            | 18. NUMBER<br>OF PAGES                       | 19a. NAME OF<br>RESPONSIBLE PERSON |                                                                 |

| a. REPORT<br>unclassified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | b. ABSTRACT<br>unclassified               | c. THIS PAGE<br>unclassified | Same as<br>Report (SAR)                      | 112                                | RESI ONSIDLE I EKSON                                            |

| Standard Form | 298 (Rev. 8-98)   |

|---------------|-------------------|

| Prescribed b  | y ANSI Std Z39-18 |

## DESIGN OF A GIGABIT OPTICAL NETWORK INTERFACE CARD

## AND

## LAYOUT METHODOLOGY FOR HIGH-VOLTAGE DRIVERS IN LARGE ARRAYS FOR MODULATORS AND MEMS DEVICES

by

Premanand Chandramani

Approved:

Gonzalo R. Arce, Ph.D. Chair of the Department of Department Name

Approved:

Eric W. Kaler, Ph.D. Dean of the College of Engineering

Approved:

Conrado M. Gempesaw II, Ph.D. Vice Provost for Academic Programs and Planning

|         | I certify that I have read this dissertation and that in my opinion it meets<br>the academic and professional standard required by the University as a<br>dissertation for the degree of Doctor of Philosophy. |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signed: | Fouad E. Kiamilev, Ph.D.<br>Professor in charge of dissertation                                                                                                                                                |

|         | I certify that I have read this dissertation and that in my opinion it meets<br>the academic and professional standard required by the University as a<br>dissertation for the degree of Doctor of Philosophy. |

| Signed: | Michael Haney, Ph.D.<br>Member of dissertation committee                                                                                                                                                       |

|         | I certify that I have read this dissertation and that in my opinion it meets<br>the academic and professional standard required by the University as a<br>dissertation for the degree of Doctor of Philosophy. |

| Signed: | Kenneth E. Barner, Ph.D.<br>Member of dissertation committee                                                                                                                                                   |

|         | I certify that I have read this dissertation and that in my opinion it meets<br>the academic and professional standard required by the University as a<br>dissertation for the degree of Doctor of Philosophy. |

| Signed: | Joseph E. Pellegrino, Ph.D.<br>Member of dissertation committee                                                                                                                                                |

## ACKNOWLEDGMENTS

I would like to express my sincere gratitude to my advisor, Professor Fouad E. Kiamilev, who is one of the strongest and most positive influences of my life. His motivation, support, and confidence facilitated a productive working relationship. He is the one who gave me the opportunity to accomplish the work and to guide me with what I am today.

I would like to thank Dr. Michael Haney, Dr. Kenneth E. Barner, and Dr. Joseph Pellegrino for being in my dissertation committee and for their useful discussions and suggestions in this dissertation.

In addition, I use this opportunity to acknowledge Dr. Jon Ciemiwicz and Dr. Pellegrino BAE systems as part of the DARPA STAB program for their support of the work presented in this dissertation. Also, I would like to acknowledge Dr. Allen Cox Honeywell technology Center as part of the DARPA VLSI Photonics program for the support of the work presented in this dissertation.

I would like to acknowledge my friends Jeremy Ekman, Xiaoqing Wang, and Ping Gui as colleagues, consultants and most importantly, friends who helped me keep my sanity. I would also like to acknowledge the other graduate students in our group, past and present, Dietmer Schmid, Fikri Muhammad, Mayra Sarmiento and Xingle Wang.

Lastly, I would like to thank my family for their support; it has been a long road. I am thankful to my parents, who have demonstrated to me time and again the meaning of perseverance, taught me the power of independence, and cultivated my internal strength. I am also grateful to my in-laws for their kindness and belief in my ability to accomplish this goal. I am honored and grateful to my uncle Dr.Rajaram Janardhanam, for his whole hearted support and motivation through out my educational career. I express my ultimate gratitude to my wife and my better half, Sabari Priya, who has sacrificed much for the good of our life, showed me the meaning of synergy, and held me to a higher standard from the very beginning. I would express my love and gratitude for my daughter, Subitcha for her unparalleled affection with the precious little time I spent with her during my work and twilight for me and my wife in keeping our life happy.

## DEDICATION

To my parents,

Whose endless love and support have inspired my achievements

## TABLE OF CONTENTS

| LIST | OF FIG     | 3LESix<br>URESx<br>xiv                             |

|------|------------|----------------------------------------------------|

| Chap | oter       |                                                    |

| 1    | INTRO      | DDUCTION1                                          |

|      | 1.1        | Dissertation organization                          |

| 2    | BACK       | GROUND INFORMATION AND MOTIVATION4                 |

|      | 2.1<br>2.2 | Optical Network Interface Card (ONIC)              |

| 3    | GIGA       | BIT OPTICAL NETWORK INTERFACE CARD 10              |

|      | 3.1<br>3.2 | ONIC Architecture                                  |

|      |            | <ul> <li>3.2.1 Optical data link modules</li></ul> |

|      | 3.3        | Optical Network Interface Card (ONIC) design       |

|      | 3.4        | Programming of the ONIC hardware                   |

|      | 3.5        | Test and results on the ONIC                       |

|      |            | 3.5.1 Link integrity test                          |

|      |            | 3.5.2 Message passing application                  |

|      | 3.6        | Application of ONIC                                |

|      |            | 3.6.1 Communication request protocol               |

|      |            | 3.6.2 Communication response protocol              |

|      |            | 3.6.3 Message transmission protocol                |

| 4   |       | YOUT METHODOLOGY OF HIGH-VOLTAGE DRIVER IC<br>R MODULATORS AND MEMS DEVICES |    |

|-----|-------|-----------------------------------------------------------------------------|----|

|     | 4.1   | Optical device integration to Photonic ICs                                  |    |

|     | 4.2   | Layout methodology                                                          |    |

|     | 4.3   |                                                                             |    |

|     | 4.4   |                                                                             |    |

|     | 4.5   |                                                                             |    |

|     |       | 4.5.1 High-voltage driver design                                            |    |

|     |       | 4.5.2 Architecture of the high-voltage driver IC                            |    |

|     |       | 4.5.3 Layout and fabrication of the high-voltage driver IC.                 |    |

|     | 4.6   | Testing and results                                                         |    |

| 5   | CO    | NCLUSIONS                                                                   | 75 |

|     | 5.1   | ONIC                                                                        |    |

|     |       | 5.1.1 Suggestions for future studies and improvements                       |    |

|     | 5.2   | High-voltage drivers for MEMS and modulators                                | 77 |

|     |       | 5.2.1 Adaptability and improvements                                         |    |

| App | endix |                                                                             |    |

# rhh

| А    | Electrical probe testing response for driver IC with maximum output                                         | 80 |

|------|-------------------------------------------------------------------------------------------------------------|----|

| В    | range of 50Volts<br>Electrical probe testing response for driver IC with maximum output                     |    |

| С    | range of 25Volts<br>Electrical probe testing response for driver IC with maximum output<br>range of 12Volts |    |

| BIBI | LIOGRAPHY                                                                                                   |    |

## LIST OF TABLES

| 4.1 | Design versions of the high-voltage driver                         | . 50 |

|-----|--------------------------------------------------------------------|------|

| 4.2 | List of Input/ Output and Power pads on the high-voltage driver IC | . 62 |

## LIST OF FIGURES

| 2.1  | Network architecture with 'N' compute nodes interconnected in a switch fabric through ONIC                                    |

|------|-------------------------------------------------------------------------------------------------------------------------------|

| 3.1  | Generic architecture of an Optical Network Interface Card<br>(ONIC)                                                           |

| 3.2  | Architecture of Optical Network Interface Board (ONIB) 12                                                                     |

| 3.3  | Picture of the fabricated Optical Network Interface Board                                                                     |

| 3.4  | Twelve Channel Optical Data link modules14                                                                                    |

| 3.5  | ONIB to ONIB Interface demonstrator system using the 12-<br>channel optical data link                                         |

| 3.6  | Oscilloscope snapshot of one of the channels transmitting data at 1Gbps data rates                                            |

| 3.7  | Schematic view of the components in the Optical Network<br>Interface Card (ONIC)                                              |

| 3.8  | Prototype Optical Network Interface Card (ONIC) hardware with the whole card assembled                                        |

| 3.9  | Snapshot of the 500hm impedance matched transmission lines<br>from the SERDES to the parallel optical link modules            |

| 3.10 | Design flow steps for the FPGA on the ONIC hardware                                                                           |

| 3.11 | Steps involved in the link integrity test on the ONIC                                                                         |

| 3.12 | Scope snapshot of the data through one of the high-speed channels at 1Gbps                                                    |

| 3.13 | Message passing application running between two servers with<br>ONIC hardware connected through a parallel optical fiber link |

| 3.14 | Steps involved in the message passing application test                                                                                                                                                                                                                                             | 29 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

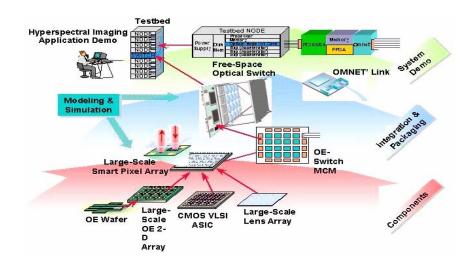

| 3.15 | VIVACE System concept                                                                                                                                                                                                                                                                              | 31 |

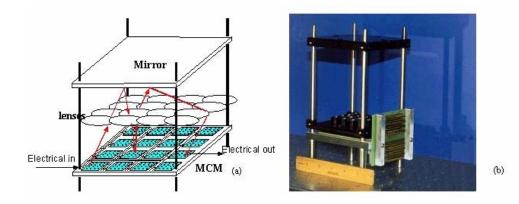

| 3.16 | FastNet switch assembly. (a) Shows the Free Space Optical<br>Interconnect (FSOI) switch concept, (b) Prototype FastNet FSOI<br>switch assembly                                                                                                                                                     | 31 |

| 3.17 | Schematic view of the VIVACE Protocol with communication from one compute node to another through the FSOI switch fabric                                                                                                                                                                           | 32 |

| 3.18 | Function implemented on the FPGA of the ONIC                                                                                                                                                                                                                                                       | 34 |

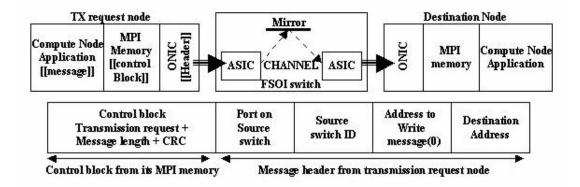

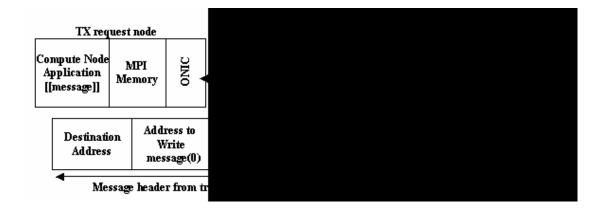

| 3.19 | Communication request from Transmission request node to the destination node through the ONIC and FSOI switch                                                                                                                                                                                      | 35 |

| 3.20 | Communication response from the destination node to the transmission request node through the ONIC and FSOI switch                                                                                                                                                                                 | 36 |

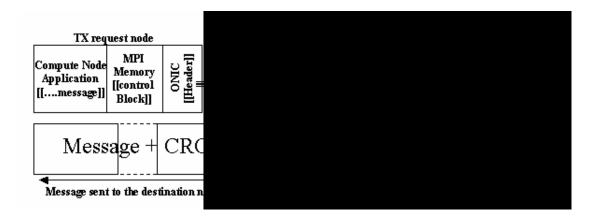

| 3.21 | Message transmission protocol where the Transmission request<br>node send the message to the destination node                                                                                                                                                                                      | 37 |

| 4.1  | Steps involved in integration of VLSI IC with optoelectronic devices                                                                                                                                                                                                                               | 40 |

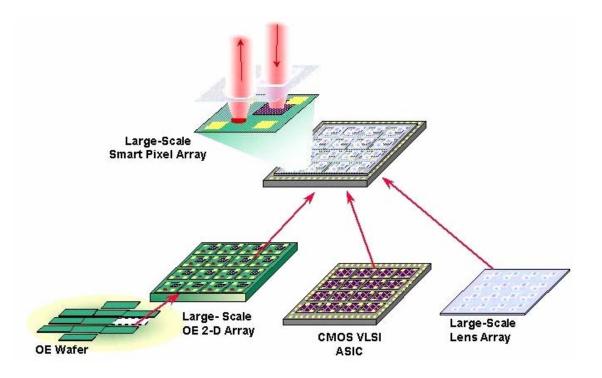

| 4.2  | Flip-chip integration process, where the optoelectronic devices<br>are fabricated separately and then flip-chip attached on top of<br>VLSI IC with driver, receivers and processing logic                                                                                                          | 41 |

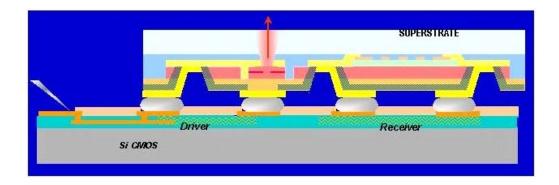

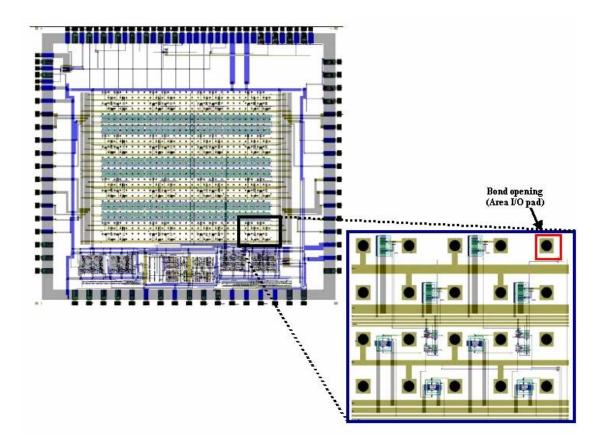

| 4.3  | Example of a smart-pixel layout style where two types of circuit<br>are replicated in a two-dimensional array is shown. The layout<br>implements a 4 x 4 array of cluster with eight smart-pixels in each<br>cluster. The optoelectronic devices were attached by flip-chip<br>integration process | 43 |

| 4.4  | CMOS scanner chip designed for it to be flip-chip attached with 768 MQW modulators                                                                                                                                                                                                                 | 44 |

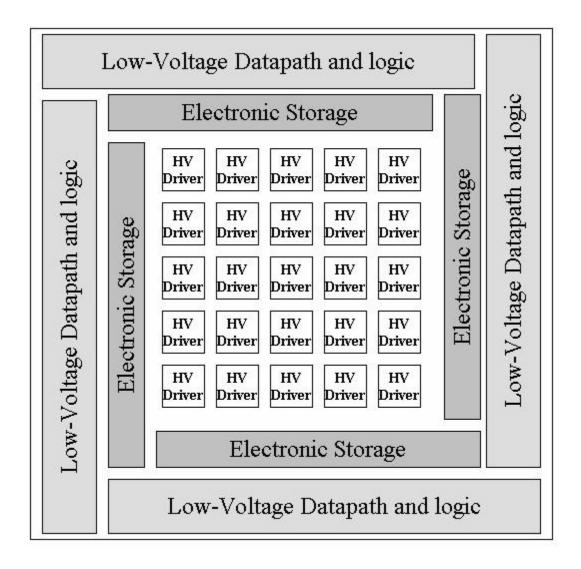

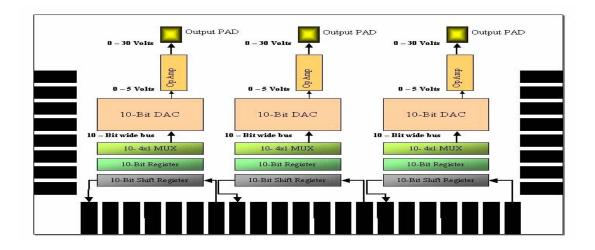

| 4.5  | Layout Methodology for high-voltage drivers to drive MEMS and SLM devices                                                                                                                                                                                                                          | 46 |

| 4.6  | High-voltage CMOS driver IC and its functional blocks                                                                                                                                                                                                                                              | 47 |

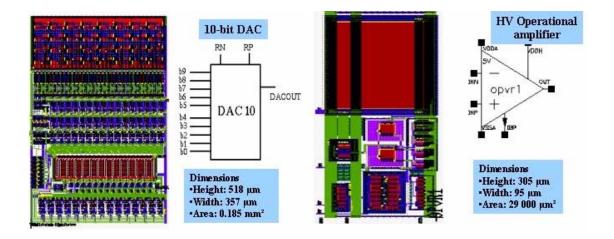

| 4.7  | Layout of the DAC and the operational amplifier from the standard cell library                                                                                                                                                                           | 48 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

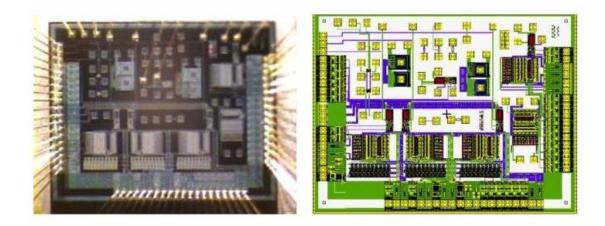

| 4.8  | Picture of the fabricated high-voltage test chip is on the left of the figure. The layout of the IC is shown on the right of the figure                                                                                                                  | 49 |

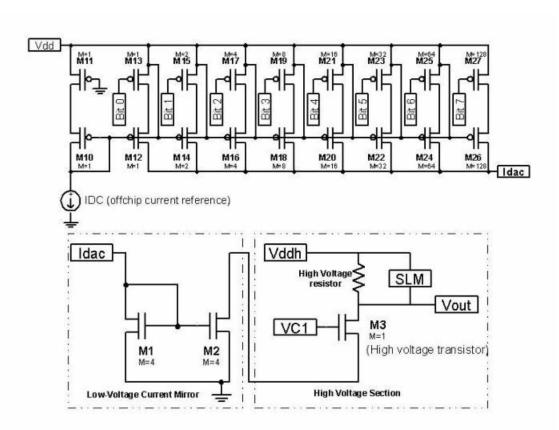

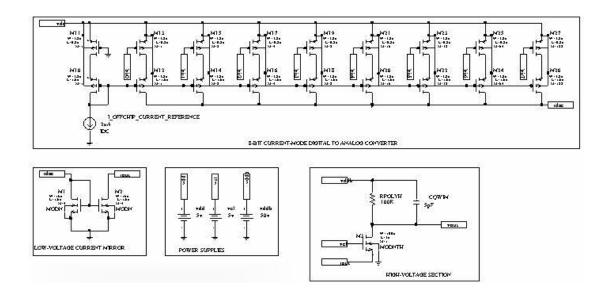

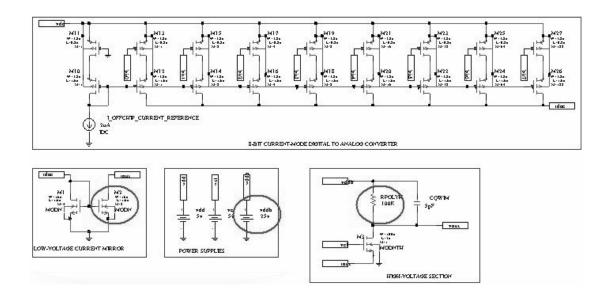

| 4.9  | Generic Schematic of the high-voltage driver circuit. The 8-bit<br>current DAC with off-chip reference current and the low-voltage<br>current mirror followed by the high voltage section                                                                | 50 |

| 4.10 | Schematic of the 50Volts driver                                                                                                                                                                                                                          | 52 |

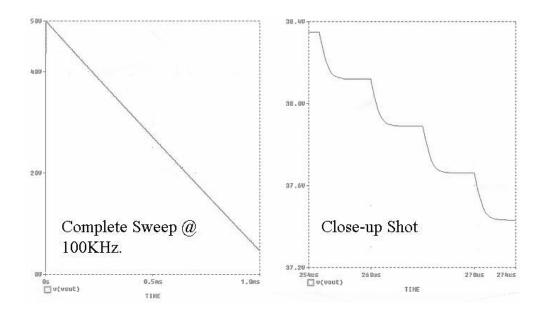

| 4.11 | Simulation results of the 50Volts driver. The trace on the left is<br>the complete sweep of the driver from 0Volts to 50Volts at 100<br>KHz. The simulation results on the right are the voltage step size<br>with the change in the digital input sweep | 52 |

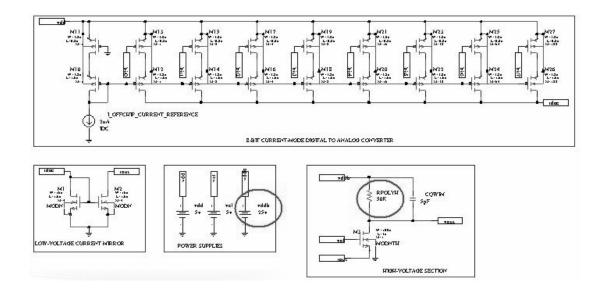

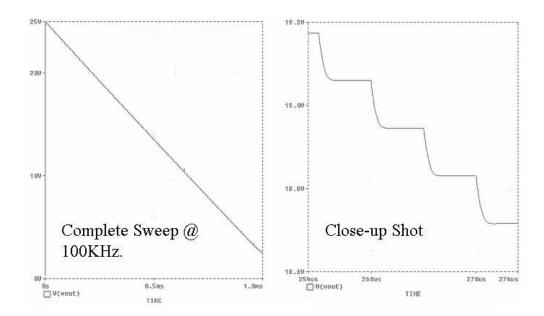

| 4.12 | Schematic of the 25Volts driver with speed up to 250 KHz                                                                                                                                                                                                 | 53 |

| 4.13 | Simulation results of the 25Volts driver. The trace on the left is<br>the complete sweep of the driver from 0Volts to 25Volts at 100<br>KHz. The trace on the right is the voltage step size with the<br>change in the digital input sweep               | 53 |

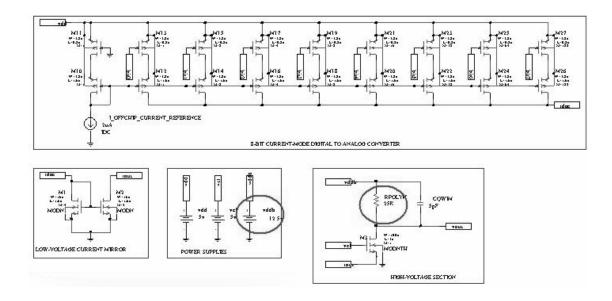

| 4.14 | Schematic of the 25Volts driver with speed up to 125 KHz                                                                                                                                                                                                 | 54 |

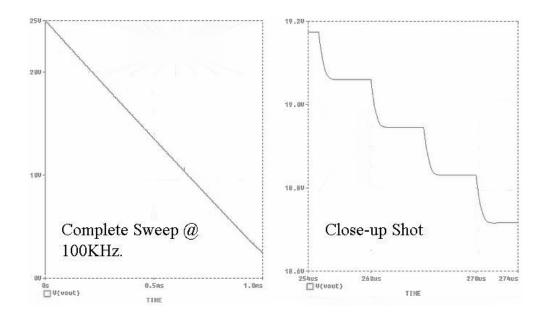

| 4.15 | Simulation results of the 25Volts driver circuit are shown. The trace on the left is the complete sweep of the driver from 0Volts to 25Volts at 100 KHz. The trace on the right is the voltage step size with the change in the digital input sweep      | 54 |

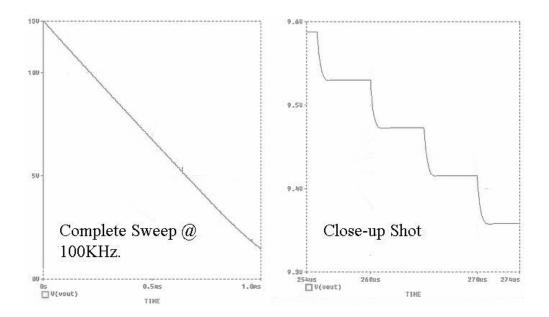

| 4.16 | Schematic of the 12Volts driver with speed up to125KHz                                                                                                                                                                                                   | 55 |

| 4.17 | Simulation results of the 12Volts driver circuit are shown. The trace on the left is the complete sweep of the driver from 0Volts to 12Volts at 100 KHz. The trace on the right is the voltage step size with the change in the digital input sweep      | 56 |

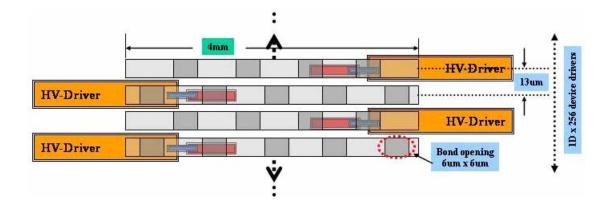

| 4.18 | Layout of the high-voltage drivers with staggered placement<br>under the top layer metal with 6µm x 6µm bond opening at<br>regular intervals. The drivers are driven from left and right<br>alternating                                                  | 58 |

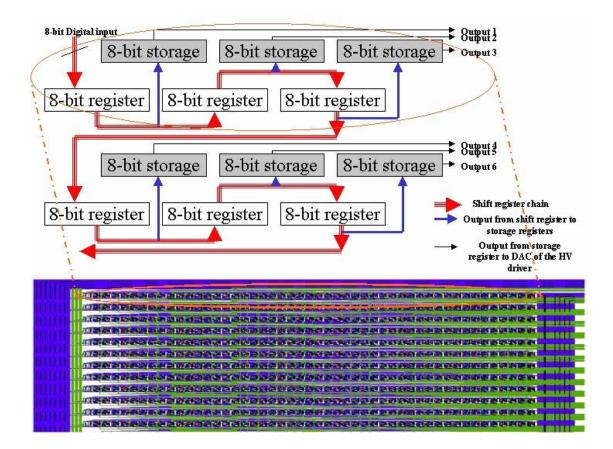

| 4.19 | Layout scheme for the shift register chain and the storage registers                                                                                                                                                                                                                                                                                             | 9 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

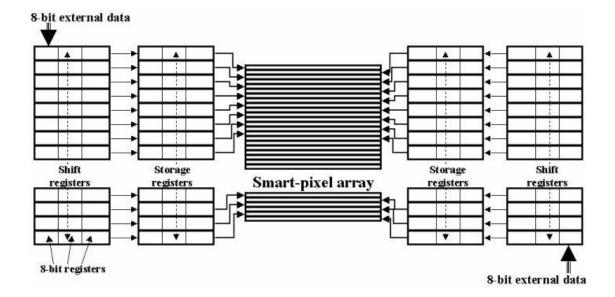

| 4.20 | Architecture of the driver ASIC is shown with the smart-pixel array in the center. The storage and shift registers are on either side of the smart-pixel array                                                                                                                                                                                                   | 0 |

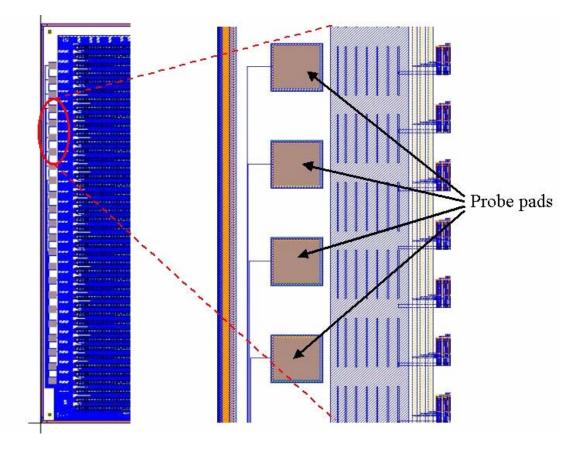

| 4.21 | Probe pads on the edge of the IC to electrically probe the driver<br>output using a probe card mounted on a probe station                                                                                                                                                                                                                                        | 1 |

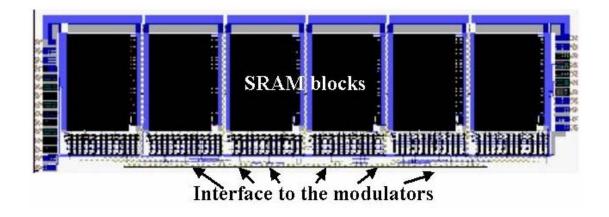

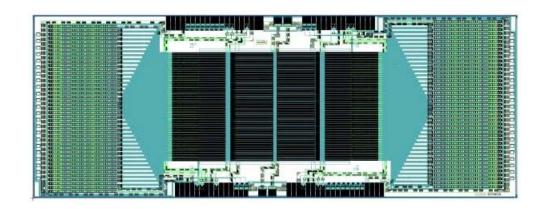

| 4.22 | Layout snapshot of the high-voltage driver IC with a 1-D array of 256 drivers                                                                                                                                                                                                                                                                                    | 7 |

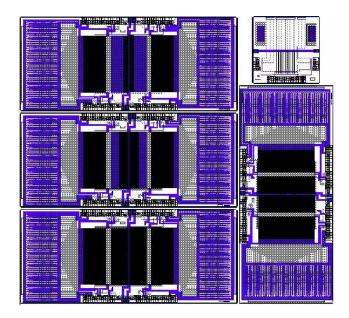

| 4.23 | Wafer reticle with four versions of the driver IC and a test chip                                                                                                                                                                                                                                                                                                | 9 |

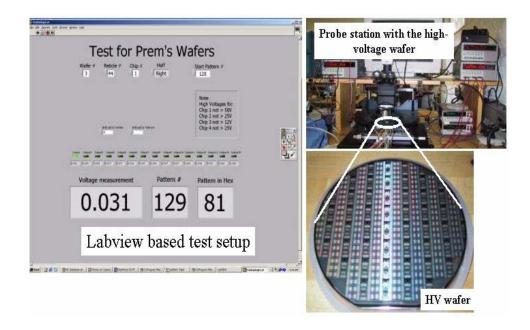

| 4.24 | Picture of the fabricated driver ICs at wafer level                                                                                                                                                                                                                                                                                                              | 9 |

| 4.25 | Semi-automated test setup to test the driver IC electrically with<br>the wafer mounted on a probe station. A probe card mounted on<br>the probe station probes the wafer. On the left of the figure is the<br>test panel interface written using Labview software to define the<br>various test parameters and to monitor the response from the<br>wafer probing | 1 |

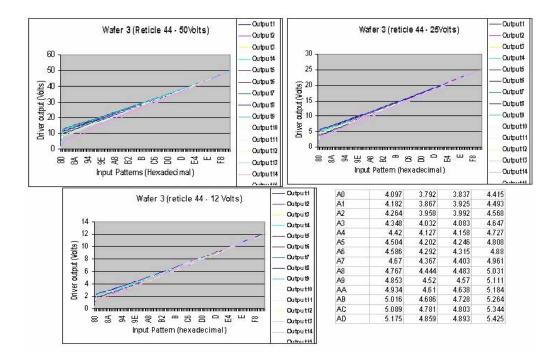

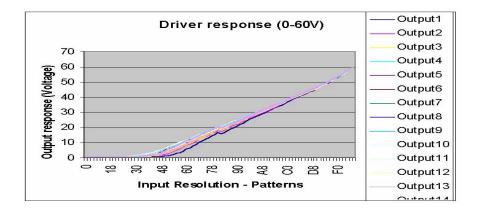

| 4.26 | Electrical probe testing results of reticle 44 in one of the wafers<br>marked 3. Shown are the drivers operating at 50Volts, 25Volts<br>and 12Volts. Also an inset shows the test pattern input and<br>responses from four of the drivers                                                                                                                        | 3 |

| 4.27 | Electrical stress testing of the wafer at 20% more than the maximum rated voltage range of the fabrication process                                                                                                                                                                                                                                               | 3 |

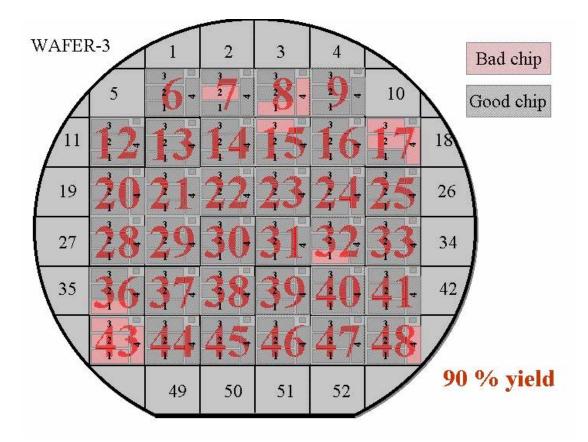

| 4.28 | Test results of the whole wafer yield after electrically tested using the semi-automated test process                                                                                                                                                                                                                                                            | 4 |

## ABSTRACT

High-speed optical data links enable local area networks (LANs) that operate at data rates above 10Gbps. Various networks, protocol and switch architectures have been proposed that use these links. The optical network interface card (ONIC) is an important component for demonstrating efficient application of these architectures. In this paper, we describe the design of a programmable ONIC that interfaces a 12-channel gigabit parallel optical link module with a 64-bit/66-MHz PCI computer bus. Hardware programmability (using FPGAs) enables the ONIC to efficiently implement different communication protocols. For hardware testing, the ONIC hardware was programmed for bit error rate (BER) analysis. In continuous operation at 8Gbps for 30 days through a 1-meter fiber, no errors occurred. For application testing, a custom ONIC software driver was developed. We used this driver to demonstrate message passing between applications running on two ONICequipped servers. The ONIC design provides a low-cost solution that can be readily adapted for application and device specific requirements. The use of ONIC in a freespace optical switch system is described in the dissertation.

A layout methodology for high-voltage smart-pixel ICs that can integrate, high-voltage circuits and low-voltage high-density VLSI circuits with a one dimensional/two dimensional array of modulators and MEMS devices. This layout methodology is compatible with the existing CAD tools enabling the automation of placement and routing tasks. This layout methodology was applied to a high-voltage driver IC with 256 individual high-voltage driver cells to drive a one-dimensional array of 256 Spatial Light Modulator devices. The IC was designed and fabricated using AMS 0.8um high-voltage CXZ process in a wafer run and has about 210,000 transistors. This IC has been designed to be flip-chip integrated with GaAs Multiple-Quantum-Well SLM devices. This high-voltage driver IC has the largest numbers of high-voltage drivers integrated on to a single VLSI IC compared to any commercially available driver ICs. For testing the driver performance and process variance across the array in each ASIC, the output of every eighth driver in the array was brought out to a bond pad. Also present in this dissertation is the test strategy used to test these ICs electrically at wafer level.

### Chapter 1

### INTRODUCTION

The use of photons to move information is making rapid strides in terms of research and development and is looked upon as the future technology of the communication world. On a networking level the undisputed trend is higher speed. The increased use of fiber optic links to get that extra speed supports that trend. High-Speed digital chips with low power consumption continue to flow out of semiconductor industry and the optical component industry has matched them with optoelectronic devices with improved performance.

Popular communication networking systems such as Wide Area Networks (WAN), Local Area Network (LAN) [1], Personal Area Network (PAN) [2], and Storage Area Network (SAN) has a unique place in market today. Of these the LAN and SAN have a brighter spot in networking. These networks interconnect large disk arrays to servers and other systems through gigabit optical data links. High-Speed optical data links enable LAN that operates at data rates above 10Gbps. In SAN the speed has been increased up to 2.125Gbps.

On the other hand the research community is coming up with new networks, protocols and switch architectures for computational intensive application that have wide range of commercial and defense related interests. The Optical Network Interface Cards (ONIC) are the gateways of communication between compute nodes in such a network for efficient demonstration of their applications. More and more optical communication modules, with varying speed and bandwidth are available commercially. With the architectures and their applications changing, a generic architecture of the ONIC is needed for future researchers. The generic architecture of the ONIC and how future designers can readily adapt it is the first subject of this dissertation.

On the other front optoelectronic devices such as modulators and Micro Electro Mechanical Systems (MEMS) find immense use in both commercial and defense related applications. Designing and fabricating these devices in large arrays with tight pitch is possible now and the Complementary Metal Oxide Semiconductor (CMOS) Integrated Circuits (IC) to drive these devices must be able to match these advancements. A well-defined and tested CMOS IC layout methodology needs to be in place to do this. The CMOS design approach becomes more stringent when the optoelectronic devices need higher operating voltage ranges. A lot of high-voltage driver IC is available commercially. However, they don't have large number of drivers and they cannot be adapted for applications where the optoelectronic devices needed to be attached on top of active silicon. So, a custom CMOS solution that can be readily adapted and modified to suit the optoelectronic device array and application needs to be designed. This included the driver circuitry for the devices and the processing logic operating at a much lower voltage. A layout methodology needs to be defined to partition the IC with the high-voltage cells and low-voltage cells isolated and optimized separately on the same IC.

The second subject of this dissertation is the proposed layout methodology for such a high-voltage driver IC. Also, it describes the design methodology applied to a high-voltage CMOS driver IC that can drive up to 50Volts to drive modulators. This procedure has been developed as the result of designing custom ICs whose size range from a few thousand transistors to 220,000 transistors and their functions range from driver/receiver chips to high-speed scanner IC with 768 modulators and 85Kbits of Random Access Memory (RAM). They make use of custom cells and standard cells from the vendor libraries. This layout methodology includes partitioning of the design at the voltage level and integrating mixed-signal analog and digital circuits.

#### **1.1 Dissertation Organization**

Chapter 2 provides some background information on ONIC design methodology and high-voltage driver IC layout methodology to provide some context and help the reader understand the motivation behind the designs.

Chapter 3 covers the ONIC design methodology and design implementation targeting a certain application and the results.

Chapter 4 covers the layout methodology of the high-voltage driver IC and its implementation on to a driver IC targeting a certain application. It also explains the test setup and the results from the design implementation.

The conclusions of applying the ONIC architecture and high-voltage driver layout methodology to designs and what future designers can do to improve are discussed in chapter 5.

## Chapter 2

## **BACKGROUND INFORMATION AND MOTIVATION**

## 2.1 Optical Network Interface Card (ONIC)

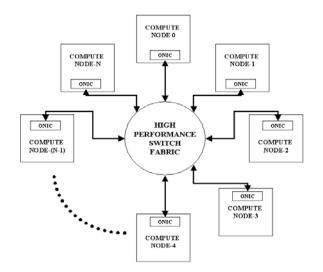

Various very short-reach (VSR) optical data links that operate at data rates of 10Gb/s (Gigabits per second) and beyond are now becoming available as commercial products [3], [4], [5]. Various network, protocol and switch architectures that utilize these links have been proposed [6], [7], [8]. Example network architecture is shown in Figure 2.1.

Figure 2.1 Network architecture with 'N' compute nodes interconnected in a switch fabric through ONIC

It uses VSR optical data links to interconnect multiple compute nodes through a central switch. In order to efficiently utilize the increased bandwidth capability of VSR optical data links, these network architectures use new communication protocols rather than relying on legacy based such as ATM, Ethernet, or HIPPI [9], [10], and [11]. The ONIC is an important instrument for demonstrating efficient application of these new architectures. The purpose of the ONIC is to interface a standard computing node, such as a workstation or an embedded processor, with a VSR optical data link. On the hardware front, the ONIC converts slow, wideparallel and clock-synchronous data streams (typically used in chip-level computer interconnection) to narrow gigabit-speed data streams with embedded clock information (typically used in VSR optical data links). The ONIC hardware often contains First-In First-Out (FIFO) memory storage to buffer incoming and outgoing network data for flow control. On the software front, the ONIC includes software drivers to provide communication and flow control between the hardware, application running on the computing node and the custom network protocol used by the network that is being demonstrated.

This dissertation work describes the design of a programmable ONIC that interfaces a 12-channel, gigabit parallel optical link module [12] and [13] with a 64bit/66-MHz Peripheral Component Interface (PCI) bus [14]. The adoption of PCI bus allows our ONIC design to be used in widely available PCI-based workstation and server computers. Hardware programmability is achieved using Field Programmable Gate Array (FPGA) integrated circuits. This enables our ONIC design to efficiently implement different network protocols. Although the current ONIC design uses a specific VSR optical data link hardware, it can be readily modified to support other types of optical data links. The ONIC design was originally developed to demonstrate a specific network architecture that used free-space optical interconnection inside the switch fabric [6]. However, the novelty of the design is that it provides a low-cost network interface solution that can be readily modified by other researchers for network protocol and optical device specific requirements. The following paragraphs compare the ONIC approach described in this dissertation with existing ONIC implementations and provide justification for the approach followed.

Commercially available ONICs use custom integrated circuits and/or network processor chips to implement specific network protocols [15] and [16]. They cannot keep up with the 10-100 Gigabit data rates available with VSR optical data links. Finally, commercial ONICs use proprietary designs and cannot be modified to use new VSR optical link hardware. These attributes make commercial ONICs unusable for experimenting with new network architectures and VSR optical data links. On the other hand, a ONIC has been previously demonstrated that used custommade integrated circuits to implement a specific network protocol [17]. While this approach successfully demonstrated the new network protocol proposed by its authors, it is difficult to modify this design because of the high cost and extensive knowledge required for the design of custom integrated circuits.

References [7] and [18] describe a network architecture demonstration that used a ONIC design similar to the one being proposed in this dissertation. This ONIC design also used FPGAs and Serializer De-Serializer chips (SERDES) that can be reconfigured to support various network protocols. However, it employed a proprietary memory-bus interface to connect the optical link with the computing node. While a memory bus interface permits higher bandwidth communication between the processor and the optical link, our PCI-based ONIC supports a broad range of computing hardware from a multitude of computer manufacturers. Future modifications of the ONIC design can use the emerging PCI bus extensions to achieve higher communication bandwidth than that possible with existing 64-bit/66-MHz PCI standard [19]. Finally, more work was done at the software driver level to demonstrate application-level message passing between computing nodes interconnected using ONICs.

#### 2.2 High-Voltage Driver for Optoelectronic Devices

Recent advancements in research and development of Spatial Light Modulators (SLM) and Micro Electro Mechanical Systems (MEMS) devices find use in various applications such as optical correlators for optical processing, optical beam steering for avionic counter measures and input/output devices for memory systems [20] and [21]. The application requirements and technological advancements have enabled the devices to be designed and fabricated in large one-dimensional/twodimensional arrays with increasingly shorter pitch between them. These requirements have pushed for very compact driver solution but with high-voltage drive capability. Commercially available high-voltage driver ICs only has a limited number of drivers in them and multitudes of these devices have to be used when driving huge arrays of Modulators and MEMS devices. Custom Complimentary Metal Oxide Semiconductor (CMOS) Very Large Scale Integrated (VLSI) circuit design is best suited for large arrays and compact solution.

Application demands for compact solution with little or no electrical parasitics or losses poses a challenge in using commercially available driver ICs. Also when the device array is large trying to drive them externally almost becomes impossible with the number of electrical Input and Output (I/O) pads needed. On the other hand hybridization of the optical device on top of the active silicon helps in achieving optical device arrays in tighter pitch, larger array size and with less interconnects capacitances.

Technological advancements have enabled hybrid integration of VLSI ICs with two-dimensional arrays of Multiple Quantum Well (MQW) based Modulators, Photodetectors, Vertical Cavity Surface Emitting LASER (VCSEL), SLMs and MEMS devices [22] and [23]. These advancements will enable to integrate VLSI Integrated Circuits (IC) with millions of transistors and thousands of optical Input/Output operating at high-speed for various computing and switching applications. The important aspect in integrate of the VLSI IC with millions of transistors with optoelectronic and MEMS devices is the efficient method of VLSI circuit layout methodology. The ability to integrate optoelectronic device arrays with optimized, high-density VLSI layout of RAMS and datapaths has been demonstrated by an efficient layout methodology. The optoelectronic devices used in these systems were low-voltage devices and so was possible to design VLSI circuits in deep submicron processes. With the above mentioned constraints a CMOS process technology that can support high voltage ranges and also smaller feature size needs to be chosen.

An efficient layout methodology is proposed in this dissertation to design and layout high-voltage drivers and the supporting digital logic. This needs to be done in a way so as to have both the high-voltage cells and low-voltage cells on the IC and still be able to partition and place them without breaking any design rules or cause fatalities to the driver IC. The proposed driver IC layout is explained in chapter 4. To verify the proposed layout methodology the design was implemented on a 1D array of 256 high-voltage drivers to be flip-chip bonded with a 1D array of 256 modulators. The IC integrated with the modulators will be used to steer Infra-Red (IR) beams for avionic countermeasures applications. The IC was fabricated in a wafer run using Austria Micro Systems (AMS) high-voltage CXZ process [24] and probe tested electrically.

## Chapter 3

## **GIGABIT OPTICAL NETWORK INTERFACE CARD**

The Optical Network Interface Card is an important instrument in demonstrating efficient application of architectures where high-speed optical datalinks at data rates above 10Gbps are necessary. The purpose of the ONIC is to interface a standard computing node, such as a workstation or an embedded processor, with a VSR optical data link. On the hardware front, the ONIC converts slow, wide parallel and clock-synchronous data streams (typically used in chip-level computer interconnects) to narrow gigabit-speed data streams with embedded clock information (typically used in VSR optical data links). The ONIC hardware often contains First-In First-Out (FIFO) memory storage to buffer incoming and outgoing network data for flow control. On the software front, the ONIC includes software drivers to provide communication and flow control between the hardware, application running on the computing node and the custom network protocol used by the network that is being demonstrated.

### 3.1 ONIC Architecture

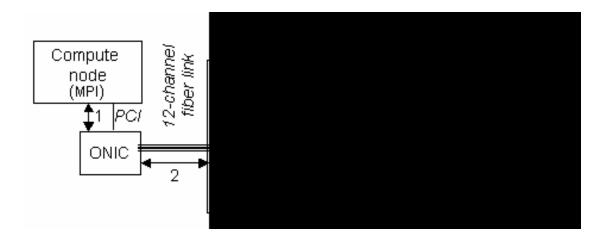

The architecture of the ONIC was developed in two phases. The first phase was to design prototype hardware with no compute node interface and highspeed electrical network interface. This evaluation prototype hardware was called Optical Network Interface Board (ONIB). The second phase was to design prototype hardware with the compute node interface and all optical network interfaces. A generic architecture as the base for any ONIC design was developed to suit application requirements. The ONIC architecture developed at University of Delaware is shown in Figure 3.1. It is a PCI based Network Interface Card (NIC). It has a high-end reconfigurable chip such as an FPGA that is programmed with the network protocols. The network interface of the ONIC is through an N-channel gigabit parallel optical link modules to transmit and receive data. The FPGA sends and receives the parallel data from the compute server to the optical modules through a set of SERDES. The SERDES converts the parallel data to high-speed. Serial data suitable for the optical module and recover the data and clock from the optical receive module.

Figure 3.1 Generic Architecture of an Optical Network Interface Card (ONIC)

### **3.2** Optical Network Interface Board (ONIB)

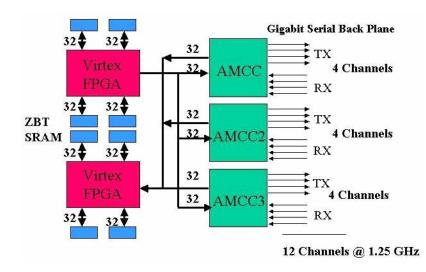

The ONIB was designed to develop and test the protocols to be performed in the application. This was based on the generic architecture of an Optical NIC. However, the ONIB does not interface with any compute nodes. It has a high-speed electrical interface. The architecture of the ONIB is shown in Figure 3.2. It has two Xilinx VIRTEX XCV1000 FPGAs. Each FPGA has 1 million system gates. One FPGA is to generate and transmit data. The second FPGA is to receive and process the received data. Each FPGA has two banks of Zero Bus Turnaround (ZBT) SRAM and the total memory capacity of the four banks combined is 8Mb (256k x 32bits). These SRAM are for buffering the transmit data and received data. The FPGA interfaces to three four channel SERDES S2065S from AMCC.

Figure 3.2 Architecture of Optical Network Interface Board (ONIB)

Each AMCC interface to both the transmit FPGA and receive FPGA through a 32bit synchronous line running at 100MHz each. Of each 32bit lines to the SERDES 8bits are assigned to every high-speed differential channel. Each AMCC can transmit and receive high-speed data at up to 1.25Gbps rate. The SERDES does 8b/10b encoding of the data when transmitting and 8b/10b decoding when receiving the data. The high-speed data to and from the SERDES is through MMCX connectors.

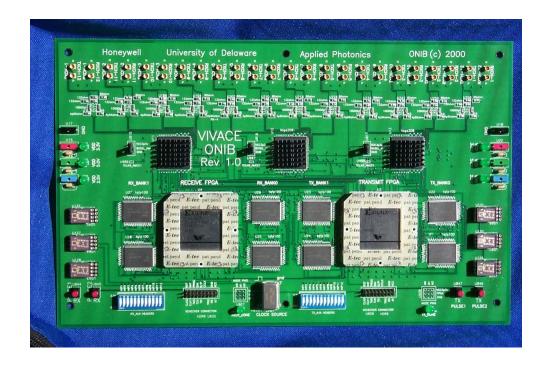

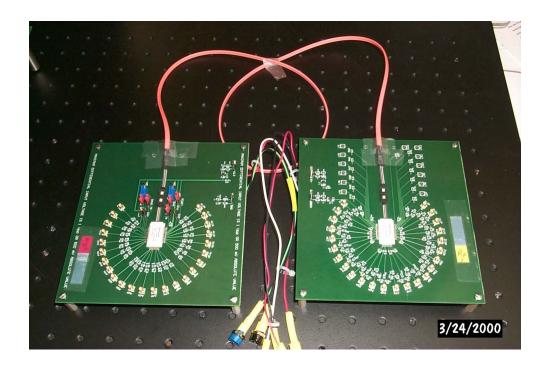

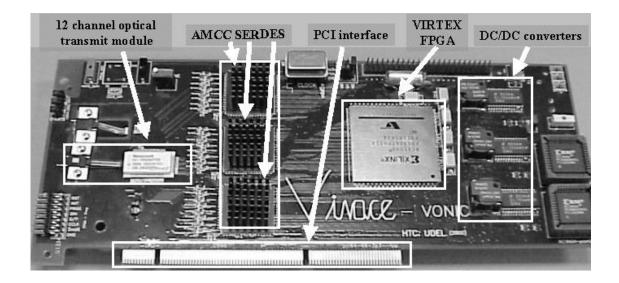

The ONIB was designed and fabricated using FR-4 based 8-layer PCB in January 2000. Many prototypes were fabricated for test and demonstration purposes. Figure 3.3 shows a picture of the fabricated and fully assembled ONIB.

Figure 3.3 Picture of the fabricated Optical Network Interface Board (ONIB)

## **3.2.1 Optical Data Link modules**

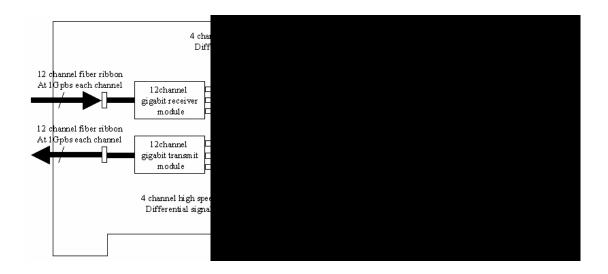

The optical data link to the ONIB is through two sets of 12-channel parallel optical data link modules. The optical data transmission is through a optical module that has a 1-Dimenisonal (D) array of 12 VCSELs. The Optical data reception is through an optical module that has a 1D array of 12 Photodetectors. The optical modules are mounted on two separate PCB with electrical interface through MMCX connectors. The transmit module and receive modules interface each other through a 12-channel optical fiber link. Each channel in the optical module has been tested to run greater than 1Gbps data rate. The ONIB interfaces to one optical transmit and one optical receive module for a full duplex connection between two ONIB to establish communication. With full duplex connection between two ONIBs the total bandwidth is greater than 24Gbps. This bandwidth is after 8b/10 encoding of the transmitted data. The optical data link modules with a parallel fiber link between them are shown in Figure 3.4.

Figure 3.4 Twelve-channel Optical Transmit and Receive Data Link Modules

## **3.2.2** ONIB to ONIB Interface Demonstrator System

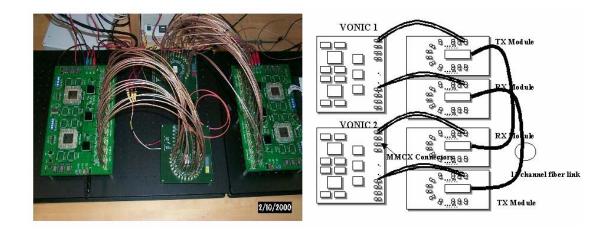

A demonstrator system was setup to interface two ONIBs through a 12channel optical fiber link. The system setup is shown in Figure 3.5.

Figure 3.5 ONIB to ONIB Interface Demonstrator System using the 12-channel Optical Data Link

The schematic on the right of Figure 3.5 shows the system setup. Each ONIB is connected to one optical transmit and one optical receive module. The ONIB are connected to the transmit module and receive module through co-axial cables with MMCX connectors. The transmit module and receive module are connected to each other through two sets of 12-channel fiber ribbon. The picture of the system setup is shown on the left of Figure 3.5. It shows only one-way communication from one ONIB to the other. Since the high-speed lines are differential signals, the co-axial cables for establishing the two-way communication are clustered and difficult to debug. Even though the system was demonstrated for two-way communication as in the schematic of Figure 3.5, only one-way communication is shows to make the picture simple.

A link integrity test was performed to test the interface between the ONIB hardware. An algorithm for generating and transmitting the data was developed. Another algorithm to receive and process the data was developed.

### **Transmit Algorithm:**

The algorithm for transmitting the data is configured onto the transmit FPGAs on both the ONIBs. The transmitting state machine is

**State 1:** Reset all three SERDES and run them at channel lock mode. This is done to synchronize all three SERDES and run them of a single clock source.

**State 2:** Run transmit test on all three SERDES separated by one clock cycle interval. The one clock cycle interval is to make sure there is no cross talk between the four channels in a single SERDES.

#### **Transmit Test Program:**

**Step 1:** Transmit synchronization characters K28.5 simultaneously on all four channels of each SERDES.

**Step 2:** Transmit 8-bit digital signature on every channel separated by one clock cycle interval. This indicates to the receiving ONIB that the data flowing immediately after the digital signature is real data.

**Step 3:** Transmit 8-bit Pseudo Random Bit Pattern (PRBS) test data on every channel separated by one clock cycle interval. It is a 255 non-repeating pattern generated using an 8-bit Linear Feedback Shift Register (LFSR) on the FPGA.

### **Receiver Algorithm:**

The algorithm for receiving the data is configured onto the receive FPGAs on both the ONIBs. The receive algorithm is

**State 1:** Watch for error status bit for each SERDES and update the error counter to assess the bit error rate of the optical channel.

State 2: Report error if loss of synchronization occurs for each SERDES.State 3: Run the test program.

### **Receiver test Program**

**Step 1:** Establish word boundary in each data stream. This is done from the K28.5 characters transmitted by the transmit ONIB.

**Step 2:** Wait for the digital signature. Once digital signature is received it indicates that the data bits following the signature are real data.

**Step 3:** Receive and check the PRBS data received on each channel. This is done by starting an 8-bit LFSR with the same seed value as the transmit data and comparing the received data. Report any errors by asserting an error status bit and the error counter keeps track of the total errors.

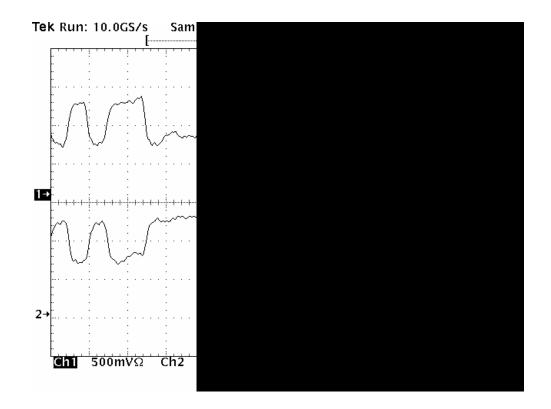

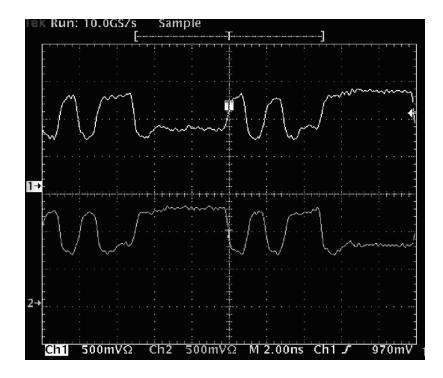

On continuous operation of the demonstrator system with two ONIBs communication to each other a bit error rate was reported in the order of  $10^{-16}$ . All twelve channels (full duplex) were tested at 900Mbps. The system was tested and verified for establishing sync between the transmit ONIB and receive ONIB at 1Gbps on all twelve channels. Figure 3.6 shows the oscilloscope snapshot of the data at 1Gbps rate in one of the channels.

Figure 3.6 Oscilloscope snapshot of one of the channels transmitting data at 1Gbps data rates

### 3.3 Optical Network Interface Card (ONIC) design

The ONIC was designed using the generic architecture described in section 3.1. The schematic if the ONIC is shown in Figure 3.7. The communication between the ONIC hardware and the compute node is through the fast-wide PCI 64-bit/66MHz interface. The theoretical maximum bandwidth of the bi-directional PCI performance is 4.22Gbps half duplex. This was done as the PCI interface is widely used and the only option available to interface a NIC to a compute node when the card was designed [25], [26] and [27].

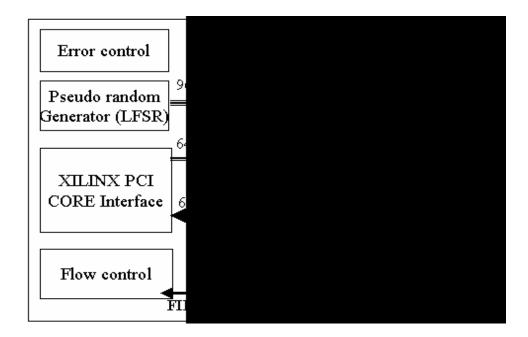

In the heart of the ONIC is an FPGA that has the network protocol and acts like a network processor. The advantage is it has the protocol defined by the user. The FPGA on the ONIC is a high-performance VIRTEX XCV1000 from Xilinx [28]. This FPGA is similar to the one used on ONIB. The whole network protocol can be implemented on to the FPGA and gives greater flexibility in modifying it. Parts of the FPGA resources on the ONIC were devoted to Xilinx PCI core. This is required for establishing communication between the ONIC and the compute node to which it will be plugged. The ONIC uses only one FPGA for handling both transmitting and receiving of the data.

Figure 3.7 Schematic view of the components in the Optical Network Interface Card (ONIC)

The data from the FPGA goes to three AMCC S2065 quad channel serial back-plane SERDES. Each SERDES has a 32-bit slow speed input and output channels and four high-speed differential inputs and outs. Each of these high-speed input and output channels can operate between 0.7Gbps and 1.4Gbps. The data to and from the compute server to the SERDES is fro the FPGA through the 32 input and 32 output data lines running between 70Mbps and 130Mbps. The SERDES on the transmit side does the 8b/10 encoding of the data. It generated K28.5 synchronization characters to establish communication with the destination node.

The high-speed differential signals from the three SERDES connect to a 12-channel gigabit parallel optical link driver and receiver module from Honeywell Technology Center. Unlike the ONIB the optical modules are placed on the Optical Network card itself. Each optical module couples to a 12-channel parallel fiber link. Each channel of this link has been demonstrated at 1.06Gbps giving the full composite parallel link a full-duplex bandwidth of 24Gbps. With the 8b/10 encoding/decoding of the data done by the SERDES at the transmitting and receiving ONIC to maintain signal integrity, the real full-duplex data bandwidth is approximately 20Gbps for each compute node the ONIC is attached to. The data from the optical receive modules is sent to the SERDES. The SERDES does data decoding, clock recovery and synchronization on the received data. The ONIC does not have any external memory as in the ONIB. The protocol uses the memory available on the FPGA for flow control.

The ONIC was fabricated using a standard copper and FR-4 PCB fabrication process. The PCB has eight layers of routing with full and split power planes. A picture of the fabricated ONIC hardware with all the components soldered to it in Figure 3.8. The PCI bus is designed to provide power to the PCI cards plugged into it. However the ONIC draws more power than the PCI bus can sustain. The three SERDES on the ONIC draws close to 10 watts of power. Hence the ONIC is powered

externally fro the compute server power supply. The isolation of power from the PCI bus ensures reliable power from the compute server without affecting the ability to add other system components on the PCI bus. The ONIC has onboard DC/DC converters to regulate the power to various components in it. The FPGA needs two power supplies: 3.3Volts for the FPGA I/Os and 2.5 Volts for the FPGA core logic. The SERDES also require 3.3Volts but draw more current than the FPGA. With this requirement three DC/DC converter circuits were implemented on the ONIC. The first power supply is to regulate FPGA 3.3Volts. Second DC/DC converter is to regulate FPGA 2.5Volts and the third to regulate 3.3Volts power supply for the SERDES and Optical link modules. All the three power supplies are generated from the 5Volts power supply of the compute server.

Figure 3.8 Prototype Optical Network Interface Card (ONIC) hardware with the whole card assembled

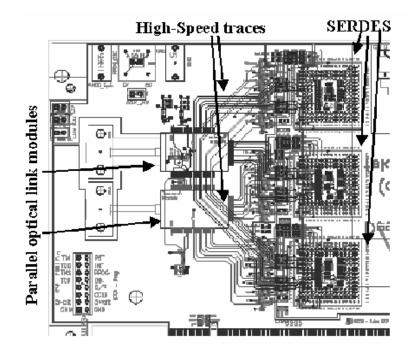

The parallel optical driver and receiver modules are located on either side of the ONIC. The transmit module is shown in Figure 3.8. The receiver module is attached on the other side of the ONIC and the fiber link comes through a cut out on the card. Differential transmission lines run from the SERDES to the optical transmit and receive modules. These lines are 500hm impedance matched and they are located only on the outer layer of the ONIC. This was done to avoid multiple vias and the inherent problems associated with vias in transmission lines [29]. Figure 3.9 is a snapshot of the high-speed traces on the ONIC.

Figure 3.9 Snapshot of the 50ohm impedance matched transmission lines from the SERDES to the parallel optical link modules

# 3.4 Programming of the ONIC hardware

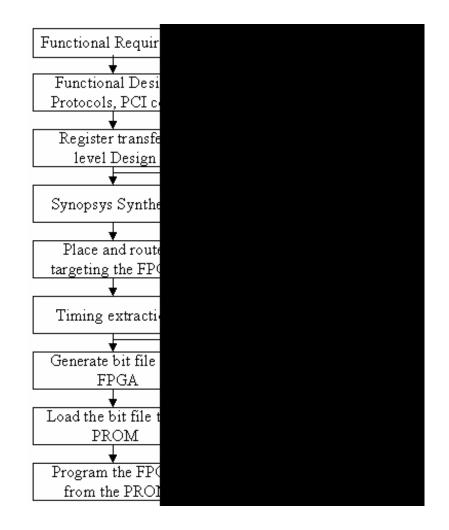

The design flow for the FPGA on the ONIC is described in this section. The design starts with a description of the protocol functional requirements. The functionality is then modeled using Very High Speed Integrated Circuits (VHSIC) Hardware Descriptive Language (VHDL) [30]. The design is further converted to register Transfer Level code. A behavioral simulation of the VHDL model is performed to validate functionality. On completion of the simulation, the VHDL model is synthesized to a netlist using tools from Synopsys. During synthesis the VHDL model is targeted towards the FPGA on the ONIC. This determines the resources that will be used on the FPGA and the timing. Once a netlist is generated it is simulated to verify functionality. Fig. 3.10 shows the steps involved in programming the FPGA with the protocols and IP core. Upon validation a bit file is generated for programming the FPGA. The bit file is loaded into a Programmable Read Only Memory (PROM) on the ONIC through a Joint Test Action Group (JTAG) interface [31]. Once the PROM is loaded with the bit file, it can be used to program the FPGA multiple times with the same functionality. When a new functionality needs to be implemented the steps described above are followed and the PROM is loaded with the new bit file.

Figure 3.10 Design flow steps for the FPGA on the ONIC hardware

# 3.5 Test and results on the ONIC

The ONIC hardware was tested in two phases. A link integrity test for Bit Error Rate (BER) analysis and a message passing application was run to test the ONIC hardware. These tests were conducted by sending synchronization characters followed by a digital signature (data starting point). This is followed by the real data.

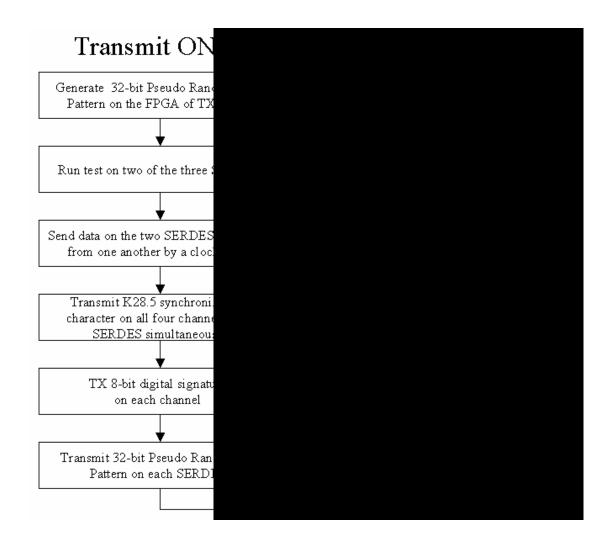

#### **3.5.1** Link Integrity Test

The link integrity test was performed on the ONIC hardware for BER analysis. Initially, ONIC loop-back test was performed. Only one ONIC was used in this test. The parallel fiber ribbon from the transmitting optical module is looped back to the optical receiver module. The fiber ribbon was 1 meter in length. The ONIC was plugged into the PCI bus of a compute server.

The FPGA of the ONIC was programmed with the test protocols and the PCI core. A 32-bit Linear Feedback Shift Register (LFSR) was used to generate Pseudo Random Bit Stream (PRBS). All three SERDES on the ONIC are controlled by the FPGA. Two of the three SERDES were run in sync with each other. The third SERDES was not used in the test. The K28.5 character for data synchronization between the two ONICs was sent on all four channels of each SERDES. After sending the K28.5 characters, an 8-bit digital signature was sent. This was followed by the same PRBS on both SERDES delayed from one another by a clock cycle. This data is encoded by the SERDES and sent to the optical modules. The data is then sent through the fiber-ribbon and is received by the receiver module. Figure 3.11 shows the steps involved in the link integrity test.

The data goes to the receiver optical module and is converted to electrical signals and sent to the SERDES. The SERDES waits for the K28.5 characters and when it recognizes the characters it synchronizes onto the oncoming data. The SERDES performs data decoding, recovers the clock from the data and sends them to the FPGA. The FPGA establishes the word boundary in the data stream from the K28.5 characters. It waits for the digital signature. As soon as the FPGA sees the digital signature it starts an LFSR with the same seed as the transmit LFSR. It compares the oncoming data with its LFSR data. A status bit gets asserted when an

error occurs. An error counter keeps track of the error from each SERDES. It also reports error on loss of synchronization in any of the SERDES. Fig. 3.12 shows a scope snapshot of the data through one of the high-speed channels at 1Gbps. The error count is communicated back to the compute server through the PCI interface and is continuously updated. The test was run for 30 days and we encountered no errors. The total bandwidth of optical data communication in this test was 8Gbps.

Figure 3.11 Steps involved in the link integrity test on the ONIC

The same test was repeated with two ONIC plugged onto two compute servers. One ONIC acts as the transmitter and the second ONIC as the receiver. The protocols were separated and the transmitting ONIC was programmed with the PCI core and the transmission protocol. The receiver ONIC was programmed with the PCI core and the receiver protocol. The length of the fiber ribbon used in this test was 1 meter. The test was run for 2 hours without any errors.

Figure 3.12 Scope snapshot of the data through one of the high-speed channels at 1Gbps

# 5.5.2 Message Passing Application

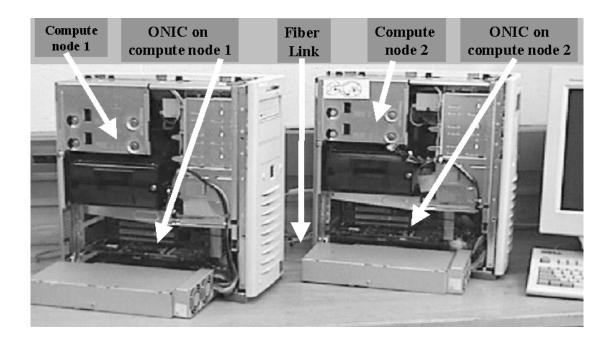

A message passing demonstration was performed to test application level communication between two ONICs plugged into the PCI bus of two compute servers. They were connected to each other through a 12-channel fiber-link. Fig. 3.13 shows a picture of the two servers with ONIC hardware.

Figure 3.13 Message passing application running between two servers with ONIC hardware connected through a parallel optical fiber link

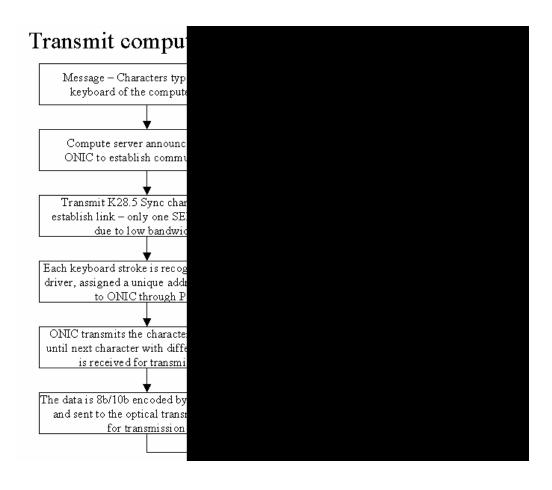

A custom software driver was written for the application to communicate with the PCI core on the ONIC FPGA through the PCI bus. The device driver was developed for Windows NT 4.0. The server uses the driver function calls to communicate with the ONIC.