# <section-header><section-header><text>

# **Classification of Digital Circuits**

- Combinational logic circuits.

- □ Output depends only on present input.

# Sequential circuits.

Output depends on present input and present state of the circuit.

- Transistor Transistor Logic (TTL) is one of the most popular and widespread of all logic families.

- Very high number of SSI and MSI devices available in the market.

- Several number of sub-families that provide a wide range of speed and power consumption.

# **Logic Families**

#### Sub families:

- □ **74***xx* : The original TTL family.

- These devices had a propagation delay of 10ns and a power consumption of 10mW, and they were introduced in the early 60's.

- □ **74H***xx* : High speed.

- Speed was improved by reducing the internal resistors. Note that this improvement caused an increase in the power consumption.

- □ **74L***xx* : Low power.

- Power consumption was improved by increasing the internal resistances, and the speed decreased.

#### □ 74Sxx : Schottky.

The use of Schottky transistors improved the speed. The power dissipation is less than the 74Hxx sub-family.

□ **74LS***xx* : Low power Schottky.

- Uses Schottky transistors to improve speed. High internal resistances improves power consumption.

- □ **74AS***xx* : Advanced Schottky.

- Twice as fast as 74Sxx with approximately the same power dissipation.

# **Logic Families**

- □ **74ALS***xx* : Advanced Low power Schottky.

- Lower power consumption and higher speed than 74LSxx.

- 74Fxx : Fast.

- Performance is between 74ASxx and 74ALSxx.

- Most TTL sub-families have a corresponding 54series (military) version, and these series operate in a wider temperature and voltage ranges.

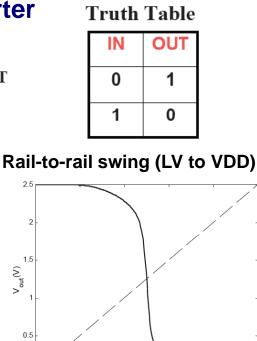

- Complementary Metal Oxide Semiconductor (CMOS) replaced TTL devices in the 90's due to advances in the design of MOS circuits made in mid 80's.

- Advantages:

- Operate with a wider range of voltages that any other logic family.

- □ Has high noise immunity.

- □ Dissipates very low power at low frequencies.

- □ It requires an extremely low driving current.

- □ High fanout.

# **Logic Families**

#### Disadvantages:

- □ Power consumption increases with frequency.

- □ Susceptible to ESD electro-static discharges.

#### Sub-families:

- □ 40xx : Original CMOS family.

- Fairly slow, but it has a low power dissipation.

- □ **74HC***xx* : High speed CMOS.

- Better current sinking and sourcing than 40xx. It uses voltage supply between 2 and 6 volts.

- Higher voltage  $\rightarrow$  higher speed.

- Lower voltage →lower power consumption.

# **74HCT***xx* : High speed CMOS, TTL compatible. Better current sinking and sourcing than 40*xx*. It uses voltage supply of 5V. Compatible with TTL family.

- □ **74AC***xx* : Advanced CMOS.

- Very fast. It can source and sink high currents. Not TTL compatible.

- □ **74ACT***xx* : Advanced CMOS, TTL compatible.

- Same as 74ACxx, but it is compatible with TTL family.

- □ **74FCT***xx* : Fast CMOS, TTL compatible.

- It is faster and has lower power dissipation than the 74ACxx and 74ACTxx sub-families. Compatible with TTL family.

# **Logic Families**

- Prefixes, to identify the manufacturer.

- □ SN : Texas Instrument.

- □ MN : Motorola.

- DM : National

- □ N : Signetics

- D P : Intel

- □ H : Harris

- AMD : Advanced Micro Devices

- Suffixes, identifies the packaging.

- N : Plastic DIP (dual in-line package)

- P : Plastic DIP

- J : Ceramic DIP

- $\square$  W : Ceramic flat package.

- D : Plastic 'small outline' package

# **Logic Circuits**

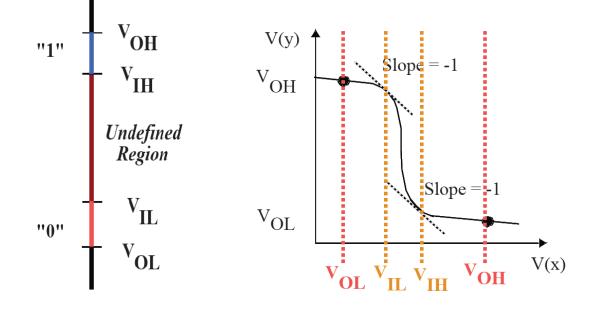

Several voltage and current levels are of interest when working with logic gates, including:

V<sub>OL</sub> = output voltage when the gate is LOW

V<sub>OH</sub> = output voltage when the gate is HIGH

V<sub>IL</sub> = input voltage when the gate is LOW

V<sub>IH</sub> = input voltage when the gate is HIGH

I<sub>OL</sub> = output current when the gate is LOW

I<sub>OH</sub> = output current when the gate is LOW

I<sub>OH</sub> = input current when the gate is HIGH

I<sub>IL</sub> = input current when the gate is HIGH

I<sub>IL</sub> = input current when the gate is HIGH

# **Logic Circuits**

# 74LL Data Sheet

- Package Options Include Plastic "Small Outline" Packages, Ceramic Chip Carriers and Flat Packages, and Plastic and Ceramic DIPs

- Dependable Texas Instruments Quality and Reliability

#### description

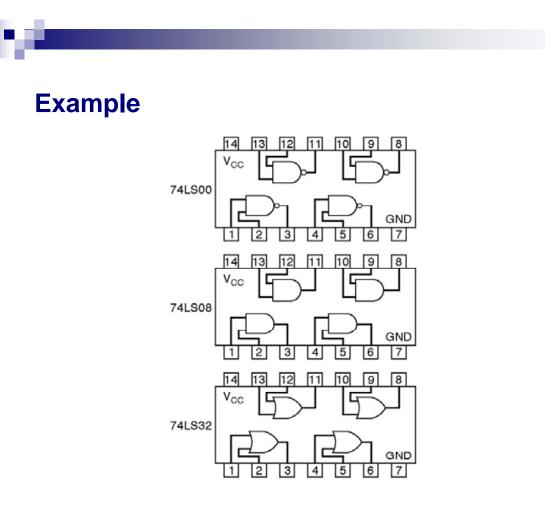

These devices contain four independent 2-input-NAND gates.

The SN5400, SN54LS00, and SN54S00 are characterized for operation over the full military temperature range of -55 °C to 125 °C. The SN7400, SN74LS00, and SN74S00 are characterized for operation from 0 °C to 70 °C.

#### FUNCTION TABLE (each gate)

| INP | UTS | OUTPUT |

|-----|-----|--------|

| A   | в   | Y      |

| н   | н   | L      |

| L   | х   | н      |

| х   | L   | н      |

#### SN5400, SN54LSOO, SN54SOO, SN7400, SN74LSOO, SN74SOO QUADRUPLE 2-INPUT POSITIVE-NAND GATES December 1983-revised March 1988

| SN5400 J PACKAGE<br>SN54LS00, SN54S00 J OR W PACKAGE<br>SN7400 N PACKAGE<br>SN74LS00, SN74S00 D OR N PACKAGE<br>(TOP VIEW)                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $1A \ \begin{bmatrix} 1 \\ 0 \\ 14 \end{bmatrix} \ V_{CC}$ $1B \ \begin{bmatrix} 2 \\ 13 \end{bmatrix} \ 4B$ $1Y \ \begin{bmatrix} 3 \\ 2 \end{bmatrix} \ 4A$ $2A \ \begin{bmatrix} 4 \\ 11 \end{bmatrix} \ 4Y$ $2B \ \begin{bmatrix} 5 \\ 10 \end{bmatrix} \ 3B$ $2Y \ \begin{bmatrix} 6 \\ 9 \end{bmatrix} \ 3A$ $GND \ \begin{bmatrix} 7 \\ 8 \end{bmatrix} \ 3Y$           |

| SN5400 W PACKAGE<br>(TOP VIEW)                                                                                                                                                                                                                                                                                                                                                 |

| $1A \begin{bmatrix} 1 \\ 1 \\ 1 \end{bmatrix} \begin{bmatrix} 1 \\ 14 \end{bmatrix} 4Y$ $1B \begin{bmatrix} 2 \\ 13 \end{bmatrix} 4B$ $1Y \begin{bmatrix} 3 \\ 12 \end{bmatrix} 4A$ $V_{CC} \begin{bmatrix} 4 \\ 11 \end{bmatrix} GND$ $2Y \begin{bmatrix} 5 \\ 10 \end{bmatrix} 3B$ $2A \begin{bmatrix} 6 \\ 9 \end{bmatrix} 3A$ $2B \begin{bmatrix} 7 \\ 8 \end{bmatrix} 3Y$ |

| 74LL Data Sheet                               |      | SN7400 |       |      |     |       |      |

|-----------------------------------------------|------|--------|-------|------|-----|-------|------|

|                                               | MIN  | NOM    | MAX   | MIN  | NOM | МАХ   | UNIT |

| Vcc Supply voltage                            | 4.5  | 5      | 5.5   | 4.75 | 5   | 5.25  | V    |

| VIH High-level input voltage                  | 2    |        |       | 2    |     |       | v    |

| VIL Low-level input voltage                   |      |        | 0.8   |      |     | 0.8   | V    |

| OH High-level output current                  |      |        | - 0.4 |      |     | - 0.4 | mA   |

| IOL Low-level output current                  |      |        | 16    |      |     | 16    | mA   |

| T <sub>A</sub> Operating free-air temperature | - 55 |        | 125   | 0    |     | 70    | °c   |

electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|           |                        |                          |                            | SN5400 |      |          | SN7400 |          |       |      |

|-----------|------------------------|--------------------------|----------------------------|--------|------|----------|--------|----------|-------|------|

| PARAMETER |                        | TEST CONDI               | TIONST                     | MIN    | TYP‡ | ГҮР‡ МАХ |        | MIN TYP‡ |       | UNIT |

| VIK       | V <sub>CC</sub> ≈ MIN, | I <sub>I</sub> = – 12 mA |                            |        |      | - 1.5    |        |          | - 1.5 | V    |

| ∨он       | V <sub>CC</sub> = MIN, | VIL = 0.8 V,             | I <sub>OH</sub> = - 0.4 mA | 2.4    | 3.4  |          | 2.4    | 3.4      | _     | V    |

| VOL       | V <sub>CC</sub> = MIN, | V <sub>IH</sub> = 2 V,   | IOL = 16 mA                |        | 0.2  | 0.4      |        | 0.2      | 0.4   | v    |

| 1         | V <sub>CC</sub> = MAX, | Vj = 5.5 V               |                            |        |      | 1        |        |          | 1     | mA   |

| Чн        | V <sub>CC</sub> = MAX, | VI = 2.4 V               |                            |        |      | 40       |        |          | 40    | μA   |

| ΙL        | V <sub>CC</sub> = MAX, | VI = 0.4 V               | •                          |        |      | - 1.6    |        |          | - 1.6 | mA   |

| IOS §     | V <sub>CC</sub> = MAX  |                          |                            | - 20   |      | - 55     | - 18   |          | - 55  | mA   |

| Іссн      | V <sub>CC</sub> = MAX, | VI = 0 V                 |                            |        | 4    | 8        |        | 4        | 8     | mA   |

| CCL       | V <sub>CC</sub> = MAX, | V <sub>1</sub> = 4.5 V   |                            |        | 12   | 22       |        | 12       | 22    | mA   |

15

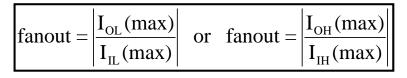

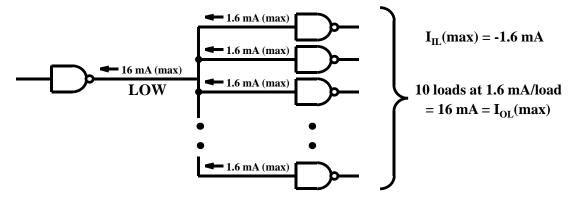

#### **Fanout**

- The number of standard loads that the output can drive.

- the number of standard loads is limited by the amount of input current each load requires as compared to the current that the driving gate can deliver.

# Fanout

| fanout = $\left  \frac{I_{OL}(max)}{I_{IL}(max)} \right $ | or | fanout = | $\frac{I_{OH}(max)}{I_{IH}(max)}$ |

|-----------------------------------------------------------|----|----------|-----------------------------------|

|-----------------------------------------------------------|----|----------|-----------------------------------|

- Fanout is much higher for CMOS devices than for TTL devices.

- I<sub>IL</sub> and I<sub>IH</sub> are extremely small for CMOS devices (< 1 uA).</li>

- However, the input capacitance of CMOS gates affects propagation delay, so increased fanout results in increased delay.

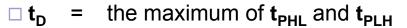

# **Propagation Delay**

- The time that it takes a gate to switch logic levels

- □ **t**<sub>PLH</sub> = propagation delay when the OUTPUT switches from LOW to HIGH

- □ **t**<sub>PHL</sub> = propagation delay when the OUTPUT switches from HIGH to LOW

# **Propagation Delay**

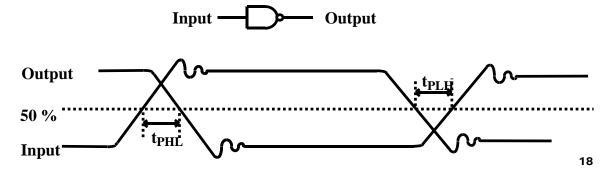

- Fanout affects propagation delay for CMOS gates.

- □ the delay (in ns) for a 2-input NAND is  $t_D = 0.05 + 0.014$ \*SL

where SL is the number of standard loads.

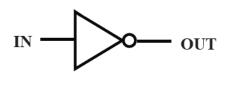

$V_{DD}$

D

G

IN

OUT

0.5

0

0.5

1.5

V<sub>in</sub> (V)

2

2.5

# **Common Logic Gates**

| Gate | Symbol         | Truth-Table                                                                                                                                           | Expression                                 |

|------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| NAND | x<br>y =z      | X         Y         Z           0         0         1           0         1         1           1         0         1           1         1         0 | $\mathbf{Z} = \mathbf{X} \cdot \mathbf{Y}$ |

| AND  | x<br>y = z     | X         Y         Z           0         0         0           0         1         0           1         0         0           1         1         1 | $\mathbf{Z} = \mathbf{X} \cdot \mathbf{Y}$ |

| NOR  | x<br>y<br>z    | X         Y         Z           0         0         1           0         1         0           1         0         0           1         1         0 | Z = X + Y                                  |

| OR   | x<br>y = D - z | X         Y         Z           0         0         0           0         1         1           1         0         1           1         1         1 | $\mathbf{Z} = \mathbf{X} + \mathbf{Y}$     |

|      |                |                                                                                                                                                       |                                            |

# **Common Logic Gates**

| <b>XOR</b><br>(X ⊕ Y)  | x<br>y<br>J<br>D-z | X         Y         Z           0         0         0           0         1         1           1         0         1           1         1         0 | $Z = X \overline{Y} + \overline{X} Y$<br>X or Y but not both<br>("inequality", "difference") |

|------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| <b>XNOR</b><br>(X ⊕ Y) | ×<br>y ⊐)⊃o− z     | X         Y         Z           0         0         1           0         1         0           1         0         0           1         1         1 | Z = X Y + X Y<br>X and Y the same<br>("equality")                                            |

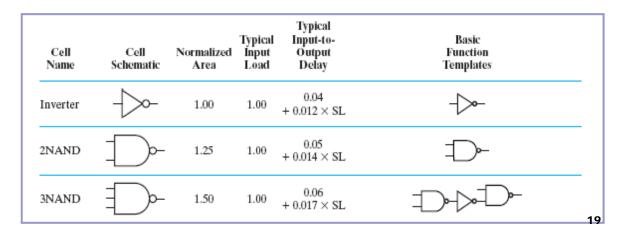

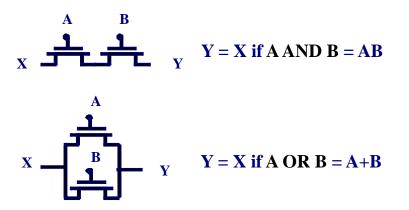

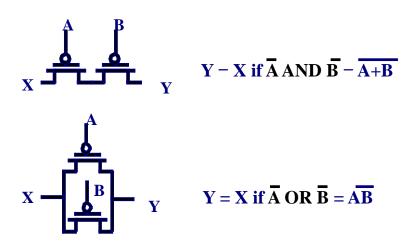

# **NMOS Series/Parallel Connection**

- Transistors can be thought as a switch controlled by its gate signal

- NMOS switch closes when switch control input is HIGH

NMOS Transistors pass a "strong" L but a "weak" H

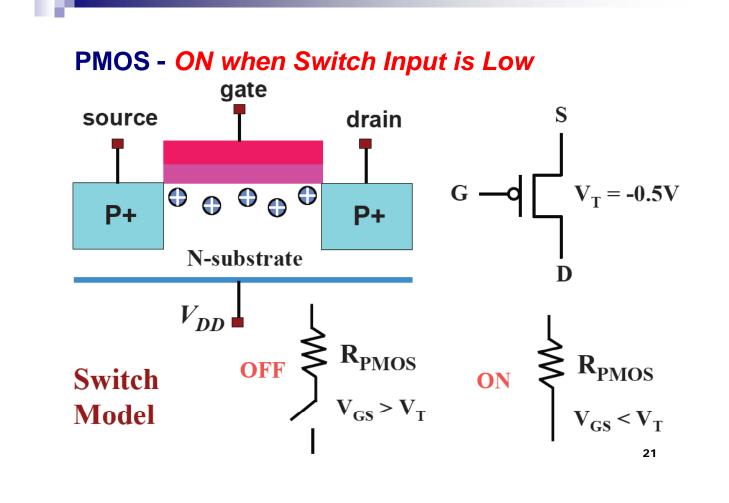

# **PMOS Series/Parallel Connection**

PMOS switch closes when switch control input is LOW

PMOS Transistors pass a "strong" H but a "weak" L

27

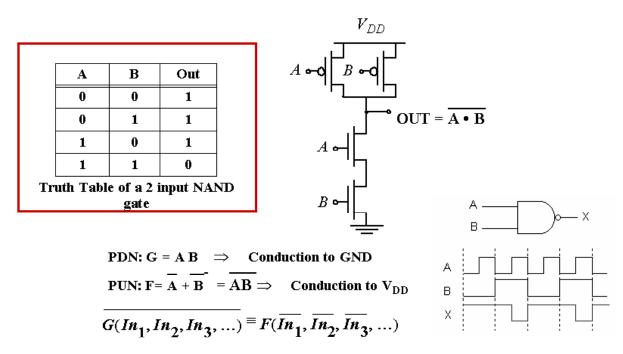

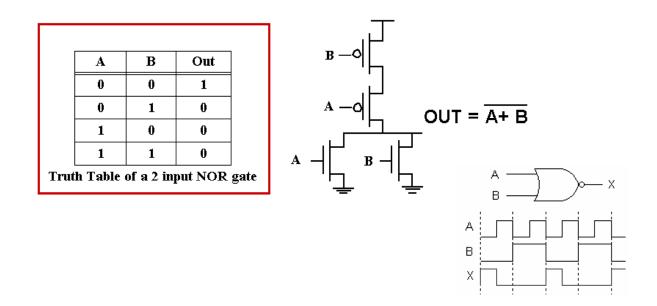

# **The NAND Gate**

# Inverter with more inputs gates

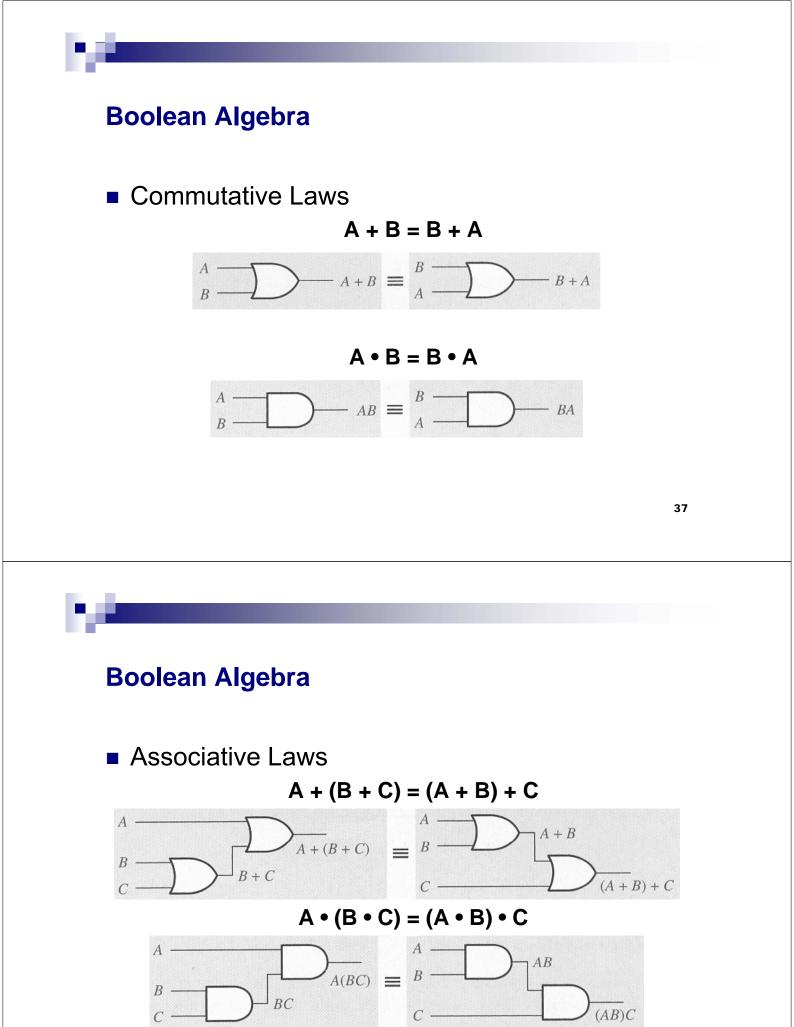

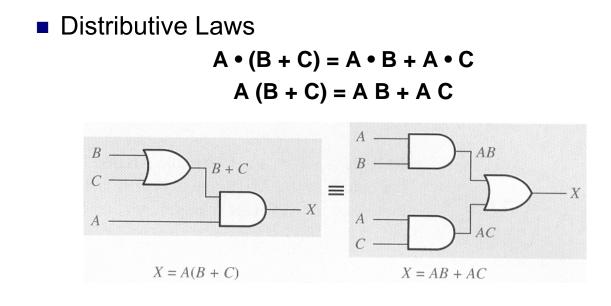

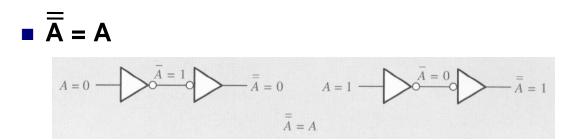

# **Boolean Algebra**

39

# **Rules of Boolean Algebra**

- A + 0 = A А в Х 0 A = 1 -0 0 A = 0X = 1-X = 00 1 1 0 0 1 0 1 1 1 1 X = A + 0 = A

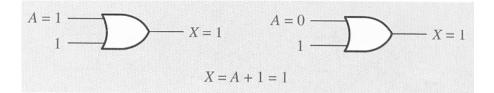

- A + 1 = 1

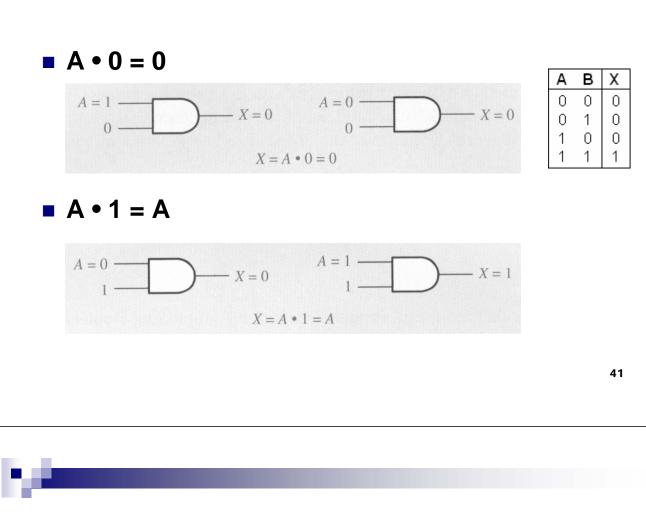

# **Rules of Boolean Algebra**

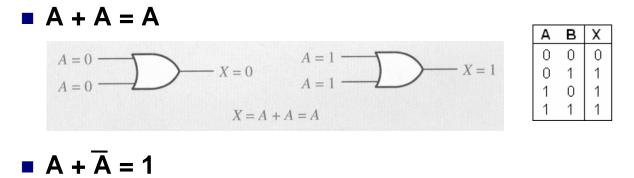

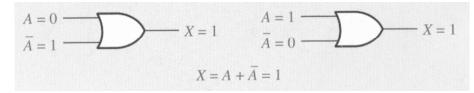

**Rules of Boolean Algebra**

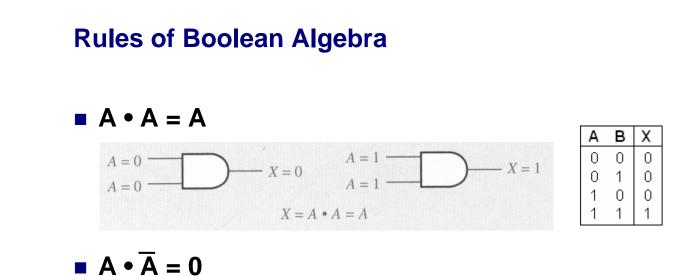

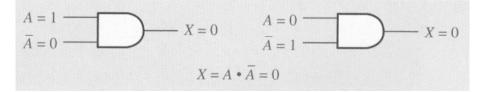

# **Rules of Boolean Algebra**

# A + AB = A

| A | В | AB | A + AB |                       |

|---|---|----|--------|-----------------------|

| 0 | 0 | 0  | 0      |                       |

| 0 | 1 | 0  | 0      |                       |

| 1 | 0 | 0  | 1      | ↓ ↓                   |

| 1 | 1 | 1  | 1      | A straight connection |

| • |   |    | *      |                       |

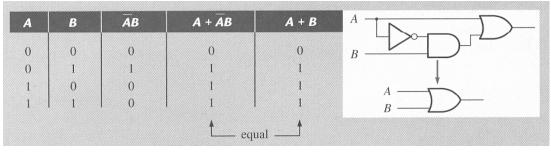

# **Rules of Boolean Algebra**

A + AB = A + B

# (A + B)(A + C) = A + BC

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$  | A | B | С | A + B | A + C | (A + B)(A + C) | ВС | A + BC | ATT |

|--------------------------------------------------------|---|---|---|-------|-------|----------------|----|--------|-----|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$  | 0 | 0 | 0 | 0     | 0     | 0              | 0  | 0      |     |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$  | 0 | 0 | 1 | 0     | 1     | 0              | 0  | 0      |     |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | 0 | 1 | 0 | 1     | 0     | 0              | 0  | 0      | c   |

|                                                        | 0 | 1 | 1 | 1     | 1     | 1              | 1  | 1      |     |

|                                                        | 1 | 0 | 0 | 1     | 1     | 1              | 0  | 1      | Ļ   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$  | 1 | 0 | 1 | 1     | 1     | 1              | 0  | 1      | A   |

|                                                        | 1 | 1 | 0 | 1     | 1     | 1              | 0  | 1      |     |

|                                                        | 1 | 1 | 1 | 1     | 1     | 1              | 1  | 1      |     |

•

$$y = A\overline{B}D + A\overline{B}\overline{D}$$

•  $y = A\overline{B}$

•  $z = (\overline{A} + B)(A + B)$

•  $z = B$

•  $x = ACD + \overline{A}BCD$

x = ACD + BCD

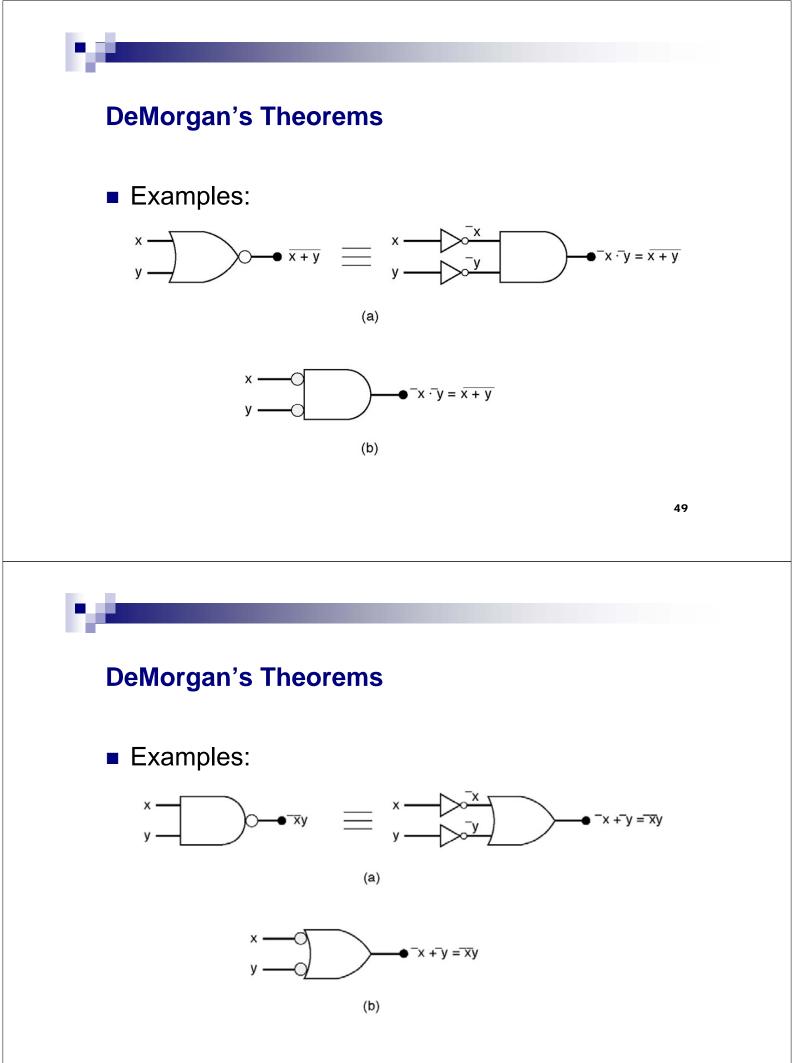

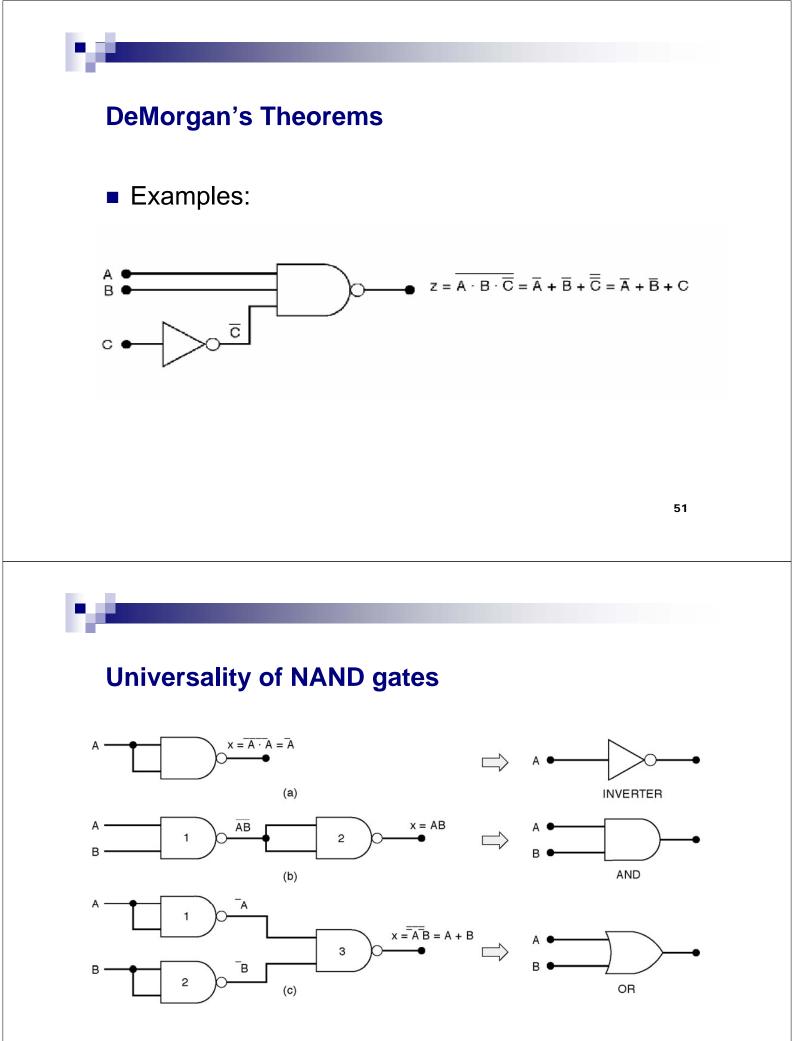

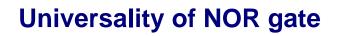

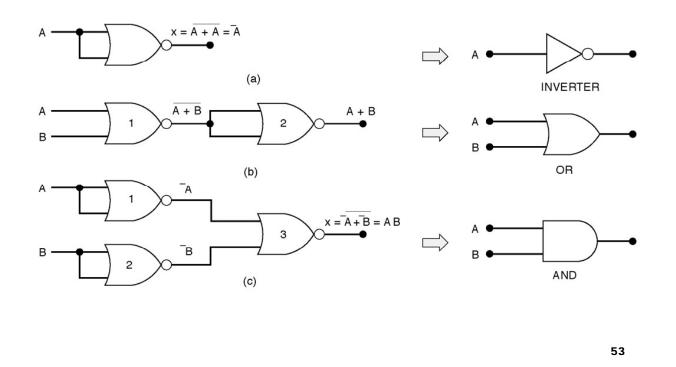

# **DeMorgan's Theorems**

Theorem 1  $(\overline{x+y}) = \overline{x} \cdot \overline{y}$ Theorem 2  $(\overline{x \cdot y}) = \overline{x} + \overline{y}$

Remember: "Break the bar, change the operator"

- DeMorgan's theorem is very useful in digital circuit design

- It allows ANDs to be exchanged with ORs by using invertors

47

#### **DeMorgan's Theorems**

Examples:

$$F = \overline{X \cdot Y} + \overline{P \cdot Q}$$

$$= \overline{X} + \overline{Y} + \overline{P} + \overline{Q}$$

2 NAND plus 1 OR

1 OR with some input invertors

$$Z = (\overline{A} + C) \cdot (B + \overline{D})$$

$$= A\overline{C} + \overline{B} D$$