# **DIGITAL ELECTRONICS**

# F.Y.B.Sc.I.T

# SEM-I

| B. Sc                  | (Informa                                          | tion Technology)                                                                     | Semester – I         |                       |  |  |  |  |

|------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------|----------------------|-----------------------|--|--|--|--|

|                        |                                                   | al Electronics Practical                                                             | Course Code: USIT1P2 |                       |  |  |  |  |

|                        |                                                   | Period is 50 minutes)                                                                | 3                    |                       |  |  |  |  |

| Credits                | 5                                                 |                                                                                      | 2<br>Marks           |                       |  |  |  |  |

| <u>Hours</u><br>Evalua | tion System                                       | Practical Examination                                                                | 2 <sup>1</sup> /2    | 50                    |  |  |  |  |

| Lvarua                 | tion bystem                                       | Internal                                                                             |                      |                       |  |  |  |  |

| List of                | Practical                                         |                                                                                      |                      | i                     |  |  |  |  |

| 1.                     | Study of I                                        | Logic gates and their ICs a                                                          | nd universal gat     | es:                   |  |  |  |  |

| a.                     | Study of A                                        | ND, OR, NOT, XOR, XNC                                                                | R, NAND and N        | IOR gates             |  |  |  |  |

| b.                     | IC 7400, 7                                        | 402, 7404, 7408, 7432, 748                                                           | 6, 74266             |                       |  |  |  |  |

| c.                     | Implement                                         | t AND, OR, NOT, XOR, XN                                                              | NOR using NAN        | D gates.              |  |  |  |  |

| d.                     | Implemen                                          | t AND, OR, NOT, XOR, XN                                                              | NOR using NOR        | gates.                |  |  |  |  |

| 2.                     | Implemen                                          | nt the given Boolean expres                                                          | sions using min      | imum number of gates. |  |  |  |  |

| a.                     | Verifying                                         | De Morgan's laws.                                                                    |                      |                       |  |  |  |  |

| b.                     | Implemen                                          | t other given expressions usi                                                        | ng minimum nur       | nber of gates.        |  |  |  |  |

| c.                     | Implement                                         | t other given expressions usi                                                        | ng minimum nur       | nber of ICs.          |  |  |  |  |

|                        |                                                   |                                                                                      |                      |                       |  |  |  |  |

| 3.                     | Implemen                                          | nt combinational circuits.                                                           |                      |                       |  |  |  |  |

| a.                     | -                                                 | Design and implement combinational circuit based on the problem given and minimizing |                      |                       |  |  |  |  |

|                        | using K-maps.                                     |                                                                                      |                      |                       |  |  |  |  |

| 4.                     | Implemer                                          | nt code converters.                                                                  |                      |                       |  |  |  |  |

| a.                     | -                                                 | d implement Binary – to – G                                                          | trav code convert    | er                    |  |  |  |  |

| u.<br>b.               | -                                                 | d implement Gray – to – Bin                                                          | -                    |                       |  |  |  |  |

| c.                     | -                                                 | d implement Binary – to – B                                                          |                      |                       |  |  |  |  |

| d.                     |                                                   | d implement Binary – to – X                                                          |                      |                       |  |  |  |  |

| _                      |                                                   |                                                                                      |                      |                       |  |  |  |  |

| 5.                     | -                                                 | nt Adder and Subtractor A                                                            |                      | ts.                   |  |  |  |  |

| a.                     | ę                                                 | d implement Half adder and                                                           | Full adder.          |                       |  |  |  |  |

| b.                     | _                                                 | d implement BCD adder.                                                               |                      |                       |  |  |  |  |

| с.                     | -                                                 | d implement XS – 3 adder.                                                            |                      |                       |  |  |  |  |

| d.                     | -                                                 | d implement binary subtracted                                                        |                      |                       |  |  |  |  |

| e.                     | _                                                 | Design and implement BCD subtractor.                                                 |                      |                       |  |  |  |  |

| f.                     | _                                                 | Design and implement XS – 3 subtractor.                                              |                      |                       |  |  |  |  |

| 6.                     | -                                                 | nt Arithmetic circuits.                                                              |                      |                       |  |  |  |  |

| a.                     | Design and implement a 2-bit by 2-bit multiplier. |                                                                                      |                      |                       |  |  |  |  |

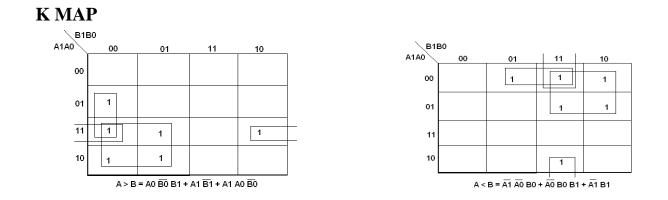

| b.  | Design and implement a 2-bit comparator.                                                            |

|-----|-----------------------------------------------------------------------------------------------------|

| 7.  | Implement Encode and Decoder and Multiplexer and Demultiplexers.                                    |

| и.  | Design and implement 8:3 encoder.                                                                   |

| b.  | Design and implement 3:8 decoder.                                                                   |

| с.  | Design and implement 4:1 multiplexer. Study of IC 74153, 74157                                      |

| d.  | Design and implement 1:4 demultiplexer. Study of IC 74139                                           |

| e.  | Implement the given expression using IC 74151 8:1 multiplexer.                                      |

| f.  | Implement the given expression using IC 74138 3:8 decoder.                                          |

|     |                                                                                                     |

| 8.  | Study of flip-flops and counters.                                                                   |

| a.  | Study of IC 7473.                                                                                   |

| b.  | Study of IC 7474.                                                                                   |

| с.  | Study of IC 7476.                                                                                   |

| d.  | Conversion of Flip-flops.                                                                           |

| e.  | Design of 3-bit synchronous counter using 7473 and required gates.                                  |

| f.  | Design of 3-bit ripple counter using IC 7473.                                                       |

| 9.  | Study of counter ICs and designing Mod-N counters.                                                  |

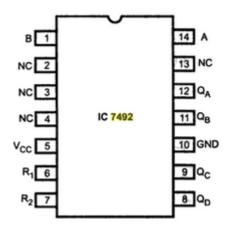

| a.  | Study of IC 7490, 7492, 7493 and designing mod-n counters using these.                              |

| b.  | Designing mod-n counters using IC 7473 and 7400 (NAND gates)                                        |

| 10. | Design of shift registers and shift register counters.                                              |

| a.  | Design serial – in serial – out, serial – in parallel – out, parallel – in serial – out, parallel – |

|     | in parallel – out and bidirectional shift registers using IC 7474.                                  |

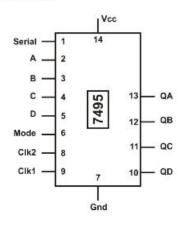

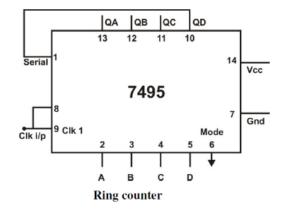

| b.  | Study of ID 7495.                                                                                   |

| с.  | Implementation of digits using seven segment displays.                                              |

| Books and References: |                                         |                      |                     |         |      |  |  |  |

|-----------------------|-----------------------------------------|----------------------|---------------------|---------|------|--|--|--|

| Sr. No.               | Title                                   | Author/s             | Publisher           | Edition | Year |  |  |  |

| 1.                    | Digital Electronics and<br>Logic Design | N. G. Palan          | Technova            |         |      |  |  |  |

| 2.                    | Digital Principles and<br>Applications  | Malvino and<br>Leach | Tata McGraw<br>Hill |         |      |  |  |  |

# **PRACTICAL-1**

# Study of Logic gates and their ICs and universal gates:

- 1.Study of AND, OR, NOT, XOR, XNOR, NAND and NOR gates

- 2.IC 7400, 7402, 7404, 7408, 7432, 7486, 74266

- 3.Implement AND, OR, NOT, XOR, XNOR using NAND gates.

- 4.Implement AND, OR, NOT, XOR, XNOR using NOR gates.

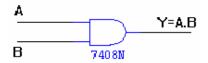

### AND GATE:

## SYMBOL:

#### TRUTH TABLE

| А | В | A.B |

|---|---|-----|

| 0 | 0 | 0   |

| O | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 1   |

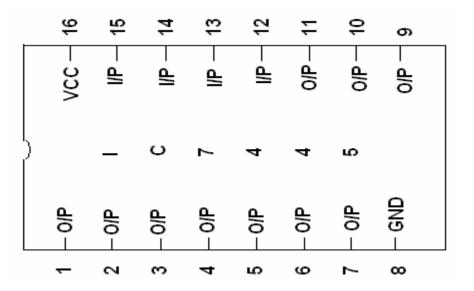

**PIN DIAGRAM:**

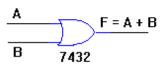

## **OR GATE:**

SYMBOL :

### TRUTH TABLE

| А | В | A+B |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 1   |

$\mathbf{PIN}\,\mathbf{DIAG}\,\mathbf{RAM}:$

F.Y.B.Sc.I.T

SEM-1

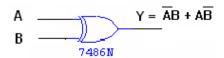

### **NOT GATE:**

### SYMBOL:

A  $Y = \overline{A}$ 7404N

#### TRUTH TABLE :

| А | Ā |

|---|---|

| 0 | 1 |

| 1 | 0 |

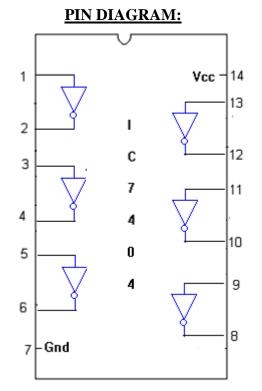

## **X-OR GATE :**

## **SYMBOL :**

### TRUTH TABLE :

| А | в | AB + AB |

|---|---|---------|

| O | 0 | 0       |

| O | 1 | 1       |

| 1 | 0 | 1       |

| 1 | 1 | 0       |

## PIN DIAGRAM :

F.Y.B.Sc.I.T

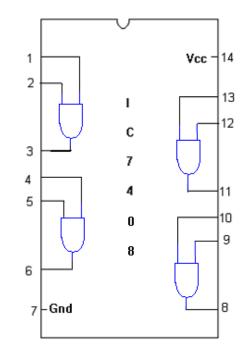

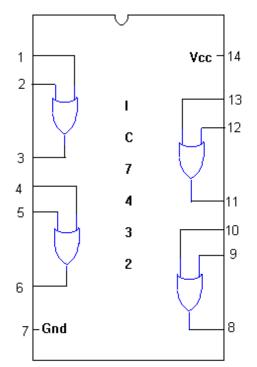

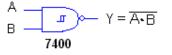

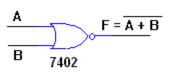

#### **2-INPUT NAND GATE:**

#### SYMBOL:

## **PIN DIAGRAM:**

#### TRUTH TABLE

| А | В | A.B |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

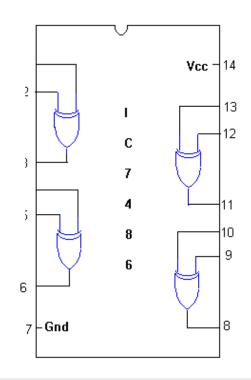

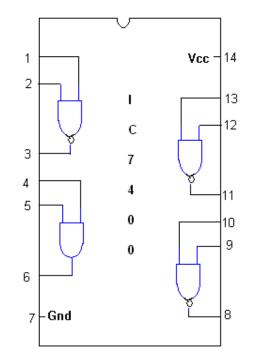

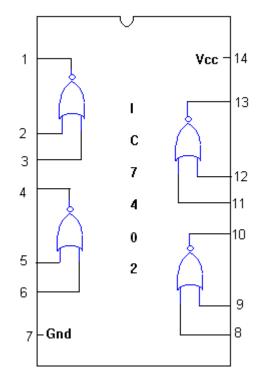

#### **NOR GATE:**

#### SYMBOL :

### TRUTH TABLE

| А | В | A+B |

|---|---|-----|

| O | 0 | 1   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

## PIN DIAGRAM :

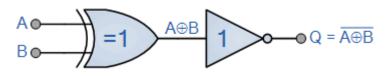

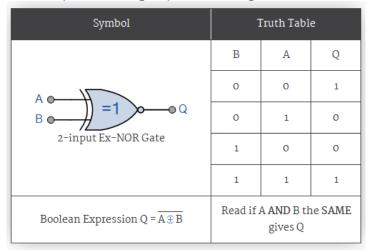

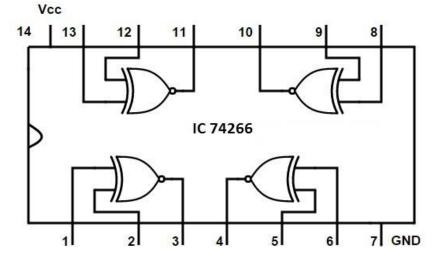

# IC 74266

2-input "Ex-OR" gate plus a "NOT" gate

74266 Quad 2-input Ex-NOR Gate

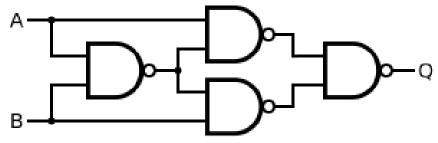

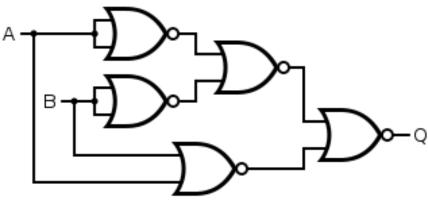

XOR gate from NAND gates:

XOR gate from NOR gates:

# PRACTICAL-2 Implement the given Boolean expressions using minimum number of gates

- 1. Verifying De Morgan's laws.

- 2. Implement other given expressions using minimum number of gates. (any expression from Chapter 3, Reference 1)

- 3. Implement other given expressions using minimum number of ICs. (any expression from Chapter 3, Reference 1)

De Morgan has suggested two theorems which are extremely useful in Boolean Algebra. The two theorems are discussed below.

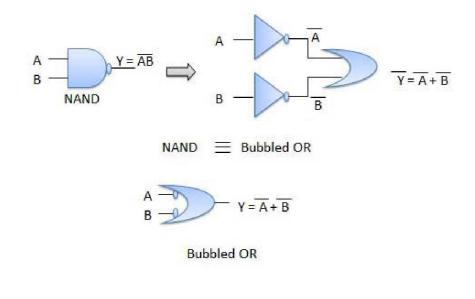

### Theorem 1

## $\overline{A.B} = \overline{A} + \overline{B}$

#### NAND = Bubbled OR

- The left hand side *LHS* of this theorem represents a NAND gate with inputs A and B, whereas the right hand side *RHS* of the theorem represents an OR gate with inverted inputs.

- This OR gate is called as **Bubbled OR**.

| Α | В | AB | Ā | B | $\overline{A} + \overline{B}$ |

|---|---|----|---|---|-------------------------------|

| 0 | 0 | 1  | 1 | 1 | 1                             |

| 0 | 1 | 1  | 1 | 0 | 1                             |

| 1 | 0 | 1  | 0 | 1 | 1                             |

| 1 | 1 | 0  | 0 | 0 | 0                             |

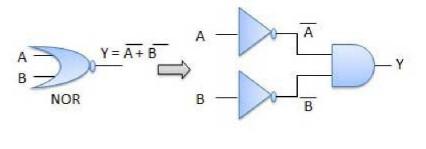

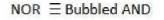

## Theorem 2

#### $\overline{A + B} = \overline{A} \cdot \overline{B}$

NOR = Bubbled AND

The LHS of this theorem represents a NOR gate with inputs A and B, whereas the RHS represents an AND gate with inverted inputs.

This AND gate is called as **Bubbled AND**.

**Bubbled AND**

| A | В | A+B | Ā | B | Ā.B |

|---|---|-----|---|---|-----|

| 0 | 0 | 1   | 1 | 1 | 1   |

| 0 | 1 | 0   | 1 | 0 | 0   |

| 1 | 0 | 0   | 0 | 1 | 0   |

| 1 | 1 | 0   | 0 | 0 | 0   |

# **PRACTICAL-3 Implement combinational circuits**

Design and implement combinational circuit based on the problem given and minimizing using K-maps.

(any question from Chapter 5, Reference 1)

# **PRACTICAL-4**

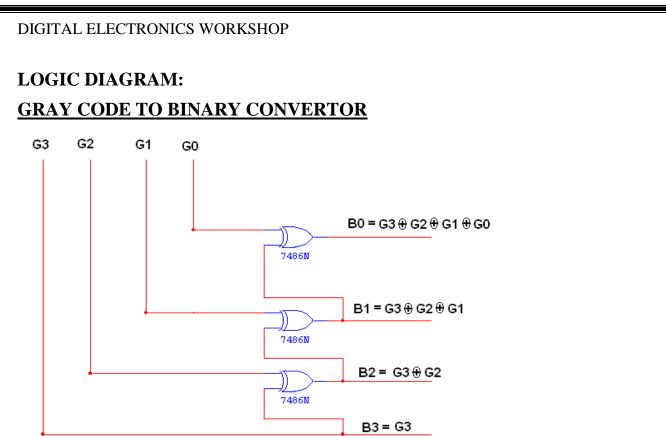

# **Implement code converters**

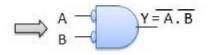

- 1. Design and implement Binary to Gray code converter

- 2. Design and implement Gray to Binary code converter

- 3. Design and implement Binary to BCD code converter

- 4. Design and implement Binary to XS-3 code converter

# LOGIC DIAGRAM: BINARY TO GRAY CODE CONVERTOR

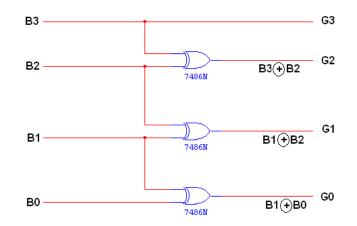

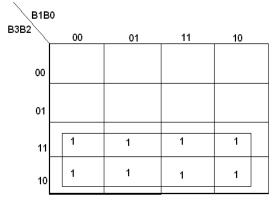

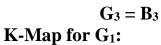

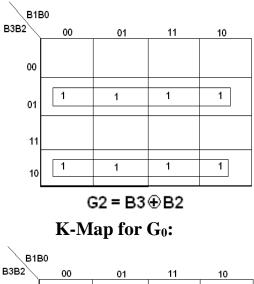

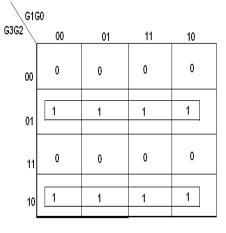

## K-Map for G<sub>3</sub>:

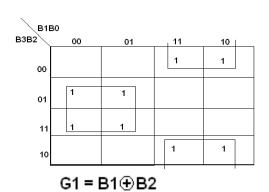

# K-Map for G<sub>2</sub>:

# **TRUTH TABLE:**

| Bin       | ary input | -<br>,    |           |    | Gray code | e output  |           |

|-----------|-----------|-----------|-----------|----|-----------|-----------|-----------|

| <b>B3</b> | <b>B2</b> | <b>B1</b> | <b>B0</b> | G3 | G2        | <b>G1</b> | <b>G0</b> |

| 0         | 0         | 0         | 0         | 0  | 0         | 0         | 0         |

| 0         | 0         | 0         | 1         | 0  | 0         | 0         | 1         |

| 0         | 0         | 1         | 0         | 0  | 0         | 1         | 1         |

| 0         | 0         | 1         | 1         | 0  | 0         | 1         | 0         |

| 0         | 1         | 0         | 0         | 0  | 1         | 1         | 0         |

| 0         | 1         | 0         | 1         | 0  | 1         | 1         | 1         |

| 0         | 1         | 1         | 0         | 0  | 1         | 0         | 1         |

| 0         | 1         | 1         | 1         | 0  | 1         | 0         | 0         |

| 1         | 0         | 0         | 0         | 1  | 1         | 0         | 0         |

| 1         | 0         | 0         | 1         | 1  | 1         | 0         | 1         |

| 1         | 0         | 1         | 0         | 1  | 1         | 1         | 1         |

| 1         | 0         | 1         | 1         | 1  | 1         | 1         | 0         |

| 1         | 1         | 0         | 0         | 1  | 0         | 1         | 0         |

| 1         | 1         | 0         | 1         | 1  | 0         | 1         | 1         |

| 1         | 1         | 1         | 0         | 1  | 0         | 0         | 1         |

| 1         | 1         | 1         | 1         | 1  | 0         | 0         | 0         |

## **TRUTH TABLE:**

| Gray Code

**Binary Code**

**G3 G1 G2** GO **B3 B2 B1 B0**

F.Y.B.Sc.I.T

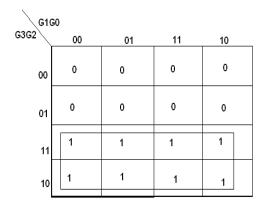

# K-Map for B<sub>3</sub>:

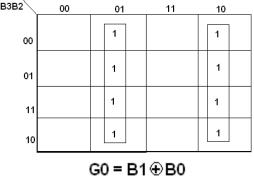

$\mathbf{B3} = \mathbf{G3}$

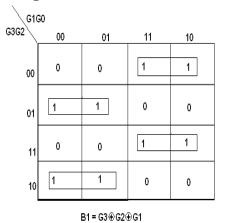

## K-Map for B<sub>1</sub>:

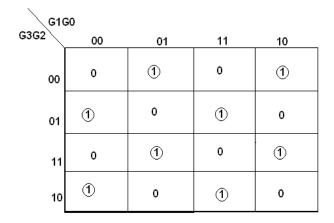

$B0 = G3 \oplus G2 \oplus G1 \oplus G0$

## K-Map for B<sub>2</sub>:

B2 = G3⊕G2

## K-Map for B<sub>0</sub>:

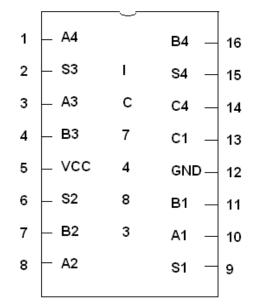

## **PIN DIAGRAM FOR IC 7483:**

# **PRACTICAL-5**

# **Implement Adder and Subtractor Arithmetic circuits**

1. Design and implement half adder and Full adder.

- 2. Design and implement BCD adder.

- 3. Design and implement XS 3 adder.

# 4. Design and implement binary subtractor.

- 5. Design and implement BCD subtractor.

- 6. Design and implement XS 3 subtractor.

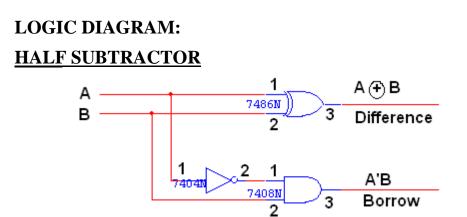

# LOGIC DIAGRAM:

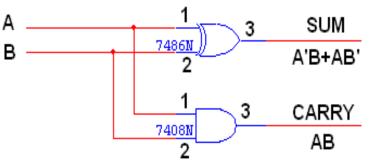

# HALF ADDER

## **TRUTH TABLE:**

| Α | B | CARRY | SUM |

|---|---|-------|-----|

| 0 | 0 |       | 0   |

| 0 | 0 | 0     | 0   |

| 0 | 1 | 0     | 1   |

| 1 | 0 | 0     | 1   |

| 1 | 1 | 1     | 0   |

|   |   |       |     |

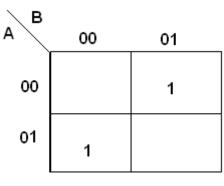

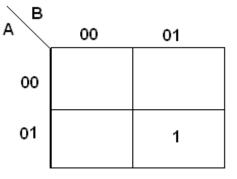

K-Map for SUM:

K-Map for CARRY:

SUM = A'B + AB'

CARRY = AB

# LOGIC DIAGRAM:

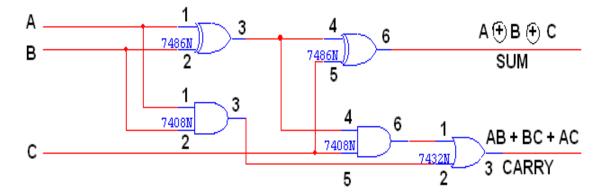

# FULL ADDER USING TWO HALF ADDER

## **TRUTH TABLE:**

| Α | B | С | CARRY | SUM |

|---|---|---|-------|-----|

|   |   |   |       |     |

| 0 | 0 | 0 | 0     | 0   |

| 0 | 0 | 1 | 0     | 1   |

| 0 | 1 | 0 | 0     | 1   |

| 0 | 1 | 1 | 1     | 0   |

| 1 | 0 | 0 | 0     | 1   |

| 1 | 0 | 1 | 1     | 0   |

| 1 | 1 | 0 | 1     | 0   |

| 1 | 1 | 1 | 1     | 1   |

|   |   |   |       |     |

А

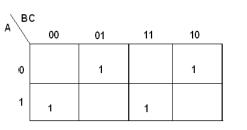

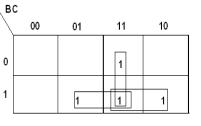

# K-Map for SUM:

SUM = A'B'C + A'BC' + ABC' + ABC CARRY = AB + BC + AC

# K-Map for CARRY:

## **TRUTH TABLE:**

| Α | В      | BORROW | DIFFERENCE |

|---|--------|--------|------------|

| 0 | 0      | 0      | Δ          |

| 0 | 0<br>1 | 1      | 1          |

| 1 | 0      | 0      | 1          |

| 1 | 1      | 0      | 0          |

|   |        |        |            |

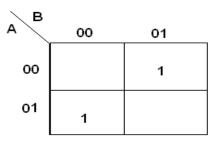

## **K-Map for DIFFERENCE:**

**DIFFERENCE** = A'B + AB'

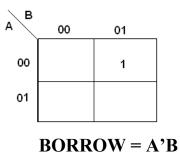

## K-Map for BORROW:

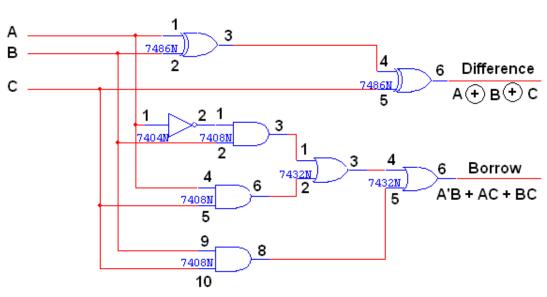

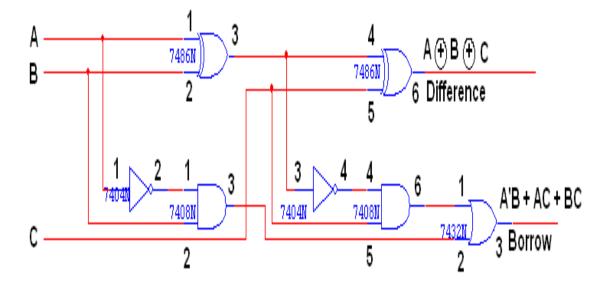

## FULL SUBTRACTOR

# FULL SUBTRACTOR USING TWO HALF SUBTRACTOR:

# **TRUTH TABLE:**

| Α | B | С | BORROW | DIFFERENCE |

|---|---|---|--------|------------|

|   |   |   |        |            |

| 0 | 0 | 0 | 0      | 0          |

| 0 | 0 | 1 | 1      | 1          |

| 0 | 1 | 0 | 1      | 1          |

| 0 | 1 | 1 | 1      | 0          |

| 1 | 0 | 0 | 0      | 1          |

| 1 | 0 | 1 | 0      | 0          |

| 1 | 1 | 0 | 0      | 0          |

| 1 | 1 | 1 | 1      | 1          |

|   |   |   |        |            |

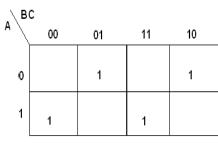

# K-Map for Difference:

## **K-Map for Borrow:**

Difference = A'B'C + A'BC' + AB'C' + ABC

Borrow = A'B + BC + A'C

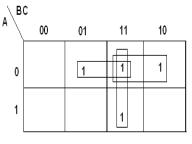

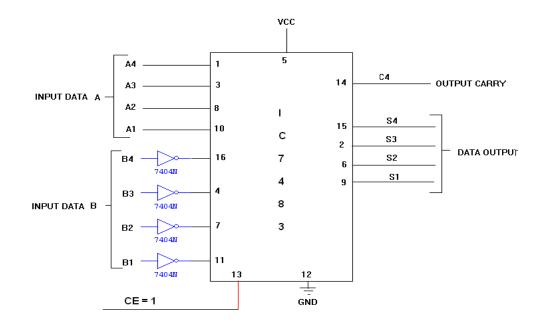

# LOGIC DIAGRAM: 4-BIT BINARY SUBTRACTOR

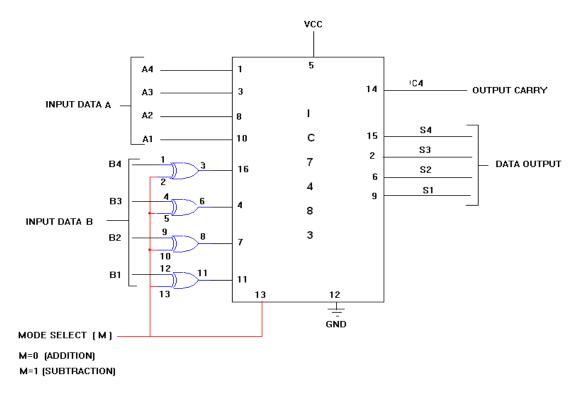

# LOGIC DIAGRAM: 4-BIT BINARY ADDER/SUBTRACTOR

| Ir | nput ] | Data | A  | Ir        | nput ]    | Data | B         | Addition Sub |           |            |    | btrac     | otraction |    |    |    |    |

|----|--------|------|----|-----------|-----------|------|-----------|--------------|-----------|------------|----|-----------|-----------|----|----|----|----|

| A4 | A3     | A2   | A1 | <b>B4</b> | <b>B3</b> | B2   | <b>B1</b> | С            | <b>S4</b> | <b>S</b> 3 | S2 | <b>S1</b> | В         | D4 | D3 | D2 | D1 |

| 1  | 0      | 0    | 0  | 0         | 0         | 1    | 0         | 0            | 1         | 0          | 1  | 0         | 1         | 0  | 1  | 1  | 0  |

| 1  | 0      | 0    | 0  | 1         | 0         | 0    | 0         | 1            | 0         | 0          | 0  | 0         | 1         | 0  | 0  | 0  | 0  |

| 0  | 0      | 1    | 0  | 1         | 0         | 0    | 0         | 0            | 1         | 0          | 1  | 0         | 0         | 1  | 0  | 1  | 0  |

| 0  | 0      | 0    | 1  | 0         | 1         | 1    | 1         | 0            | 1         | 0          | 0  | 0         | 0         | 1  | 0  | 1  | 0  |

| 1  | 0      | 1    | 0  | 1         | 0         | 1    | 1         | 1            | 0         | 0          | 1  | 0         | 0         | 1  | 1  | 1  | 1  |

| 1  | 1      | 1    | 0  | 1         | 1         | 1    | 1         | 1            | 1         | 0          | 1  | 0         | 0         | 1  | 1  | 1  | 1  |

| 1  | 0      | 1    | 0  | 1         | 1         | 0    | 1         | 1            | 0         | 1          | 1  | 1         | 0         | 1  | 1  | 0  | 1  |

F.Y.B.Sc.I.T

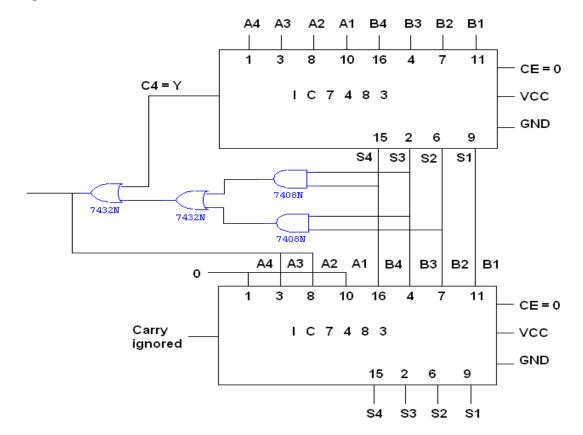

# LOGIC DIAGRAM: BCD ADDER

## **TRUTH TABLE:**

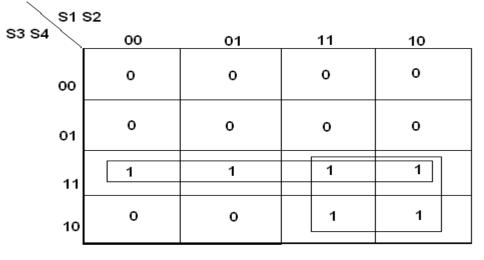

# K MAP

Y = S4 (S3 + S2)

## **TRUTH TABLE:**

|           | BCD SUM   |    |           |   |  |  |  |  |

|-----------|-----------|----|-----------|---|--|--|--|--|

| <b>S4</b> | <b>S3</b> | S2 | <b>S1</b> | С |  |  |  |  |

| 0         | 0         | 0  | 0         | 0 |  |  |  |  |

| 0         | 0         | 0  | 1         | 0 |  |  |  |  |

| 0         | 0         | 1  | 0         | 0 |  |  |  |  |

| 0         | 0         | 1  | 1         | 0 |  |  |  |  |

| 0         | 1         | 0  | 0         | 0 |  |  |  |  |

| 0         | 1         | 0  | 1         | 0 |  |  |  |  |

| 0         | 1         | 1  | 0         | 0 |  |  |  |  |

| 0         | 1         | 1  | 1         | 0 |  |  |  |  |

| 1         | 0         | 0  | 0         | 0 |  |  |  |  |

| 1         | 0         | 0  | 1         | 0 |  |  |  |  |

| 1         | 0         | 1  | 0         | 1 |  |  |  |  |

| 1         | 0         | 1  | 1         | 1 |  |  |  |  |

| 1         | 1         | 0  | 0         | 1 |  |  |  |  |

| 1         | 1         | 0  | 1         | 1 |  |  |  |  |

| 1         | 1         | 1  | 0         | 1 |  |  |  |  |

| 1         | 1         | 1  | 1         | 1 |  |  |  |  |

# **PRACTICAL-6**

# **Implement Arithmetic circuits**

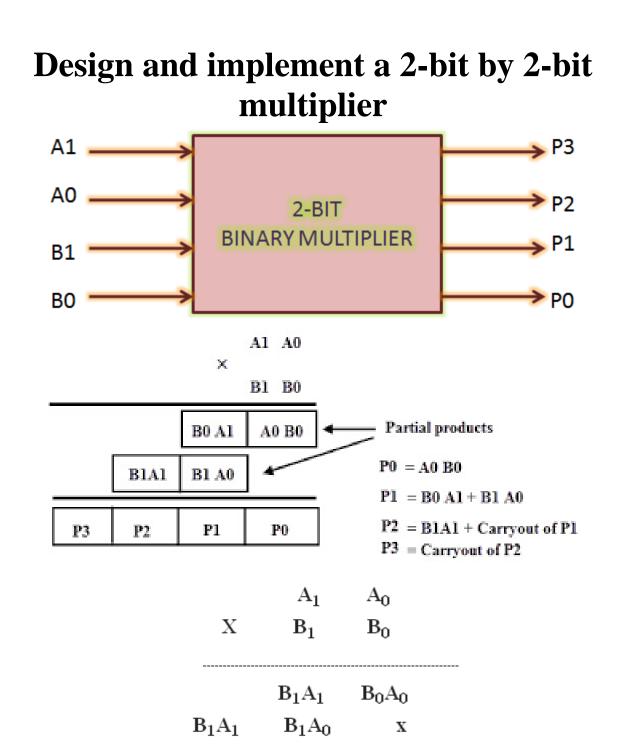

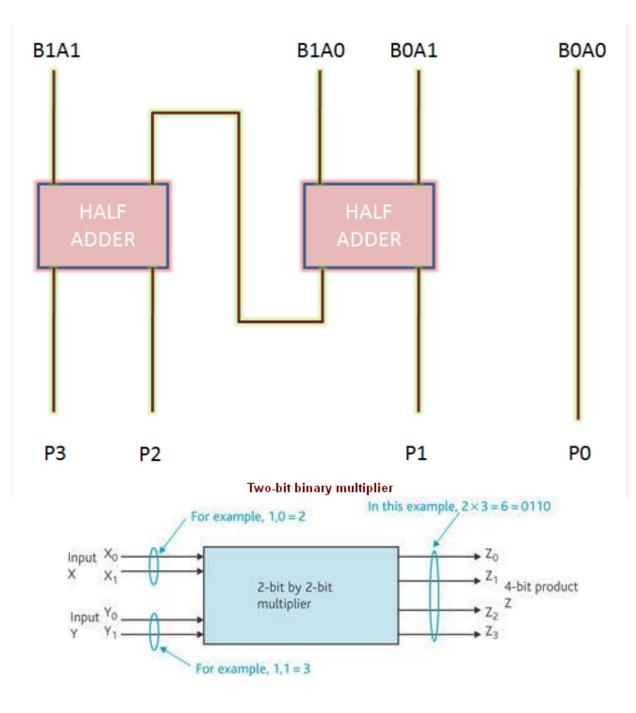

1. Design and implement a 2-bit by 2-bit multiplier.

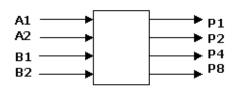

2. Design and implement a 2-bit comparator

F.Y.B.Sc.I.T

we get the partial products as:

P0 = A0\*B0 P1 = A0\*B1 xor A1 \* B0 ; carry generated here goes to next stage P2 = A1\*B1 xor (A0\*B1) \* (A1\*B0) P3 = A1\*B1 and (A0\*B1) \* (A1\*B0)

block diagram and truth table

| A2 | A1 | <b>B</b> 2 | <b>B1</b> | <b>P8</b> | P4 | P2 | P1 |

|----|----|------------|-----------|-----------|----|----|----|

| 0  | 0  | 0          | 0         | 0         | 0  | 0  | 0  |

|    |    | 0          | 1         | 0         | 0  | 0  | 0  |

|    |    | 1          | 0         | 0         | 0  | 0  | 0  |

|    |    | 1          | 1         | 0         | 0  | 0  | 0  |

| 0  | 1  | 0          | 0         | 0         | 0  | 0  | 0  |

|    |    | 0          | 1         | 0         | 0  | 0  | 1  |

|    |    | 1          | 0         | 0         | 0  | 1  | 0  |

|    |    | 1          | 1         | 0         | 0  | 1  | 1  |

| 1  | 0  | 0          | 0         | 0         | 0  | 0  | 0  |

|    |    | 0          | 1         | 0         | 0  | 1  | 0  |

|    |    | 1          | 0         | 0         | 1  | 0  | 0  |

|    |    | 1          | 1         | 0         | 1  | 1  | 0  |

| 1  | 1  | 0          | 0         | 0         | 0  | 0  | 0  |

|    |    | 0          | 1         | 0         | 0  | 1  | 1  |

|    |    | 1          | 0         | 0         | 1  | 1  | 0  |

|    |    | 1          | 1         | 1         | 0  | 0  | 1  |

|    |    |            |           | I         |    |    |    |

4-variable K-map for each of the 4 output functions

7408

| A1 | A0 | <b>B1</b> | <b>B0</b> | A > B | $\mathbf{A} = \mathbf{B}$ | A < B |

|----|----|-----------|-----------|-------|---------------------------|-------|

| 0  | 0  | 0         | 0         | 0     | 1                         | 0     |

| 0  | 0  | 0         | 1         | 0     | 0                         | 1     |

| 0  | 0  | 1         | 0         | 0     | 0                         | 1     |

| 0  | 0  | 1         | 1         | 0     | 0                         | 1     |

| 0  | 1  | 0         | 0         | 1     | 0                         | 0     |

| 0  | 1  | 0         | 1         | 0     | 1                         | 0     |

| 0  | 1  | 1         | 0         | 0     | 0                         | 1     |

| 0  | 1  | 1         | 1         | 0     | 0                         | 1     |

| 1  | 0  | 0         | 0         | 1     | 0                         | 0     |

| 1  | 0  | 0         | 1         | 1     | 0                         | 0     |

| 1  | 0  | 1         | 0         | 0     | 1                         | 0     |

| 1  | 0  | 1         | 1         | 0     | 0                         | 1     |

| 1  | 1  | 0         | 0         | 1     | 0                         | 0     |

| 1  | 1  | 0         | 1         | 1     | 0                         | 0     |

| 1  | 1  | 1         | 0         | 1     | 0                         | 0     |

| 1  | 1  | 1         | 1         | 0     | 1                         | 0     |

# **PRACTICAL-7**

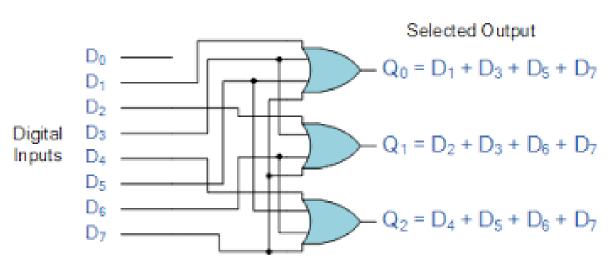

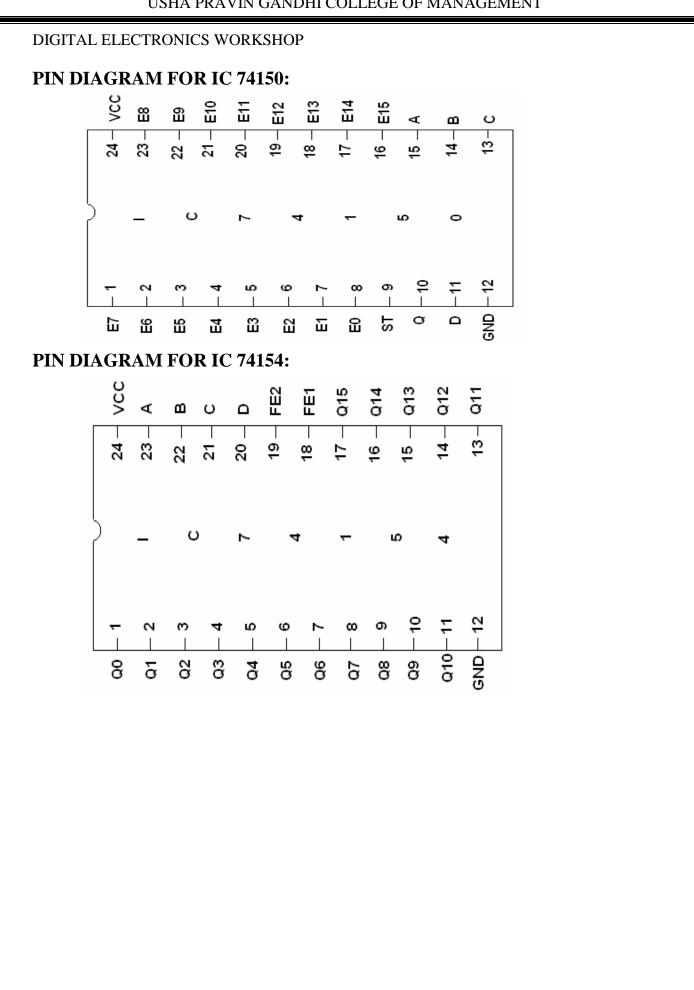

# **Implement Encode and Decoder and Multiplexer and De-multiplexers**

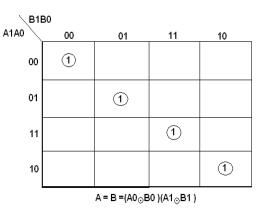

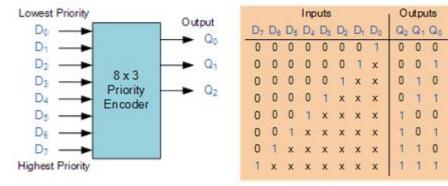

- 1. Design and implement 8:3 encoder.

- 2. Design and implement 3:8 decoder.

- 3. **Design and implement 4:1 multiplexer**. Study of IC 74153, 74157

- 4. **Design and implement 1:4 demultiplexer.** Study of IC 74139

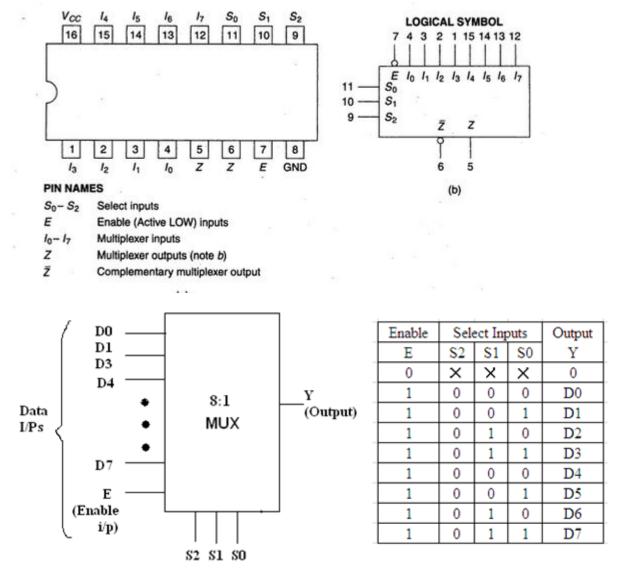

- 5. Implement the given expression using IC 74151 8:1 multiplexer

- 6. Implement the given expression using IC 74138 3:8 decoder

| IC No. | Description                 | Output              |

|--------|-----------------------------|---------------------|

| 74139  | Dual 1:4 Demultiplexer      | Inverted input      |

|        | (2-line-to-4-line decoder)  |                     |

| 74155  | Dual 1:4 Demultiplexer      | 1Y — Inverted input |

|        | (2-line-to-4-line decoder)  | 2Y — Same as input  |

| 74156  | -do-                        | Open-collector      |

|        |                             | 1 Y—Inverted input  |

|        |                             | 2Y-Same as input    |

| 74138  | 1:8 Demultiplexer           | Inverted input      |

|        | (3-line-to-8-line decoder)  |                     |

| 74154  | 1:16 Demultiplexer          | Same as input       |

|        | (4-line-to-16-line decoder) |                     |

| 74159  | -do-                        | Same as input       |

|        |                             | Open-collector      |

# **Design and implement 8:3 encoder**

8-to-3 Bit Priority Encoder

X • denticare

|                |    | D  | igital | Input | s              |    |                | Bina           | iry Ou | tput |

|----------------|----|----|--------|-------|----------------|----|----------------|----------------|--------|------|

| D <sub>7</sub> | Dő | D5 | $D_4$  | D3    | D <sub>2</sub> | D1 | D <sub>0</sub> | Q <sub>2</sub> | Qı     | Qo   |

| 0              | 0  | 0  | 0      | 0     | 0              | 0  | 1              | 0              | 0      | 0    |

| 0              | 0  | 0  | 0      | 0     | 0              | 1  | х              | 0              | 0      | 1    |

| 0              | 0  | 0  | 0      | 0     | 1              | х  | х              | 0              | 1      | 0    |

| 0              | 0  | 0  | 0      | 1     | х              | х  | х              | 0              | 1      | 1    |

| 0              | 0  | 0  | 1      | х     | х              | х  | х              | 1              | 0      | 0    |

| 0              | 0  | 1  | х      | х     | х              | х  | х              | 1              | 0      | 1    |

| 0              | 1  | х  | х      | х     | х              | х  | х              | 1              | 1      | 0    |

| 1              | x  | x  | х      | x     | x              | x  | х              | 1              | 1      | 1    |

|    |                | p  | igital |    | Binary Output |    |    |    |     |    |

|----|----------------|----|--------|----|---------------|----|----|----|-----|----|

| D7 | D <sub>6</sub> | Ds | Da     | D3 | D2            | 01 | Dq | Q2 | Q3  | Qo |

| 0  | 0              | 0  | 0      | 0  | 0             | 0  | 1  | 0  | 0.  | 0  |

| 0  | 0.             | 00 | 0      | 0  | (0.)          | 1  | Х  | 0  | 0.5 | ŧ  |

| 0  | 0              | 0  | 0      | 0  | 81            | X  | х  | 0  | 1   | 0  |

| 0  | 0              | 0  | 9      | 1  | X             | X  | X  | 0  | Ť.  | Ť  |

| 0  | 0              | 0  | 1      | X  | ×             | ×  | ×  | Ť  | 0   | 0  |

| 0  | 0              | 1  | X      | X  |               | X  | X  | T  | 0   | 1  |

| 0  | 1              | X  | X      | X  | Х             | х  | X  | 1  | 10  | 0  |

| 1  | x              | x. | ×.     | ×  | ×             | X  | ×  | 1  | ¥2, | Ť. |

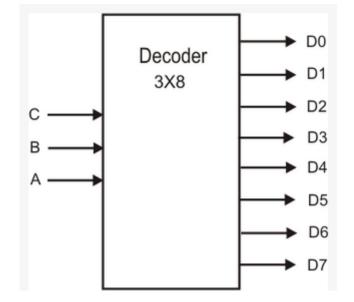

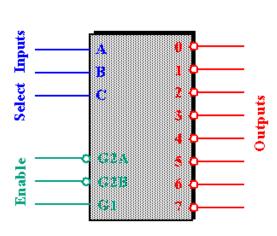

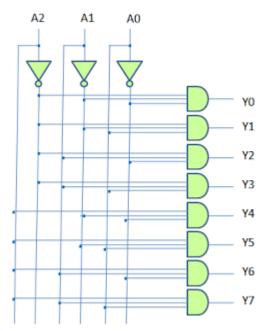

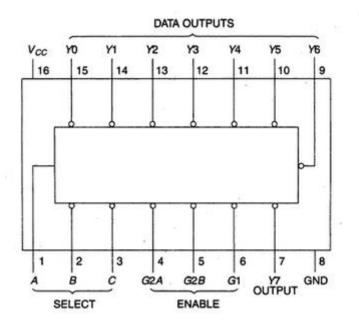

# **Design and implement 3:8 decoder**

|     | •    | Inpu | ıts |        |   |   |   |   | o |   |   |   |   |

|-----|------|------|-----|--------|---|---|---|---|---|---|---|---|---|

| E   | nabl | e    | S   | Output |   |   |   | _ |   |   |   |   |   |

| G2A | G2B  | Gl   | С   | в      | Α | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 1   | Χ    | Χ    | Χ   | Χ      | Χ | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| X   | 1    | Х    | Х   | Х      | Х | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| Χ   | Χ    | 0    | Χ   | Х      | Х | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0   | 0    | 1    | Ö   | 0      | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0   | Õ    | 1    | Ö   | 0      | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0   | 0    | 1    | 0   | 1      | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0   | 0    | 1    | 0   | 1      | 1 | 1 | 1 | 1 | Õ | 1 | 1 | 1 | 1 |

| 0   | 0    | 1    | 1   | 0      | 0 | 1 | 1 | 1 | 1 | Ũ | 1 | 1 | 1 |

| 0   | 0    | 1    | 1   | 0      | 1 | 1 | 1 | 1 | 1 | 1 | Ö | 1 | 1 |

| 0   | 0    | 1    | 1   | 1      | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 0   | 0    | 1    | 1   | 1      | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

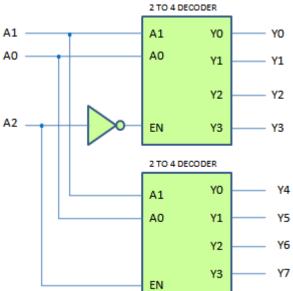

### 3 to 8 decoder using 2 to 4 decoders:

3 to 8 decoder using gates:

# Design and implement 4:1 multiplexer.

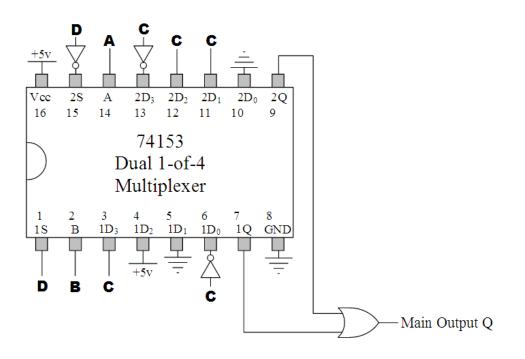

Study of IC 74153

| D | С | B | Α | Q | Di              |

|---|---|---|---|---|-----------------|

| 0 | 0 | 0 | 0 | 1 | 1D <sub>0</sub> |

| 0 | 0 | 0 | 1 | 0 | 1D1             |

| 0 | 0 | 1 | 0 | 1 | 1D <sub>2</sub> |

| 0 | 0 | 1 | 1 | 0 | 1D3             |

| 0 | 1 | 0 | 0 | 0 | 1D <sub>0</sub> |

| 0 | 1 | 0 | 1 | 0 | 1D1             |

| 0 | 1 | 1 | 0 | 1 | 1D <sub>2</sub> |

| 0 | 1 | 1 | 1 | 1 | 1D3             |

| 1 | 0 | 0 | 0 | 0 | 2D <sub>0</sub> |

| 1 | 0 | 0 | 1 | 0 | 2D1             |

| 1 | 0 | 1 | 0 | 0 | 2D <sub>2</sub> |

| 1 | 0 | 1 | 1 | 1 | 2D <sub>3</sub> |

| 1 | 1 | 0 | 0 | 0 | 2D <sub>0</sub> |

| 1 | 1 | 0 | 1 | 1 | 2D1             |

| 1 | 1 | 1 | 0 | 1 | 2D <sub>2</sub> |

| 1 | 1 | 1 | 1 | 0 | 2D <sub>3</sub> |

F.Y.B.Sc.I.T

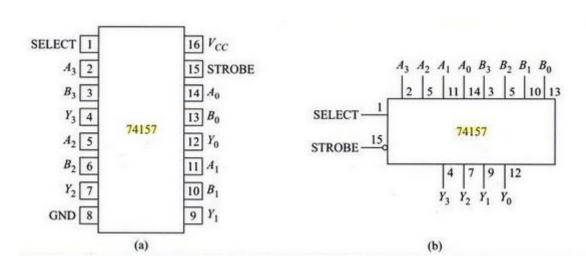

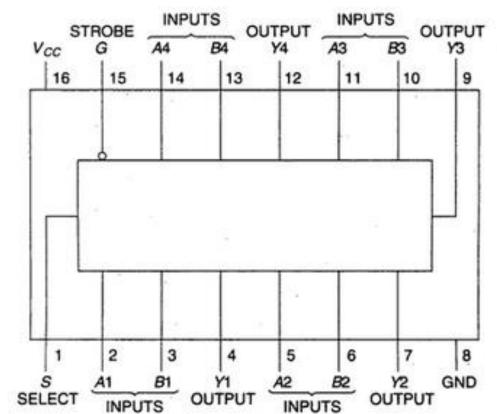

# **Design and implement 4:1 multiplexer**. Study of IC 74157 Enable E D3-Output D2-4:1 Inputs ►Y MUX D1-D0-**S1** S0 Select Data Inputs Output Y S<sub>1</sub> S<sub>0</sub> 0 0 $D_0$ 0 1 $D_1$ 0 1 $D_2$ 1 1 $D_3$

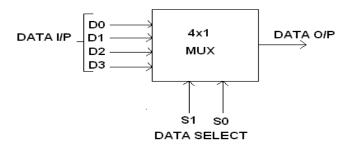

# **BLOCK DIAGRAM FOR 4:1 MULTIPLEXER:**

# **FUNCTION TABLE:**

| <b>S1</b>                                         | <b>S0</b> | INPUTS Y                      |  |  |  |  |  |  |

|---------------------------------------------------|-----------|-------------------------------|--|--|--|--|--|--|

| 0                                                 | 0         | $D0 \rightarrow D0 S1' S0'$   |  |  |  |  |  |  |

| 0                                                 | 1         | $D1 \rightarrow D1 S1' S0$    |  |  |  |  |  |  |

| 1                                                 | 0         | $D2 \rightarrow D2 S1 S0'$    |  |  |  |  |  |  |

| 1                                                 | 1         | $D3 \rightarrow D3 \ S1 \ S0$ |  |  |  |  |  |  |

| Y = D0 S1' S0' + D1 S1' S0 + D2 S1 S0' + D3 S1 S0 |           |                               |  |  |  |  |  |  |

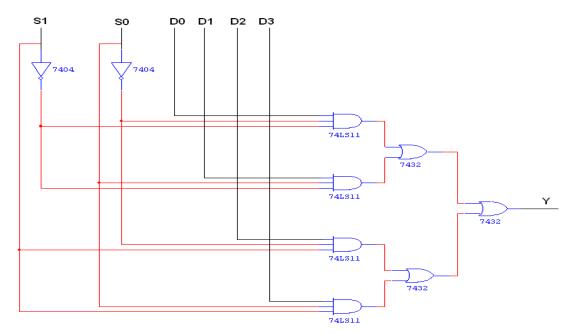

# **CIRCUIT DIAGRAM FOR MULTIPLEXER:**

| <b>S1</b> | <b>S0</b> | Y = OUTPUT |

|-----------|-----------|------------|

| 0         | 0         | D0         |

| 0         | 1         | D1         |

| 1         | 0         | D2         |

| 1         | 1         | D3         |

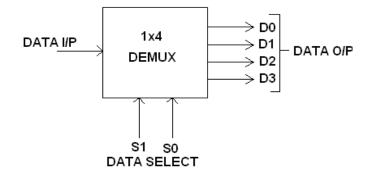

# **BLOCK DIAGRAM FOR 1:4 DEMULTIPLEXER:**

# **FUNCTION TABLE:**

| S1 | <b>S0</b> | INPUT                                                                       |

|----|-----------|-----------------------------------------------------------------------------|

| 0  | 0         | $\mathbf{X} \rightarrow \mathbf{D0} = \mathbf{X} \mathbf{S1'} \mathbf{S0'}$ |

| 0  | 1         | $X \rightarrow D1 = X S1' S0$                                               |

| 1  | 0         | $X \rightarrow D2 = X S1 S0'$                                               |

| 1  | 1         | $X \rightarrow D3 = X S1 S0$                                                |

Y = X S1' S0' + X S1' S0 + X S1 S0' + X S1 S0

|           | INPUT     |     | OUTPUT    |    |    |    |  |  |

|-----------|-----------|-----|-----------|----|----|----|--|--|

| <b>S1</b> | <b>S0</b> | I/P | <b>D0</b> | D1 | D2 | D3 |  |  |

| 0         | 0         | 0   | 0         | 0  | 0  | 0  |  |  |

| 0         | 0         | 1   | 1         | 0  | 0  | 0  |  |  |

| 0         | 1         | 0   | 0         | 0  | 0  | 0  |  |  |

| 0         | 1         | 1   | 0         | 1  | 0  | 0  |  |  |

| 1         | 0         | 0   | 0         | 0  | 0  | 0  |  |  |

| 1         | 0         | 1   | 0         | 0  | 1  | 0  |  |  |

| 1         | 1         | 0   | 0         | 0  | 0  | 0  |  |  |

| 1         | 1         | 1   | 0         | 0  | 0  | 1  |  |  |

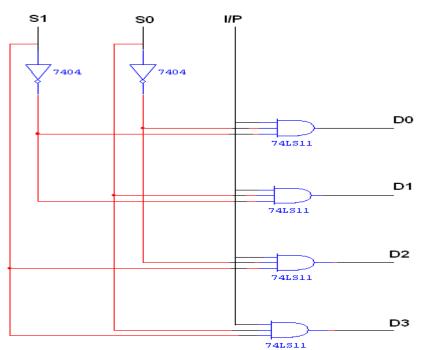

# LOGIC DIAGRAM FOR DEMULTIPLEXER:

|           | INPUT     |     | OUTPUT    |    |    |    |  |  |  |

|-----------|-----------|-----|-----------|----|----|----|--|--|--|

| <b>S1</b> | <b>S0</b> | I/P | <b>D0</b> | D1 | D2 | D3 |  |  |  |

| 0         | 0         | 0   | 0         | 0  | 0  | 0  |  |  |  |

| 0         | 0         | 1   | 1         | 0  | 0  | 0  |  |  |  |

| 0         | 1         | 0   | 0         | 0  | 0  | 0  |  |  |  |

| 0         | 1         | 1   | 0         | 1  | 0  | 0  |  |  |  |

| 1         | 0         | 0   | 0         | 0  | 0  | 0  |  |  |  |

| 1         | 0         | 1   | 0         | 0  | 1  | 0  |  |  |  |

| 1         | 1         | 0   | 0         | 0  | 0  | 0  |  |  |  |

| 1         | 1         | 1   | 0         | 0  | 0  | 1  |  |  |  |

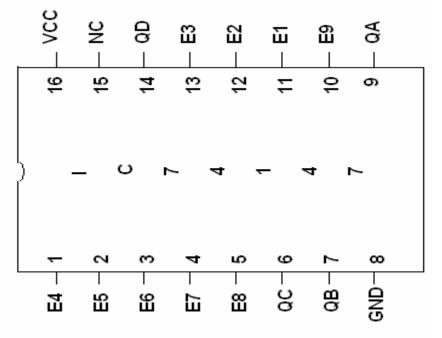

# PIN DIAGRAM FOR IC 7445: BCD TO DECIMAL DECODER:

# **PIN DIAGRAM FOR IC 74147:**

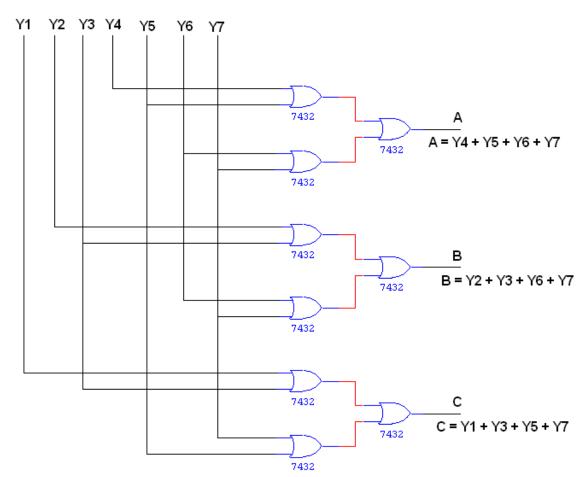

# LOGIC DIAGRAM FOR ENCODER:

# **TRUTH TABLE:**

|    |    |    | INP | UT |    |    | ( | OUTPU | Т |

|----|----|----|-----|----|----|----|---|-------|---|

| Y1 | Y2 | Y3 | Y4  | Y5 | Y6 | Y7 | Α | B     | C |

| 1  | 0  | 0  | 0   | 0  | 0  | 0  | 0 | 0     | 1 |

| 0  | 1  | 0  | 0   | 0  | 0  | 0  | 0 | 1     | 0 |

| 0  | 0  | 1  | 0   | 0  | 0  | 0  | 0 | 1     | 1 |

| 0  | 0  | 0  | 1   | 0  | 0  | 0  | 1 | 0     | 0 |

| 0  | 0  | 0  | 0   | 1  | 0  | 0  | 1 | 0     | 1 |

| 0  | 0  | 0  | 0   | 0  | 1  | 0  | 1 | 1     | 0 |

| 0  | 0  | 0  | 0   | 0  | 0  | 1  | 1 | 1     | 1 |

F.Y.B.Sc.I.T

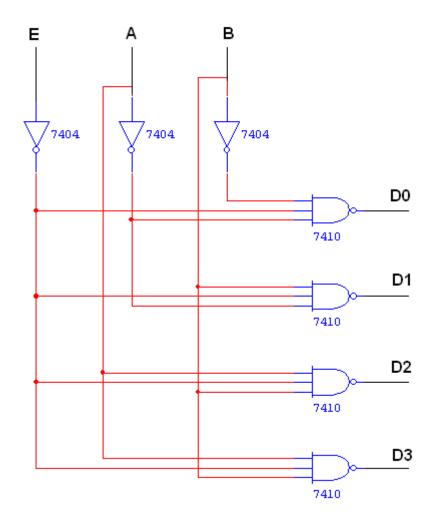

# LOGIC DIAGRAM FOR DECODER:

| INPUT |   |   | OUTPUT |    |    |    |  |

|-------|---|---|--------|----|----|----|--|

| E     | Α | В | DO     | D1 | D2 | D3 |  |

| 1     | 0 | 0 | 1      | 1  | 1  | 1  |  |

| 0     | 0 | 0 | 0      | 1  | 1  | 1  |  |

| 0     | 0 | 1 | 1      | 0  | 1  | 1  |  |

| 0     | 1 | 0 | 1      | 1  | 0  | 1  |  |

| 0     | 1 | 1 | 1      | 1  | 1  | 0  |  |

# Implement the given expression using IC

# 74151 8:1 multiplexer

Select Inputs

# **Implement the given expression using IC 74138 3:8 decoder**

| Inputs |      |    |      |   |    |    | Out | outs |    |    |    |    |

|--------|------|----|------|---|----|----|-----|------|----|----|----|----|

| En     | able | Se | lect | 1 |    |    |     |      |    |    |    |    |

| GI     | G2   | С  | B    | A | YO | Y1 | Y2  | Y3   | Y4 | Y5 | ¥6 | ¥7 |

| X      | Н    | X  | X    | X | H  | H  | H   | H    | H  | H  | H  | H  |

| L      | x    | x  | X    | X | H  | H  | H   | H    | H  | H  | H  | H  |

| H      | L    | L  | L    | L | L  | H  | H   | H    | H  | H  | H  | H  |

| H      | L    | L  | L    | H | H  | L  | H   | H    | H  | H  | H  | н  |

| H      | L.   | L  | H    | L | H  | H  | L   | H    | H  | н  | H  | н  |

| H      | L    | L  | H    | H | H  | H  | H.  | L    | H  | H  | H  | H  |

| H      | L    | н  | L    | L | H  | H  | H   | H    | L  | H  | H  | H  |

| H      | L    | н  | L    | H | H  | H  | H   | H    | H  | L  | H  | H  |

| H      | L    | н  | н    | L | H  | H  | H   | H    | H  | H  | L  | H  |

| H      | L    | н  | H    | H | H  | H  | H   | H    | H  | H  | H  | L  |

# PRACTICAL-8 Study of flip-flops and counters

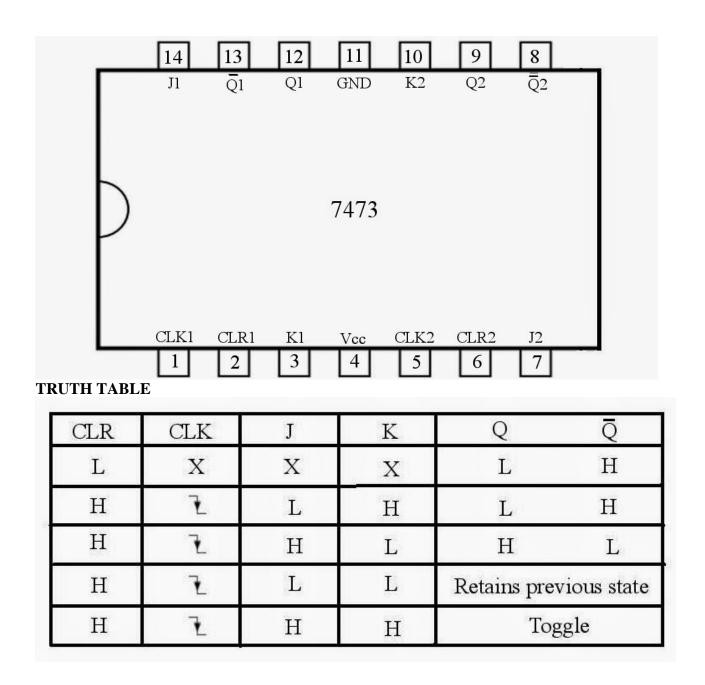

- 1. Study of IC 7473.

- 2. Study of IC 7474.

- 3. Study of IC 7476.

- 4. Conversion of Flip-flops.

- 5. Design of 3-bit synchronous counter using 7473 and required gates.

- 6. Design of 3-bit ripple counter using IC 7473.

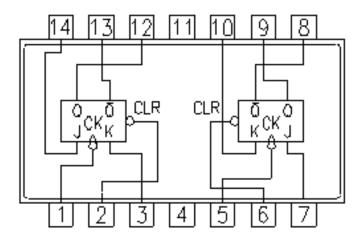

# Study of IC 7473

Each 7473 has two master-slave J K flip-flips. Half portion of IC, above VCC and ground constitutes the first flip-flop and the half portion below VCC and Ground constitutes the second master-slave flip-flop.

# Study of IC 7473

7473 Dual JK Flip-Flop with Clear Two JK Flip-Flops with Clear

7473 Dual J—K M/S Flip—Flop with Clear

| Pin Number   | Description           |

|--------------|-----------------------|

| 1            | Clock 1               |

| 2            | Clear 1               |

| 3            | K1 Input              |

| 4            | Vcc - Positive Supply |

| 5            | Clock 2               |

| 6            | Clear 2               |

| 7            | J2 Input              |

| 8            | Complement Q2 Output  |

| 9            | Q2 Output             |

| 10           | K2 Input              |

| 11 Ground    |                       |

| 12 Q1 Output |                       |

| 13           | Complement Q1 Output  |

| 14           | J1 Input              |

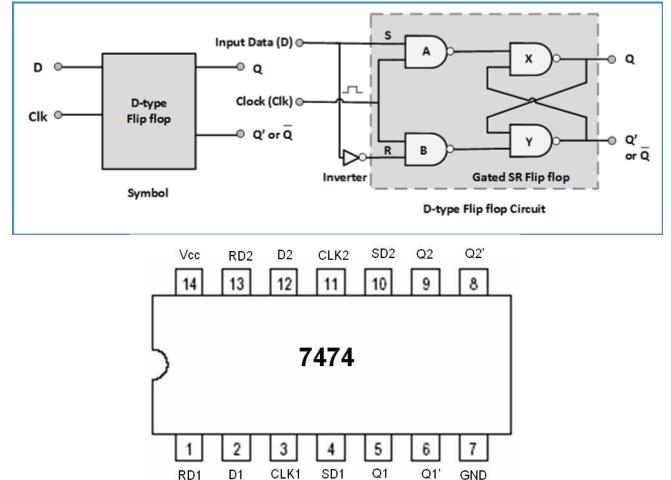

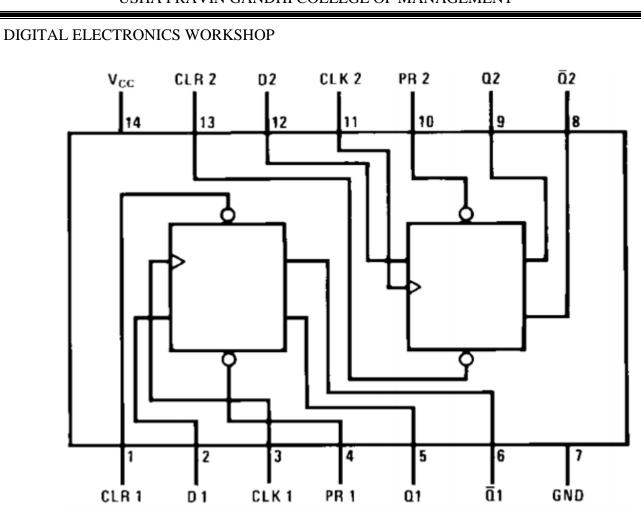

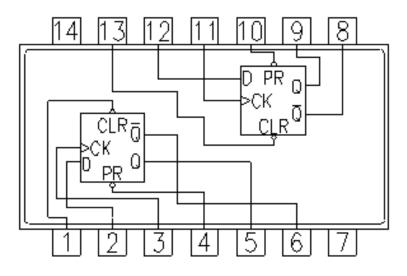

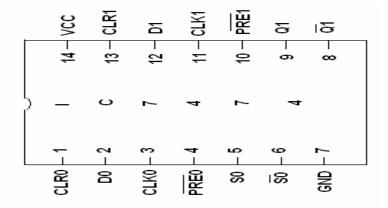

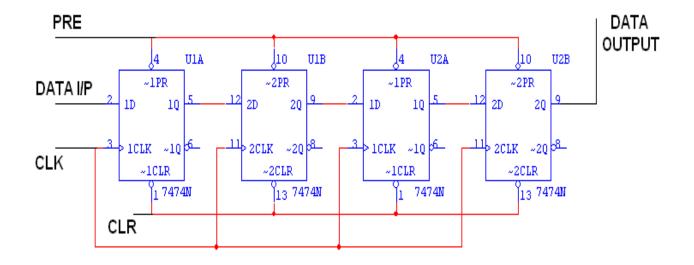

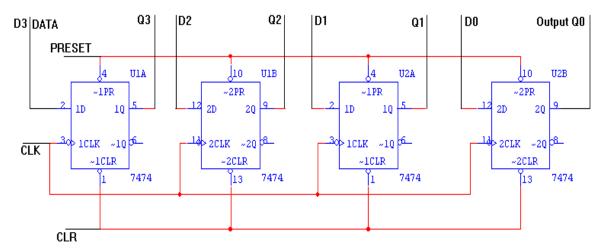

# Study of IC 7474.

IC DM74S74N is the Dual D-type Flip-flop IC, in which there are two D-type Flip-flops, which can be either used individually or as a master-slave toggle combination Pins for first D flip-flop are the left side and for second flip flop are at right side. Also there are PRE and CLR pins for both the D-type Flip-flops which are active-low pins. These pin used to SET or RESET the D-type Flip-flop respectively, regardless of INPUT D and Clock. We have connected both to Vcc to make them inactive.

### USHA PRAVIN GANDHI COLLEGE OF MANAGEMENT

# 7474 Dual D-Type Flip-Flop (Two D-Type Flip-Flops with Preset and Clear)

| Pin Number       | Description          |  |

|------------------|----------------------|--|

| 1                | Clear 1 Input        |  |

| 2                | D1 Input             |  |

| 3                | Clock 1 Input        |  |

| 4                | Preset 1 Input       |  |

| 5                | Q1 Output            |  |

| 6                | Complement Q1 Output |  |

| 7                | Ground               |  |

| 8                | Complement Q2 Output |  |

| 9                | Q2 Output            |  |

| 10               | Preset 2 Input       |  |

| 11 Clock 2 Input |                      |  |

| 12               | D2 Input             |  |

| 13               | Clear 2 Input        |  |

| 14               | Positive Supply      |  |

F.Y.B.Sc.I.T

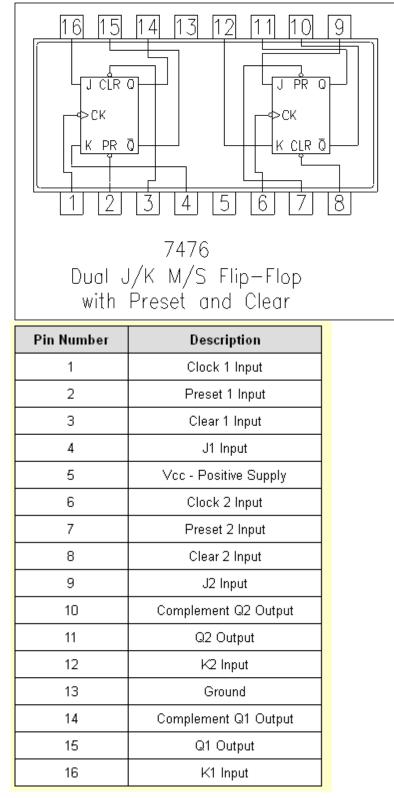

# Study of IC 7476

# 7476 Dual JK Flip-Flop with Preset and Clear

Two JK Type Master/Slave Flip-Flops with Preset and Clear

F.Y.B.Sc.I.T

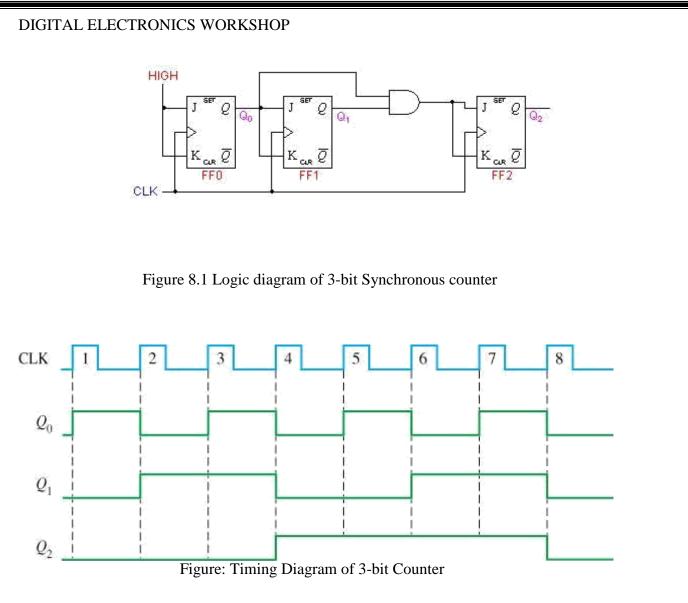

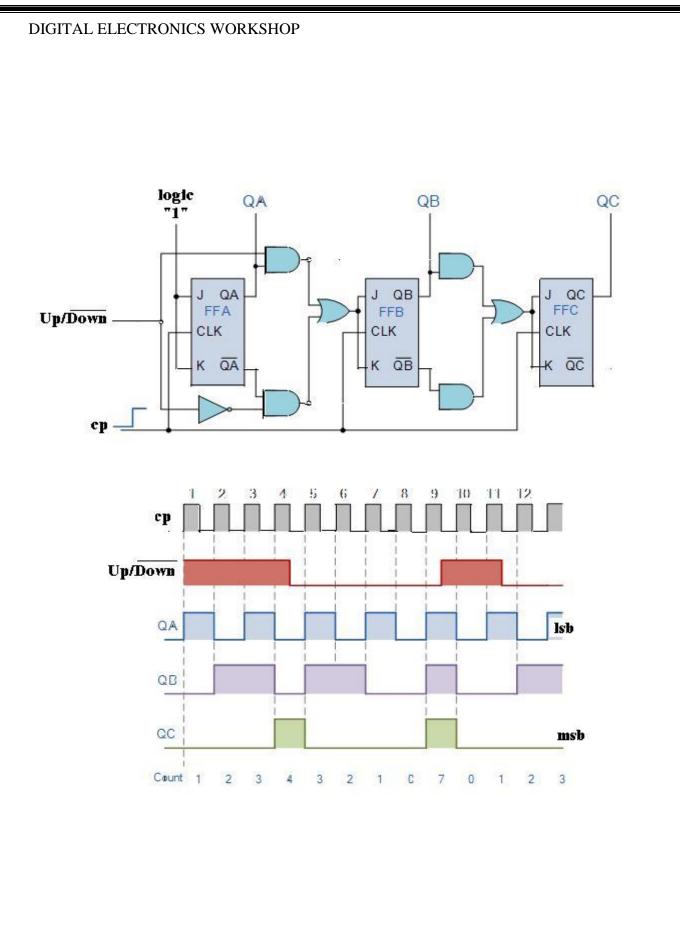

### Aim

To design and verify the truth table for 3-bit synchronous up/down counter.

#### Hardware Requirement

Equipment : Equipment : Bread Board, Power Supply, Resistors, LEDs or Digital IC Trainer Kit Discrete Components :

> IC 7473 Dual JK Flip Flop 74LS08 Quad 2 input AND gate 74LS32Quad 2 input OR gate 74LS04 Hex 1 input NOT gate

#### Theory

Circuits for counting events are frequently used in computers and other digital systems. Since a counter circuit must remember its past states, it has to possess memory. The number of flip flops used and how they are connected determine the number of states and the sequence of the states that the counter goes through in each complete cycle.

Counters can be classified into two broad categories according to the way they are clocked:

- a. Asynchronous (Ripple) Counters the first flip-flop is clocked by the external clock pulse, and then each successive flip -flop is clocked by the Q or Q' output of the previous flip -flop.

- b. Synchronous Counters all memory elements are simultaneously triggered by the same clock.

### Synchronous Counters

In *synchronous counters*, the clock inputs of all the flip-flops are connected together and are triggered by the input pulses. Thus, all the flip-flops change state simultaneously (in parallel). The circuit below is a 3-bit synchronous counter. The J and K inputs of FF0 are connected to HIGH. FF1 has its J and K inputs connected to the output of FF0, and the J and K inputs of FF2 are connected to the output of an AND gate that is fed by the outputs of FF0 and FF1. After the 3rd clock pulse both outputs of FF0 and FF1 are HIGH. The positive edge of the 4th clock pulse will cause FF2 to change its state due to the AND gate.

The most important advantage of synchronous counters is that there is no cumulative time delay because all flip -flops are triggered in parallel. Thus, the maximum operating frequency for this counter will be significantly higher than for the corresponding ripple counter.

### Lab Procedure

- 1. Construct the logic circuit as shown in figure.

- 2. Use the up/(down)' input to choose up counter or down counter.

- 3. Verify the count sequence as given in figure.

#### **PreLab** questions

1. How does synchronous counter differ from asynchronous counter?

2. A 4-bit up/down binary counter is in the DOWN mode and in the 1010 state. On the next clock pulse, to what state does the counter go?

3. How many flip-flops do you require to design Mod-7 counter.

4. Give the Transition table and excitation table of JK Flip flop.

#### Result

Thus the 3-bit synchronous up/down counter is designed and verified.

### **PostLab** questions

- 1. Draw the state Diagram, state table and Timing Diagram of a 2-bit synchronous counter.

- 2. Deign a 3-bit Up/Down Gray Code Counter using D Flip-flop

- 3. Design a 11011 sequence detector using JK flip-flops. Allow overlap.

- 4. What is decade Counter?

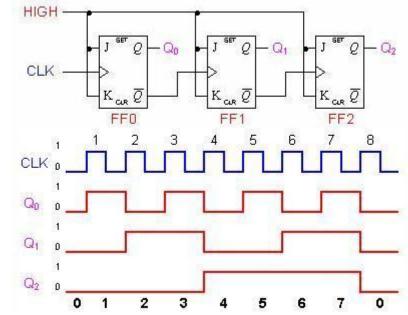

#### Aim

To design and verify the timing diagram of 3 bit Ripple Counter

#### Apparatus Required

a. Equipment : Bread Board, Power Supply, Resistors, LEDs or Digital IC Trainer Kit b. Discrete Components - IC7473 Dual JK Flip-flop

#### Theory

Asynchronous Counter is sequential circuit that is used to count the number of clock input signal. The output of one flip flop is given as a clock input to another flip-flop,

F.Y.B.Sc.I.T

so it is called as Serial Counter.

A ripple counter is an asynchronous counter where only the first flip-flop is clocked by an external clock. All subsequent flip-flops are clocked by the output of the preceding flip-flop. Asynchronous counters are also called ripple-counters because of the way the clock pulse ripples it way through the flip-flops.

The MOD of the ripple counter or asynchronous counter is  $2^n$  if n flip-flops are used. A three-bit asynchronous counter is shown on the below figure . The external clock is connected to the clock input of the first flip-flop (FF0) only. So, FF0 changes state at the falling edge of each clock pulse, but FF1 changes only when triggered by the falling edge of the Q output of FF0 similarly FF2 changes only when triggered by the falling edge of the Q output of FF1. Because of the inherent propagation delay through a flip-flop, the transition of the input clock pulse and a transition of the Q output of FF0 can never occur at exactly the same time. Therefore, the flip-flops cannot be triggered simultaneously, producing an asynchronous operation.

Usually, all the CLEAR inputs are connected together, so that a single pulse can clear all the flip-flops before counting starts. The clock pulse fed into FF0 is rippled through the other counters after propagation delays, like a ripple on water, hence the name Ripple Counter.

#### Logic Diagram with Timing Diagram:

# Truth table:

### **Counting Sequence**

### **Prelab** questions

- 1. What do you mean by Glitch?

- 2. How many flip-flops are required to produce a divide-by-64 device?

- 3. Why Asynchronous counter is called as Ripple Counter?

- 4. What do you mean by synchronous reset and asynchronous reset?

- 5. What is the use of Preset input?

- 6. What is use of Ring and Johnson's Counter?

### Lab Procedure

- 1. Construct the logic circuit as shown in Figure

- 2. Verify the count sequence as given in figure

### **Result:**

Thus the timing diagram and state diagram of 3 bit asynchronous Ripple counter was verified.

### **Postlab** questions

- 1. Draw the logic diagram of Mod 12 Asynchronous Counter and its timing diagram.

- 2. Design a 4-bit frequency divider.

- 3. Design a sequential circuit that is used to generate the timing signals with a combination of Shift register and a decoder.

- 4. What is state table?

# **PRACTICAL-9**

# Study of counter ICs and designing Mod-N counters

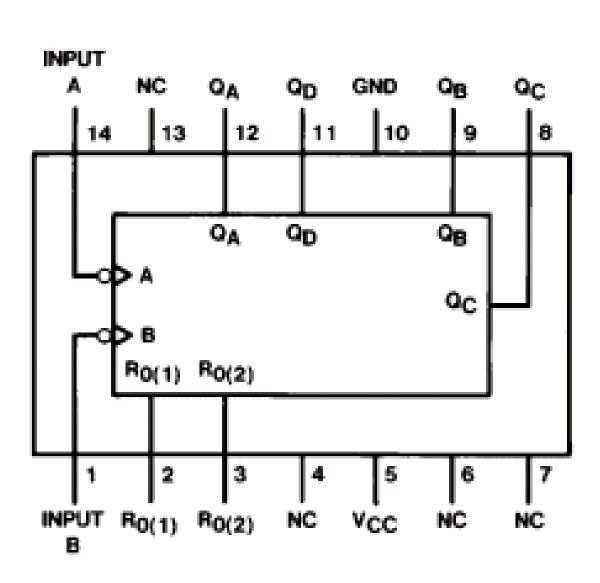

- 1. Study of IC 7490, 7492, 7493 and designing mod-n counters using these.

- 2. Designing mod-n counters using IC 7473 and 7400 (NAND gates)

| IC No. Description |                                  | Features    | Group |

|--------------------|----------------------------------|-------------|-------|

| 7490, 74290        | BCD counter                      | Set, reset  | A     |

| 7492               | Divide-by-12 counter             | Reset       | B     |

| 7493, 74293        | 4-bit binary counter             | Reset       | B     |

| 74176, 74196       | Presettable BCD counter          | Reset, load | C     |

| 74177, 74197       | Presettable 4-bit binary counter | Reset, load | C     |

| 74390              | Dual decade counters             | Reset       | B     |

| 74393              | Dual 4-bit binary counters       | Reset       | B     |

| 74490              | Dual BCD counters                | Set, reset  | A     |

#### Available asynchronous counter ICs

#### 9.1 Aim

The purpose of this experiment is to introduce the design of Mod-N Counter and to implement it using suitable Flip-flops.

#### 9.2 Hardware Requirement

Equipment : Bread Board, Power Supply, Resistors, LEDs or Digital IC Trainer Kit Discrete Components : IC 7473 Dual JK Flip Flop IC 7400 NAND Gate

#### IC /400 NAND C

### 9.3 Theory:

Circuits for counting events are frequently used in computers and other digital systems. Since a counter circuit must remember its past states, it has to possess memory. The number of flip flops used and how they are connected determine the number of states and the sequence of the states that the counter goes through in each complete cycle.

Counters can be classified into two broad categories according to the way they are clocked: 1. Asynchronous (Ripple) Counters - the first flip-flop is clocked by the external clock pulse, and then each successive flip -flop is clocked by the Q or Q' output of the previous flip -flop.

2. Synchronous Counters - all memory elements are simultaneously triggered by the same clock.

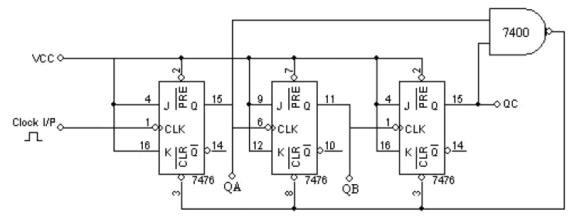

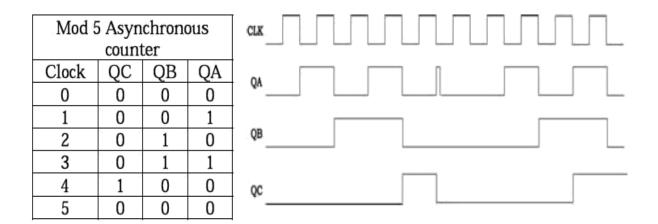

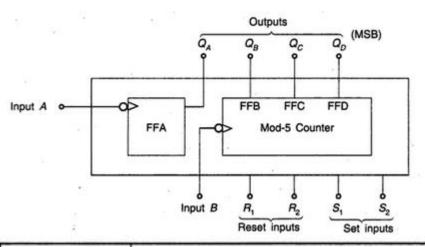

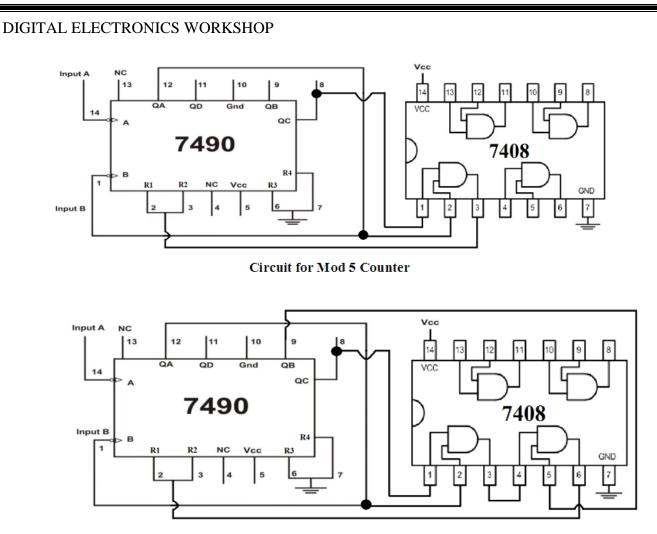

A mod N counter is a counter that has N states. Its output frequency is f/N. A counter which is reset at the fifth clock pulse is called Mod 5 counter or Divide by 5 counter. The circuit diagram of Mod 5 counter is shown in the figure. This counter contains three JKMS flip-flop.

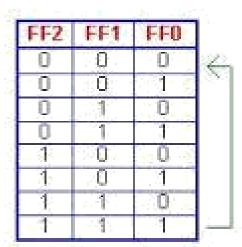

### Mod 5 Asynchronous Counter:-

A 3 bit binary counter is normally counting from 000 to 111. The actual output of a 3 bit binary counter at the fifth clock pulse is 101. A two input NAND gate is used to make a Mod 5 counter.

The outputs of the first and third flip flops (QA and QC) are connected to the input of the give NAND gate, and its output is connected to the RESET terminal of the counter, Hence the counter is reset at the fifth clock pulse, which produces the output QC,QB,QA as 000. It is called divide by 5th counter or mod 5 counter.

### 9.4 Lab Procedure

- 1. Connections are made as per circuit diagram.

- 2. Clock pulses are applied one by one at the clock I/P and the O/P is observed at QA, QB & QC for IC 7476.

- 3. Truth table is verified.

### 9.5 Prelab questions

- 1. Which flipflop is suitable for counter? Why?

- 2. Draw the timing diagrams for mod 6 counter.

### 9.6 Result

Thus the Mod-5 counter is designed and verified.

F.Y.B.Sc.I.T

#### 9.7 PostLab questions

- 1 Draw the state Diagram, state table and Timing Diagram of a 2-bit synchronous counter.

- 2 Design a modulus seven synchronous counter that can count 0, 3, 5, 7, 9, 11, and 12 using D flip-flop.

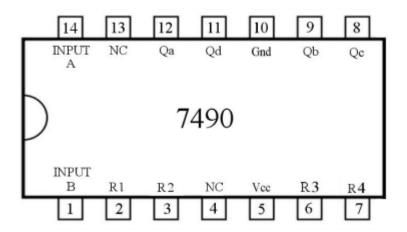

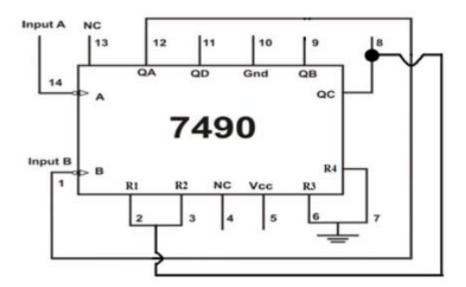

# Study of IC 7490

- The 74LS90 is a simple counter, it can count from 0 to 9 cyclically in its natural mode.

- It counts the input pulses and the output is received as a 4 bit binary number through pins

# $Q_A, Q_B, Q_C \text{ and } Q_D.$

| Counter state |       | FLIP-FLC | P outputs |    |

|---------------|-------|----------|-----------|----|

| 4             | $Q_D$ | Qc       | $Q_B$     | QA |

| 0             | 0     | 0        | 0         | 0  |

| 1             | 0     | 0        | 0         | 1  |

| 2             | 0     | 0        | -1        | 0  |

| 3             | 0     | 0        | 1         | 1  |

| 4             | 0     | 1 .      | 0         | 0  |

| 5             | 0     | 1        | 0         | 1  |

| 6             | 0     | 1        | 1         | 0  |

| 7             | 0     | 1        | 1         | 1  |

| 8             | 1     | 0        | 0         | 0  |

| 9             | 1     | 0        | 0         | 1  |

| 10            | 0     | 0        | 0         | 0  |

#### USHA PRAVIN GANDHI COLLEGE OF MANAGEMENT

**Circuit for Mod 7 Counter**

**Circuit for Mod 4 Counter**

# Study of IC 7492

74LS92 (Divide by 12 Counter)

| Count |    | Output |    |   |  |  |

|-------|----|--------|----|---|--|--|

|       | QA | QB     | Qc | Q |  |  |

| 0     | L  | L      | L  | L |  |  |

| 1     | н  | L      | L  | L |  |  |

| 2     | L  | н      | L  | L |  |  |

| 3     | н  | н      | L  | L |  |  |

| 4     | L  | L      | н  | L |  |  |

| 5     | н  | L      | н  | L |  |  |

| 6     | L  | L      | L  | н |  |  |

| 7     | н  | L      | L  | н |  |  |

| 8     | L  | н      | L  | н |  |  |

| 9     | н  | н      | L  | н |  |  |

| 10    | L  | L      | н  | н |  |  |

| 11    | н  | L      | н  | н |  |  |

F.Y.B.Sc.I.T

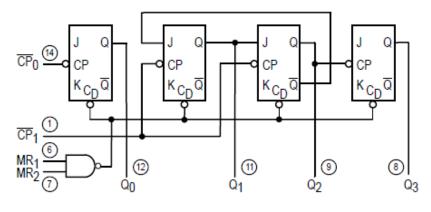

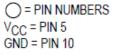

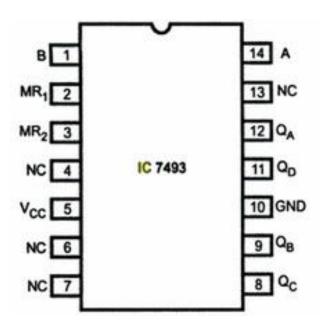

# Study of IC 7493

# 4-bit BINARY COUNTER

| Count | 129.04 | Out | tput |    |

|-------|--------|-----|------|----|

|       | QA     | QB  | Qc   | QD |

| 0     | L      | L   | L    | L  |

| 1     | н      | L   | L    | L  |

| 2     | L      | н   | L    | L  |

| 3     | н      | н   | L    | L  |

| 4     | L      | L   | н    | L  |

| 5     | н      | L   | н    | L  |

| 6     | L      | н   | н    | L  |

| 7     | н      | н   | н    | L  |

| 8     | L      | L   | L    | н  |

| 9     | н      | L   | L    | н  |

| 10    | L      | н   | L    | н  |

| 11    | н      | н   | L    | н  |

| 12    | L      | L   | н    | н  |

| 13    | н      | L   | н    | н  |

| 14    | L      | н   | н    | н  |

| 15    | н      | н   | н    | н  |

F.Y.B.Sc.I.T

81 | P a g e

Order Number DM7493AN See NS Package Number N14A

# **PRACTICAL-10**

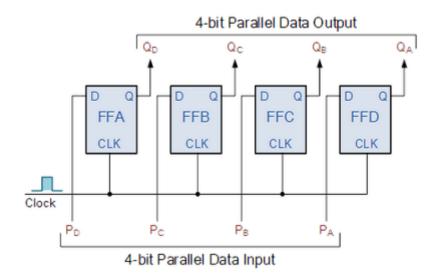

# Design of shift registers and shift register counters

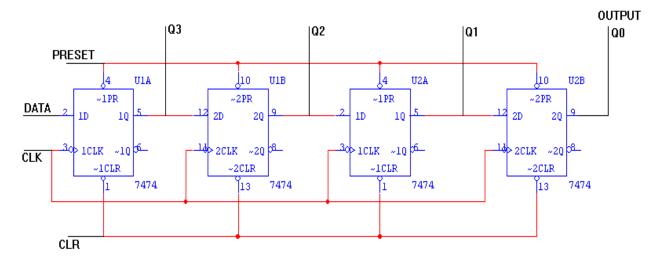

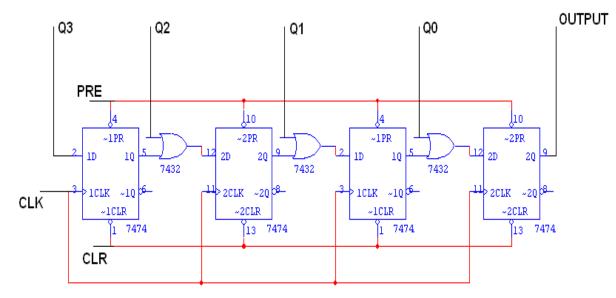

- 1. Design serial in serial out, serial in parallel out, parallel – in serial – out, parallel – in parallel – out and bidirectional shift registers using IC 7474

- 2. Study of IC 7495.

- 3. Implementation of digits using seven segment displays.

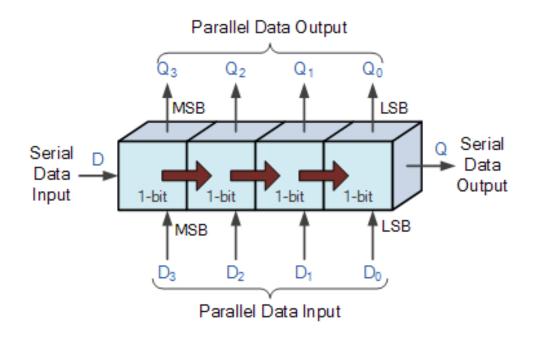

# **The Shift Register**

- The **Shift Register** is another type of sequential logic circuit that can be used for the storage or the transfer of data in the form of binary numbers.

- This sequential device loads the data present on its inputs and then moves or "shifts" it to its output once every clock cycle, hence the name "shift register".

- Universal shift registers are very useful digital devices.

- They can be configured to respond to operations that require some form of temporary memory storage or for the delay of information such as the SISO or PIPO configuration modes or transfer data from one point to another in either a serial or parallel format.

- Universal shift registers are frequently used in arithmetic operations to shift data to the left or right for multiplication or division.

## **PIN DIAGRAM:**

# LOGIC DIAGRAM:

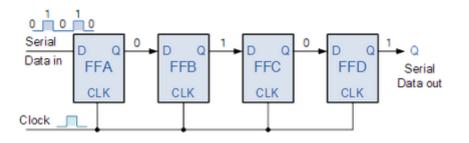

# SERIAL IN SERIAL OUT:

## **TRUTH TABLE:**

|     | Serial in | Serial out |

|-----|-----------|------------|

| CLK |           |            |

| 1   | 1         | 0          |

| 2   | 0         | 0          |

| 3   | 0         | 0          |

| 4   | 1         | 1          |

| 5   | Х         | 0          |

| 6   | Х         | 0          |

| 7   | X         | 1          |

# 4-bit Serial-in to Serial-out Shift Register

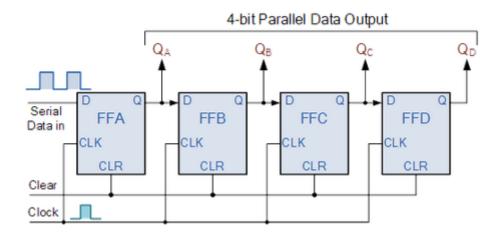

# LOGIC DIAGRAM:

# SERIAL IN PARALLEL OUT:

### **TRUTH TABLE:**

|     |      | OUTPUT |    |    |    |  |  |

|-----|------|--------|----|----|----|--|--|

| CLK | DATA | QA     | QB | Qc | QD |  |  |

| 1   | 1    | 1      | 0  | 0  | 0  |  |  |

| 2   | 0    | 0      | 1  | 0  | 0  |  |  |

| 3   | 0    | 0      | 0  | 1  | 1  |  |  |

| 4   | 1    | 1      | 0  | 0  | 1  |  |  |

# 4-bit Serial-in to Parallel-out Shift Register

# LOGIC DIAGRAM:

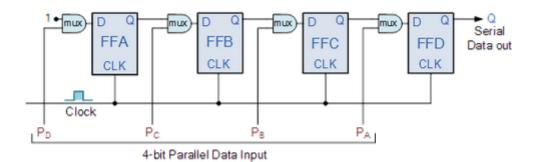

# PARALLEL IN SERIAL OUT:

## **TRUTH TABLE:**

| CLK | Q3 | Q2 | Q1 | Q0 | O/P |

|-----|----|----|----|----|-----|

| 0   | 1  | 0  | 0  | 1  | 1   |

| 1   | 0  | 0  | 0  | 0  | 0   |

| 2   | 0  | 0  | 0  | 0  | 0   |

| 3   | 0  | 0  | 0  | 0  | 1   |

# 4-bit Parallel-in to Serial-out Shift Register

# LOGIC DIAGRAM:

## PARALLEL IN PARALLEL OUT:

## **TRUTH TABLE:**

|     | DATA INPUT |                |                |    | OUTPUT |    |    |    |

|-----|------------|----------------|----------------|----|--------|----|----|----|

| CLK | DA         | D <sub>B</sub> | D <sub>C</sub> | DD | QA     | QB | Qc | QD |

| 1   | 1          | 0              | 0              | 1  | 1      | 0  | 0  | 1  |

| 2   | 1          | 0              | 1              | 0  | 1      | 0  | 1  | 0  |

4-bit Parallel-in to Parallel-out Shift Register

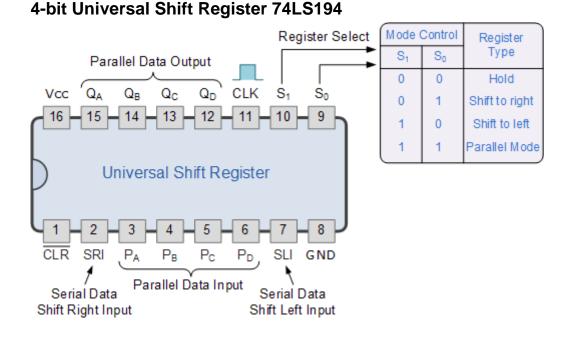

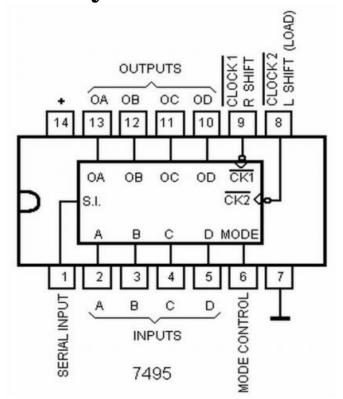

# Study of IC 7495

IC 7495:

#### **OPERATION OF 7495:**

Mode-0 for serial shifting of data Mode-1 for parallel loading of data Clk 1 is used for right shifting of data Clk 2 is used for left shifting of data and for parallel loading of data A, B, C, D – Parallel data inputs QA, QB, QC, QD - Outputs

#### Circuit for Ring Counter :

#### State Table

| Clk | QA      | QB | Qc | QD |  |  |  |

|-----|---------|----|----|----|--|--|--|

| 1   | 1       | 0  | 0  | 0  |  |  |  |

| 2   | 0       | 1  | 0  | 0  |  |  |  |

| 3   | 0       | 0  | 1  | 0  |  |  |  |

| 4   | 0       | 0  | 0  | 1  |  |  |  |

| 5   | 1       | 0  | 0  | 0  |  |  |  |

| 6   | Repeats |    |    |    |  |  |  |

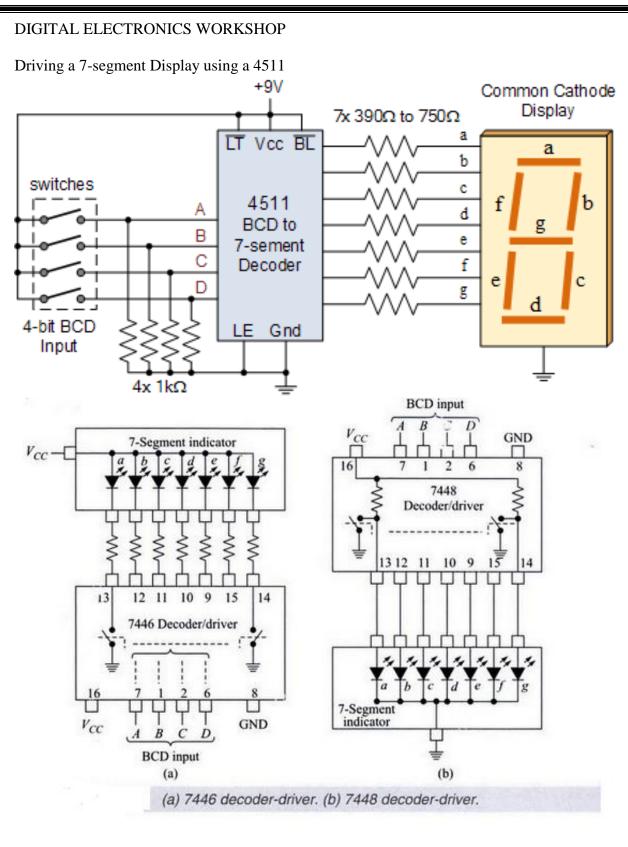

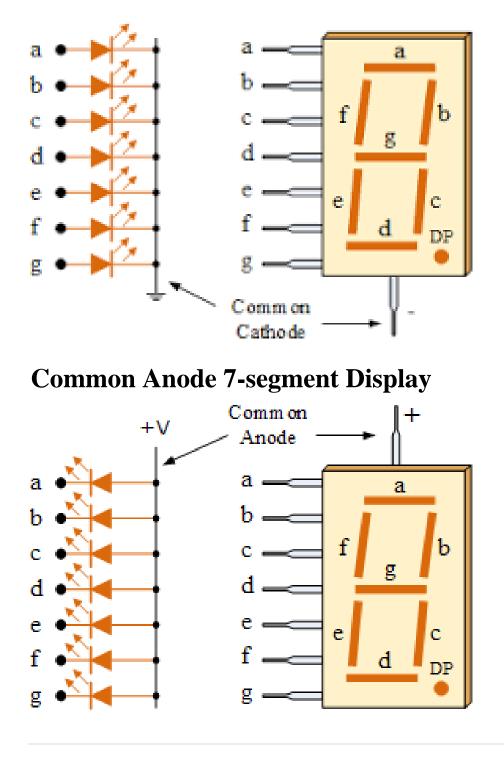

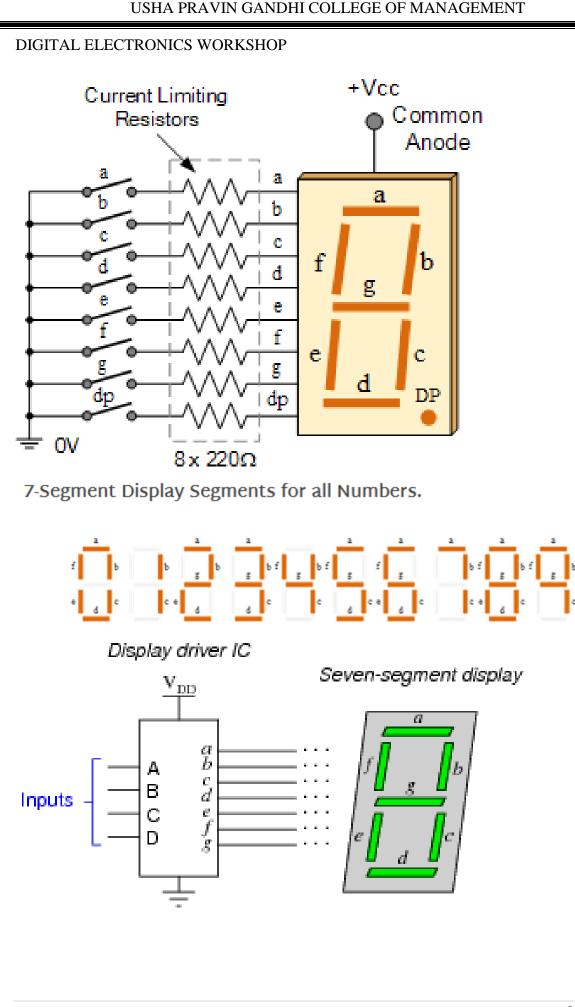

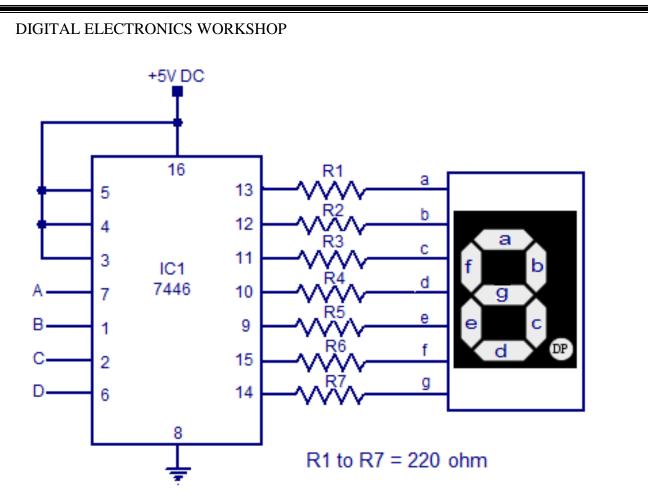

# Implementation of digits using seven segment displays

# **Common Cathode 7-segment Display**

F.Y.B.Sc.I.T

92 | P a g e

|   |   | Segn | 7 Segment Display Output |   |   |   |   |

|---|---|------|--------------------------|---|---|---|---|

| а | b | с    | d                        | е | f | g |   |

| 0 | 0 | 0    | 0                        | 0 | 0 | 1 | 0 |

| 1 | 0 | 0    | 1                        | 1 | 1 | 1 | 1 |

| 0 | 0 | 1    | 0                        | 0 | 1 | 0 | 2 |

| 0 | 0 | 0    | 0                        | 1 | 1 | 0 | 3 |

| 1 | 0 | 0    | 1                        | 1 | 0 | 0 | 4 |

| 0 | 1 | 0    | 0                        | 1 | 0 | 0 | 5 |

| 0 | 1 | 0    | 0                        | 0 | 0 | 0 | 6 |

| 0 | 0 | 0    | 1                        | 1 | 1 | 1 | 7 |

| 0 | 0 | 0    | 0                        | 0 | 0 | 0 | 8 |

| 0 | 0 | 0    | 0                        | 1 | 1 | 0 | 9 |