The documentation and process conversion measures necessary to comply with this revision shall be completed by 18 February 2018.

INCH-POUND

MIL-STD-750-4 w/CHANGE 2 18 August 2017 SUPERSEDING MIL-STD-750-4 w/CHANGE 1 15 August 2014 (see 6.4)

# **DEPARTMENT OF DEFENSE**

# **TEST METHOD STANDARD**

# DIODE ELECTRICAL TEST METHODS FOR SEMICONDUCTOR DEVICES

PART 4: TEST METHODS 4000 THROUGH 4999

AMSC N/A

#### **FOREWORD**

- 1. This standard is approved for use by all Departments and Agencies of the Department of Defense.

- 2. This issue of MIL-STD-750-4 establishes uniform test methods for testing the electrical characteristics of diodes, microwave diodes, thyristors, and tunnel diodes.

- 3. Comments, suggestions, or questions on this document should be addressed to: Commander, Defense Logistics Agency, DLA Land and Maritime, ATTN: VAC, P.O. Box 3990, Columbus, OH 43218–3990, or emailed 750.TestMethods@dla.mil. Since contact information can change, you may want to verify the currency of this address information using the ASSIST Online database at https://assist.dla.mil.

# SUMMARY OF CHANGE 2 MODIFICATIONS

- 1. Paragraph 1.3 has been added to address method of reference.

- 2. Paragraphs 3.1.1, 3.1.2 and 3.1.3 have been added to separate acronyms from symbols from terms used throughout the standard. Acronyms used in various test methods have been added. Acronyms not used in any test methods have been deleted.

- 3. Test method 4011 was reformatted and revised to correct errors and include requirements to allow the use of automatic test equipment.

- 4. Test method 4026 was reformatted and revised to correct errors and to standardize the definitions and symbols used.

- 5. The following modifications to MIL-STD-750-4 have been made:

| <u>Paragraph</u>                                                          | Modification                                                  |

|---------------------------------------------------------------------------|---------------------------------------------------------------|

| 1.3<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.3.1<br>3.1.3.2<br>4.6<br>6.4<br>6.5 | Added. Changed. Added. Added. Added. Added. Deleted. Changed. |

| Test Method                                                               | Modification                                                  |

| 4011<br>4026                                                              | Revised.<br>Revised.                                          |

|         | )<br>DF CHANGE 2 MODIFICATIONS                                                  |

|---------|---------------------------------------------------------------------------------|

|         |                                                                                 |

|         | OPE                                                                             |

| 1.1     | Purpose                                                                         |

| 1.2     | Numbering system                                                                |

| 1.2.1   | Classification of tests                                                         |

| 1.2.2   | Test method revisions                                                           |

| 1.3     | Methods of reference                                                            |

| 2. AF   | PLICABLE DOCUMENTS                                                              |

| 2.1     | General                                                                         |

| 2.2     | Government documents                                                            |

| 2.2.1   | Specifications, standards, and handbooks                                        |

| 2.3     | Non-Government publications                                                     |

| 2.4     | Order of precedence                                                             |

|         | ·                                                                               |

|         | FINITIONS                                                                       |

| 3.1     | Acronyms, symbols, and terms                                                    |

| 3.1.1   | Acronyms used in this standard                                                  |

| 3.1.2   | Symbols used in this standard                                                   |

| 3.1.3   | Terms used in this standard                                                     |

| 3.1.3.1 | NPN                                                                             |

| 3.1.3.2 | PNP                                                                             |

| 4. GE   | NERAL REQUIREMENTS                                                              |

| 4.1     | General                                                                         |

| 4.2     | Test conditions for electrical measurements                                     |

| 4.2.1   | Steady-state dc measurements (test method series 4000)                          |

| 4.2.2   | Pulse measurements (test method series 4000)                                    |

| 4.2.3   | Electrical characteristics tests for microwave diodes (test method series 4100) |

| 4.2.4   | Test circuits                                                                   |

| 4.3     | Non-destructive tests                                                           |

| 4.4     | Destructive tests                                                               |

| 4.5     | Laboratory suitability                                                          |

| 5. DE   | TAILED REQUIREMENTS                                                             |

| 6. NC   | DTES                                                                            |

| 6.1     | Intended use                                                                    |

| 6.2     | International standardization agreement                                         |

| 6.3     | Subject term (key word) listing                                                 |

| 6.4     | Supersession data.                                                              |

| 6.5     | Changes from previous issue                                                     |

|         |                                                                                 |

| <u>FIGURE</u>    | TITLE                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------|

| 4001–1           | Test circuit for capacitance                                                                         |

| 4011–1           | Test circuits for forward voltage                                                                    |

| 4016–1           | Test circuit for reverse current leakage (dc method)                                                 |

| 4016–2           | Test circuit for reverse current leakage (ac method)                                                 |

| 4021–1           | Test circuit for breakdown voltage (diodes)                                                          |

| 4022–1           | Test circuit for breakdown voltage (voltage regulators and voltage – reference diodes)               |

| 4023–1           | Ideal reverse trace                                                                                  |

| 4023–2           | Soft knee                                                                                            |

| 4023–3           | Drift                                                                                                |

| 4023–4           | Slope                                                                                                |

| 4023–5           | Double break (reject criteria for sharp knee devices                                                 |

| 4023–6           | Double trace                                                                                         |

| 4023–7           | Double trace, soft knee                                                                              |

| 4023-8           | Unstable (jitter)                                                                                    |

| 4023–9           | Discontinuity                                                                                        |

| 4023–10          | Snap back – collapsing V <sub>BR</sub>                                                               |

| 4023–11          | Floater                                                                                              |

| 4023–12          | Arcing                                                                                               |

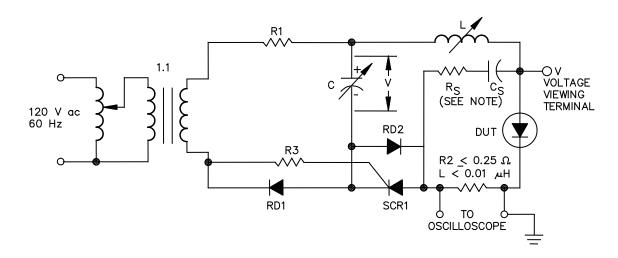

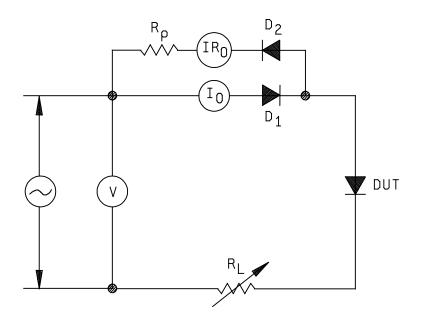

| 4026–1           | Test circuit for forward recovery time and peak forward recovery voltage                             |

| 4026–2<br>4031–1 | Input forward current pulse and output voltage waveforms Test circuit for condition A                |

| 4031–1           |                                                                                                      |

| 4031–2           | Response pulse waveforms for condition A Test circuit for condition B                                |

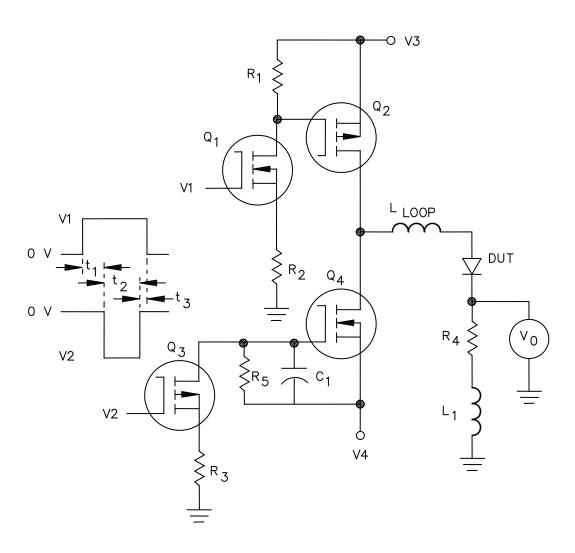

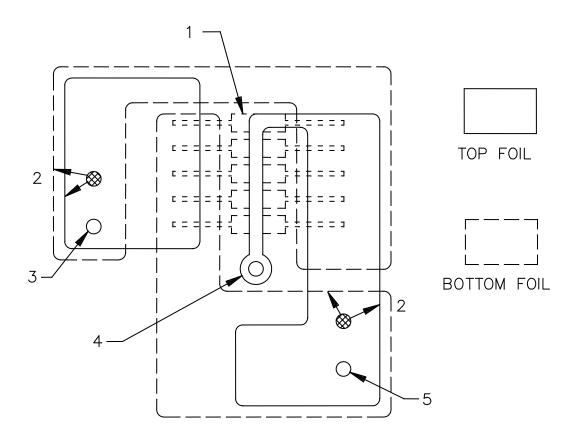

| 4031–4           | Suggested board layout for low L <sub>1</sub> /R <sub>4</sub> for condition B                        |

| 4031–5           | Current through DUT (condition B)                                                                    |

| 4031–6           | Circuit for measuring reverse recovery characteristics (condition C)                                 |

| 4031–7           | Test current waveforms for various types of rectifier diodes under test in the circuit for measuring |

| 4001-7           | reverse recovery characteristics                                                                     |

| 4031–8           | Test circuit for condition D                                                                         |

| 4031–9           | Suggest board layout for low L <sub>1</sub> /R <sub>4</sub> for test condition D                     |

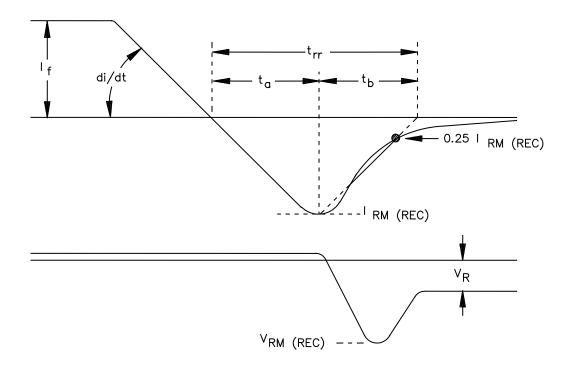

| 4031–10          | Generalized reverse recovery waveforms for test condition D                                          |

| 4036–1           | Test circuit for measuring Q                                                                         |

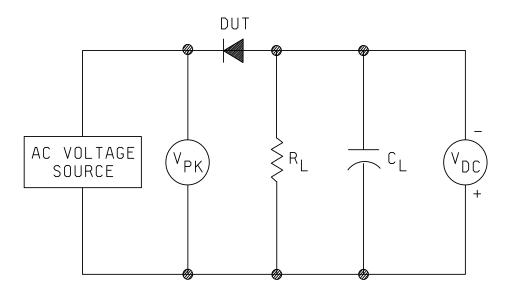

| 4041–1           | Test circuit for rectification efficiency                                                            |

| 4046–1           | Test circuit for reverse current, average                                                            |

| 4051–1           | Test circuit for small-signal reverse breakdown impedance                                            |

| 4056–1           | Test circuit for small-signal forward impedance                                                      |

| 4061–1           | Test circuit for stored charge                                                                       |

| 4064-1           | Test circuit 1                                                                                       |

| 4064-2           | Test circuit 1 response                                                                              |

| 4064-3           | Test Circuit 2                                                                                       |

| 4064-4           | Test Circuit 2 response                                                                              |

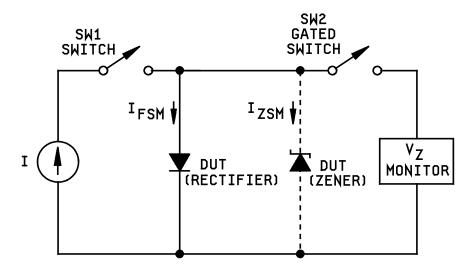

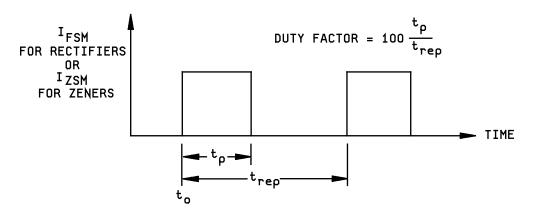

| 4065-1           | Rectangular current pulse test setup                                                                 |

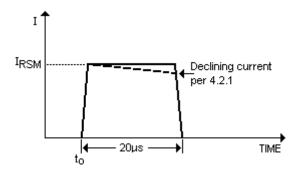

| 4065-2           | Rectangular 20µs Current Pulse Waveform                                                              |

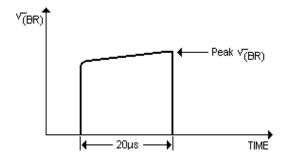

| 4065-3           | Voltage response                                                                                     |

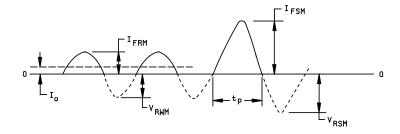

| 4066-1           | Surge pulse applied to continuous halfwave conditions (condition A1)                                 |

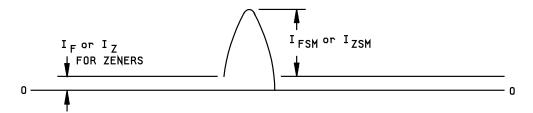

| 4066–2           | Surge pulse applied to continuous dc conditions (condition A2)                                       |

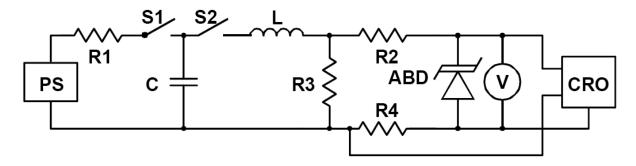

| 4066-3           | Rectangular current pulse test setup                                                                 |

| 4066-4           | Rectangular current pulse waveforms                                                                  |

| 4066-5           | Clamping voltage test circuit                                                                        |

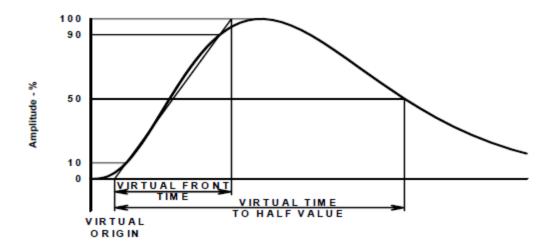

| 4066-6           | Standard current impulse waveshape                                                                   |

| <u>FIGURE</u>     | <u>TITLE</u>                                                                                                 |

|-------------------|--------------------------------------------------------------------------------------------------------------|

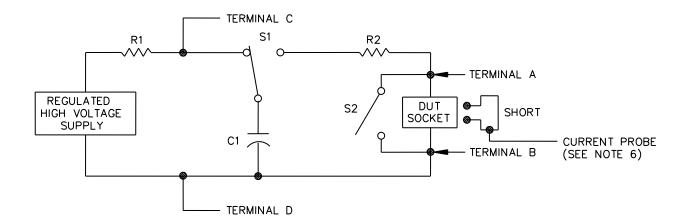

| 4066–7            | ESD test circuit (human body model)                                                                          |

| 4066-8            | ESD test circuit waveforms (human body model)                                                                |

| 4076–1            | Test circuit for saturation current                                                                          |

| 4081–1            | Test circuit                                                                                                 |

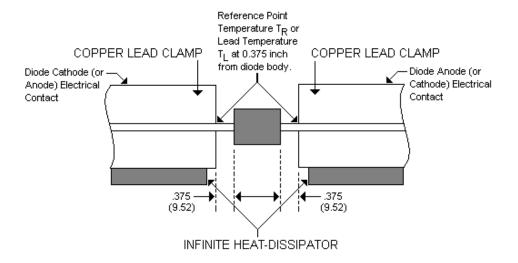

| 4081–2            | Axial-leaded mounting arrangement                                                                            |

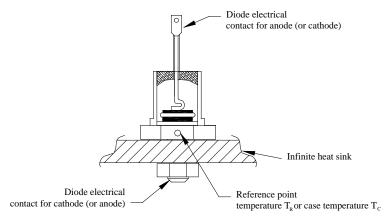

| 4081–3            | Case mounting arrangement (stud packages)                                                                    |

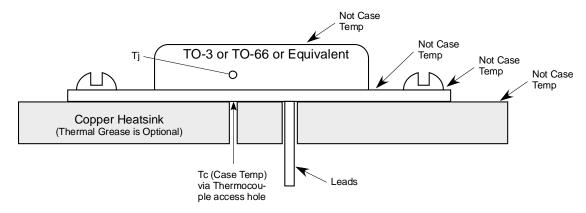

| 4081–4            | Case mounting arrangement (TO-3 or TO-66)                                                                    |

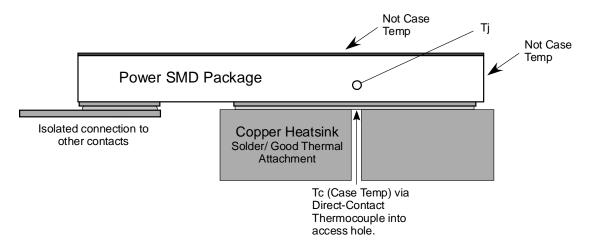

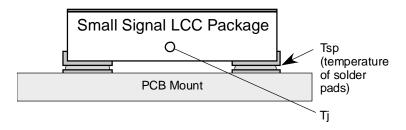

| 4081–5            | Surface-Mount arrangement and Temperature Sensing Location (SMD)                                             |

| 4081–6            | Surface-Mount arrangement and Temperature Sensing Location (LCC)                                             |

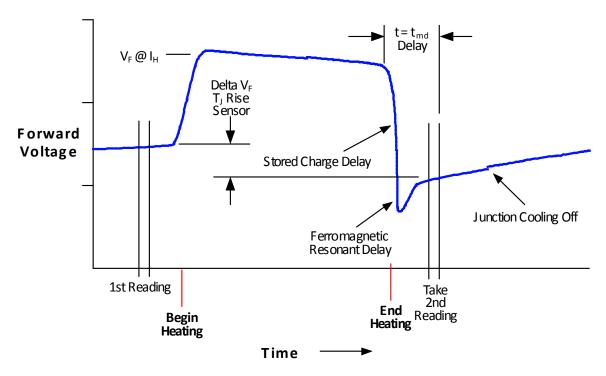

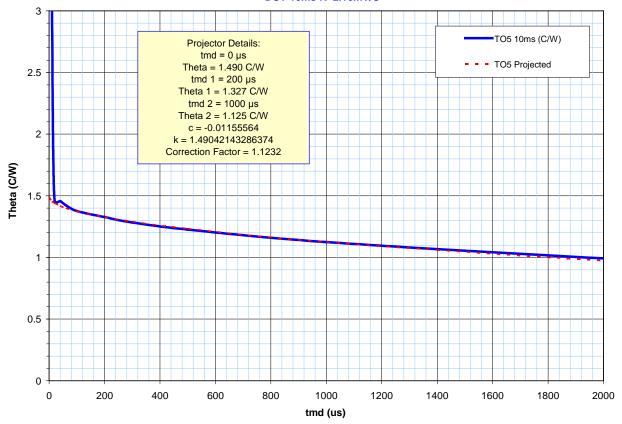

| 4081–A1           | Analysis of theta test                                                                                       |

| 4081–A2           | Theta vs. t <sub>MD</sub>                                                                                    |

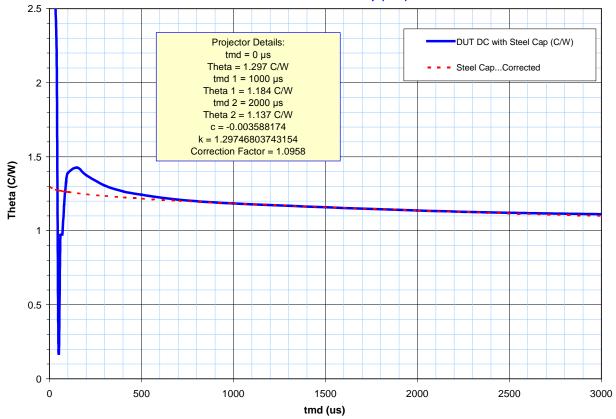

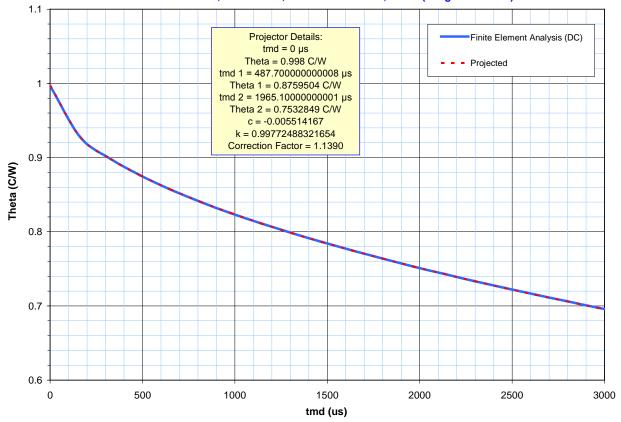

| 4081–A3           | Theta vs. t <sub>MD</sub>                                                                                    |

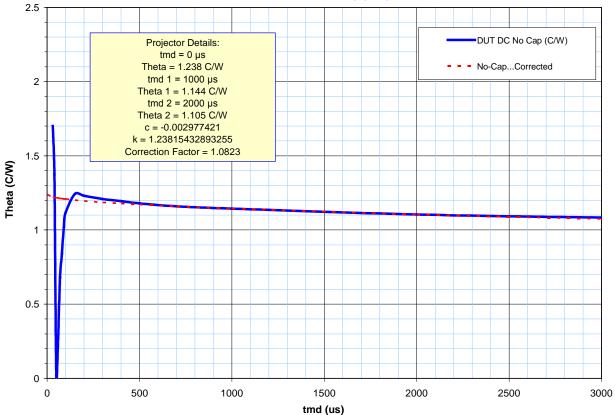

| 4081–A4           | Theta vs. t <sub>MD</sub>                                                                                    |

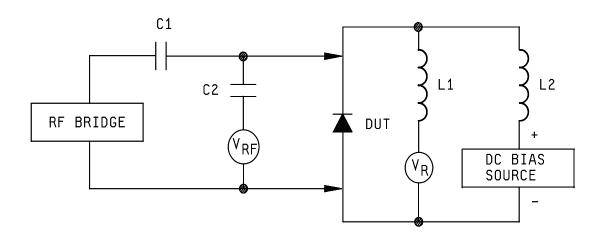

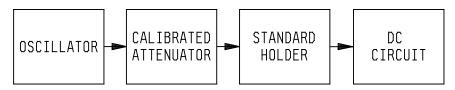

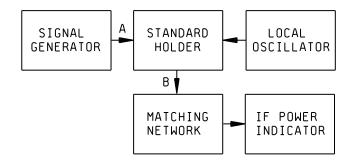

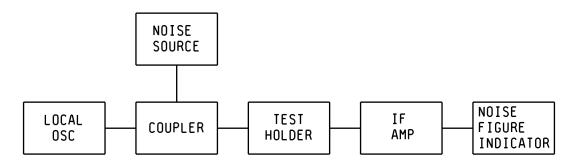

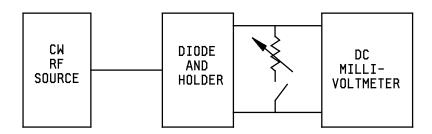

| 4081–A5<br>4101–1 | Theta vs. t <sub>MD</sub> Test setup for incremental measurement                                             |

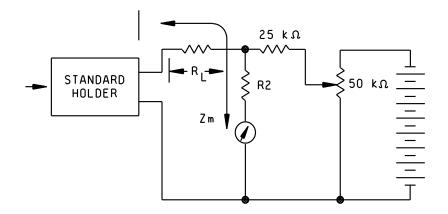

| 4101–1            | Open circuit for the incremental measurement                                                                 |

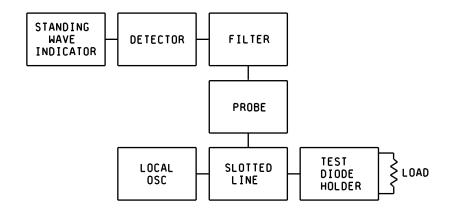

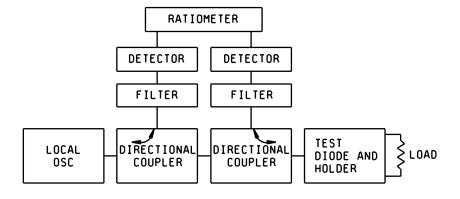

| 4101–3            | Test setup for heterodyne measurement                                                                        |

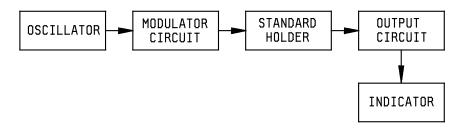

| 4101–4            | Test setup for modulation measurement                                                                        |

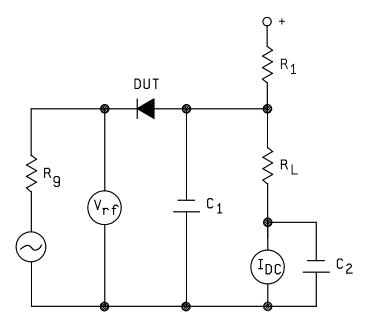

| 4106–1            | Test circuit for detector power efficiency                                                                   |

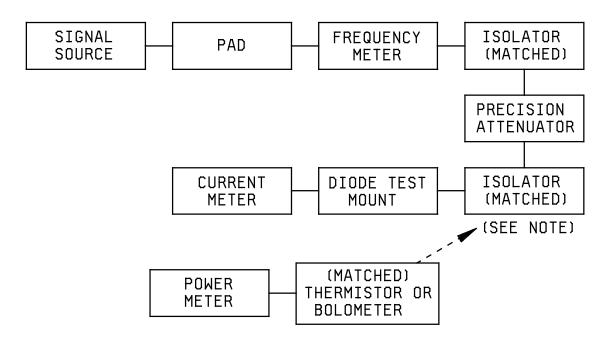

| 4111–1            | Test setup for figure of merit measurement                                                                   |

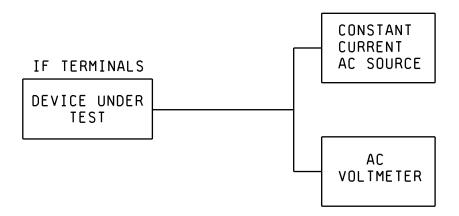

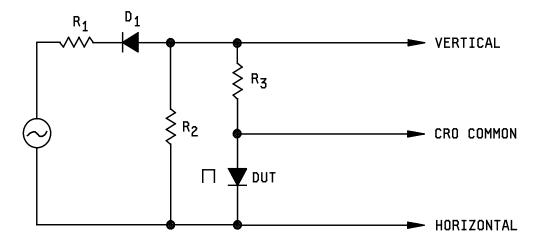

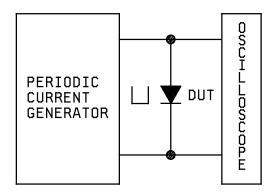

| 4116–1            | AC method                                                                                                    |

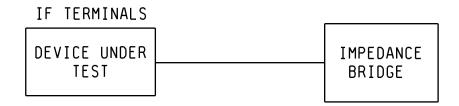

| 4116–2            | Impedance bridge method                                                                                      |

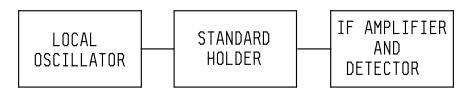

| 4121-1            | Direct measurement method                                                                                    |

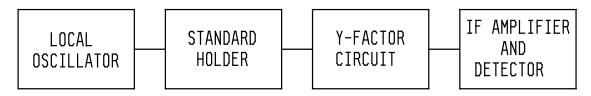

| 4121-2            | Y-factor method                                                                                              |

| 4126-1            | Test setup for overall noise figure                                                                          |

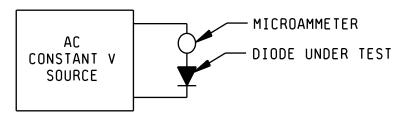

| 4131-1            | Constant voltage method                                                                                      |

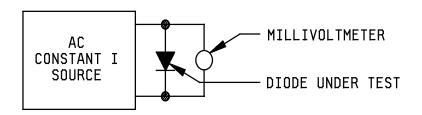

| 4131-2            | Constant current method                                                                                      |

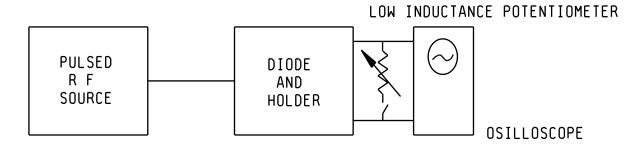

| 4131–3            | Pulsed RF method                                                                                             |

| 4131–4            | Continuous wave RF method                                                                                    |

| 4136–1            | Slotted line method                                                                                          |

| 4136–2            | Reflectometer method                                                                                         |

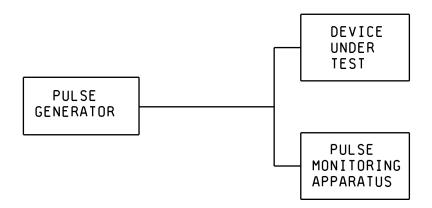

| 4141–1            | Test setup for repetitive pulsing                                                                            |

| 4146–1            | Burnout by single pulse                                                                                      |

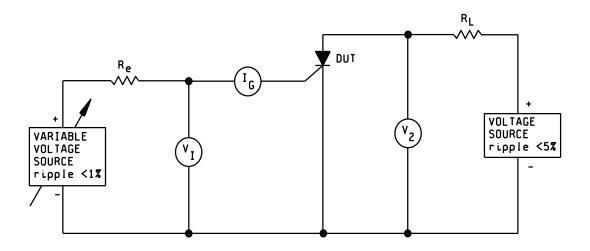

| 4201–1            | Test circuit for holding current                                                                             |

| 4206–1            | Test circuit for forward blocking current (dc method)                                                        |

| 4206–2            | Test circuit for forward blocking current (ac method)                                                        |

| 4211–1            | Test circuit for reverse blocking current (dc method)                                                        |

| 4211–2            | Test circuit for reverse blocking current (ac method)                                                        |

| 4216–1<br>4219–1  | Test circuit for pulse response Test circuit for reverse gate current                                        |

| 4221–1            | Test circuit for gate-trigger voltage or gate-trigger current                                                |

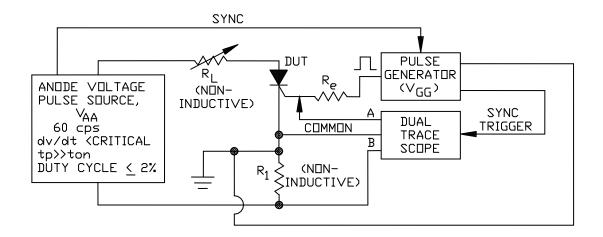

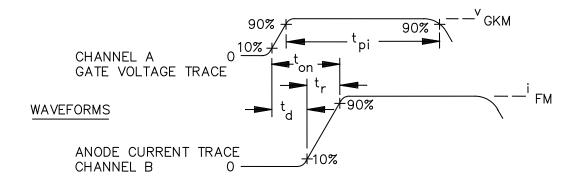

| 4223–1            | Test circuit for gate-trigger voltage or gate-trigger current  Test circuit for gate-controlled turn-on time |

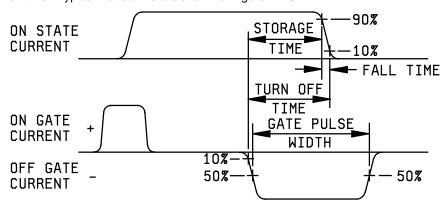

| 4223–2            | Waveforms, gate-controlled turn-on time                                                                      |

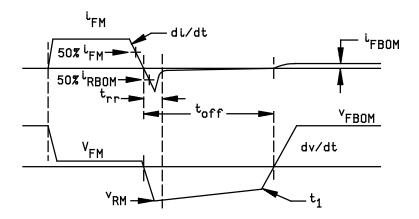

| 4224–1            | Circuit-commutated turn-off time waveforms                                                                   |

| 4224–2            | Test circuit for circuit-commutated turn-off time                                                            |

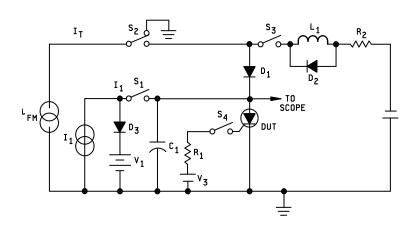

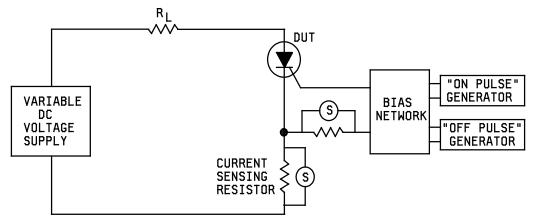

| 4225–1            | Gate turn-off test circuit                                                                                   |

| 4225–2            | Typical gate turn-off circuit waveforms                                                                      |

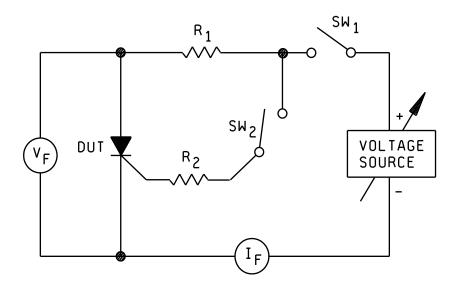

| 4226-1            | Test circuit for forward on voltage                                                                          |

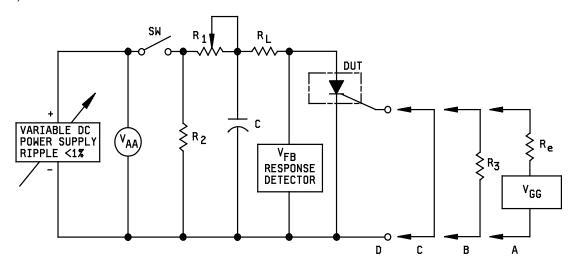

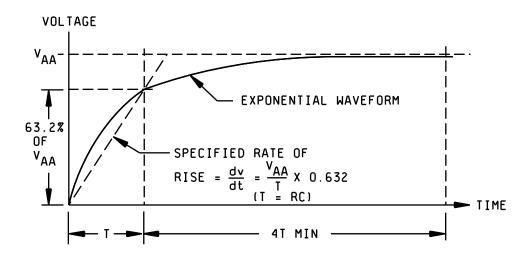

| 4231-1            | Test circuit for exponential rate of voltage rise                                                            |

| 4231-2            | Waveforms across the DUT                                                                                     |

| 4301–1            | Test circuit for junction capacitance                                                                        |

| <u>FIGURE</u>                                                                                                                                                                        | TITLE                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

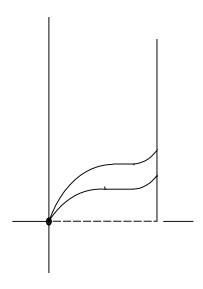

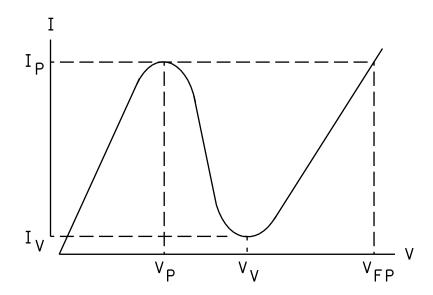

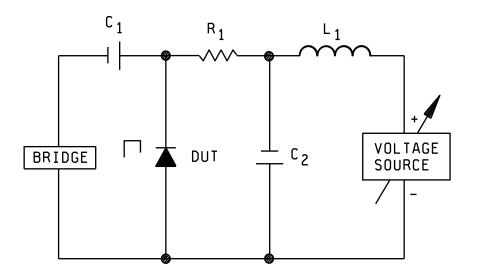

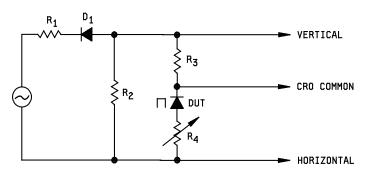

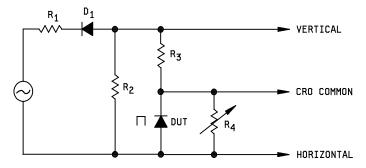

| 4306-1<br>4306-2<br>4306-3<br>4316-1<br>4321-1<br>4321-2<br>4326-1<br>4331-1                                                                                                         | Test circuit for static characteristics of tunnel diodes (dc method) Test circuit for static characteristics of tunnel diodes (ac method) Typical tunnel diode forward characteristic Test circuit for series inductance Test circuit for negative resistance, short-circuit stable method Test circuit for negative resistance, open-circuit stable method Test circuit for series resistance Test circuit for switching time |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <u>TABLE</u>                                                                                                                                                                         | TITLE                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4031-1<br>4031-II                                                                                                                                                                    | Test cor<br>Test cor                                                                                                                                                                                                                                                                                                                                                                                                           | ndition B<br>ndition D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TEST METHO                                                                                                                                                                           | D NO.                                                                                                                                                                                                                                                                                                                                                                                                                          | TITLE OF ELECTRICAL CHARACTERISTICS TESTS FOR DIODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4000<br>4001.1<br>4011.6<br>4016.4<br>4021.2<br>4022<br>4023.2<br>4026.5<br>4031.5<br>4036.1<br>4041.2<br>4046.1<br>4051.3<br>4056.2<br>4061.1<br>4064.1<br>4065<br>4066.5<br>4071.1 |                                                                                                                                                                                                                                                                                                                                                                                                                                | Condition for measurement of diode static parameters Capacitance Forward voltage Reverse current leakage Breakdown voltage (diodes) Breakdown voltage (voltage regulators and voltage-reference diodes) Scope display Forward recovery time and peak forward recovery voltage and time Reverse recovery characteristics Quality factor (Q) for voltage variable capacitance diodes Rectification efficiency Reverse current, average Small-signal reverse breakdown impedance Small-signal forward impedance Stored charge Inductive avalanche energy test for diodes Peak reverse power test Surge current and impulse clamp voltage Temperature coefficient of breakdown voltage |

| 4076.1<br>4081.4                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                | Saturation current Thermal resistance of diodes (forward voltage, switching method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TEST METHOD NO.  | TITLE OF ELECTRICAL CHARACTERISTICS TESTS FOR MICROWAVE DIODES                   |

|------------------|----------------------------------------------------------------------------------|

| 4101.3           | Conversion loss                                                                  |

| 4102             | Microwave diode capacitance                                                      |

| 4106             | Detector power efficiency                                                        |

| 4111.1           | Figure of merit (current sensitivity)                                            |

| 4116.1<br>4121.2 | Intermediate frequency (IF) impedance                                            |

| 4121.2           | Output noise ratio  Overall noise figure and noise figure of the IF amplifier    |

| 4131.1           | Video resistance                                                                 |

| 4136.1           | Standing wave ratio (SWR)                                                        |

| 4141.1           | Burnout by repetitive pulsing                                                    |

| 4146.1           | Burnout by single pulse                                                          |

| 4151             | Rectified microwave diode current                                                |

|                  |                                                                                  |

|                  | TITLE OF ELECTRICAL CHARACTERISTICS TESTS FOR THYRISTORS (CONTROLLED RECTIFIERS) |

| 4201.2           | Holding current                                                                  |

| 4206.1           | Forward blocking current                                                         |

| 4211.1           | Reverse blocking current                                                         |

| 4216             | Pulse response                                                                   |

| 4219             | Reverse gate current                                                             |

| 4221.1           | Gate-trigger voltage                                                             |

| 4223             | Gate-controlled turn-on time                                                     |

| 4224             | Circuit-commutated turn-off time                                                 |

| 4225             | Gate-controlled turn-off time                                                    |

| 4226.1           | Forward on voltage                                                               |

| 4231.2           | Exponential rate of voltage rise                                                 |

|                  | TITLE OF ELECTRICAL CHARACTERISTICS TESTS FOR TUNNEL DIODES                      |

| 4301             | Junction capacitance                                                             |

| 4306.1           | Static characteristics of tunnel diodes                                          |

| 4316             | Series inductance                                                                |

| 4321             | Negative resistance                                                              |

| 4326             | Series resistance                                                                |

| 4331             | Switching time                                                                   |

|                  |                                                                                  |

#### 1. SCOPE

- 1.1 <u>Purpose</u>. Part 4 of this test method standard establishes uniform test methods for the basic electrical testing of semiconductor diodes to determine resistance to deleterious effects of natural elements and conditions surrounding military operations. For the purpose of this standard, the term "devices" includes such items as transistors, diodes, voltage regulators, rectifiers, tunnel diodes, and other related parts. This part of a multipart test method standard is intended to apply only to semiconductor devices.

- 1.2 <u>Numbering system</u>. The test methods are designated by numbers assigned in accordance with the following system:

- 1.2.1 Classification of tests. The electrical test methods included in this part are numbered 4000 to 4999 inclusive.

- 1.2.2 <u>Test method revisions</u>. Test method revisions are numbered consecutively using a period to separate the test method number and the revision number. For example, 4011.4 designates the fourth revision of test method 4011.

- 1.3 <u>Method of reference</u>. When applicable, test methods contained herein should be referenced in the individual specification, specification sheet, or procurement documents by specifying the test method number and the details specified in the summary of the applicable test method. The basic standard should be referenced and not the individual part or parts of this standard. To avoid the necessity for changing documents that refer to test methods of this standard, the revision number of a test method should not be used when referencing individual test methods. For example, use 4011 as a reference versus 4011.4.

#### 2. APPLICABLE DOCUMENTS

2.1 <u>General</u>. The documents listed in this section are specified in sections 3 and 4 and the individual test methods of this standard. This section does not include documents cited in other sections of this standard or recommended for additional information or as examples. While every effort has been made to ensure the completeness of this list, document users are cautioned that they must meet all specified requirements documents cited in sections 3 and 4 and the individual test methods of this standard, whether or not they are listed.

#### 2.2 Government documents.

2.2.1 <u>Specifications, standards, and handbooks</u>. The following specifications, standards, and handbooks form a part of this document to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

# DEPARTMENT OF DEFENSE SPECIFICATIONS

MIL-PRF-19500 - Semiconductor Devices, General Specification for.

#### DEPARTMENT OF DEFENSE STANDARDS

MIL-STD-750 - Test Methods For Semiconductor Devices.

(Copies of these documents are available online at http://quicksearch.dla.mil.)

2.3 <u>Non-Government publications</u>. The following documents form a part of this document to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

# ASME INTERNATIONAL (ASME)

ASME Y14.38 - Abbreviations and Acronyms for Use on Drawings and Related Documents.

(Copies of these documents are available online at <a href="http://www.asme.org">http://www.asme.org</a> or from ASME International, Three Park Avenue, New York, NY 10016–5990.)

JEDEC - SOLID STATE TECHNOLOGY ASSOCIATION (JEDEC)

JEDEC JESD320 - Conditions for Measurement of Diode Static Parameters.

(Copies of this document are available online at http://www.jedec.org or from JEDEC, 3103 North 10<sup>th</sup> Street, Suite 240-S Arlington, VA 22201–2107.)

2.4 <u>Order of precedence</u>. Unless otherwise noted herein or in the contract, in the event of a conflict between the text of this document and the references cited herein (except for related applicable specification sheet, the text of this document takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

#### 3. DEFINITIONS

- 3.1 <u>Acronyms, symbols, and terms</u>. For the purposes of this part of the test method standard, the acronyms, symbols, and terms specified in MIL-PRF-19500, ASME Y14.38, and herein apply.

- 3.1.1 Acronyms used in this standard. Acronyms used in this part of the test method standard are defined as follows:

- a. ATE Automatic test equipment.

- b. ABD Avalanche breakdown diodes.

- c. DUT Device under test.

- d. ESD Electrostatic discharge.

- e. LCC Leadless chip carrier.

- f. MELF Metal electrode leadless face.

- g. MOSFET Metal oxide semiconductor field-effect transistor.

- h. RF Radio frequency.

- i. SCR Silcon controlled rectifier.

- j. SWR Standing wave ratio.

- k. TSP Temperature sensitive parameter.

- n. TVS Transient voltage suppressors.

- I. UHF Ultra high frequency.

- m. VTC Voltage-temperature coefficient.

- n. VSWR Voltage standing wave ratio.

- 3.1.2 Symbols used in this standard. The symbols used in this standard are as follows:

- a. Hz Hertz.

- b. μH Microhenries.

- c. ns Nanosecond.

- d. pF Picofarad.

- 3.1.3 Terms used in this standard. The definitions of terms used in this standard are as follows:

- 3.1.3.1 <u>NPN</u>. The term NPN refers to one of the two types of bipolar junction transistors, consisting of a layer of P-doped semiconductor between two N-doped layers.

- 3.1.3.2 <u>PNP</u>. The term PNP refers to the other type of bipolar junction transistors, consisting of a layer of N-doped semiconductor between two P-doped layers.

#### 4. GENERAL REQUIREMENTS

- 4.1 <u>General</u>. Unless otherwise specified in the individual test method, the general requirements of <u>MIL-STD-750</u> shall apply.

- 4.2 <u>Test conditions for electrical measurements</u>. Unless otherwise required for a specified test method, semiconductor devices should not be subjected to any condition that will cause any maximum rating of the device to be exceeded. The precautions should include limits on maximum instantaneous currents and applied voltages. High series resistances (constant current supplies) and low capacitances are usually required. If low cutoff or reverse current devices are to be measured; for example, nanoampere units, care should be taken to ensure that parasitic circuit currents, or external leakage currents are small compared with the cutoff or reverse current of the device to be measured.

- 4.2.1 <u>Steady-state dc measurements (test method series 4000)</u>. Unless otherwise specified, all steady-state dc parameters are defined using steady-state dc conditions.

- 4.2.2 <u>Pulse measurements (test method series 4000)</u>. When device static or dynamic parameters are measured under pulsed conditions, in order to avoid measurement errors introduced by device heating during the measurement period, the following items should be covered in the performance specification sheet:

- a. The statement "pulsed test" shall be placed by the test specified.

- b. Unless otherwise specified, the pulse time (t<sub>p</sub>) shall be ≤10 milliseconds and the duty cycle shall be a maximum of 2 percent; within this limit the pulse must be long enough to be compatible with test equipment capability and the accuracy required, and short enough to avoid heating.

- 4.2.3 <u>Electrical characteristics tests for microwave diodes (test method series 4100)</u>. When device static or dynamic parameters are measured under pulsed conditions, in order to avoid measurement errors introduced by device heating during the measurement period, the following items should be covered in the performance specification sheet:

- a. Measurement of conversion loss, output noise ratio, and other microwave parameters shall be conducted with the device fitted in the holder. All fixed adjustments of the holder shall be made at a laboratory designated by the Government. In the test equipment, the impedance presented to the mixer by the local oscillator (and the signal generator, if used) shall be the characteristic impedance of the transmission line between the local oscillator and mixer (the maximum VSWR, looking toward the local oscillator, shall be 1.05 at the signal and image frequencies).

- b. For qualification inspection of reversible UHF and microwave devices, the radio frequency measurements, excluding the post environmental test end points and high temperature life (nonoperating) end points, shall be made, first, with the adapter on one end of the device, and then repeated with the adapter at the opposite end of the device; for the environmental and life tests, fifty percent of each sample shall be tested with the adapter on one end of the device and the remaining half of the sample shall be tested with the adapter on the opposite end of the device. End point measurements shall be made without moving the adapter. This procedure shall be repeated on at least one lot every 6 months.

- c. For quality conformance inspection of reversible UHF and microwave devices, the electrical measurements, including the post environmental test end points, may be made with the adapter on either end of the device.

- 4.2.4 <u>Test circuits</u>. The test circuits shown in the test methods of this test method standard are given as examples which may be used for the measurements. They are not necessarily the only test circuits which can be used; however the manufacturer shall demonstrate to the Government that other test circuits which they may desire to use will give results within the desired accuracy of measurement. Circuits are shown for PNP transistors in one circuit configuration only. They may readily be adapted for NPN devices and for other circuit configurations.

4.3 <u>Non-destructive tests</u>. Unless otherwise demonstrated, the test methods listed in table I shall be classified as nondestructive.

TABLE I. Non-destructive tests.

| Test method number | Test                                                                         |

|--------------------|------------------------------------------------------------------------------|

| 4066               | Surge current                                                                |

| 4081               | Thermal resistance of lead mounted diode (forward voltage, switching method) |

NOTE: When the junction temperature exceeds the device maximum rated junction temperature for any operation or test (including electrical stress test), these tests shall be considered destructive except under transient surge or nonrepetitive fault conditions or approved accelerated screening when it may be desirable to allow the junction temperature to exceed the rated junction temperature. The feasibility shall be determined on a part by part basis and in the case where it is allowed adequate sample testing, shall be performed to provide the proper reliability safeguards.

- 4.4 Destructive tests. No test methods within this test method standard have been classified as destructive.

- 4.5 <u>Laboratory suitability</u>. Prior to processing any semiconductor devices intended for use in any military system or sub-system, the facility performing the test(s) shall be audited by the DLA Land and Maritime, Sourcing and Qualification Division and be granted written Laboratory Suitability status for each test method to be employed. Processing of any devices by any facility without Laboratory Suitability status for the test methods used shall render the processed devices nonconforming.

#### 5. DETAILED REQUIREMENTS

This section is not applicable to this standard.

#### 6. NOTES

(This section contains information of a general or explanatory nature that may be helpful, but is not mandatory.)

- 6.1 <u>Intended use</u>. The intended use of this test method standard is to establish appropriate conditions for testing semiconductor devices to give test results that simulate the actual service conditions existing in the field. This test method standard has been prepared to provide uniform test methods, controls, and procedures for determining with predictability the suitability of such devices within military, aerospace and special application equipment.

- 6.2 <u>International standardization agreement</u>. Certain provisions of this test method standard are the subject of international standardization agreement. When amendment, revision, or cancellation of this test method standard is proposed which will affect or violate the international agreement concerned, the preparing activity will take appropriate reconciliation action through international standardization channels, including departmental standardization offices, if required.

- 6.3 Subject term (key word) listing.

Destructive tests

Electrical characteristics tests

Laboratory suitability

Non–destructive tests

- 6.4 <u>Supersession data</u>. The main body and test methods of this subpart replaces portions of main body and test method series 4000 of the superseded MIL-STD-750E.

- 6.5 <u>Change notations</u>. The margins of this standard are marked with vertical lines to indicate modifications generated by this change. This was done as a convenience only and the Government assumes no liability whatsoever for any inaccuracies in these notations. Bidders and contractors are cautioned to evaluate the requirements of this document based on the entire content irrespective of the marginal notations.

#### METHOD 4000

#### CONDITION FOR MEASUREMENT OF DIODE STATIC PARAMETERS

- 1. <u>Purpose</u>. The purpose of this test method is for measuring a temperature-sensitive static parameter under conditions such that the product of the applied voltage and current at the test point produces a power dissipation level that will cause significant heating of the junction, the measured result may be subject to errors due to thermal or transient effects. In order to avoid such errors, the measurement should be made under defined conditions.

- 2. <u>Steady-state dc measurements</u>. When making measurements under conditions of steady-state dc, a condition of thermal equilibrium may be considered to have been achieved if halving the time between the application of power and the taking of the reading causes no error in the indicated results within the required accuracy of measurement. For these purposes very long pulses or step functions may be considered as steady-state dc. When appropriate, the mounting conditions (T<sub>L</sub> or T<sub>C</sub>) or the thermal resistance (reference point to ambient R<sub>BCA</sub> or R<sub>BLA</sub>) shall be specified.

- 3. <u>Pulse measurements</u>. When a measurement is made under pulse conditions, the point of measurement after the start of the pulse shall be chosen such that it is long enough to charge interconnecting test cable capacitance, avoid electrical transient effects, and short enough to avoid heating effects. This can be ensured if halving the minimum selected time, or doubling the maximum selected time, will not produce errors beyond the defined accuracy of the measurement. The pulse measurement may be intended to correlate to a steady-state dc measurement, provided that a correlation has been established.

METHOD 4000

This page intentionally left blank.

#### METHOD 4001.1

#### **CAPACITANCE**

- 1. <u>Purpose</u>. The purpose of this test method is to measure the capacitance across the semiconductor device terminals under specified dc bias and ac signal voltages.

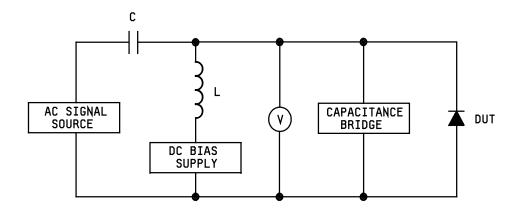

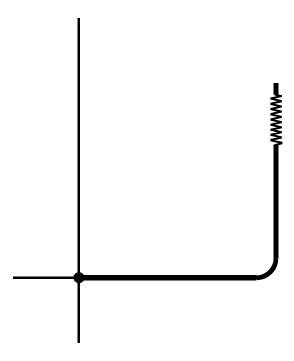

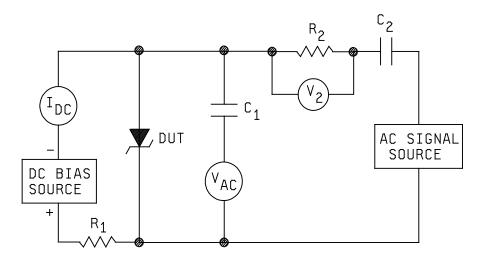

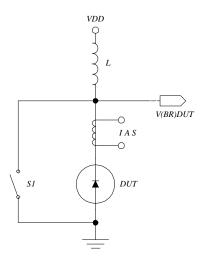

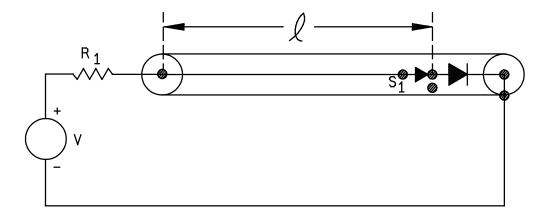

- 2. Test circuit. See figure 4001-1.

NOTE: Both dc bias and ac signal sources may be incorporated in the capacitance bridge. The dc bias source should be properly isolated, preferably with an inductance L in series and have negligible capacitance compared to the DUT. The reactance of C must be negligible compared to the reactance of the DUT, at the frequency of measurement. Impedance of voltmeter should be at least 10 times that of the DUT.

# FIGURE 4001-1. Test circuit for capacitance.

- 3. <u>Procedure</u>. The dc voltage source shall be adjusted to the specified bias voltage. The ac small signal voltage shall be adjusted to the specified frequency for the capacitance measurement. The bridge shall be nulled and adjusted for zero capacitance reading just prior to insertion of the DUT to eliminate error from external circuitry.

- 4. <u>Summary</u>. The following conditions shall be specified in the applicable performance specification sheet or acquisition document:

- a. DC bias voltage.

- b. Test frequency.

This page intentionally left blank.

#### METHOD 4011.6

#### FORWARD VOLTAGE

- 1. <u>Purpose</u>. The purpose of this test method is to measure the voltage across the device when a specified current flows through the semiconductor device in the forward direction.

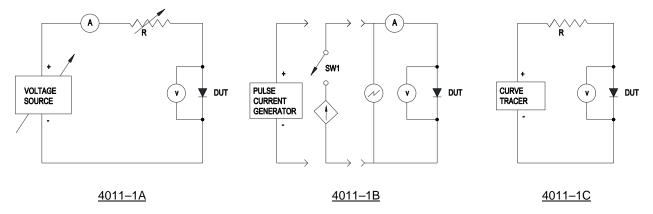

- 2. <u>Applicability</u>. This test method has three different conditions: A, B, and C. A summary of each condition is as follows:

Condition A uses a dc forward current to stimulate the device under test (DUT) and the resulting forward voltage is measured. The measurement is typically performed under conditions of thermal equilibrium and thermal management is usually necessary.

Condition B uses a forward current pulse of specified duration to stimulate the DUT and the resulting forward voltage is measured. In order to avoid significant heating of the junction during the test for forward voltage, the width of the current pulse used to make the measurement should not exceed 8.3 milliseconds and the repetition rate of the pulses should be low enough to impose a duty cycle of no more than 2 percent. Thermal management is generally unnecessary.

Condition C uses a curve tracer to stimulate the DUT. The forward voltage can be determined by observing the curve tracer waveform at the specified forward current.

- 3. <u>Definitions</u>, symbols, and terms. The following definitions, symbols, and terms shall apply to this test method.

- 3.1 Symbols. The following symbols shall apply for the purpose of this test method:

IF Forward current (dc).

R Resistance  $(\Omega)$ .

V<sub>F</sub> Forward voltage (dc).

V<sub>FM</sub> Maximum (peak) forward voltage.

- 3.2 Forward voltage. A forward voltage across a diode is defined as positive anode-to-cathode voltage.

- 3.3 <u>Maximum (peak) forward voltage</u>. The value of maximum instantaneous forward voltage measured under specified conditions of temperature and forward current.

Change 2 resulted in revision 6 of this test method.

METHOD 4011.6

## 4. General requirements.

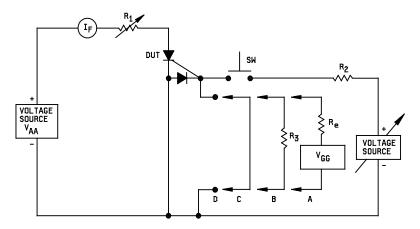

- 4.1 <u>Apparatus</u>. The apparatus used to determine the forward voltage shall be capable of applying the specified current to the DUT and measuring the resulting parameters. The apparatus required for this test method shall include the applicable test circuit shown on figure 4011–1 and the following as applicable to the specified test condition:

- a. Accessories (cold plates, fans, fluid or gas coolants, heat sinks, thermal compounds, thermocouples, etc.) needed for thermal management. Required for condition A only. Optional for condition C.

- b. Ammeter. Required for condition A only.

- c. Curve tracer. The curve tracer shall be a Tektronix Type 576 or equivalent. Required for condition C only.

- d. Oscilloscope or automatic test equipment (ATE). Required for conditions B and C only.

- e. Pulse generator or electronic switch. Required for condition B only.

- f. Resistor (R).

- g. Variable voltage source.

- h. Voltmeter.

- 4.1.1 <u>Automatic test equipment (ATE)</u>. When used, ATE test instrumentation shall be capable of establishing the required test conditions and measuring the required electrical parameters to perform the specified forward voltage tests.

- 4.1.2 <u>Electronic switch or pulse generator</u>. When specified, the test circuit for condition B (see figure 4011–1B) shall use either an electronic switch or a pulse generator to provide pulses of short-duty cycle to minimize device heating.

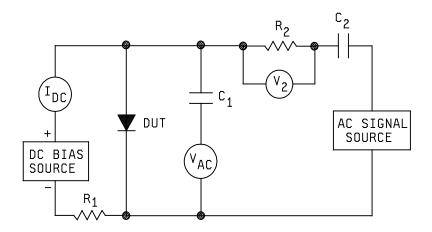

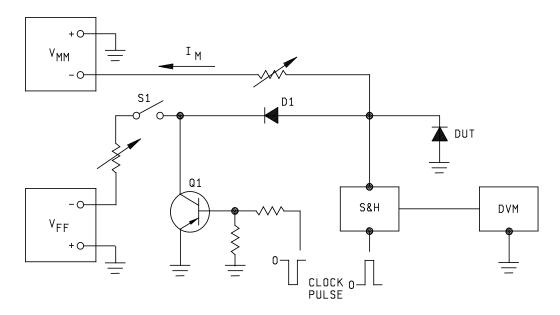

FIGURE 4011-1. Test circuits for forward voltage.

#### 4.2 Procedure.

- 4.2.1 Condition A (dc method) (see figure 4011–1A). The specified dc forward current I<sub>F</sub> shall be applied to the DUT by varying either the variable voltage source or the resistor (R) of the test circuit. The forward current I<sub>F</sub> shall be measured using an ammeter. The forward voltage V<sub>F</sub> shall be measured using a dc voltmeter. The voltmeter connections shall be made at specified points on the DUT (see figure 4011–1A) and always within the current connection points. As needed, appropriate thermal management shall be used and the DUT shall be monitored so as not to exceed the specified temperature rise.

- 4.2.2 Condition B (pulse method) (see figure 4011–1B). The specified forward current I<sub>F</sub> pulse shall be applied to the DUT by adjusting the pulse generator or electronic switch or by programming the automatic test equipment (ATE) to achieve the specified amplitude, frequency, and pulse width values (see 6.a.2). An oscilloscope or ATE shall be used to measure the pulse characteristics. After adjusting pulse level to the correct value for the required forward current I<sub>F</sub>, measure forward voltage V<sub>F</sub>.

- 4.2.3 <u>Condition C (curve tracer method)</u> (see figure 4011–1C). The DUT shall be tested by applying a positive voltage to the anode and limiting the current to within the manufacturer's ratings for forward current I<sub>F</sub>. The forward voltage V<sub>F</sub> shall be determined by observing the curve tracer waveform at the specified forward current I<sub>F</sub>.

- 5. Measurements. The following details shall apply when taking the measurements for forward voltage V<sub>F</sub>.

- 5.1 <u>Details for conditions A and C</u>. When dc techniques are used, device thermal equilibrium shall be achieved before the measurements are made.

- 5.2 <u>Details for condition B</u>. When pulse techniques are used, suitable peak reading methods shall be used to measure the parameters of pulse amplitude, frequency, duty cycle, and pulse width.

- 6. <u>Summary</u>. The following details should be specified in the applicable performance specification sheet or acquisition document:

- a. Test condition letter.

- 1) For condition A,

- (i) The test time shall be specified.

- (ii) If thermal equilibrium is required, the case or lead temperature shall also be specified.

- (iii) For thermal management considerations, the maximum temperature rise (Tc, TEc, TL, Tsp, as applicable) of the DUT during testing shall be specified.

- 2) For condition B, the pulse width.

- For condition C, the number of curve tracer waveforms to be applied (single or multiple) to the DUT during testing shall be specified.

- b. Forward test current (I<sub>F</sub>).

This page intentionally left blank.

#### **METHOD 4016.4**

# REVERSE CURRENT LEAKAGE

- 1. <u>Purpose</u>. The purpose of this test method is to measure the reverse current leakage through a device at a specified reverse voltage using a dc method or an ac method, as applicable.

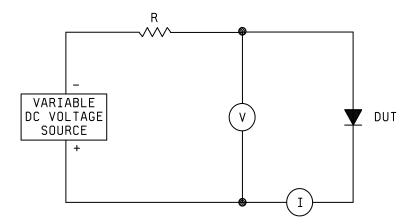

- 2. DC method.

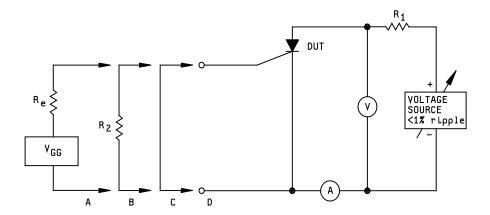

- 2.1 Test circuit. See figure 4016-1.

NOTE: To assure accurate measurement of reverse leakage current, the voltage drop across the ammeter shall be subtracted from the measured value of reverse voltage. Resistor (R) shall be chosen to limit the current flow in the event the device goes into reverse breakdown.

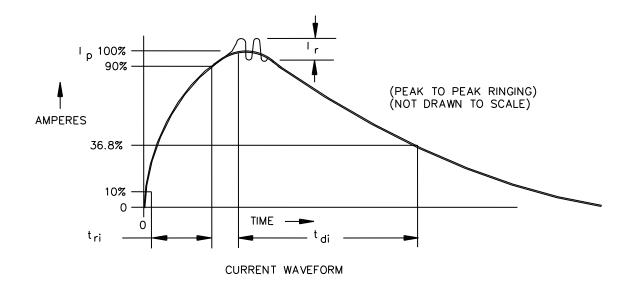

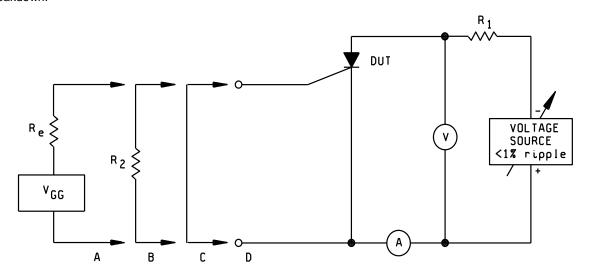

FIGURE 4016-1. Test circuit for reverse current leakage (dc method).

# 2.2 Procedure.

2.2.1 Reverse current. The dc voltage shall be adjusted to the specified value by voltmeter (V) and the reverse current (IR) shall be measured by current meter (I).

## 3. AC method.

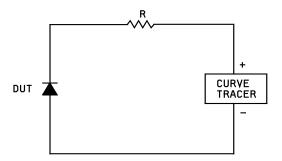

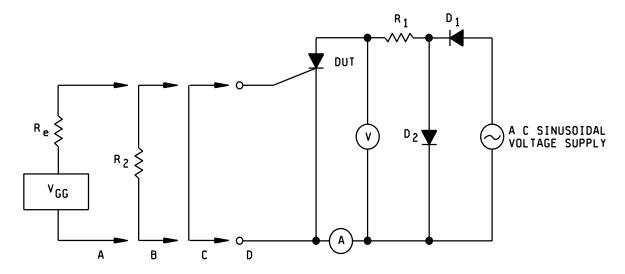

3.1 Test circuit. See figure 4016-2.

\*NOTE: The resistor R is a selectable value within the curve tracer.

FIGURE 4016-2. Test circuit for reverse current leakage (ac method).

#### 3.2 Procedure.

- 3.2.1 <u>Reverse current</u>. A Tektronix 576-curve tracer or equivalent shall be used to apply voltage in the reverse direction only. The curve tracer supply shall be adjusted to obtain the specified peak reverse voltage across the device. Current and voltage shall be measured on the curve tracer.

- 4. <u>Summary</u>. The following conditions shall be specified in the applicable performance specification sheet or acquisition document:.

- a. DC or ac method.

- b. Test voltage (dc method) or peak reverse voltage (ac method).

- c. Thermal resistance of minimum heat dissipater on which device is mounted in °C/W (where applicable).

- d. Thermal equilibrium or pulse condition such as specified in JEDEC JESD320. (If pulse test is not specified, thermal equilibrium dc test method correlation will be applicable. This may include pulse measurement intended to correlate to steady-state dc measurement as described in JEDEC JESD320.)

#### METHOD 4021.2

# **BREAKDOWN VOLTAGE (DIODES)**

- 1. <u>Purpose</u>. The purpose of this test method is to determine if the breakdown voltage of the semiconductor device is greater than the specified minimum limit.

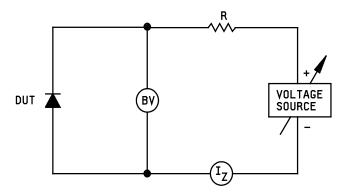

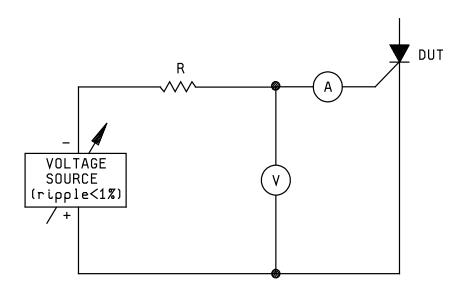

- 2. <u>Test circuit</u>. The resistance R is a current-limiting resistance and is chosen to avoid excessive current flowing through the device. (See figure 4021–1).

NOTE: The ammeter shall present essentially a short-circuit to the terminals between which the current is being measured or the voltmeter readings shall be corrected for the drop across the ammeter.

FIGURE 4021-1. Test circuit for breakdown voltage (diodes).

- 3. <u>Procedure</u>. The reverse current shall be adjusted from zero until either the minimum limit for breakdown voltage or the specified test current is reached. The device is acceptable if the specified minimum limit for BV is reached before the test current reaches the specified value. If the specified test current is reached first, the device is rejected.

- 4. <u>Summary</u>. The test current (see 3) shall be specified in the applicable performance specification sheet or acquisition document:

This page intentionally left blank.

#### METHOD 4022

# BREAKDOWN VOLTAGE (VOLTAGE REGULATORS AND VOLTAGE-REFERENCE DIODES)

- 1. <u>Purpose</u>. This test method is designed to measure the breakdown voltage of voltage regulator and voltage-reference semiconductor devices under the specified conditions.

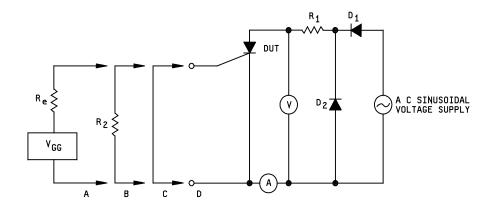

- 2. Test circuit. See figure 4022-1.

NOTE: The voltmeter being used to measure the terminal voltage should present an open circuit to the terminals across which the voltage is being measured.

FIGURE 4022-1. Test circuit for breakdown voltage (voltage regulators and voltage-reference diodes).

- 3. <u>Procedure</u>. The reverse current shall be adjusted from zero until the specified test current is reached. The specified test current shall remain applied for the specified time to approach thermal equilibrium with the device mounted as specified in the individual specification sheet. The breakdown voltage shall then be read from the voltmeter.

- 4. <u>Summary</u>. The following conditions shall be specified in the applicable performance specification sheet or acquisition document:

- a. Test current (see 3).

- b. Time after application of test current when breakdown voltage shall be read.

- c. Method of mounting.

METHOD 4022

This page intentionally left blank.

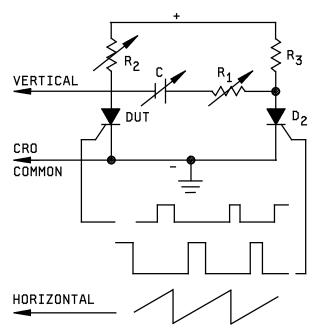

#### METHOD 4023.2

# SCOPE DISPLAY

- 1. <u>Purpose</u>. The purpose of this test method is to define criteria for inspection of the dynamic reverse characteristics of rectifiers, switching, and zener diodes when viewed on a curve tracer. This inspection criteria may not be applicable to specific rectifier designs where the semiconductor device is not intended to be driven into avalanche breakdown, or where the applicable specification sheet has not provided for this inspection.

- 2. <u>Scope</u>. This test applies to all devices requiring stable or sharp and stable breakdown characteristics. Figures 4023–1 through 4023–12 are shown in the first quadrant. The depictions on figures 4023–2 through 4023–12 have been compiled to describe commonly observed faults. The inspections shall be classified as follows:

- a. Condition A stable (only) types. The curve traces on figures 4023–3, 4023–8, 4023–10, and 4023–11 shall apply for condition A.

- b. Condition B sharp and stable types. The curve traces on figures 4023–2 through 4023–12 shall apply for condition B. The ideal sharp and stable trace is one which exhibits a single horizontal line up to the point of breakdown, then transitions vertically to form a 90 degree angle while maintaining the single line (see figure 4023–1). Deviations from this ideal, which are not specifically allowed in this method or applicable specification sheet shall be cause for rejection of the DUT. Tolerances from acceptable devices have been assigned when applicable.

NOTE: Since low voltage zeners do not inherently have, and some other devices may not have a sharp breakdown, specific exceptions in requirements are also provided herein. For ideal reverse trace see figure 4023–1. For soft knee see figure 4023–2. For drift see figure 4023–3.

#### 3. Procedures.

- a. The curve tracer presentation shall be configured so that the horizontal axis shall be calibrated in volts per division and the vertical axis shall be calibrated in amperes per division (or fractions thereof). The vertical and horizontal axis of the curve tracer presentation will be graduated into eight or ten divisions, each representing a precalibrated increment of current or voltage.

- b. A series load resistor shall be used to limit the device reverse current and prevent device damage. This typical resistance should be approximately one quarter or more of the device resistance at the breakdown specification, when the curve trace set-up permits.

Example: A device to be observed at  $I_{BR}$  of 100  $\mu$ A which is specified to be 400 volts minimum, would have a series resistance chosen according to the following:

```

R \geq 0.25 (400 / 0.0001), therefore:

R \geq 1 M\Omega

```

The curve tracer peak voltage ( $V_{CT}$ ) may also require limitation, particularly if the series load resistance described cannot be achieved. See figure 4023–1 and 3.e. for typical load line relationships to assure safe reverse current monitoring.

Unless otherwise specified, the breakdown current shall be the current used for the breakdown voltage test.

c. The trace should occur in the first and third quadrant of the display and be slowly adjusted from zero volts to attain the specified current with the maximum amount of resolution for determination of trace characteristics.

METHOD 4023.2

- d. The DUT shall be held under breakdown conditions for at least two second to ensure freedom from intermittent instability for breakdown drift.

- e. The vertical and horizontal sensitivity shall be adjusted on the curve tracer to provide a rendition of the complete trace to the specified current. Horizontal and vertical sensitivity shall be adjusted to provide a trace occupying no less than 50 percent of the available screen.

- f. The curve trace voltage shall not be simply set at a predetermined value and snapped on instantaneously. This may be done only if the product to be tested is known to have a sufficiently narrow breakdown voltage (V<sub>BR</sub>) range with a predetermined series (load line) resistor setting (see b.) and described below, to assure that the device will not be overpowered. This is typically the case for zener diodes prescreened on V<sub>Z</sub> (or V<sub>BR</sub>). The peak open circuit supply voltage of the curve tracer (V<sub>CT</sub>) may then be adjusted such that the V<sub>CT</sub> setting can provide no more current (I<sub>BR</sub> or I<sub>Z</sub>) than that required for avalanche breakdown, taking into account the series load resistance R on figure 4023–1. Unless otherwise specified, these relationships may be calculated by:

$$I_{\it BR} = rac{V_{\it CT} - V_{\it BR}}{\it R}$$

, and  $V_{\it CT} = I_{\it BR} R + V_{\it BR}$

The resistance R may be determined by:

$$R = \frac{V_{CT} - V_{BR}}{I_{BR}}$$

The  $V_{BR}$  (or  $V_Z$ ) utilized in this equation should be the minimum expected so as to always maximize the R value selected.

- g. Allowance for deviation from the desired characteristics described in this method or applicable specification sheet shall be granted by the qualifying activity. If a particular rejectable trace described is expected in a manufacturer's normal process, it shall be identified and explained during device conformance/ qualification. Devices exhibiting the exceptional trace characteristic shall be present in the conformance/qualification lot to establish reliability.

- h. Any device that is stable and passes the applicable illustrated scope conditions shall be passed. Any device that exceeds the conditions in the applicable illustrate scope conditions will be failed. Any device that passes but is continuing to move, drift or otherwise change shall be observed for another 2 seconds. This cycle of 2 second intervals will continue until the part stabilizes and passes by still meeting the pass criteria or fails by exceeding the pass criteria. Any device that is still drifting after a total of 10 seconds shall be failed as being chronically unstable.

- 4. <u>Summary</u>. The following shall be specified in the applicable performance specification sheet or acquisition document: Test condition to be used.

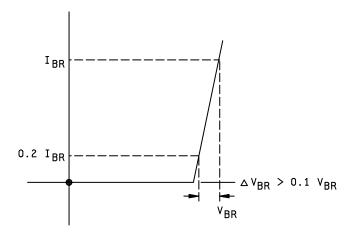

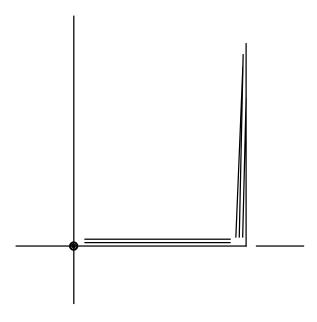

This ideal trace exhibits none of the characteristics described on the figures below. Also, illustrated are the basic curve tracer adjustments and relation for a safe maximum operating current ( $I_{BR}$ ) with the series load resistor (R) versus peak open circuit voltage ( $V_{CT}$ ) and device breakdown voltage ( $V_{BR}$ ).

FIGURE 4023-1. Ideal reverse trace.

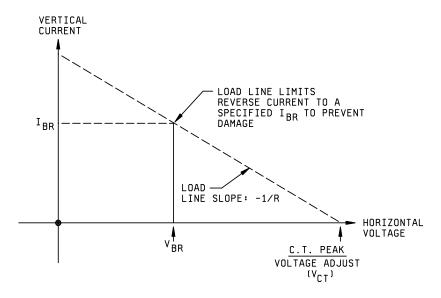

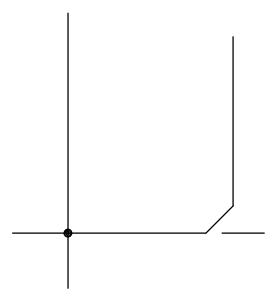

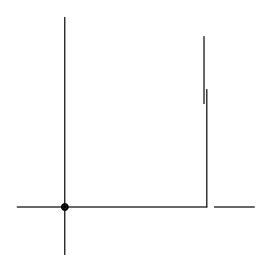

The knee area is the area in which the trace transitions from the horizontal to the vertical. Unless otherwise specified, this area should not require more than 10 percent of the total horizontal voltage component being viewed, or more than 20 percent of the specified  $I_{BR}$ . Not applicable to signal diodes, low voltage zeners, fast, ultrafast, and Schottky rectifiers or low voltage zeners  $\leq$  10 volts.

FIGURE 4023-2. Soft knee.

The vertical component of the trace should remain stable in the horizontal axis. An undesirable drift is defined as greater than a 10 percent increase or 2 percent decrease in actual breakdown voltage up to 1,500 volts. If over 1,500 volts, the allowable drift should be separately specified.

FIGURE 4023-3. Drift.

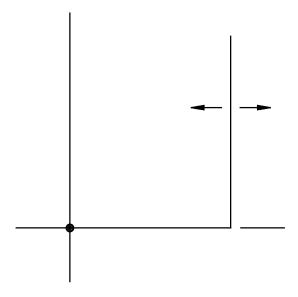

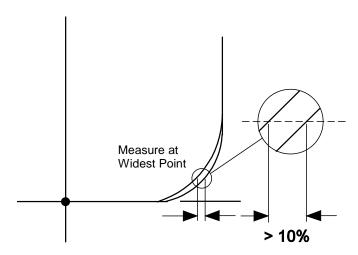

The slope shall be less than 10 percent of  $V_{BR}$  when viewed between 20 percent to 100 percent of the specified  $I_{BR}$  or  $I_{Z}$ . Low voltage zeners below 5.5 volts are in exception to this requirement also, or other devices, as may be specified.

FIGURE 4023-4. Slope.

METHOD 4023.2

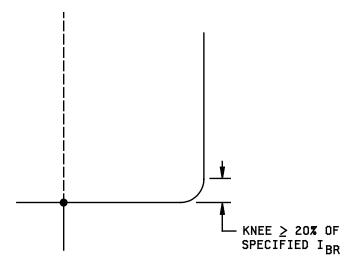

The double break is the area in which the trace transitions from the horizontal to the vertical. Unless otherwise specified, this area should not occupy more than 10 percent of the total horizontal voltage component being viewed, or more than 20 percent of the specified  $I_{BR}$  or  $I_{ZT}$ . This requirement is not applicable to ultrafast or Schottky rectifiers, and low voltage zeners  $\leq$  10 volts.

FIGURE 4023-5. Double break (reject criteria for sharp knee devices).

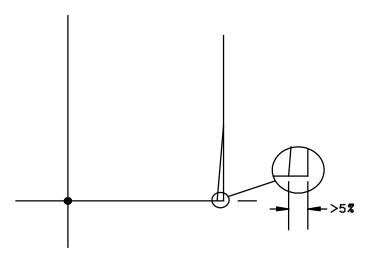

For standard rectifiers and zeners, the region at the knee may display a secondary trace no more than 5 percent of the total voltage of the DUT (see detail).

FIGURE 4023-6. Double trace.

For soft knee diodes including signal diodes, low voltage zeners, and altered junction fast, superfast and ultrafast rectifiers, the region at the knee may display a secondary trace no more than 10 percent of the total voltage of the DUT (see detail).

FIGURE 4023-7. Double trace, soft knee.

METHOD 4023.2

Any jittery movement of the trace in any direction, not caused by power line voltage fluctuations, shall not occur.

FIGURE 4023-8. Unstable (jitter).

The vertical component shall not depart from a single vertical line, except as allowed on figures 4023–6 and 4023–7.

FIGURE 4023-9. Discontinuity.

METHOD 4023.2

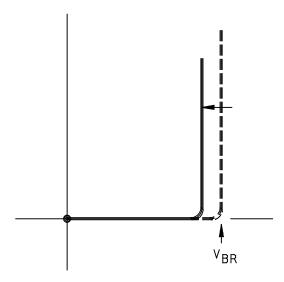

The vertical component shall not decrease its value abruptly by 2 percent or more of V<sub>BR</sub>.

FIGURE 4023-10. Snap back - collapsing VBR.

Leakage current (vertical) shall not degrade from an initial value.

FIGURE 4023-11. Floater.

Instability (arcing) appearing at or near the specified  $I_{BR}$  region on the vertical trace (such as may be coincident with visible sparking activity within the device die region) shall not be present. Noise at or near the knee is permissible, such as typically observed on avalanche-zener devices.

FIGURE 4023-12. Arcing.

#### **METHOD 4026.5**

### FORWARD RECOVERY TIME AND PEAK FORWARD RECOVERY VOLTAGE

- 1. <u>Purpose</u>. The purpose of this test method is to measure the forward recovery time and peak forward recovery voltage of the semiconductor device undergoing testing.

- 2. <u>Applicability</u>. A device under test (DUT) reveals an excessive transient forward voltage when it is switched rapidly into the forward conductance region. The amplitude and time duration of this voltage peak can be measured by observing the voltage waveform across the DUT when a forward current pulse of the specified amplitude, rise time, and pulse width, are applied to the DUT.

- 3. <u>Definitions</u>, symbols, and terms. The following definitions, symbols, and terms shall apply to this test method.

- 3.1 Symbols. The following symbols shall apply to this test method:

- IF Forward current (dc).

- $R_F$  Forward resistance ( $\Omega$ ). For this test method, the value of  $R_F = V_F / I_F$  at the specified  $I_F$ .

- t<sub>fr</sub> Forward recovery time (s).

- t<sub>p</sub> Pulse time (s).

- t<sub>r</sub> Rise time (s).

- V<sub>F</sub> Forward voltage (see 4.2.3).

- VFR Forward recovery voltage (instantaneous total value).

- V<sub>FRM</sub> Peak forward recovery voltage (dc).

- 3.2 <u>Forward recovery time</u>. The forward recovery time is the time interval between the instant when the forward current rises from a specified value, usually 10 percent of I<sub>F</sub>, and the time when the forward voltage falls below a specified v<sub>FR</sub>.

- 3.3 <u>Peak forward recovery voltage</u>. The peak forward recovery voltage is the maximum instantaneous value across the DUT resulting from the application of a specified forward current pulse. Peak forward recovery voltage is sometimes identified as  $V_{F(PK)}$ ,  $V_{FM(DYN)}$ ,  $V_{FM}$ , and  $V_{peak}$ .  $V_{FRM}$  is the preferred symbol.

Change 2 resulted in revision 5 of this test method.

METHOD 4026.5

### 4. General requirements.

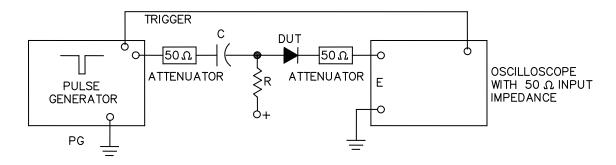

- 4.1 <u>Apparatus</u>. The apparatus used to determine the forward recovery time and peak forward recovery voltage shall be capable of demonstrating device conformance to the minimum requirements of the applicable specification sheet. The apparatus required for this test shall include the following, as applicable.

- a. The test circuit shown on figure 4026–1. The test circuit should be configured to minimize lead length where lead inductance might cause ringing in the test circuit.

- b. Pulse generator. The pulse generator shall be capable of generating the specified forward current pulse.

- c. Response detector (oscilloscope). The input impedance of the response detector shall be  $Z \ge 100$  R<sub>F</sub>.

- d. Resistor R<sub>P</sub>: The value of resistor R<sub>P</sub> shall be chosen to optimize the impedance match between pulse generator and test circuit, thereby minimizing the ringing in the test circuit.

- e. Source resistance  $R_S$ . The value of resistor  $R_S \ge 20 R_F$ .

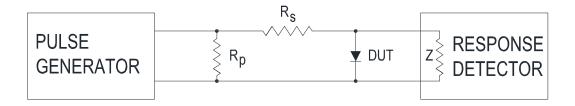

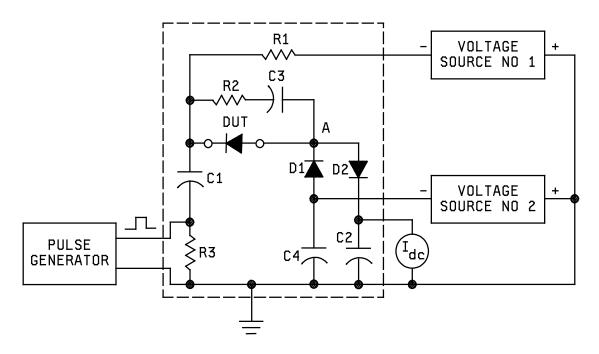

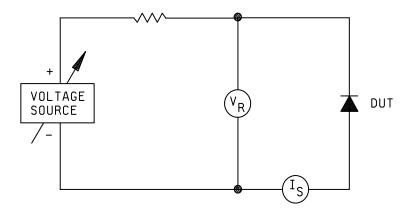

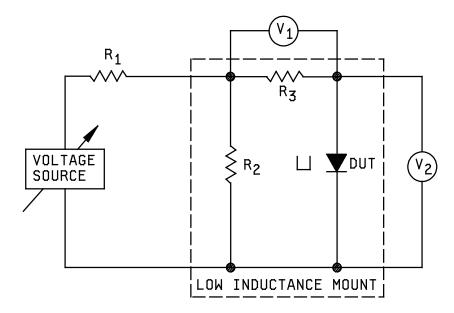

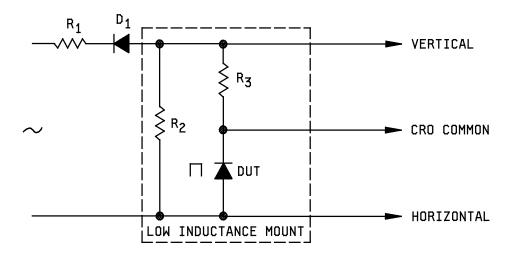

FIGURE 4026-1. Test circuit for forward recovery time and peak forward recovery voltage.

- 4.2 <u>Procedure</u>. The DUT shall be subjected to the specified forward current pulse. The pulse generator shall be adjusted to achieve the specified amplitude, pulse time, and rise time. The resulting forward current pulse through the DUT (see current waveform on figure 4026–2) and voltage waveform across the DUT (see voltage waveform on figure 4026–2) shall be graphically monitored with amplitude displayed versus time. The desired forward recovery time and peak forward recovery voltage characteristics shall be obtained from the response detector.

- 4.2.1 <u>Current pulse characteristics for peak forward recovery voltage</u>. The peak forward recovery voltage of the DUT shall be determined using the following forward current pulse characteristics:

- a. Forward current I<sub>F</sub> amplitude shall be as specified (see 6.a).

- b. Rise time tr shall be 10 ns or as specified (see 6.b).

- c. Pulse time tp shall be greater than or equal to 10 times the specified forward recovery time tfr.

- d. Pulse frequency shall be such that a reduction in frequency shall result in no change in forward recovery characteristics.

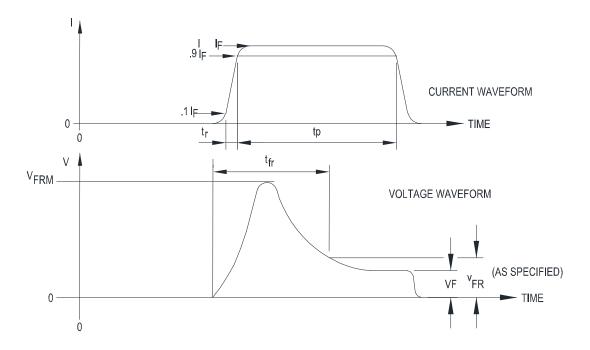

FIGURE 4026-2. Input forward current pulse and output voltage waveforms.

- 4.2.2 <u>Determination of  $v_{FR}$  for forward recovery time</u>. When  $v_{FR}$  is specified (see 6.c), the forward recovery time of the DUT shall terminate when the voltage drop reaches the  $v_{FR}$  voltage (see figure 4026–2). When  $v_{FR}$  is not specified, the forward recovery time of the DUT shall terminate as follows:

- a. If V<sub>FRM</sub> exceeds 10 volts, then v<sub>FR</sub> shall be 3 times V<sub>F</sub>.

- b. If V<sub>FRM</sub> is greater than or equal to 1.3 volts and less than 10 volts, then v<sub>FR</sub> shall be 1.1 times V<sub>F</sub>.

- c. If  $V_{FRM}$  is less than 1.3 volts, then  $v_{FR}$  shall be equal to 0.5 ( $V_{FRM} V_F$ ) +  $V_F$ .

- 4.2.3 <u>Determination of  $V_F$  for  $t_{fr}$  measurement</u>. Unless otherwise specified,  $V_F$  shall be measured at 3 times the  $t_{fr}$  specified by the performance specification sheet.

- 5. Measurements. The following measurement shall be made:

- a. The forward recovery time (t<sub>fr</sub>). The following details shall apply:

- The forward recovery time shall be measured as the time interval from 0.1 I<sub>F</sub> (see current waveform on figure 4026–2) to the time that the forward voltage recovers to a specified v<sub>FR</sub> (see voltage waveform on figure 4026–2 and 6.c).

- 2. For DUTs where V<sub>FRM</sub> is less than v<sub>FR</sub>, the t<sub>fr</sub> shall be measured at V<sub>FRM</sub>.

- b. The peak forward recovery voltage (VFRM).

METHOD 4026.5

- 5.1 Example of measuring  $t_{fr}$ . For an example DUT, the  $t_{fr}$  is specified to be 15 ns maximum by the performance specification sheet. The test operator measures the  $V_F$  at 45 ns, 3 times 15 ns as specified in 4.2.3. It has also been determined that  $V_{FRM}$  at 45 ns is greater than or equal to 1.3 volts and less than 10 volts. Using the determination factor of 4.2.2.b, the test operator would then multiply the measured value of  $V_F$  by 1.1 (110 percent) to arrive at the value of  $V_{FR}$ . The test operator then would turn the second cursor on the response detector back to the calculated value of  $V_{FR}$  value to measure the actual  $t_{fr}$  of the DUT.

- 6. <u>Summary</u>. The following conditions should be specified in the applicable performance specification sheet or acquisition document:

- a. Amplitude of the forward current pulse (I<sub>F</sub>) (see 4.2.1.a).

- b. Rise time (t<sub>r</sub>) of the forward current pulse, if other than 10 nanoseconds (see 4.2.1.b).

- c. Forward recovery voltage (vFR) chosen to terminate the forward recovery time measurement (see 4.2.2).

#### METHOD 4031.5

### REVERSE RECOVERY CHARACTERISTICS

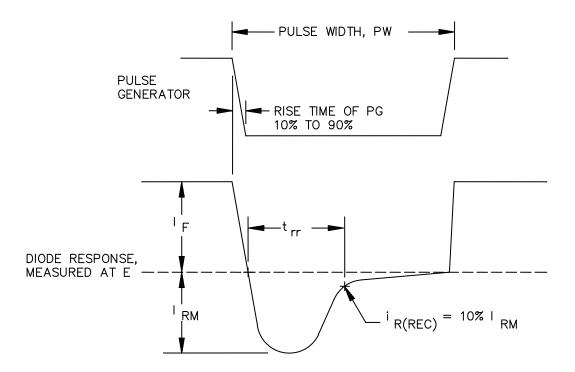

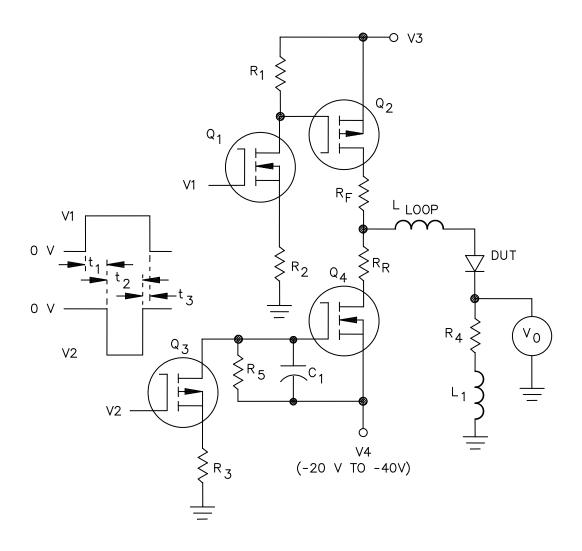

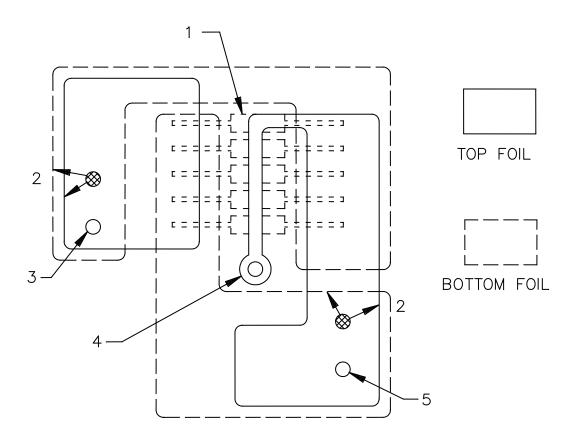

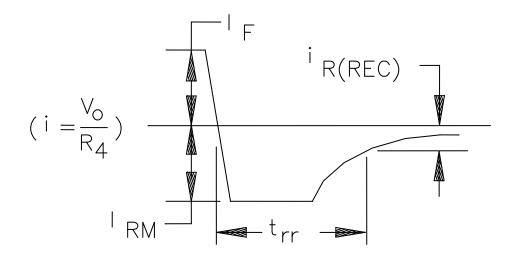

- 1. <u>Purpose</u>. The purpose of this test method is to measure the reverse recovery time and other specified recovery characteristics related to signal, switching, and rectifier diodes by observing the reverse transient current versus time when switching from a specified forward current to a reverse biased state in a specified manner.

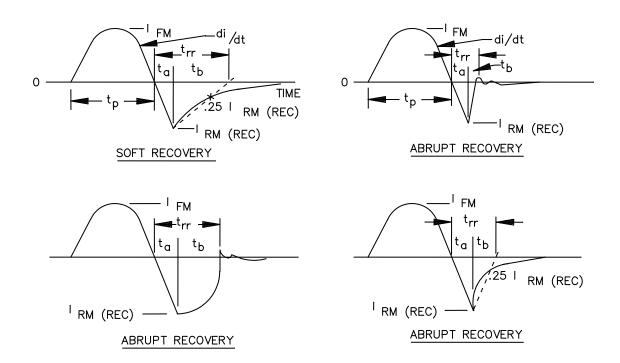

- 2. <u>General guide for selecting appropriate condition</u>. Four conditions are given to include recommended practice for the range of diodes considered. A general guide for selecting the appropriate condition letter is:

- a. Signal diodes with reverse recovery time less than 6 ns.