## **ECE232: Hardware Organization and Design**

Part 1: Introduction

http://www.ecs.umass.edu/ece/ece232/

Adapted from Computer Organization and Design, Patterson & Hennessy, UCB

## **Course Administration - 1**

• Instructors: Israel Koren

koren@ecs.umass.edu

Mani Krishna

krishna@ecs.umass.edu

TAs: Daniel Gomez-Prado

Kunal Ganeshpure Nitin Prakash

Office Hours & e-mail addresses posted

on the course web page

http://www.ecs.umass.edu/ece/ece232/ URL:

SPARK: http://spark.oit.umass.edu/

Required: Computer Organization and Design, The Text:

Hardware/Software Interface by D. A. Patterson and J. L. Hennessy, Morgan Kaufmann; 4th Edition, ISBN 978-0123744937

ECE232: Intro 2

${\tt Adapted \ from \ Computer \ Organization \ \& \ Design, \ Patterson \ \& \ Hennessy, \ UCB \ and \ Kundu, \ UMass}$

#### **Course Administration - 2**

- Slides will be posted in spark (<u>https://spark.oit.umass.edu</u>)

- Grading Policy

- Midterm 1 25% March 7, 2011, 4-6 pm

Midterm 2 25% April 14, 2011, 4-6 pm

- Final 40% TBA

- Homework 10%

- No Midterm make-up exams

- · Percentages adjusted for justified absence

- Homework policy

- Students are encouraged to work in groups. Maximum group size is 4. All names must be clearly noted. Solutions are returned during discussion

- Homework must be submitted through spark.oit.umass.edu

- If you work in a group indicate all names at the top of the page; every student must submit homework through spark

- Late policy: 20% deducted for homework turned in late

- Homework must be picked up within 2 weeks

ECE232: Intro 3

Adapted from Computer Organization & Design, Patterson & Hennessy, UCB and Kundu, UMass

Koren

### **Course Content & Goals**

- Content

- Principles of computer architecture: CPU datapath and control unit design

- Assembly language programming in MIPS

- Memory hierarchies and design

- I/O organization and design

- Possible advanced topics

- Course goals

- To learn the organizational structures that determine the capabilities and performance of computer systems

- To understand the interactions between the computer's architecture and its software

- To understand cost performance trade-offs

ECE232: Intro 4

Adapted from Computer Organization & Design, Patterson & Hennessy, UCB and Kundu, UMass

Kore

#### **What You Should Know**

- Binary numbers

- Read and write basic C/java programs

- Understand the steps in compiling and executing a program

- Basic Verliog constructs

- To deal with HW assignments

- Logic design

- · logical equations, schematic diagrams

- · Combinational vs. sequential logic

- Finite state machines (FSMs)

ECE232: Intro 5

Adapted from Computer Organization & Design, Patterson & Hennessy, UCB and Kundu, UMass

Voron

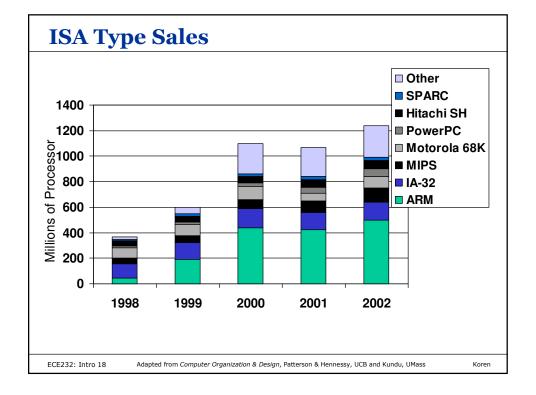

## Why you should know hardware organization?

- Computer organization principles are everywhere

- Embedded computer vs. general-purpose computers:

- Cellphone

- Digital Camera

- MP3 music player

- · Industrial process control

- Complex system design

- How to partition a problem

- Functional Spec  $\rightarrow$  Control & Datapath  $\rightarrow$  Physical implementation

- · Modern CAD tools

ECE232: Intro 6

Adapted from Computer Organization & Design, Patterson & Hennessy, UCB and Kundu, UMass

#### **Computing Systems General Purpose Computing Special Purpose Computing Application types Given Applications** Compiler **Algorithms** ISA Operating Systems **Firmware** Hardware, software Co-design CPU 10 DISK Memory Application **Dataflow** Control **Binary** Hierarchy Datapath Control **Digital Logic Design Digital Logic Design Circuit Design Circuit Design** Layout, Masks Layout, Masks Semiconductor, Packaging Semiconductor, Packaging ECE232: Intro 7

### **Abstractions: ISA and ABI**

- Abstraction helps us deal with complexity

- Hide lower-level detail

- Instruction set architecture ISA: An abstract interface between the hardware and the lowest level software of a machine

- Encompasses all the information necessary to write a machine language program that will run correctly, including

- instructions, registers, memory access, I/O

- ABI (application binary interface): The user portion of the instruction set plus the operating system interfaces used by application programmers

- Defines a standard for binary portability across computers

ECE232: Intro 8

Adapted from Computer Organization & Design, Patterson & Hennessy, UCB and Kundu, UMass

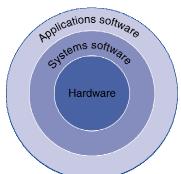

### **System Layers**

- Application software

- Written in high-level language

- System software

- Compiler: translates HLL code to machine code

- Operating System: service code

- Handling input/output

- Managing memory and storage

- Scheduling tasks & sharing resources

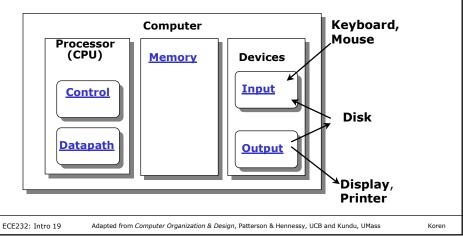

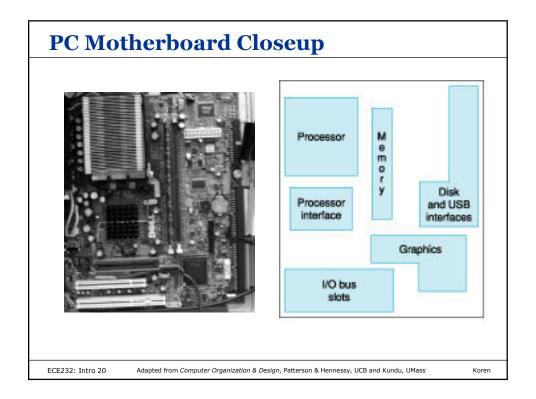

- Hardware

- · Processor, memory, I/O controllers

ECE232: Intro 9

Adapted from Computer Organization & Design, Patterson & Hennessy, UCB and Kundu, UMass

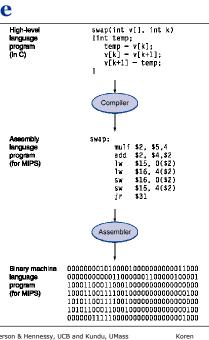

## **Levels of Program Code**

- High-level language

- · Level of abstraction closer to problem domain

- · Provides for productivity and portability

- Assembly language

- Textual representation of instructions

- Hardware representation

- Binary digits (bits)

- · Encoded instructions and data

ECE232: Intro 10

${\tt Adapted \ from \ Computer \ Organization \ \& \ Design, \ Patterson \ \& \ Hennessy, \ UCB \ and \ Kundu, \ UMass}$

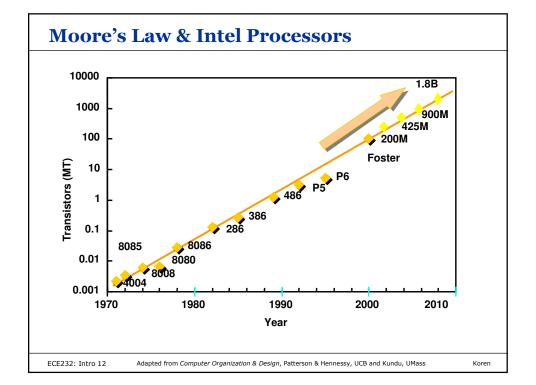

## μProcessor Advances - Moore's Law

- In 1965, Gordon Moore predicted that the number of transistors that can be integrated on a die would double every 18 to 24 months (i.e., grow exponentially with time).

- Amazingly visionary million transistor/chip barrier was crossed in the 1980's.

- 2300 transistors, 1 MHz clock (Intel 4004) 1971

- 16 Million transistors (Ultra Sparc III)

- 42 Million transistors, 2 GHz clock (Intel Xeon) 2001

- 55 Million transistors, 3 GHz, 130nm technology, 250mm<sup>2</sup> die (Intel Pentium 4) - 2004

- 140 Million transistor (HP PA-8500)

- · 1.8 Billion transistors (Itanium II)

ECE232: Intro 11

Adapted from Computer Organization & Design, Patterson & Hennessy, UCB and Kundu, UMass

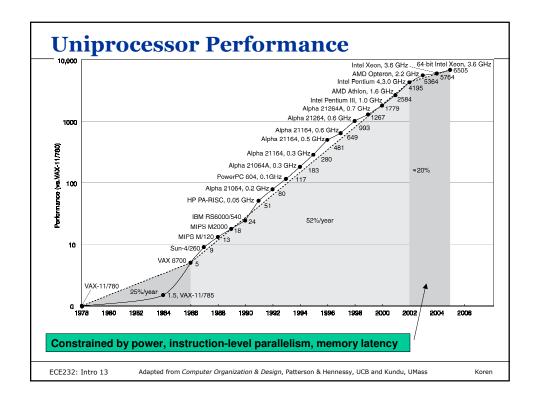

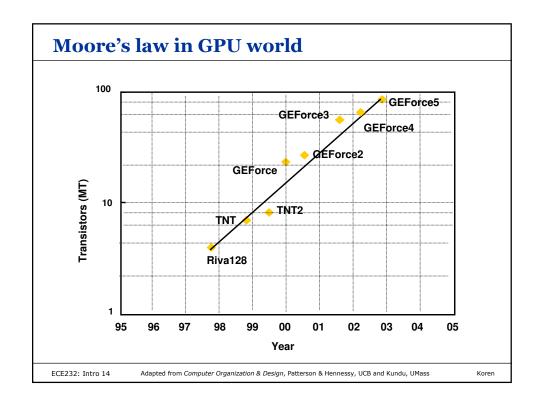

### **Observation**

- Transistor count increases to meet demand for performance and functionality

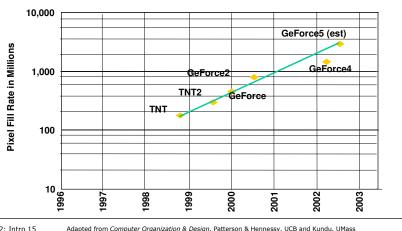

- New applications create demand for increase in performance GPU Pixel Fill-rates Doubling every 1 year!

ECE232: Intro 15

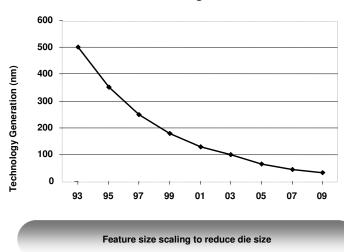

# How is that possible?

Scale the transistor channel length

ECE232: Intro 16

${\tt Adapted \ from \ Computer \ Organization \ \& \ Design, \ Patterson \ \& \ Hennessy, \ UCB \ and \ Kundu, \ UMass}$

## **Impacts of Advancing Technology**

#### Processor

• logic capacity: increases about 30% per year

• performance: 2x every 1.5 years

#### Memory

• DRAM capacity: 4x every 3 years, now 2x every 2

years

• speed: 1.5x every 10 years

• cost per bit: decreases about 25% per year

Disk

• capacity: increases about 60% per year

ECE232: Intro 17

Adapted from Computer Organization & Design, Patterson & Hennessy, UCB and Kundu, UMass

- Workstation design target

- 25% of cost processor

- 25% of cost memory (minimum memory size)

- Rest I/O devices, power supplies, box

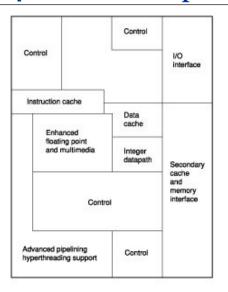

# **Inside the Pentium 4 Processor Chip**

ECE232: Intro 21

dapted from Computer Organization & Design, Patterson & Hennessy, UCB and Kundu, UMass

(oren

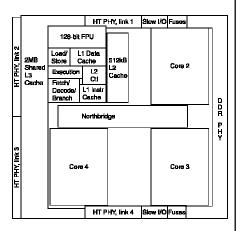

## **Inside the Processor**

AMD Barcelona: 4 processor cores

Reading assignment: Chapter 1

ECE232: Intro 22

Adapted from Computer Organization & Design, Patterson & Hennessy, UCB and Kundu, UMass