# ECOM 5335 - VLSI Design

#### Module #3 - CMOS Fabrication

# Agenda

- 1. CMOS Fabrication

- Yield

- Process Steps for MOS transistors

- Inverter Example

- Design Rules

- Passive Components

- Packaging

#### Announcements

1. Read Chapter 2

ECOM 5335 - VLSI Design

Module #3 Page 1

#### **CMOS Fabrication**

#### CMOS Fabrication

- We have talked about

- 1) Device Physics of how materials act in a MOS/MOSFET structure

- 2) IV characteristics of the MOSFET device

- 3) Small geometry effects on transistor performance

- 4) Capacitances present in the MOSFET device

- 5) How we can use SPICE to simulate the behavior

ECOM 5335 - VLSI Design

Module #3 Page 2

# **CMOS Fabrication**

#### CMOS Fabrication

- We have seen that the properties of the materials play a major role in how the MOSFET performs

- The properties of the material (which material, doping, sizes,..) come from the Fabrication of the MOSFET.

- We want to understand how the devices are created so when we are designing, we can make educated decisions on what *can* and *can't* be done to alter performance.

#### **CMOS Fabrication**

#### The Basics

- We create the majority of our IC's on Silicon

- We take a Silicon Wafer, which is a thin disk of intrinsic Silicon

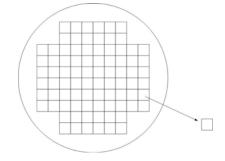

- On this disk, we create multiple IC's, which are square or rectangular in shape

#### The Basics

- Once the wafer is processed, each individual IC is tested and marked whether it passed or failed

- The individual IC's are then cut out using a precision diamond saw.

- The individual IC is called a "die"

- The plural of this is "dies" or "dice"

ECOM 5335 - VLSI Design

Module #3 Page 5

#### **CMOS Fabrication**

#### The Basics

- We define the : Yield = (# of Good die) (# of die on the wafer)

- Yield heavily drives the cost of the chip so we obviously want a high yield.

- However, yields can be very low initially (i.e., <10%).

- A mature process tries to hit ~90% yield

ECOM 5335 - VLSI Design

Module #3 Page 6

Single Silicon Crystal

Water Cooled Chamber

Quartz Crucible

#### **CMOS Fabrication**

#### The Basics

- Since all of the IC's on a wafer are processed together, the time it takes and the process steps required for the wafer are the same regardless of the # of IC's on it.

- This means the cost to process a wafer is the same whether it has 1 IC, or 1000 IC's on it.

- We can drive the cost down by:

- 1) Increasing the number of die on a wafer

- Smaller features (i.e., new processes, 1um, 0.8um, 0.25um, 90nm, 45nm)

ECOM 5335 - VLSI Design

- Larger wafers (2", 4", 8", 12", 16")

- 2) Increasing yield

- Design changes

- Fab changes

# **CMOS Fabrication**

#### Silicon Wafer Creation

- The Silicon valence of 4 means that it can form a crystalline structure

- This crystalline structure can be "grown"

- We start with a Seed, which is a small piece of pure crystalline Silicon

- We then melt raw, impure Silicon into a crucible (aka, Silica)

- We dip the Seed into the molten Silicon and pull it out slowly while turning

- As the molten Silicon cools, it forms covalent bonds with the Seed

- These bonds track the structure of the Seed, forming more Silicon crystal

Module #3 Page 7

#### Silicon Wafers

- As the Silicon is pulled out, it forms a long cylinder

- This cylinder is called an *Ingot*

- The ingot is a long cylinder of pure, crystal, Silicon

ECOM 5335 - VLSI Design

Module #3 Page 9

#### **CMOS Fabrication**

#### Silicon Wafers

- The ingots are then cut into thin disks called Wafers

- The wafers are polished and marked for crystal orientation

- Companies specialize in the creation of ingots and typically sell the wafers to Fab shops

ECOM 5335 - VLSI Design

Module #3 Page 10

#### **CMOS Fabrication**

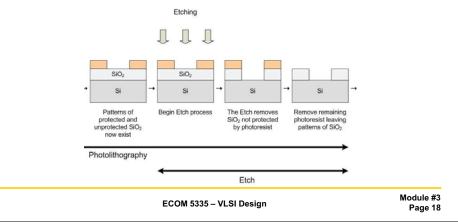

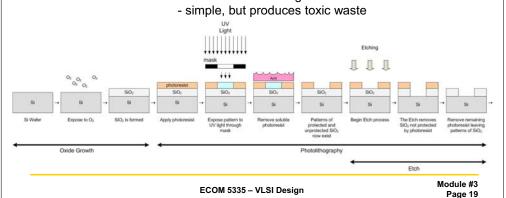

# Photolithography

- This is the process of creating patterns on a smooth surface, in our case a Silicon wafer

- This is accomplished by selectively exposing parts of the wafer while other parts are protected

- The exposed sections are susceptible to doping, removal, or metallization

- Specific patterns can be created to form regions of conductors, insulators, or doping

- Putting these patterns onto a wafer is called Photolithography

- To understand this process, we must first learn about some basic components that are used in the process.

- We'll learn these first and then put it all together to show how Photolithography is used to create an IC.

#### **CMOS Fabrication**

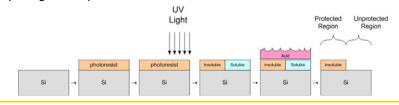

# **Photoresist**

- A material that is *acid-resistant* under normal conditions (insoluble to acids)

- When exposed to UV light, the material becomes soluble to acids

- We can put photoresist on a wafer and then selectively expose regions to UV

- Then we can soak the entire thing in acid and only the parts of the photoresist that were exposed to UV light will be removed

- This allows us to form a protective barrier on certain parts of the wafer while exposing others parts

ECOM 5335 - VLSI Design

#### **Photoresist**

- There are two flavors of photoresist

**Original State** After UV Exposure

"Positive Photoresist" Insoluble Soluble

"Negative Photoresist" Soluble Insoluble

- Positive Photoresist is the most popular due to its ability to achieve higher resolution features

ECOM 5335 - VLSI Design

Module #3 Page 13

#### **CMOS Fabrication**

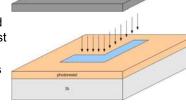

#### Masks

- A mask in an opaque plate (i.e., not transparent) with holes/shapes that allow UV light to pass

- The mask contains the pattern that we wish to form on the target wafer

- We pass UV light through the Mask and create soluble patterns in the photoresist

- Each pattern we wish to create requires a unique mask

- The physical glass plate that is used during fabrication is called a *Reticle*

ECOM 5335 - VLSI Design

Module #3 Page 14

#### **CMOS Fabrication**

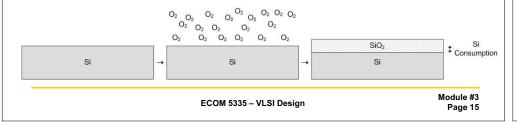

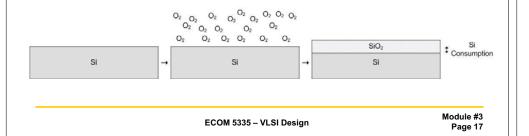

# Oxide Growth

- Silicon has an affinity to form an Oxide when exposed to Oxygen

- This forms Silicon Dioxide (SiO<sub>2</sub>), or oxide for short

- SiO<sub>2</sub> is an insulator

- So all we have to do in order to form an insulating layer on Silicon is expose it to Oxygen

- Silicon is actually consumed during this process

#### **CMOS Fabrication**

# Oxide Growth

- There are two ways to provide the Oxygen for SiO<sub>2</sub> growth

"Dry Oxidation"

- we use O<sub>2</sub> gas in a chamber with the Silicon

- this can achieve thin layers of SiO<sub>2</sub> for gates, <100nm

- No byproduct

"Wet Oxidation"

- we use water (H<sub>2</sub>0) liquid as the source

- the Silicon is submerged in water

- this process can achieve thick layers of SiO<sub>2</sub> for masking, 1-2um

- the byproduct of this process is Hydrogen, which must be disposed of

ECOM 5335 - VLSI Design

# Oxide Growth

- If heat is added to the process, the rate of  $\mathrm{SiO}_2$  growth is sped up considerably

- This is called "Thermal Oxidation"

- Applies to both Wet and Dry processes

- Temperatures usually are in the range of 700 1300 C

#### **CMOS Fabrication**

# **Etching**

- Etching is the process of removing material from the substrate

- Etches can remove Si,  $\mathrm{SiO}_2$ , polysilicon, and metal depending on what we want to accomplish

#### **CMOS Fabrication**

# **Etching**

- There are two common types of etch processes

- " Wet Etch"

- also called Chemical Etch

- this uses Hydrofluoric Acid (HF acid)

- the wafer is submerged in the acid

#### **CMOS Fabrication**

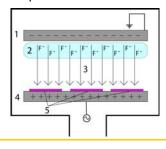

- " Dry Etch"

- Also called Plasma Etch/Reactive-Ion Etch (RIE)

- Plasma is a charged gas which has excited ions (i.e., free electrons in the outer orbital)

- Plasma can be moved by applying an E-field

- The wafer is put in a chamber with an Anode and Cathode Disk on top and bottom

- A gas is put in the chamber and charged to ionize it

ECOM 5335 - VLSI Design

- " Dry Etch"

- The Anode is energized with an AC signal (13.56MHz)

- This makes the plasma move back and forth between the Anode and Cathode

- As the Plasma makes contact with the wafer, it will chemically react with the outer layers of the wafer

- The chemical reaction forms a new compound that is loose and may be removed

- Since the ions move up and down, we can make a very

vertical etch pattern

ECOM 5335 - VLSI Design

Module #3 Page 21

#### **CMOS Fabrication**

# **Etching**

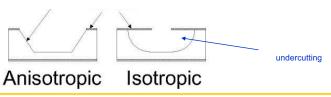

- When talking about etching, we typically talk about the etch patterns that can be formed

Isotropic

- etches equally in all direction

- wet etch is isotropic

- this etch leads to "undercutting"

Anisotropic

- the etch rate is dependant on the direction of the etch

- dry etch is anisotropic

ECOM 5335 - VLSI Design

Module #3 Page 22

#### **CMOS Fabrication**

# **Deposition**

- The process of "adding" material to the wafer (as opposed to growing, which consumes part of the target)

- This is how we put down the polysilicon layer for the gate contact (in addition to insulators and metal)

- Polysilicon is a polycrystalline material (SiH4) which is a conductor

- Polysilicon originally starts with a high resistivity, but when doped its resistively comes down

- The most common type of deposition is Chemical Vapor Deposition (CVD)

### **CMOS Fabrication**

# **Deposition**

# **Chemical Vapor Deposition**

- The wafer is put into a chamber with a gas (i.e., Si and H2)

- The gas then forms a chemical reaction with the Silicon dioxide (SiO2) and Silicon to form a bond, the polysilicon is then added via chemical reactions.

- Somewhat similar to dry oxidation, but without the consumption of the wafer

- This process can be used for polysilicon, metals, SiO2 and Nitride (Si3N4)

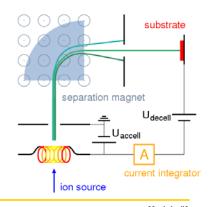

#### Ion Implantation

- The process of adding impurities to a silicon wafer

- The wafer is put in a chamber with an Ion source (i.e., B, P, As)

- The lons are accelerated toward the wafer using an E-field

- The lons collide with the wafer, tunneling into the crystal structure

ECOM 5335 - VLSI Design

Module #3 Page 25

#### **CMOS Fabrication**

#### Ion Implantation

- Photolithography allows us to selectively implant the regions we want (i.e., N-wells, Sources, Drains)

- As the impurities crash into the crystal, they damage or break the covalent bonds

- We can repair these bonds using a process called *annealing*, which heats the material up and then slowly cools it down allowing the new bonds to form

ECOM 5335 - VLSI Design

Module #3 Page 26

#### **CMOS Fabrication**

#### Fab Processes

- Now we have all of the basic ingredient for an IC Fab:

Silicon Wafer Creation

- Ingots are grown in crucible starting with a Seed crystal. The ingots are cut into thin disks and polished to form the Si wafer.

**Photolithography**

Transferring a pattern to the wafer using masks to selectively expose regions to UV light with either protect or expose areas on the wafer.

**Photoresist**

Normally insoluble material which becomes soluble when exposed to UV light. The soluble regions can be removed by acid to expose the regions beneath.

Oxide Growth

- Growing an SiO2 directly on the Silicon wafer using either a Wet or Dry process. The growth consumes part of the wafer.

Etching

- process of removing material (Si, SiO<sub>2</sub>, polysilicon, metal) using either a wet (chemical) or dry (plasma) process.

Deposition

- Process of adding material ( $\mathrm{SiO}_2$ , nitride, poly, metal) using

CVD/PVD

Ion Implantation

- Process of adding impurities or doping (ni  $\rightarrow$  N<sub>A</sub>, N<sub>D</sub>)

ECOM 5335 - VLSI Design

Module #3 Page 27

#### **CMOS Fabrication**

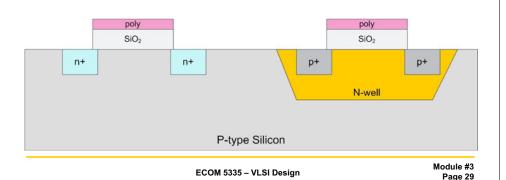

# Bulk Doping

- The first step in creating an IC is to dope the entire Si wafer to p-type

- For a CMOS process, both NMOS and PMOS transistors are present

- Remember that: N-Channel transistors require P-type substrates P-Channel transistors require N-type substrates

- We can avoid the process of selectively doping each N-channel and P-channel's substrate region by doping the entire wafer first

- So should we dope the whole thing N-type or P-type?

- There are going to be many more N-Channel devices on the wafer

- SRAM requires 6 transistors (4 NMOS, 2 PMOS)

- DRAM requires 1 transistors (1 NMOS)

- Other circuit techniques exists in addition to CMOS that only use NMOS transistors for higher performing logic circuitry.

# **Bulk Doping**

- With the entire wafer being p-type, we can directly form N-channel devices

- To make a p-channel device, we create a region of n-type material to act as the local substrate

- This is called an N-well.

#### **CMOS Fabrication**

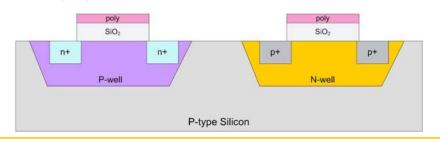

#### **Bulk Doping**

- Sometimes we wish to dope the P-type substrate even further than what is provided by bulk doping

- We can create a P-well region to increase the substrate doping density (N<sub>A</sub>)

- This configuration is called a Twin Tub

- We won't use this in ECOM5335, but we want to know what people mean when they say Twin Tub

ECOM 5335 - VLSI Design

Module #3 Page 30

#### **CMOS Fabrication**

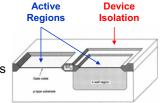

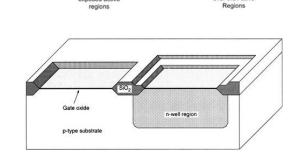

# **Active Regions (Device isolation)**

- When we create multiple transistors on the same substrate, the electrical operation of one transistor can effect the operation of adjacent transistors

- coupling

- inadvertent inversion layers

- parasitic conduction paths

- The first step in fabrication is to create an isolation layer on the wafer that defines where the MOSFETs will be located.

Module #3

Page 31

- This isolation region is made up of SiO<sub>2</sub> called Field Oxide and Channel-Stop Implants (p+)

- This Oxide region is relatively thick and sometimes called *Thick Oxide* (thin oxide is what we call the gate oxide)

- The Silicon regions where we put our MOSFETs are called *Active Regions*

1) P+ channel stop implants

in order to form a more planar surface

- The isolation regions are formed by two layers

2) Thick SiO<sub>2</sub> insulator (Thick Oxide or Field Oxide)

# **CMOS Fabrication**

# Active Regions (Device isolation)

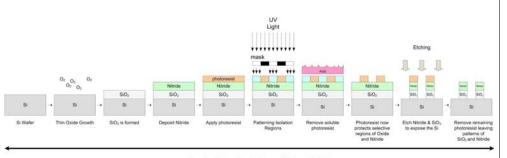

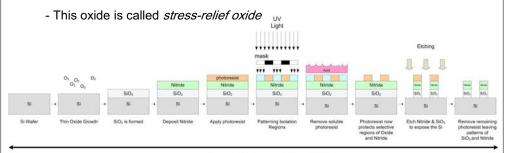

- One of the most popular techniques to create isolation between Active Regions is called

# Local Oxidation of Silicon (LOCOS)

- In LOCOS, we selectively *grow* field oxide (as opposed to growing it everywhere and then selectively etching)

- This has the advantage of actually recessing into the Silicon, i.e., consuming some of the Silicon

# **Active Regions (Device isolation)**

- The first step is to cover the Active Regions so that when we dope the channel-stop implants, the active regions are protected

- We use Nitride (Si<sub>2</sub>N<sub>4</sub>) to protect these regions. It inhibits SiO<sub>2</sub> growth

Creating Protective Patterns of SiO2 and Nitride

ECOM 5335 - VLSI Design

Module #3 Page 33

#### **CMOS Fabrication**

# **Active Regions (Device isolation)**

- Nitride is a good material for shielding but has a very different coefficient of thermal expansion than Silicon. As such, it can put a lot of mechanical stress on the wafer when heated and lead to cracks.

- To avoid this, we put a layer of thin oxide (SiO<sub>2</sub>) in between the Nitride and Silicon wafer which absorbs the mechanical stress.

Creating Protective Patterns of SiO2 and Nitride

ECOM 5335 - VLSI Design

Module #3

Page 34

#### **CMOS Fabrication**

# **Active Regions (Device isolation)**

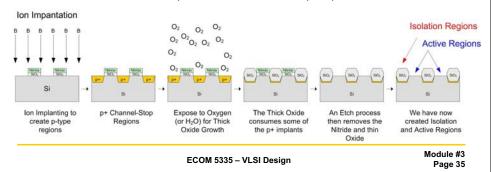

- Next, we implant Boron into the exposed Silicon to form the Channel-Stop *Implants*

- Then we grow thick Oxide on the exposed regions, noting that Oxide will not grow on the Nitride

- The Oxide will consume part of the Channel-Stop-Implants

#### **CMOS Fabrication**

#### Review

- We've talked about the basic process steps that are required for IC fabrication

- Crystal growth

- photolithography, photoresist, masks

- oxide growth

- etching

- deposition

- ion implantation

- We've started talking about the major process stages:

- Bulk Doping

- Isolation (Active Region, LOCOS)

- Now let's put everything together and walk through the creation of a full CMOS inverter

# Major Process Steps

- This flow chart shows the major process steps for a CMOS integrated circuit

fabrication

Create n-well regions and channel-stop regions

Grow field oxide and gate oxide (thin oxide)

Deposit and pattern polysilicon layer

Implant source and drain regions, substrate contacts

Create contact windows, deposit and pattern metal layer

ECOM 5335 - VLSI Design

Module #3 Page 37

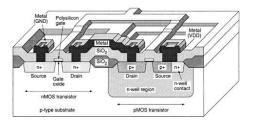

#### CMOS Fabrication

# Major Process Steps

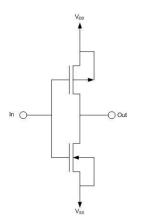

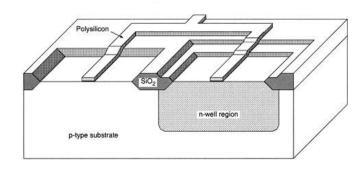

- Let's look at the design of a CMOS inverter:

- Some things to note:

- This takes both an NMOS and PMOS

- We need body connections for each MOSFET

- The Gates are connected together (poly)

- The Drains are connected together (metal)

ECOM 5335 – VLSI Design Module #3

Page 38

#### **CMOS Fabrication**

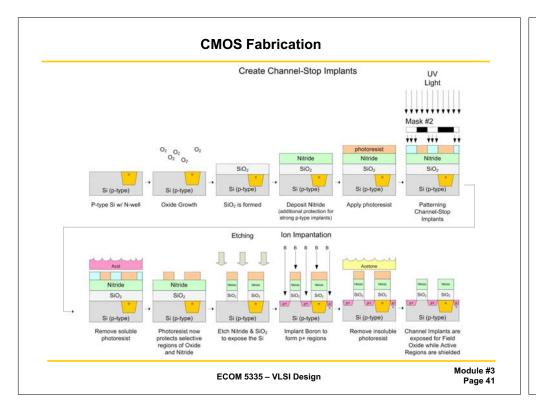

#### CMOS Inverter Fab

- We start by creating the N-well (for the P-channel devices) and the Channel-stop implants

- This takes two full process/photolithography steps

- Things to note:

- The photoresist by itself will not shield the Silicon from Ion Implantation. As a result, we use Oxide or Nitride to block the implants.

- We remove the hardened (insoluble) photoresist using a chemical such as Acetone

- We can etch away Oxide or Nitride

- We need the Oxide/Nitride to be thick enough to completely block the implants

- The Ion implants actually go through the photoresist and hit the Oxide.

ECOM 5335 - VLSI Design

Module #3

Page 39

#### **CMOS Fabrication** Create N-Wells UV Light O<sub>2</sub> O<sub>2</sub> SiO<sub>2</sub> SiOz SiO<sub>2</sub> SiO<sub>2</sub> Si (p-type) Si (p-type) Si (p-type) Si (p-type) Si Wafer (p-type Oxide Grow N-Well Patterni Remove soluble photoresist Ion Impantation Etching Etching SIO SiO Si (p-type) Etch SiO<sub>2</sub> to Etch SiO<sub>2</sub> to End result is an protects selective regions of Oxide Phosphorus to Module #3 ECOM 5335 - VLSI Design Page 40

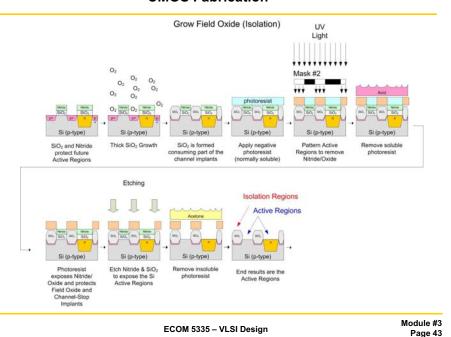

#### CMOS Inverter Fab

- We now grow the Field Oxide on top of the Channel Stop Implants to complete the Isolation Regions. Note that:

- The Nitride prevents Oxide growth over the Active Regions

- Once the Oxide has grown, we need to remove the Nitride/Oxide regions using another photolithography step

- Notice these regions are the negative of Mask #2 so it is possible to use Negative photoresist and Mask #2 to save a reticle.

- Once this is done, we have defined the Active Regions, which are where the MOSFETs will be located.

- We begin creating the MOSFETs by growing the Field Oxide (thick)

ECOM 5335 - VLSI Design

Module #3 Page 42

Create n-well regions and channel-stop regions

Grow field oxide and gate oxide (thin oxide)

Deposit and pattern

Implant source and drain

#### **CMOS Fabrication**

# **CMOS Fabrication**

Grow Thin Oxide (Gate Oxide)

Si (p-type)

Thin SiO<sub>2</sub> Growth

exposed active

Thin Oxide (Gate)

Gate Oxide is formed

over the Active

ECOM 5335 – VLSI Design

Page 44

Module #3

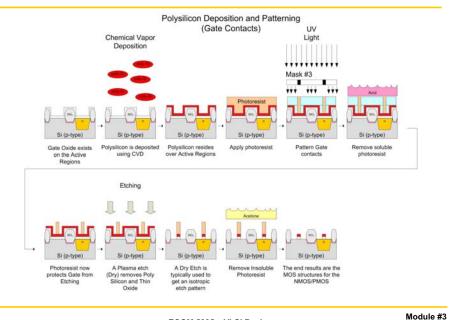

#### CMOS Inverter Fab

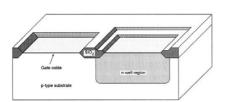

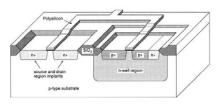

- We now deposit the polysilicon layer using chemical vapor deposition

- This will act as the Gate contact

- Sometimes metals are used such as Aluminum

- We pattern the material using a Dry Etch to get an anisotropic pattern

ECOM 5335 - VLSI Design

Module #3 Page 45

# CMOS Fabrication

ECOM 5335 - VLSI Design

Page 46

#### **CMOS Fabrication**

#### **CMOS Fabrication**

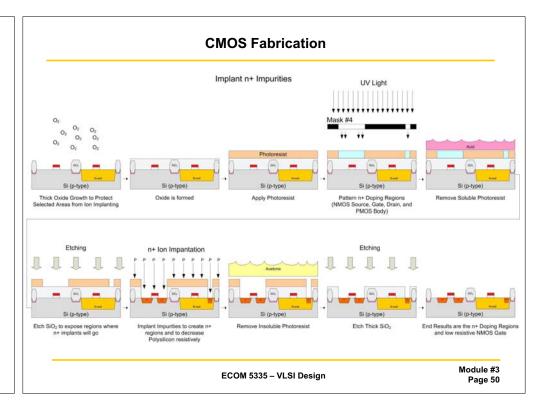

#### CMOS Inverter Fab

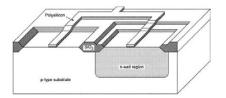

- We now implant or *dope* the Source, Drain, and Body contacts

- remember that Polysilicon has a high resistivity at this point. It will need to be doped for it to become a low-resistive conductor.

#### CMOS Inverter Fab

- A note on Substrate Connections:

- The NMOS needs a Body contact the same as the Source (GND)

- The PMOS needs a Body contact the same as the Drain  $(V_{DD})$

- A Metal to lightly doped semiconductor forms a poor connection called a "Shottky Diode"

- When making a metal connection to a semiconductor, we need to form an "Ohmic contact", which has a linear IV curve (i.e., a resistor).

- The Ohmic contact is formed by heavily doping the Semiconductor prior to attaching the metal

- We use p+ doping for the NMOS Body contact

- We use n+ doping in the N-well for the PMOS Body contact

ECOM 5335 - VLSI Design

Module #3 Page 49

# **CMOS Fabrication** Implant p+ Impurities **UV** Light Mask #5 Thick Oxide Growth to Protect Apply Photoresist Pattern p+ Doping Regions Remove Soluble Photoresist (PMOS Source, Gate, Drain, and NMOS Body) Selected Areas from Ion Implanting Etching End Results are the p+ Doping Region regions and to decrease Polysilicon resistively p+ implants will go Module #3 ECOM 5335 - VLSI Design Page 51

# CMOS Fabrication Polysilicon Newell region Polysilicon Polysilicon Newell region Polysilicon Polysilicon Newell region Polysilicon Newell region Polysilicon Module #3 Page 52

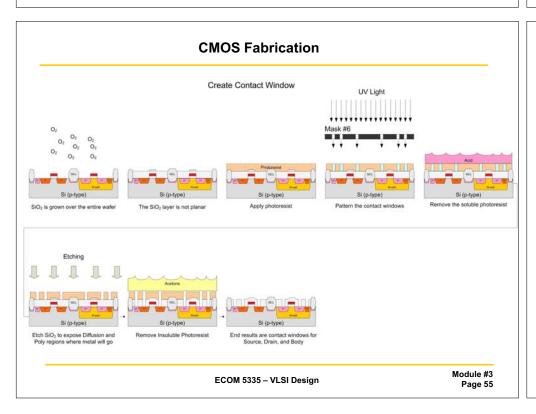

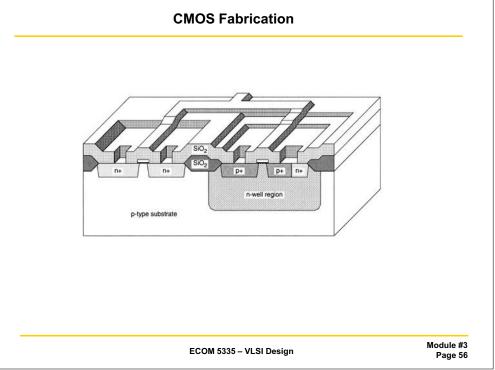

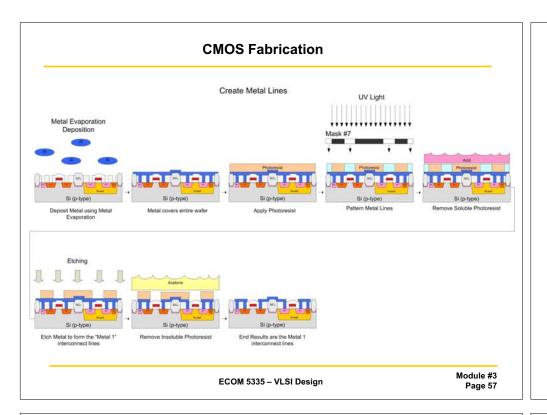

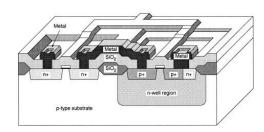

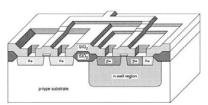

#### CMOS Inverter Fab

- Now we are ready to add the Metal contacts for the Source/Drain/Body

- The first thing we do is put an insulating layer of  ${\rm SiO_2}$  over the entire wafer using CVD

- Note that this is *deposition* instead of *growth* because we don't have access to the Silicon wafer to start the SiO<sub>2</sub> growth

- We then use a photolithography step to expose the contact windows, which is where the metal interconnects will go

- The metal contacts are made to the deposition regions (Source/Drain/Body) and to the Gate (Polysilicon)

- Metal (aluminum) is then deposited over the entire wafer using metal evaporation (similar to CVD)

- The Metal lines are then patterned through another photolithography step.

ECOM 5335 - VLSI Design

Module #3 Page 53

Create n-well regions and channel stop regions

Grow field oxide and gate oxide (thin oxide)

Deposit and pattern polysiloon laver

# CMOS Inverter Fab Things to note This metal layer is called "Metal 1". The metal layer goes on top of a very non-planar surface The metal layer goes on top of a very non-planar surface Deposit and pattern polyellon layer Deposit and pattern metal layer Create contact windows, deposit and pattern metal layer ECOM 5335 – VLSI Design Module #3 Page 54

ECOM 5335 - VLSI Design

Module #3 Page 58

#### **CMOS Fabrication**

#### CMOS Inverter Fab

- Let's review the 7 Mask steps we described in this process:

- 1) N-well

- 2) Channel-Stop Implants

- 3) Polysilicon

- 4) n+ Diffusion

- 5) p+ Diffusion

- 6) Contact Windows

- 7) Metal

- These 7 mask steps allow us to:

- Create MOSFETs

- Connect them together to form basic gates

#### **CMOS Fabrication**

# CMOS Inverter Design

- We design the shapes of the circuits in a CAD tool

- The physical design of the shapes is called *Layout*

- We'll use **Electric** as our tool

- We can enter schematics and simulate the circuits

- We can then layout the circuits, perform DRC and LVS/NCC

- The ultimate output of the tool will be the Mask artwork

- We send the mask artwork to the fab, give them some \$\$\$, then IC's show up (this is a somewhat simplified description!)

- When designing, we layout the shapes from the Top View

- We looked at the design from the side view to see how the process steps create the geometries

- Next time we'll start looking at the top view.

# · CMOS Inverter Design

- We design the shapes of the circuits in a CAD tool

- The physical design of the shapes is called *Layout*

- When designing, we layout the shapes from the Top View

- Let's see how we would design this inverter from the top view

Module #3 Page 61

# CMOS Inverter Design

- Define the Active Regions

- Define the N-well (and P-well if using) (Mask #1)

and

the Channel Stop Implants (Mask #2)

ECOM 5335 - VLSI Design

**CMOS Fabrication**

Module #3 Page 62

#### **CMOS Fabrication**

ECOM 5335 - VLSI Design

# CMOS Inverter Design

- Deposit and Pattern the Polysilicon (Mask #3)

Module #3 Page 63

# **CMOS Fabrication**

# CMOS Inverter Design

- Implant the n+ diffusion regions (Mask #4)

and

p+ diffusion regions (Mask #5)

# CMOS Inverter Design

- Open contact windows

(Mask #6)

ECOM 5335 - VLSI Design

Module #3 Page 65

#### **CMOS Fabrication**

# CMOS Inverter Design

Deposit and Pattern Metal 1 interconnect

(Mask #7)

ECOM 5335 - VLSI Design

Module #3 Page 66

#### **CMOS Fabrication**

# CMOS Inverter Design

- We're able to draw basic shapes in the CAD tool which imply a sequence of process steps

# Example:

- We draw a rectangle indicating the NMOS Active Region and the PMOS Active Regions

- Two rectangles in the CAD tool = 2 Masks + dozens of process steps

- As such, CAD tools are linked to a fabrication process. This is called a "Design Kit"

- A Design Kit is tied to a specific process (i.e., TSMC 0.18um, AMI 0.5um, MMF 5um)

#### **CMOS Fabrication**

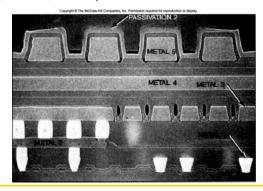

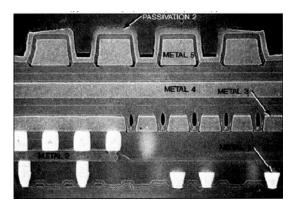

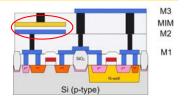

# Upper Metal Layers

- To connect Basic Gates together to form more advanced logic circuits, we need more Interconnect layers.

- We number the metal layers sequentially going upward as they are added (i.e., Metal 2, Metal 3, Metal 4)...

#### Upper Metal Layers

- To connect Metal layers together, we use *vias*. These are very similar to contacts, but typically Tungsten is used as the material

ECOM 5335 - VLSI Design

Module #3 Page 69

#### **CMOS Fabrication**

#### Upper Metal Layers

- As we go up in metal layers, the uncertainty of making contact on each subsequent process step increases. So we need to use larger and larger features to overcome this error and guarantee contact.

ECOM 5335 - VLSI Design

Module #3 Page 70

#### **CMOS** Fabrication

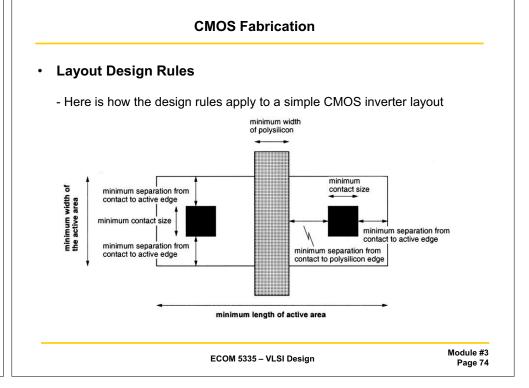

# Layout Design Rules

- A given fabrication process defines the smallest feature that can be created in any given process step.

- It also defines how close things can be together

- A set of *Design Rules* are defined for a process that the designers use.

- Layout rules can be defined in two ways:

- 1) Micron Rules: feature sizes and separations are stated in terms of absolute sizes (i.e., 1um, 0.8um)

- 2) Lambda Rules: feature sizes and separations are stated in terms of a single parameter called Lambda ( $\lambda$ ).

The Lambda rules simplify scaling from process to process.

#### **CMOS Fabrication**

# Layout Design Rules

- The Design Kit for a given process also defines the Design Rules

- As we layout the design, we periodically run a check to make sure we are not violating the design rules of the process. This is called a

# Design Rule Check (DRC)

Since we enter our circuits in a schematic and then do the physical design in a separate layout tool, we need a way to make sure that our Layout matches our Schematic. Another check that is ran periodically is called:

Layout versus Schematic (LVS) OR Network Consistency Check (NCC)

- We will learn how to run these checks once we get into Electric.

# CMOS Fabrication • Layout Design Rules - Here is an example of some Lambda Design Rules from MOSIS MOSIS Layned Design Rules Rule number Description A-Rule Active area rules Rul Mainton active reas viola Rul Mainton poly south Rul Mainton poly south Rul Mainton poly south Rule Mainton poly counts to poly dep specing Rule

Module #3

Page 73

# **CMOS Fabrication Layout Design Rules** - Here is how the design rules apply to a simple CMOS inverter layout n-well pMOS minimum overlap of n-well over p+ active area INPUT n+ active area and n-well OUTPUT metal-poly GND nMOS nMOS Module #3 ECOM 5335 - VLSI Design Page 75

ECOM 5335 - VLSI Design

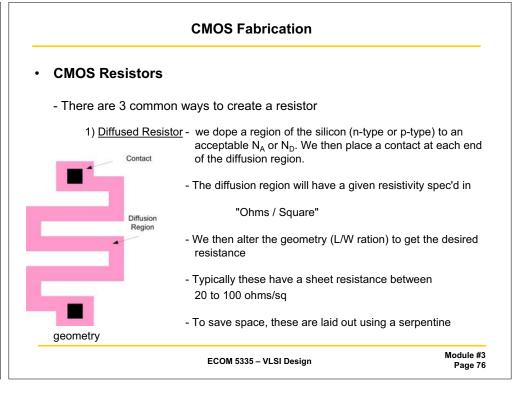

#### **CMOS Resistors**

- A note on resistivity and Ohms/square

- Resistance is given by:

$$R = \frac{l \cdot \rho}{A} = \frac{l \cdot \rho}{W \cdot H}$$

- In a CMOS process, the Height of the trace is fixed.

- In addition, the *resistively* ( $\rho$ ) is also fixed for the material.

- This means that the  $(\rho/H)$  is a constant with units of Ohms

- We define this constant as the Sheet Resistance (R<sub>s</sub>)

- We multiply this by //W to find the total resistance

ECOM 5335 - VLSI Design

Module #3 Page 77

#### **CMOS Fabrication**

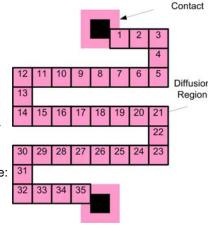

#### **CMOS Resistors**

- The interesting thing about the \( \lambda W \) ratio is that if I=W, then the shape is a *square* and R=R<sub>s</sub>

- This is true no matter how big the square is.

- In fact, the I/W ratio is actually the number of squares in a given trace geometry

- We typically just count the squares and use:

$$R = R_s \cdot (\#\_of\_squares)$$

ECOM 5335 - VLSI Design

Module #3 Page 78

Page 80

#### **CMOS Fabrication**

### **CMOS Resistors**

## 2) Polysilicon Resistor

- Anther way to fabricate a resistor is to use Polysilicon.

- Remember that Polysilicon has a high resistivity prior to Ion **Implantation**

- We can use undoped Polysilicon to create a high value R Before Ion Implantation :  $R_s = 10M$  Ohms/Square  $R_s = 20$  to 40 Ohms/Square After Ion Implantation:

- Typically don't even need 1 square to get our resistivity so we don't need to do a serpentine layout

- One drawback is that the resistance can vary widely with process when using less than 1 square to get a resistor in the k-Ohms range.

- these are typically used when we just want a BIG resistor and don't care about the exact value

ECOM 5335 - VLSI Design

Module #3 Page 79

#### **CMOS Fabrication**

#### **CMOS Resistors**

#### 3) Metal Resistor

- Metal can also be used for very small resistors

- The M1 layer typically has sheet resistance on the order of mOhms/sq.

- We can use a serpentine layout to get a small resistor (1-10 ohms)

#### CMOS Capacitors

- There are 3 common ways to make a capacitor

- 1) MOS Capacitor

- We simply create a MOS structure where the Gate (Metal) terminal is one terminal and the Body (Semiconductor) terminal is Ground

- While this is easy to implement, the capacitance changes with the bias voltage (i.e., V<sub>G</sub>) due to the depletion and inversion which occurs

ECOM 5335 - VLSI Design

Module #3 Page 81

#### **CMOS Fabrication**

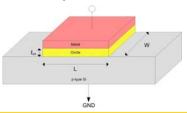

# CMOS Capacitors

### 2) MIM Capacitor

- This is simply a parallel plate capacitor using two metals and an insulator

- Typically this type of capacitor is created using an extra process step that puts in an additional metal layer that can be very close to one of the other metal layers to get a smaller plate-to-plate separation

- since the plates are made of metal, the capacitance doesn't change with bias voltage

- these capacitors are not as large as MOS capacitors

ECOM 5335 - VLSI Design

Module #3 Page 82

#### **CMOS** Fabrication

# CMOS Capacitors

3) Fringe Capacitor

- Fringe capacitance refers to the capacitance that comes from the area of the sides of the plate.

- Since the plates are thin, we typically ignore this

- However, when we bring metals together on the same layer, the fringe capacitance can become significant

- If we interleave metal fingers, we can take advantage of the fringe capacitance to create a capacitor

#### **CMOS Fabrication**

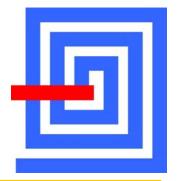

#### CMOS Inductors

- Inductors are difficult to fabricate in CMOS

- They take a lot of area and have significant parasitic resistance and capacitance

- They are typically only used in RF applications

#### Spiral Inductor

- We use 1 metal layer to create a spiral

- We use another metal layer to get contact the inside of the spiral

Module #3 Page 83

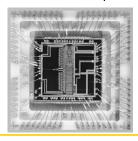

# IC Packaging

- We continue connecting all of our MOSFETS, Resistors, and Capacitors together using Metal layers and vias

- Once we're done, we need to connect our IC to the outside world.

- We need to put the silicon die into a Package

- An IC package performs the following functions

- 1) Protects the die from the outside world (contamination, etc...)

- 2) Translates the on-chip interconnect density (um) to the off-chip interconnect density (mm)

- 3) Moves the heat from the die to the outside world so it can be dissipated

- We need to put pads on the outermost metal layer for the package leads to connect to.

- The interconnect that goes from the IC to the package is called *Level 1* Interconnect

ECOM 5335 - VLSI Design

Module #3 Page 85

#### CMOS Fabrication

## IC Packaging

#### Wire Bond

- The most widely used package interconnect is a wire bond.

- This is a thin gold wire that connects the pads on the IC to the package *leads*

- To accommodate a wire bond, we put pads around the perimeter of the IC

- The pads are relatively large (100um x 100um)

ECOM 5335 - VLSI Design

Module #3 Page 86

#### **CMOS Fabrication**

# IC Packaging

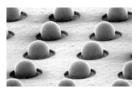

#### Flip Chip

- A higher performing and higher density interconnect is called a flip-chip bump

- A bump is a sphere of solder that is used to connect pads on the IC to the package

- The main advantage is that we can put an array of pads, instead of just pads around the perimeter

- This allows many more pads to be placed on the same die area

- The pads are still relatively large (100um x 100um)

# **CMOS Fabrication**

# IC Packaging

# Package Interconnect

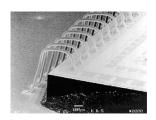

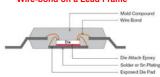

- The package itself has an interconnect which ultimately connects the packaged IC to the system PCB (Level 2)

- The two most common types of Level 2 interconnect are:

- 1) Lead Frame

- 2) Ball Grid Array

- Once the die has been connected to the packag interconnect, we put encapsulate it in a protective material (plastic, epoxy, etc....)

- This provides the protection for the die and is what we typically see when we look at a packaged part (i.e., the black plastic)

#### Wire-bond on a Lead Frame

Flip-Chip on a BGA

Module #3 ECOM 5335 - VLSI Design Page 88