University of California College of Engineering Department of Electrical Engineering and Computer Sciences

E. Alon

Thursday, November 4, 2010 6:30-8:00pm

## EECS 141: FALL 2010-MIDTERM 2

For all problems, you can assume that all transistors have a channel length of 100nm and the following parameters (unless otherwise mentioned):

**NMOS:**   $V_{Tn} = 0.3 \text{V}, \ \mu_n = 400 \text{ cm}^2/(\text{V}\cdot\text{s}), \ \text{C}_{\text{oxn}} = 1 \ \mu\text{F/cm}^2, \ v_{\text{sat}} = 1e7 \text{ cm/s}, \ \lambda = 0$  **PMOS:**  $|V_{Tp}| = 0.3 \text{V}, \ \mu_p = 200 \text{ cm}^2/(\text{V}\cdot\text{s}), \ \text{C}_{\text{oxp}} = 0.75 \ \mu\text{F/cm}^2, \ v_{\text{sat}} = 1e7 \text{ cm/s}, \ \lambda = 0$

|  | GRAD/UNDERGRAD |  |

|--|----------------|--|

|--|----------------|--|

- Problem 1: \_\_\_\_/ 24

- Problem 2: \_\_\_\_/ 18

- Problem 3: \_\_\_\_/ 24

- Total: \_\_\_\_/ 66

## PROBLEM 1. (24 pts) Wires, Delay, and Ratioed Logic

For this problem, you should assume that all of the transistors are minimum channel length (L=0.1µm) and have the following characteristics:  $C_G = C_D = 2fF/\mu m$  and  $R_{sqn} = R_{sqp}/2 = 10k\Omega/\Box$ . For the wires, you should assume that  $C_{wpp} = 0.05fF/\mu m^2$ ,  $C_{wfringe} = 0.075fF/\mu m/edge$ , and  $R_{sqw} = 0.1\Omega/\Box$

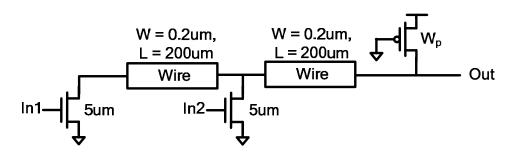

a) (6 pts) For the circuit shown above, size the PMOS pull-up transistor (i.e., choose W<sub>p</sub>) so that the pull-up resistance of the gate is equal to 4 times the worst-case pull-down resistance.

Rull-dure R:

Rw Rw Out

$$\begin{cases}

R_{W} = R_{W} \\

R_{W} \\

R_{W} = R_{W} \\

R$$

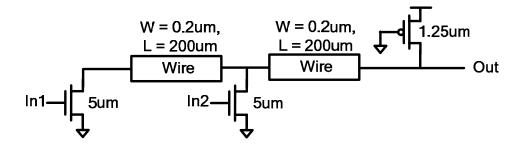

**b)** (10 pts) Assuming that you found that  $W_p = 1.25$ um in order for the pull-up resistance to be 4 times larger than the worst-case pull-down resistance (as shown above – note that this may or may not be the right answer to part a) ), what is the worst-case ramp delay of the circuit?

Since we've sized Rpn to be 4 Rpd, worst ruse delay Will actually be on output rising transition leven despite drive Fight).

$$\frac{R_{W}}{1 - \frac{1}{2}} \begin{pmatrix} R_{W} & R_{V} & C_{0} \\ R_{W} & R_{V} \\ R_{V} & C_{0} \\ R_{W} & R_{V} \\ R_{V} & C_{0} \\ R_{V} & R_{V} \\ R_{V$$

$$R_{pu} = 1.6k\Omega$$

$$C_{0p} = 2FF/\mu m \cdot 1.25\mu m = 2.5FF$$

$$C_{0N} = 2FF/\mu m \cdot 5\mu m = 10FF$$

$$= 0.2\mu m \cdot 200\mu m \cdot 0.05FF/\mu m^{2} + 2\cdot 200\mu m \cdot 0.075FF/\mu m$$

$$= 32FF$$

$$t_p = R_{pu} \cdot (C_{op+2}C_{on+2}C_w)$$

= 1.64.52 (2.5fF+ 20fF+ 64ff)

tp= 138.4ps

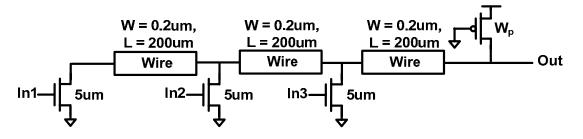

c) (8 pts) Assuming that every time you add another input to the circuit an additional 200um of wire is added as well (as shown above for 3 inputs), and that the pull-up transistor is always resized to make its resistance 4 times that of the worst-case pull-down resistance, what is the worst-case ramp delay of the circuit as a function of the number of inputs (N<sub>in</sub>)?

.

Bused a previous result:

$$p = Rpn \cdot Cop + Rpn \cdot Nin (Lon + Lw)$$

$Rpn \cdot Cop$  is fixed and equal to  $20kp \cdot 0.1pm \cdot 2ff/pm = 4ps$

So we just overs to work on the second term.

$Rpn = 4 Rpd$

$Rpd = Rn + Nin \cdot Rw$

$= 200p + Nin \cdot 100p$

$H Rpn = 400p (2 + Nin)$

$Rpn \cdot Nin (Con + Cw) = 400p (2 + Nin) \cdot Nin \cdot (10fF + 32fF)$

$= 16.8ps (2 + Nin) \cdot Nin$

## PROBLEM 2. (18 pts) Scaling and SRAM Design

Unless otherwise specified, you should assume that  $V_{DD} = 1.2V$  and use the velocity saturated model (with the parameters provided on the first page of the exam) throughout this problem.

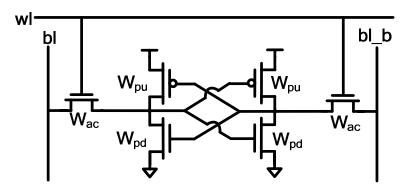

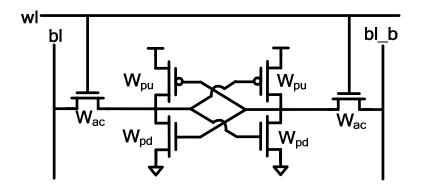

a) (6 pts) Assuming that the  $I_{DSAT}$  of the access transistor must be 1.5 times the  $I_{DSAT}$  of the pull-up transistor (i.e.,  $I_{DSAT_ac} = 1.5*I_{DSAT_pu}$ ) in order to ensure sufficient write margin, what should  $W_{pu}/W_{ac}$  be in our 100nm technology?

When vsut ~ (wh

$$\frac{(V_{00} - V_{TW})^2}{V_{00} - V_{TWT} E_{CNL}} = 1.5 W_{pN} U_{sutp} (up \frac{(V_{00} - V_{TP})^2}{V_{00} - V_{TP} - E_{CPL}}$$

$$\frac{1}{1.5} \cdot \frac{C_{\text{OKN}}}{C_{\text{OKP}}} \cdot \frac{V_{00} - V_{7+} \varepsilon_{\text{Cp}} L}{V_{00} - V_{7+} \varepsilon_{\text{CN}} L} = \frac{W_{\text{pu}}}{W_{\text{ac}}} \quad \varepsilon_{\text{Cn}} L = \frac{2v_{\text{suf}}}{\mu_{\text{m}}} \cdot L = 0.5V$$

$$\frac{W_{pn}}{W_{ac}} = \frac{1}{1.5} \cdot \frac{1}{0.75} \frac{1}{\mu F/cn^{2}} \cdot \frac{1.2V - 0.3V + 1V}{1.2V - 0.3V + 0.5V}$$

$$\frac{W_{pn}}{W_{ac}} \approx 1.21$$

b) (8 pts) If we scale to a 50nm technology with fixed voltage scaling (i.e.,  $V_{DD}$  and  $V_{TH}$  fixed), recalculate the  $W_{ac}/W_{pu}$  required to maintain the same write margin as part a).

c) (4 pts) Given your answer to part b) and assuming that W<sub>pd</sub>/W<sub>ac</sub> is set to 1.5 independent of technology and that the area of the SRAM cell is set by W<sub>ac</sub>\*L+W<sub>pu</sub>\*L+W<sub>pd</sub>\*L, how many times reduction in area is achieved by scaling the SRAM cell from the 100nm technology to the 50nm technology?

Aren, New = (1+1.08+1.5) · Wace, sum · Lour

$$\frac{\text{Areniald}}{\text{Arennew}} = \frac{1+1.21+1.5}{1+1.08+1.5} \cdot \left(\frac{100\text{ mm}}{50\text{ mm}}\right)^2$$

## **PROBLEM 3.** Power Consumption (24 points)

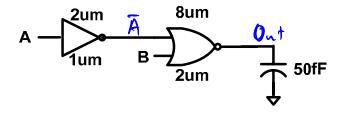

This problem will deal with the circuit shown below. Unless otherwise specified, throughout this problem you can assume that  $V_{DD} = 1.2V$ ,  $V_{THN} = |V_{THP}| = 0.3V$ ,  $C_D = 0$ ,  $C_G = 2fF/\mu m$ , and  $R_{sqn} = 2*R_{sqp}$ . You can also assume that leakage current is modeled by  $(W/L)I_0e^{(-V_{TH}/38mV)}$ , where  $I_{0,NMOS} = 10\mu A$  and  $I_{0,PMOS} = 5\mu A$ .

a) (8 pts) Assuming that the A input is high half of the time, the B input is high 1/8 of the time, and that the circuit runs at a clock frequency of 400MHz, how dynamic much power is consumed by the circuit shown above? Don't forget to include the power consumed by driving the A and B inputs.

A imput:

$$P(A=1)=1/2$$

, so  $\alpha_{0.91,A}=1/4$

$C_{su_{JA}}=1/4$ ,  $2fF/\mu m$ ,  $3\mu m = 1.5fF$

Triveter duesn't medify activity factor, so  $\alpha_{0.91,A}=1/4$

$C_{su_{JA}}=1/4$ ,  $2fF/\mu m \cdot 10\mu m = 5fF$

B imput:  $P(B=1)=1/8$ , so  $\alpha_{0.91,B}=1/8\cdot7/8=7/64$

$C_{su_{JB}}=7/64\cdot2fF/\mu n \cdot 10\mu m = 2.1875fF$

Out:  $P(0ut=1)=P(A=0)\cdot P(B=0)=\frac{1}{2}\cdot\frac{7}{8}=\frac{7}{16}$   $\alpha_{0.91,0ut}=\frac{7}{16}\cdot\frac{6}{16}=\frac{63}{254}$

$C_{su_{J},0ut}=63/256\cdot50fF\approx12.305fF$

$Pd_{1u},1+2(su,1+1)\sqrt{20}\cdot\frac{1}{8}$

b) (8 pts) Under the same conditions as part a), how much leakage power does the circuit consume?

$$\frac{\text{Inverter:}}{\text{Io},p} = \frac{\text{Wp}}{\text{Wn}}, \text{su} \quad \text{leuleuse} \quad \text{independent of state}$$

$$\frac{\text{I}(k_1,m)}{\text{Io},p} = \frac{1}{\text{Wn}}, \quad \text{IU}(p,A) = -\frac{360\text{Wn}}{38\text{W}} = 37.27 \text{WA}$$

$$\frac{NOR}{8} = \frac{1}{9} \frac{1}{8} = \frac{1}{16} = \frac$$

c) (8 pts) Given your answers to parts a) and b), if you could change both the  $V_{DD}$  and  $V_{TH}$  of the transistors in the circuit (but not any of the sizes), how would you change them in order to achieve lower total power consumption without increasing the delay? You do not need to provide any numerical answers – just an explanation of how you would change  $V_{DD}$  and  $V_{TH}$ , and why you would change them that particular way. However, the more specific your answer, the more credit you will receive. (Hint: You can use the  $V_T^*$  model to guide your answer when thinking about delay.)

$$\frac{V_{00,wew}}{V_{00,wew} = 0.325 \text{ V}} = \frac{1.2 \text{ V}}{1.2 \text{ V} = 0.425 \text{ V}}$$

$$\frac{V_{00,wew} \approx 918 \text{ mV}}{V_{00,wew} \approx 918 \text{ mV}}$$

Therefore:

$$P_{dyn,new} = \left(\frac{0.918}{1.2}\right)^2 \cdot 12.1 \mu W \approx 7.08 \mu W$$

$$P_{1k,new} = \left(e^{-200\mu V/36\mu V} / e^{-300-V/36\mu V}\right) \cdot \left(\frac{0.918}{1.2}\right) \cdot 218\mu W \approx 2.32 \mu W$$

$$P_{1ct,new} \approx 9.4 \mu W \qquad (P_{t-t,old} \approx 12.3 \mu W)$$