# <u>EECS150 - Digital Design</u> <u>Lecture 23 - FSMs & Counters</u>

## April 8, 2010 John Wawrzynek

Spring 2010

EECS150 - Lec22-counters

State Encoding

- One-hot encoding of states. Ex: 3 States.

- One FF per state.

STATE1: 001 STATE2: 010 STATE3: 100 FF1 FF2 FF3

- Why one-hot encoding?

- Simple design procedure.

- Circuit matches state transition diagram (example next page).

- Often can lead to simpler and faster "next state" and output logic.

- Why not do this?

- Can be costly in terms of FFs for FSMs with large number of states.

- FPGAs are "FF rich", therefore one-hot state machine encoding is often a good approach.

Page 1

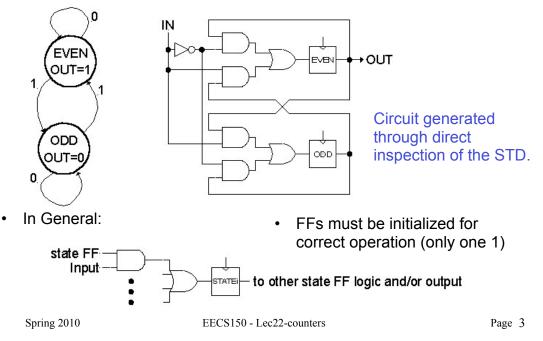

## One-hot encoded FSM

• Even Parity Checker Circuit:

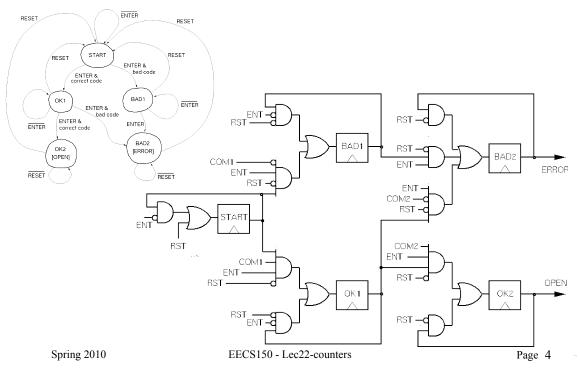

### One-hot encoded combination lock

## **FSM Implementation Notes**

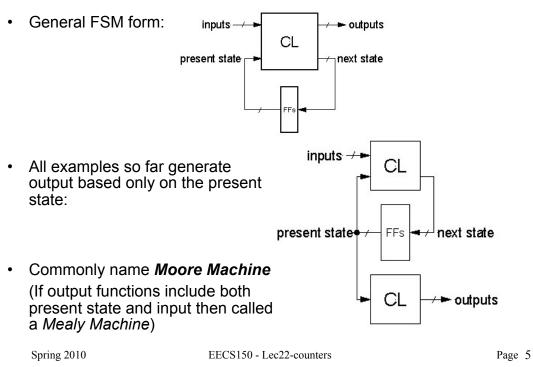

#### **Finite State Machines**

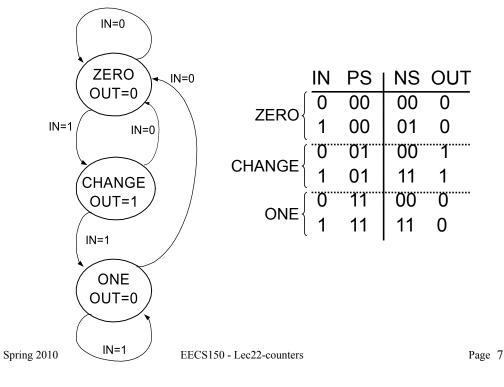

#### • Example: Edge Detector

Bit are received one at a time (one per cycle), such as:  $000111010 \longrightarrow time$

Design a circuit that asserts its output for one cycle when the input bit stream changes from 0 to 1.

Try two different solutions.

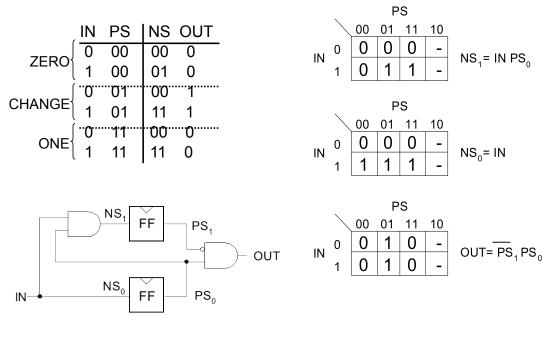

#### State Transition Diagram Solution A

Solution A, circuit derivation

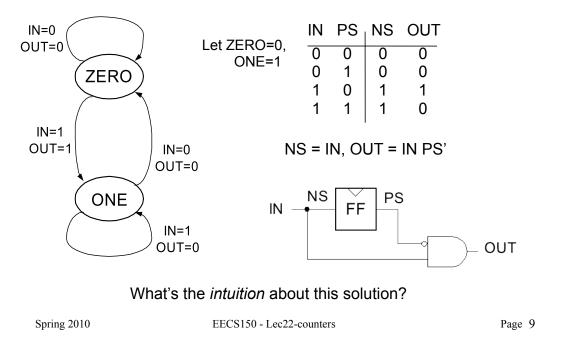

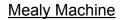

### Solution B

Output depends not only on PS but also on input, IN

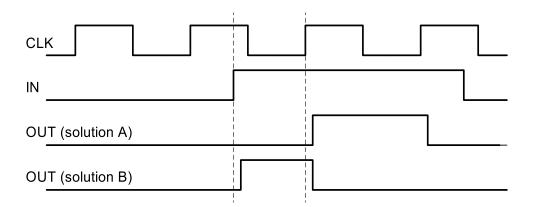

#### Edge detector timing diagrams

- Solution A: output follows the clock

- Solution B: output changes with input rising edge and is asynchronous wrt the clock.

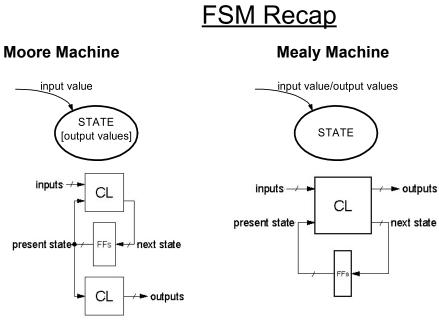

### **FSM Comparison**

#### Solution A **Moore Machine**

- output function only of PS •

- maybe more states (why?) •

- synchronous outputs •

- no glitches

- one cycle "delay"

- full cycle of stable output

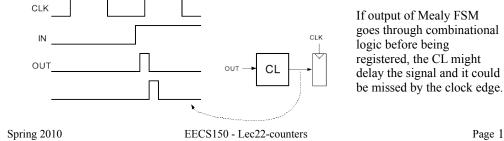

#### Solution B **Mealy Machine**

- output function of both PS & input

- maybe fewer states

- asynchronous outputs

- if input glitches, so does output

- output immediately available

- output may not be stable long enough to be useful (below):

Both machine types allow one-hot implementations.

EECS150 - Lec22-counters

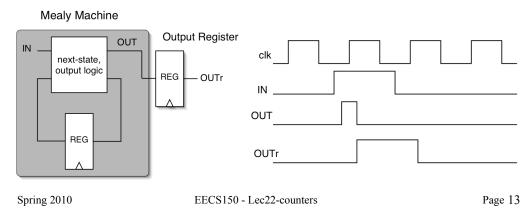

### Final Notes on Moore versus Mealy

- 1. A given state machine *could* have *both* Moore and Mealy style outputs. Nothing wrong with this, but you need to be aware of the timing differences between the two types.

- 2. The output timing behavior of the Moore machine can be achieved in a Mealy machine by "registering" the Mealy output values:

## General FSM Design Process with Verilog

Design Steps: Implementation

- 1. Specify **circuit function** (English)

- 2. Draw state transition diagram

- 3. Write down symbolic state transition table

- 4. Assign encodings (bit patterns) to symbolic states

- 5. Code as Verilog behavioral description

- ✓ Use parameters to represent encoded states.

- ✓ Use separate always blocks for register assignment and CL logic block.

- ✓ Use case for CL block. Within each case section assign all outputs and next state value based on inputs. Note: For Moore style machine make outputs dependent only on state not dependent on inputs.

#### FSMs in Verilog

#### Moore Machine

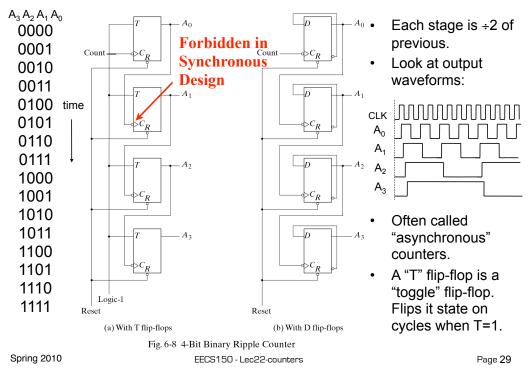

## **Counters**

- Special sequential circuits (FSMs) that repeatedly sequence through a set of outputs.

- Examples:

- binary counter: 000, 001, 010, 011, 100, 101, 110, 111, 000,

- gray code counter: 000, 010, 110, 100, 101, 111, 011, 001, 000, 010, 110, ...

- one-hot counter: 0001, 0010, 0100, 1000, 0001, 0010, ...

- BCD counter: 0000, 0001, 0010, ..., 1001, 0000, 0001

- pseudo-random sequence generators: 10, 01, 00, 11, 10, 01, 00, ...

- Moore machines with "ring" structure in State Transition Diagram:

S2

## What are they used?

- Counters are commonly used in hardware designs because most (if not all) computations that we put into hardware include iteration (looping). Examples:

- Shift-and-add multiplication scheme.

- Bit serial communication circuits (must count one "words worth" of serial bits.

- Other uses for counter:

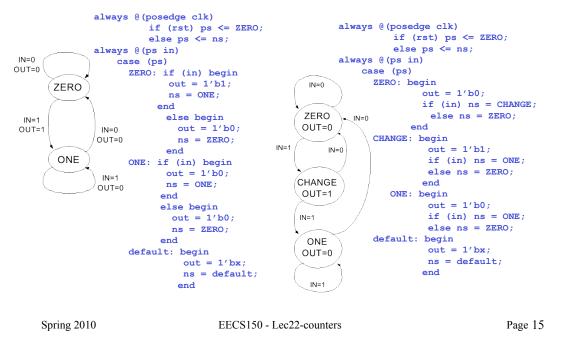

- Clock divider circuits

- Systematic inspection of data-structures

- Example: Network packet parser/filter control.

- Counters simplify "controller" design by:

- providing a specific number of cycles of action,

- sometimes used with a decoder to generate a sequence of timed control signals.

- Consider using a counter when many FSM states with few branches.

```

Spring 2010

```

```

EECS150 - Lec22-counters

```

```

Page 17

```

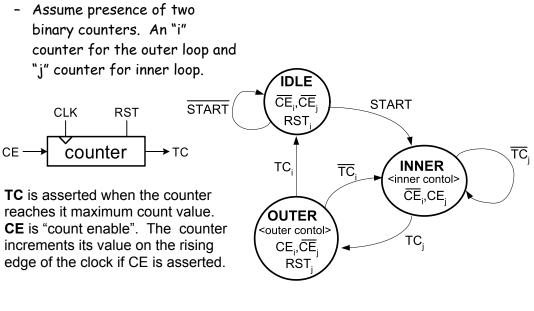

# **Controller using Counters**

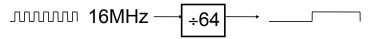

Example, Bit-serial multiplier (n<sup>2</sup> cycles, one bit of result per n cycles):

## **Controller using Counters**

#### • State Transition Diagram:

Spring 2010

EECS150 - Lec22-counters

Page 19

# **Controller using Counters**

Controller circuit Outputs: ٠ implementation:  $CE_i = q_2$  $CE_i = q_1$ START -► q<sub>0</sub> IDLE  $RST_i = q_0$ R  $RST_i = q_2$ TCi shiftA =  $q_1$ ▶ q<sub>1</sub> INNER R S shiftB =  $q_2$ Global reset shiftLOW =  $q_2$ shiftHI =  $q_1 + q_2$ OUTER  $q_2$ reset =  $q_2$ TCj -R selectSUM =  $q_1$

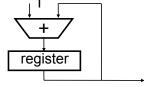

## How do we design counters?

For binary counters (most common case) incrementer circuit would work:

- In Verilog, a counter is specified as: x = x+1;

- This does not imply an adder

- An incrementer is simpler than an adder

- And a counter is simpler yet.

- In general, the best way to understand counter design is to think of them as FSMs, and follow general procedure, however some special cases can be optimized.

Spring 2010

EECS150 - Lec22-counters

Page 21

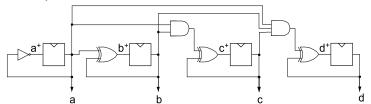

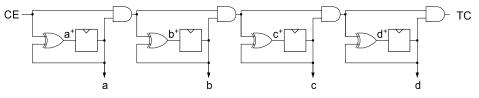

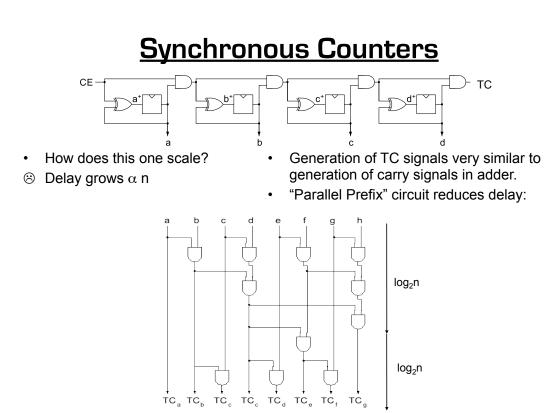

## Synchronous Counters

All outputs change with clock edge.

a+ = a' • Binary Counter Design: c b a c + b + a + b⁺ = a ⊕ b σ 00 00 1 Start with 3-bit version and 001 0 1 0 cb 0 10 011 generalize: a \ 00 01 11 10 1 1 100 0 0 0 0 1 1 0 0 1 101 1 0 1 0 1 0 1 1 1 0 1 1 1 1 1 1 0  $c^+ = a'c + abc' + b'c$ 1 1 1 000 = c(a'+b') + c'(ab)= c(ab)' + c'(ab)= c ⊕ ab C а b С

EECS150 - Lec22-counters

# Synchronous Counters

- How do we extend to n-bits?

- Extrapolate c<sup>+</sup>: d<sup>+</sup> = d  $\oplus$  abc, e<sup>+</sup> = e  $\oplus$  abcd

• Has difficulty scaling (AND gate inputs grow with n)

- · CE is "count enable", allows external control of counting,

- TC is "terminal count", is asserted on highest value, allows cascading, external sensing of occurrence of max value. Spring 2010 EECS150 - Lec22-counters

Page 23

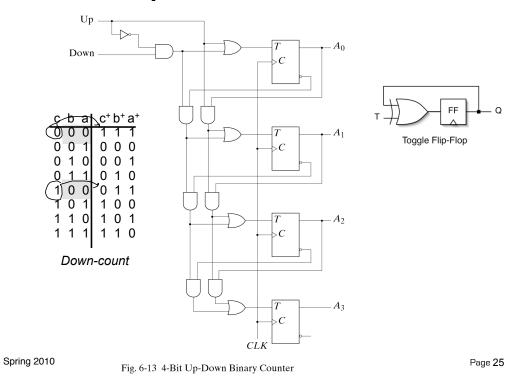

### **Up-Down Counter**

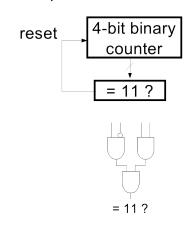

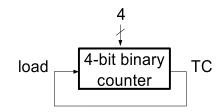

Odd Counts

- Extra combinational logic can be added to terminate count before max value is reached:

- Example: count to 12

• Alternative:

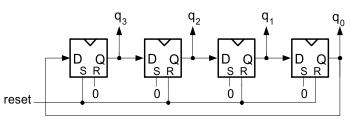

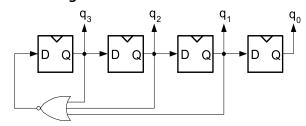

## **Ring Counters**

- "one-hot" counters

- What are these good for?

0001, 0010, 0100, 1000, 0001, ...

"Self-starting" version:

Spring 2010

EECS150 - Lec22-counters

Page 27

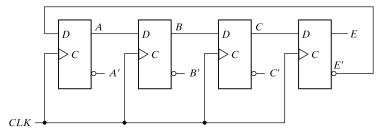

Johnson Counter

(a) Four-stage switch-tail ring counter

| Sequence<br>number | Flip-flop outputs |   |   |   | AND gate required |

|--------------------|-------------------|---|---|---|-------------------|

|                    | Ā                 | В | С | E | for output        |

| 1                  | 0                 | 0 | 0 | 0 | A'E'              |

| 2                  | 1                 | 0 | 0 | 0 | AB'               |

| 3                  | 1                 | 1 | 0 | 0 | BC'               |

| 4                  | 1                 | 1 | 1 | 0 | CE'               |

| 5                  | 1                 | 1 | 1 | 1 | AE                |

| 6                  | 0                 | 1 | 1 | 1 | A'B               |

| 7                  | 0                 | 0 | 1 | 1 | B'C               |

| 8                  | 0                 | 0 | 0 | 1 | C'E               |

(b) Count sequence and required decoding