# Electromigration Failure of Solder Interconnects under Non-DC Conditions: (IEEE-EPS-Bay Area Chapter, 7/16/2021)

Choong-Un Kim Materials Science and Engineering The University of Texas at Arlington 817-272-5497; <u>choongun@uta.edu</u>

This research is supported by SRC and Texas Instruments

#### **Presentation Overview**

- Electromigration (EM) and challenges in EM study

- generalized EM failure mechanism under DC in solder joint

- motivation for studying non-DC EM

- Non-DC EM Testing

- consideration points of EM under DC, pulsed DC, AC

- testing circuits

- Mechanism of EM failure under non-DC conditions

- AC: classic mechanism and results

- pulsed-DC: new failure mechanisms

- Summary and Implications

#### EM failure in WCSP solder joint

## **Electromigration and Research Challenges**

#### Electromigration (EM)

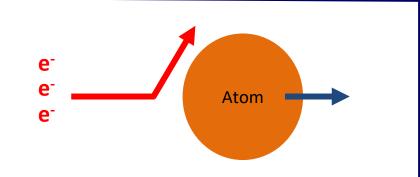

- directional diffusion of atoms driven by high density current

- known to induce failure in solder interconnects and become a major reliability threat due to aggressive miniaturization

- Limiting long-term reliability of microelectronic package

#### EM reliability prediction and challenges

- Adapt Black's empirical model

- Failure mechanism details are still not well understood

- Testing can bias the failure mechanism, leading to the erroneous reliability prediction w/o correction

- EM under non-DC conditions are rarely studied w/ difficulty in experimental testing

$$flux J \approx j \times D_0 exp(-\frac{E}{kT})$$

- : current density

- E: diffusion activation energy

$$ttf \approx Aj^{-n}exp(\frac{E}{kT})$$

- n: current exponent

- E: EM activation energy

## **Non-DC EM in Solder Joint**

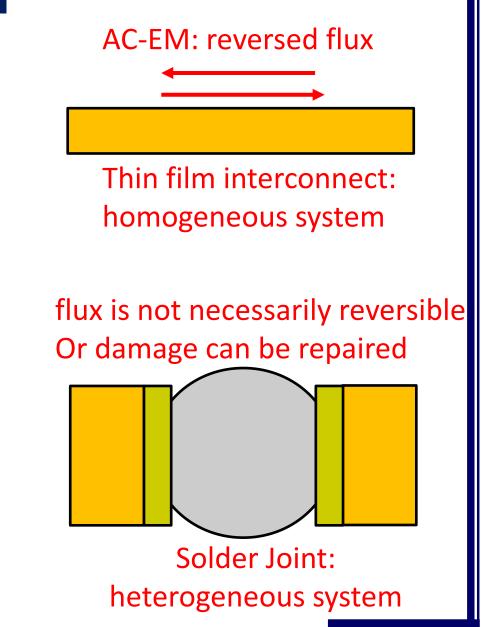

- Understanding may need completely different approaches from thin film interconnects

- EM in thin film interconnect occurs in highly homogeneous system: simple structure, one composition, negligible joule heat

- Pulsed DC and AC effect is reasonably well understood (damage relaxation mechanism)

- EM in solder is complex process

- Multiple components with different EM/diffusion rates

- Interface reaction is a part of failure mechanism

- Considerable level of joule heat can be involved

- Thermal stress can complicate the failure process

### Failure by Non-DC EM: Past Studies

#### Of practical and fundamental importance

- EM load on device can be non-DC (pulsed DC, AC)

- Can reveal key but hidden parameters to consider

- Understanding is seriously lacking for EM in solder joints

#### Existing studies suggests

- Studies are mostly based on classic EM theory (extension of DC to PDC or AC)

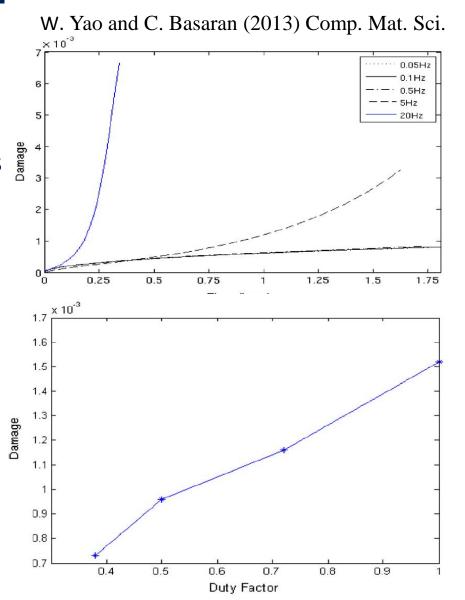

- W. Yao and C. Basaran (2013) computed PDC effect

higher damage rate at higher frequency

(because damage relaxation during "off" cannot occur)

- Z. Zhu, Y. Chan, F. Wu (2019) studied AC effect faster growth of IMC under AC (AC load was not pure AC but was sinusoidal)

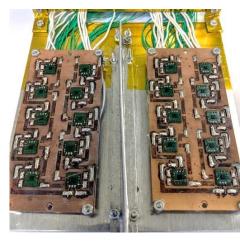

## **Selected Sample for Research**

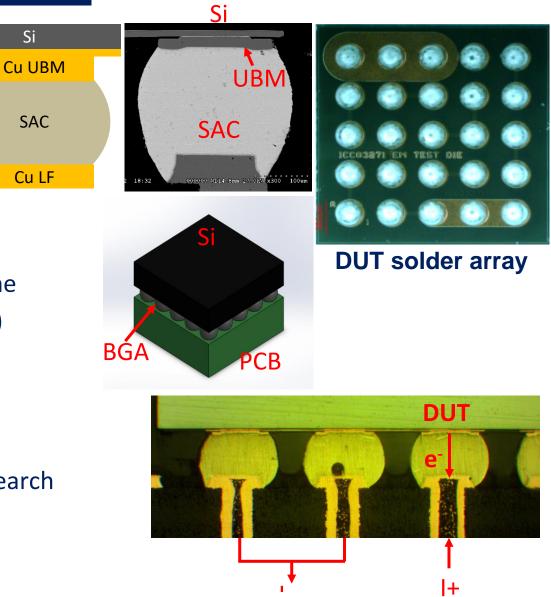

- Wafer-level chip scale package (WCSP)

- One of the worst EM resistance structures

- More prone to stress assisted EM failure —

- Easier to do microstructural EM mechanism study \_\_\_\_

#### Sample structure

- 5x5 SAC solder ball grid array (BGA)

- Consists of Cu UBM, SAC solder ball, and Cu lead-frame \_\_\_\_

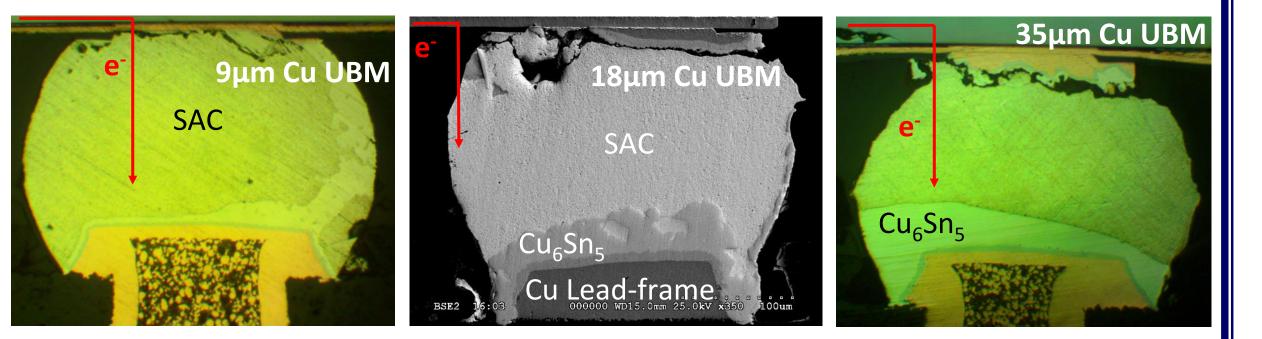

- Various thickness of Cu UBM pads (18-50µm Cu UBM) —

- 3 SAC solder bumps are connected for testing —

- Assembled into PCB

## Sample preparation

- WCSP samples provided by Texas Instruments for research

- PCB designed at UT Arlington

- WCSP assembled to PCB at SVT

Si

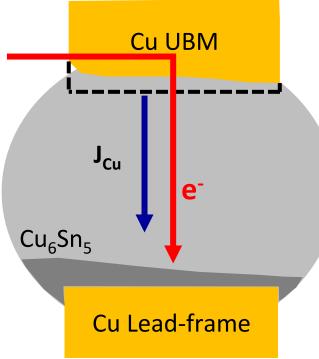

## **EM Failure Mechanism under DC**

- Cu EM controls the failure kinetics

- Cu EM occurs preferentially and protects Sn from EM, making UBM to dissolve and thick Cu<sub>6</sub>Sn<sub>5</sub> to accumulate at the anode

- Current crowding at the electron entering corner results in a faster dissolution of UBM

- Voiding starts at the corner and grows to the opposite end of UBM

- E and n of EM failure

- Activation energy (E) is related to the Cu diffusion

- n represents void nucleation and growth under current crowding (n>2)

- Contributing factors

- UBM thickness: affects amount of Cu supply and thermal stress effect

- Geometric constraint: affects current crowding and thermal stress

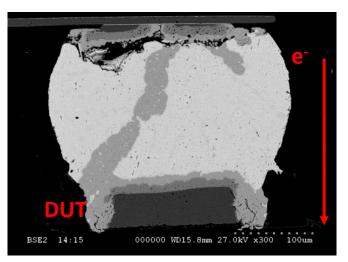

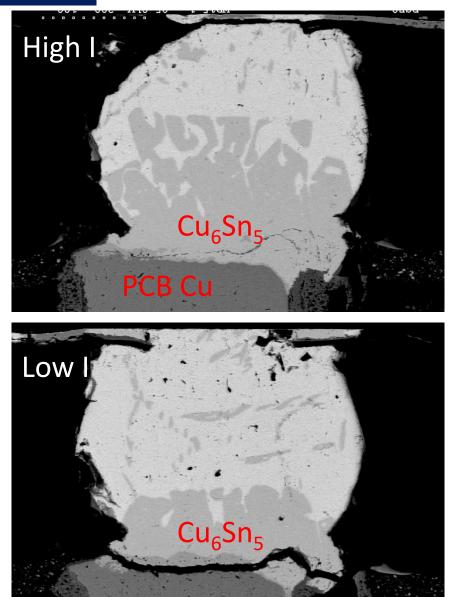

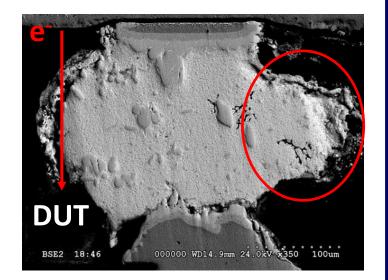

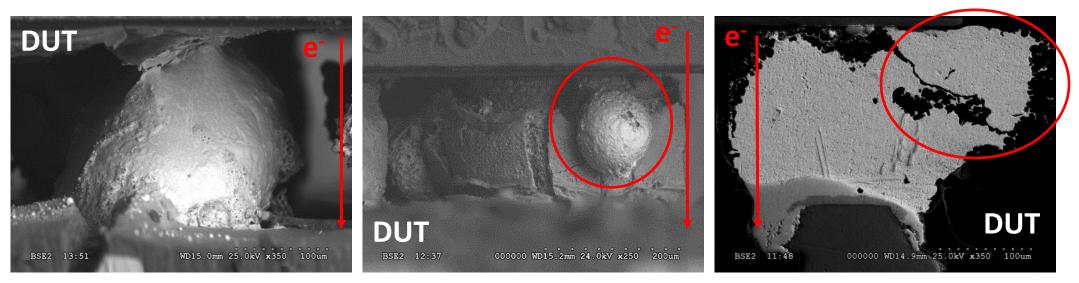

### **Microstructural Failure Mechanism**

#### Typical failure microstructure

- Failed by void nucleation and propagation at the cathode side of solder bump

- Thick Cu<sub>6</sub>Sn<sub>5</sub> IMC forms at the anode side while UBM is dissolved away

- Current crowding effect exists (void starts at the entrance of electron)

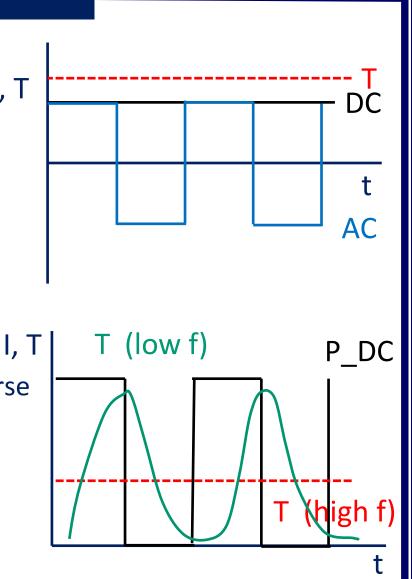

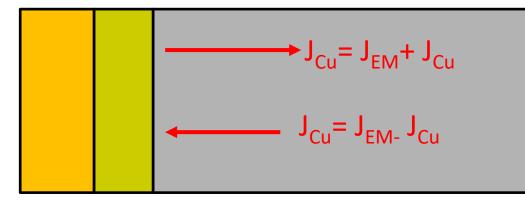

## **Factors to Consider for Non-DC EM Failure**

#### **EM failure under DC**

- Isothermal condition (with joule heat included)

- Kinetic mechanism is simpler and can be descried using the Black's model.

#### EM failure under AC

- If square AC, isothermal condition (the same JH to DC)

- Damage develops by asymmetry flux between "forward" and — "reverse" EM.

- Failure may develop faster at lower frequency when the reverse EM time is longer than the time to reverse the damage.

#### **EM failure under pulsed DC**

- Usually "on-time model": (no recovery is considered)

- Temperature is not constant at low frequency —

- Failure mechanism can be complicated with pulsing temperature

I, T

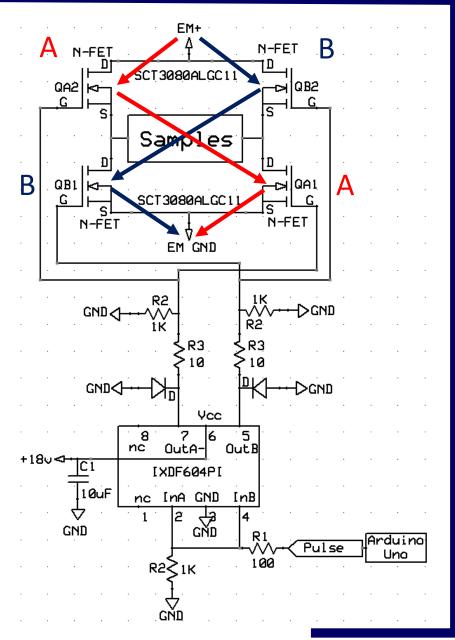

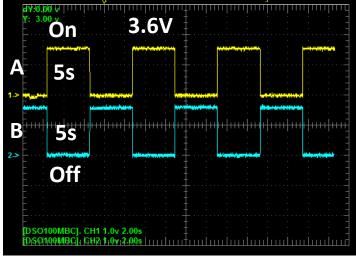

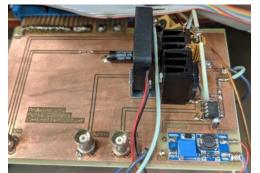

## **AC Constant Current Module Schematics**

- AC constant current power supply is not available

- Design an AC constant current generating PCB module (one of the most challenging tasks)

- Based on a H-bridge circuit consists of

- 4 MOSFETs, 1 MOSFET driver-2 outputs w/ opposite polarities

- 1 Arduino as a pulse-width modulation

- Turns on A MOSFETs to flow a forward AC polarity

Turns on B MOSFETs to flow a reverse AC polarity

#### **AC EM Test**

#### Possible failure behaviors

- No temperature fluctuation

- If EM damage is not repairable,

- AC EM failure rate is similar to DC (damaging in both forward and reverse direction)

- If EM damage is reparable,

Low frequency AC: longer failure time than DC (partial repair)

High frequency AC: not fail for very long time due to near complete damage repair mechanism

- Failure kinetics may be developed by extending the Black's model.

- But, " repairability" may not be only contributing factor

#### **0.1 Hz**

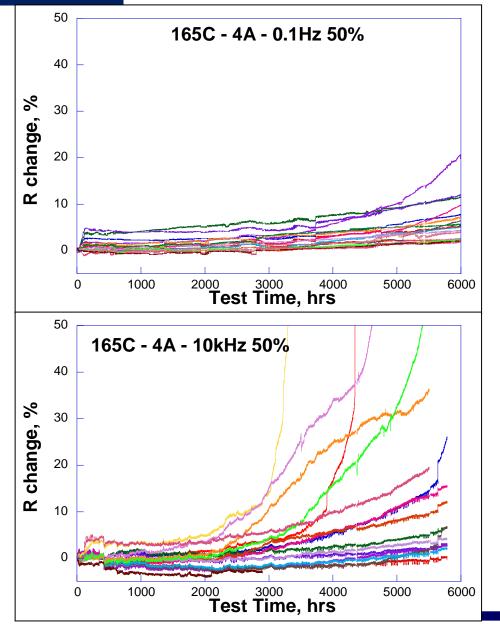

## **Failure Behavior under AC-EM Conditions**

- Results are opposite to the expected

- high frequency (10 kHz) fails faster than low frequency (0.1 Hz); true for both at DF=50 and 75%.

- Asymmetric AC (75% DF) fails faster than symmetric AC (50% DF).

- DC fails the fastest

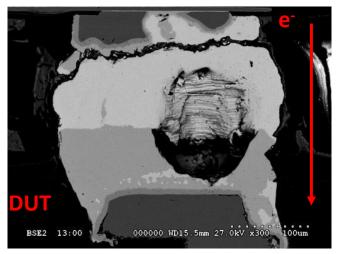

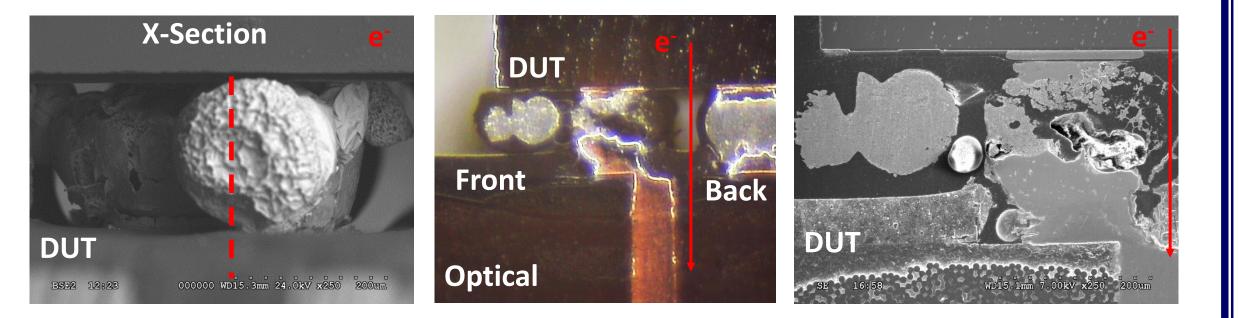

### **Microstructural Failure Mechanism under AC: 10KHz**

- Solder joint shows significant level of Cu injected into solder joint

- significant fraction of Sn-solder transformed into Cu<sub>6</sub>Sn<sub>5</sub>.

- faster failure at high frequency is resulted by excessive growth Cu-Sn IMCs.

- Cu EM at Cu/Sn interface is not reversible

- EM assists Cu dissolution but cannot reverse it.

- EM in IMC and Cu is negligible

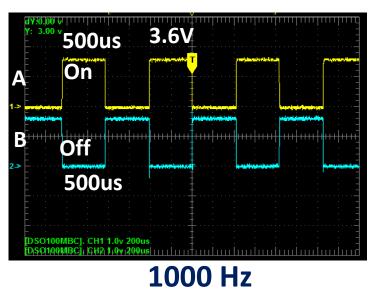

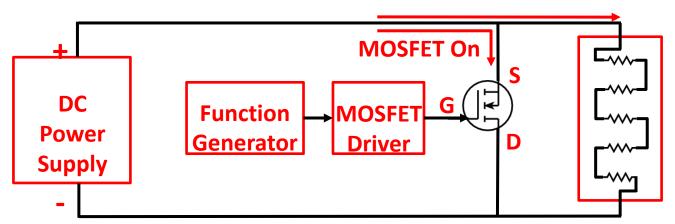

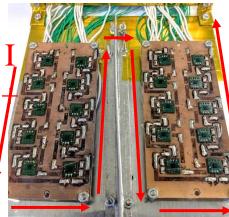

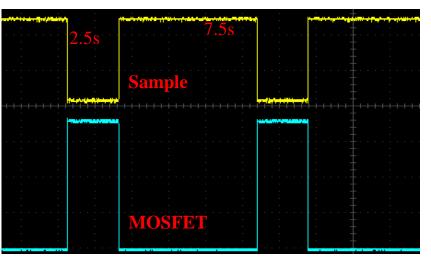

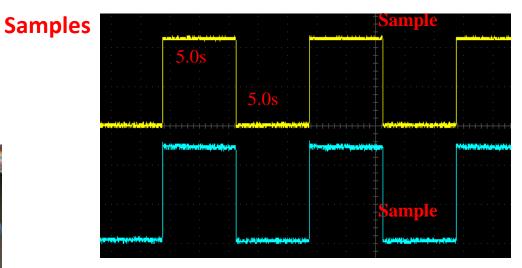

### **Pulsed DC EM Test: Circuit**

- "Crowbar" circuit

- Function generator controls MOSFET driver

- When MOSFET is closed, the test current bypasses samples

- When MOSFET is opened, the test current to samples

20 Samples on testing boards

Pulsed DC at 0.1Hz 75% DF

Pulsed DC at 0.1Hz 50% DF

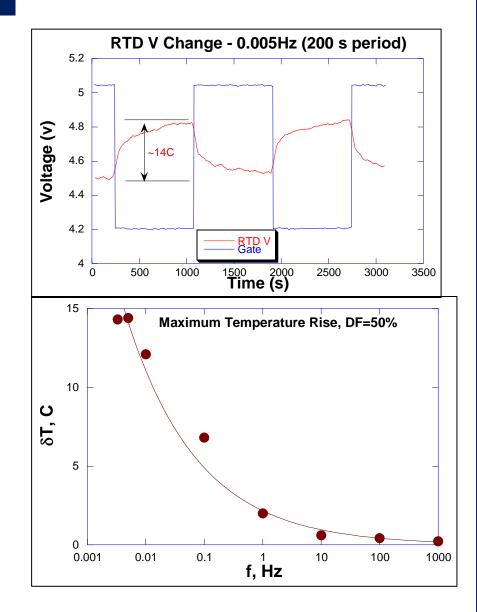

#### Hidden But Key Factor: Temperature

#### Measure at various PDC frequency using RTD

- Temperature change plateaus around 0.005 Hz (200s period) at 14 °C

- 7°C change at 0.1Hz

#### DUT Temperature dependence on frequency

- T is low and constant at high frequency (>100Hz)

- T pulsates along with pulsing current (<100Hz)</li>

#### Pulsating temperature will impact failure

- Thermal stress becomes a factor

- The failure may be assisted by the thermal fatigue

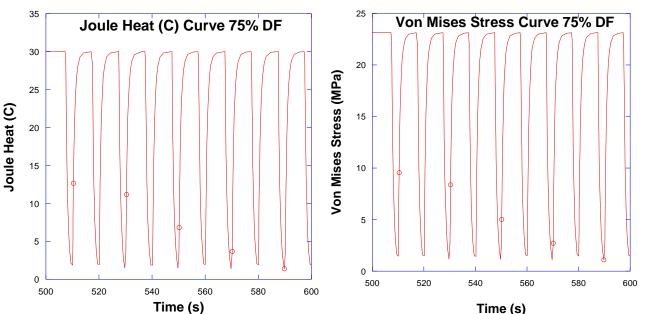

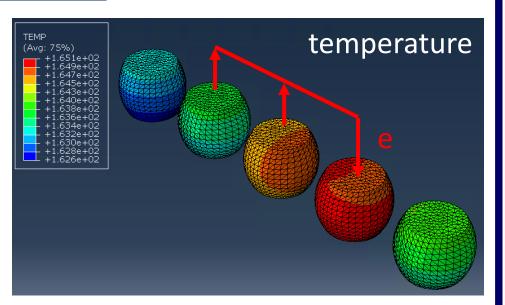

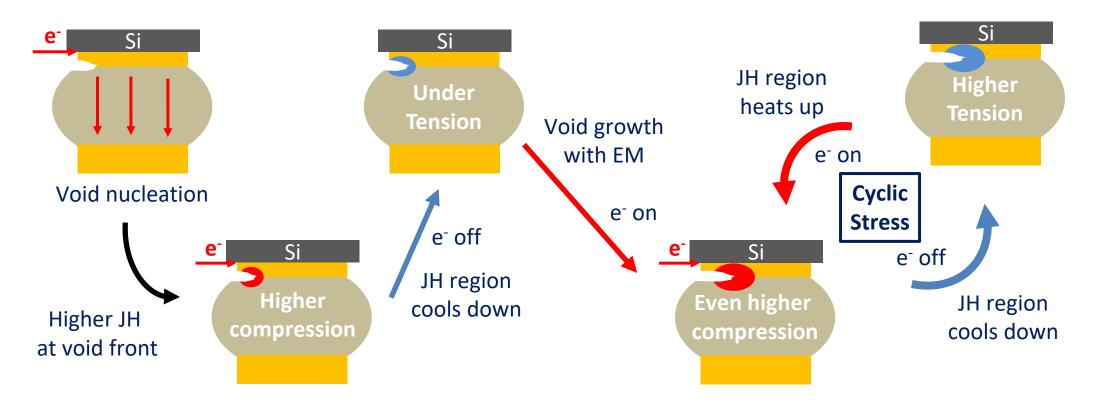

## **Source of Thermal Stress**

- Difference in Joule heat (JH) (resulting T difference) induces compressive stress on DUT and tension on surroundings

- DUT is subjected to higher local JH than the surroundings

- Higher local JH on DUT causes larger expansion than supporting bumps do, resulting in compression on DUT and tension on surroundings

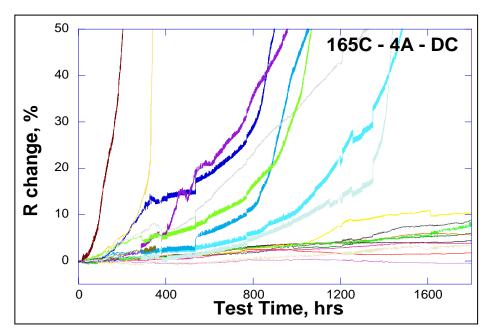

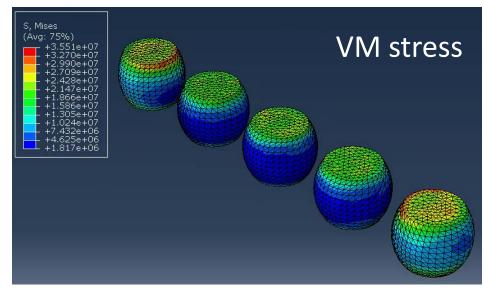

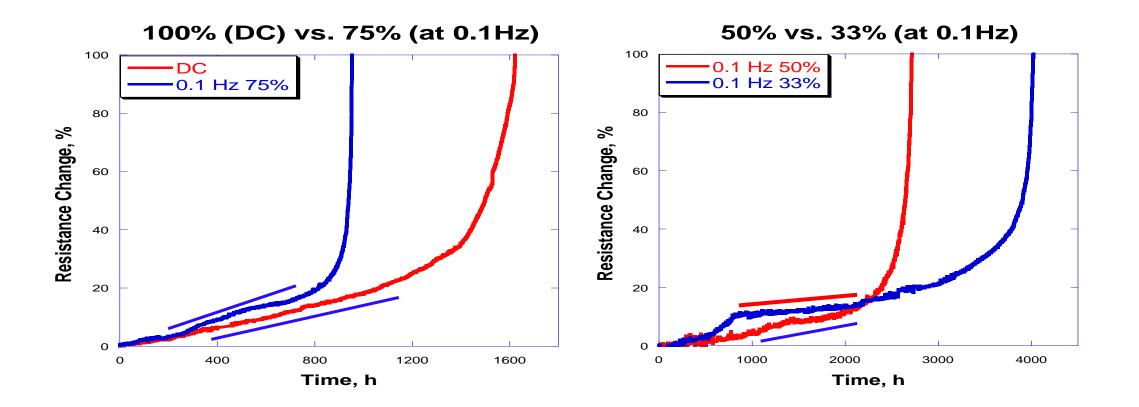

## **Failure Behavior at Pulsed EM Conditions**

#### At f>10kHz: different from the expected

- Failure rate is excessively slow (unable to induce failure even after 10k hours at 50% DF.

- 14C lower DUT temperature may provide partial explanation

- $T_{on}$  To<sub>ff</sub> may allow more active damage relaxation.

#### At f=0.1Hz: different from the expected

- 75% DF produces more damage than DC

- Reduction in DF makes failure rate to be exponentially delayed. (the reduction is again more than T effect)

#### Kinetics does not follow the Black's model

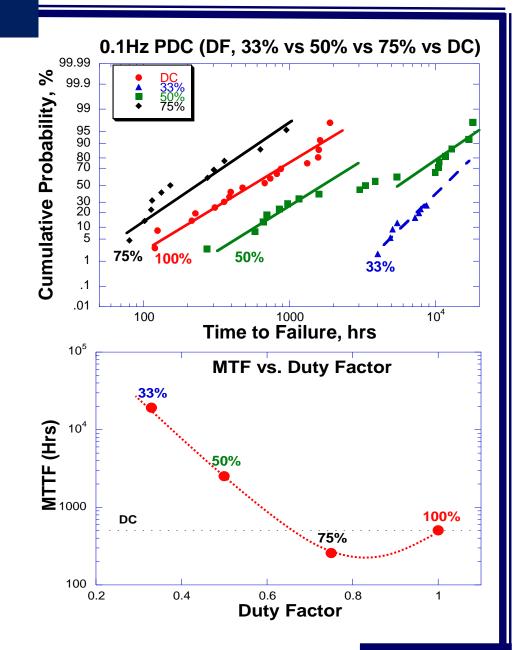

## **EM Failure Signal under Pulsed-DC Load**

#### Failure Signal

- Resistance change shows 2 stage EM failure development under pulsed DC

- The first stage induces more damages but the failure slows down at the second stage.

- The transition to second stage occurs faster at low DF.

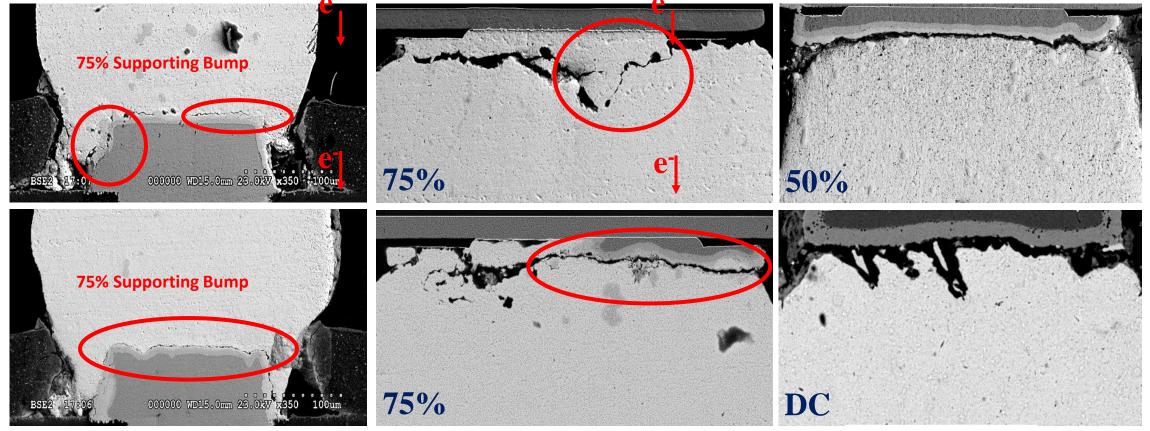

## **Cracking Assisted EM Failure under PDC**

- Narrow crack through Sn in 75% DF suggest involvement of mechanical fatigue

- Not conventional EM failure mechanism

- Evidence that the thermal fatigue affects the failure w/ pulsating temperature.

- Crack also exists at the supporting bumps

## Failure Acceleration by Thermal Fatigue

- Thermal Fatigue + EM under pulsed DC

- Most notable at DF=75%

- Conventional EM voiding combines with mechanical fatigue from thermal fluctuation

- When stress fluctuation exceeds the yield strength, plastic deformation occurs, activating fatigue

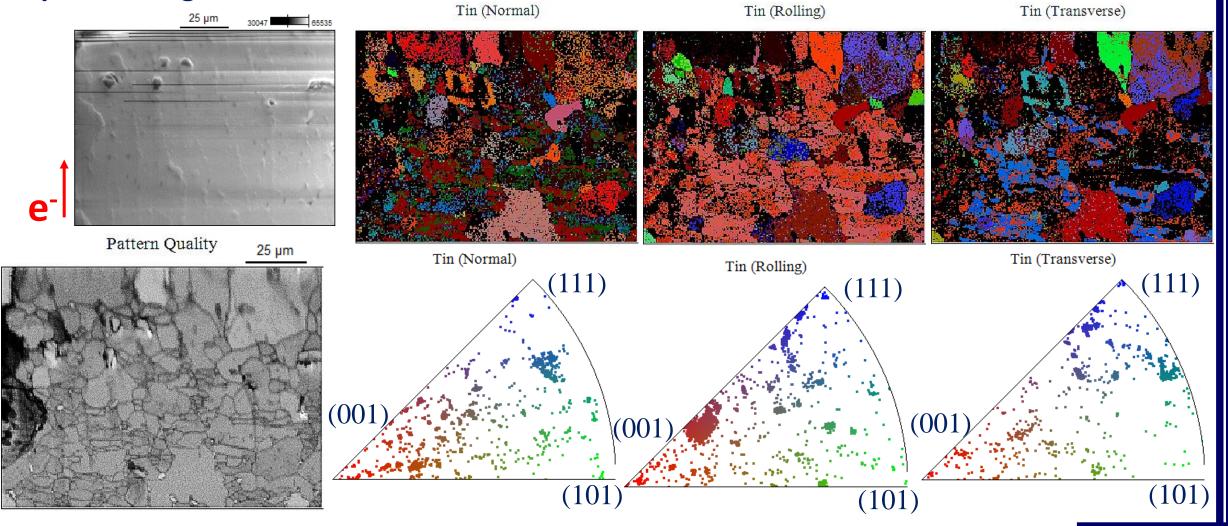

## **Failure Deceleration by Recrystallization**

Fine grain boundaries indicate a recrystallization of solder bump, removing fast EM path in Sn grain.

#### **Overall Failure Mechanism at Low Frequency**

- Two mechanisms in competition

- Failure acceleration: thermal fatigue (more intense at high DF)

- Failure suppression: recrystallization (more intense at low DF)

## New Failure Mechanism by Superplasticity

#### Superplasticity

- Extrusion of solder mass driven by uneven compressive stress

- Excessive extrusion becomes possible due to superplastic of solder

- Solder becomes superplastic by dynamic recrystallization effectively removing work hardening of solder

- Unusual to see this level of deformation because Sn is BCT

## **Ratcheting Failure by Extrusion of Solder**

- Sn gets extruded due to uneven stress

- Evidences the thermal stress and superplasticity of solder

- Danger of a short circuit

#### **Summary Experimental Observations**

- Generally understood EM failure mechanism in is not valid for pulsed DC

- Stress and its pulsation affects the failure rate and failure mechanisms

- Thermal fatigue can be included in the failure process at low frequency.

- Recrystallization is also possible at low frequency.

- Ratcheting failure is possible only with solder being superplastic

- High frequency testing may bring new surprises (testing is in progress).

#### Irreversible reaction of Cu at Cu/solder interface dictates the failure rate

- Unlike expectation, EM failure does occur and can be serious reliability issue.

- Damage starts as a format of extensive growth of IMC growth.

- Damage repair is not as effective as is seen in thin film interconnects.

- Needs more studies for better understanding.

## Acknowledgements

- Thank you very much the invitation and attention to the presentation

- Graduate students

- UTA (since 2016): H. Xu (Apple), L. S. Chen (Samsung), P. Liu (Globalfoundaries), V. Ouvarov Bancalero (Intel), H. Madanipour (intel), A. Osmanson (TI), M. Tajedini, Y.R. Kim, G. Ni, J. Bo

#### Collaborators

- Many..., but special thanks to Drs. S. H. Chae (Hynix), L. Nguyen (PsiQuantum), T. K. Lee (CISCO), Y. J. Park (TI), Q. Chen (TI), P. Thompson;

- Funding and Support

- SRC: funding

- Texas Instruments: funding and samples