Available online at www.sciencedirect.com

MICROELECTRONICS RELIABILITY

Microelectronics Reliability 46 (2006) 1957–1979

www.elsevier.com/locate/microrel

Introductory Invited Paper

# Electronic circuit reliability modeling

## Joseph B. Bernstein \*, Moshe Gurfinkel, Xiaojun Li, Jörg Walters, Yoram Shapira, Michael Talmor

Reliability Engineering Center, Mechanical Engineering Department, University of Maryland at College Park, MD 20742, USA

Received 6 December 2005; received in revised form 12 December 2005 Available online 8 February 2006

## Abstract

The intrinsic failure mechanisms and reliability models of state-of-the-art MOSFETs are reviewed. The simulation tools and failure equivalent circuits are described. The review includes historical background as well as a new approach for accurately predicting circuit reliability and failure rate from the system point of view.

© 2006 Elsevier Ltd. All rights reserved.

## 1. Introduction

Microelectronics integration density is limited by the reliability of the manufactured product at a desired circuit density. Design rules, operating voltage and maximum switching speeds are chosen to insure functional operation over the intended lifetime of the product. Thus, in order to determine the ultimate performance for a given set of design constraints, the reliability must be modeled for its specific operating condition.

Reliability modeling for the purpose of lifetime prediction is therefore the ultimate task of a failure physics evaluation. Unfortunately, all the industrial approaches to reliability evaluation fall short of predicting failure rates or wearout lifetime of semiconductor products. This is attributed mainly to two reasons: the lack of a unified approach for predicting device failure rates and the fact that all commercial reliability evaluation methods rely on the acceleration of a single, dominant failure mechanism.

Over the last several decades, our knowledge about the root cause and physical behavior of the critical failure mechanisms in microelectronic devices has grown significantly. Confidence in the reliability models have led to more aggressive design rules that have been successfully

\* Corresponding author. *E-mail address:* joey@umd.edu (J.B. Bernstein). applied to the latest VLSI technology. One result of improved reliability modeling has been accelerated performance, beyond the expectation of Moore's Law. A consequence of more aggressive design rules has been a reduction in the weight of a single failure mechanism. Hence in modern devices, there is no single failure mode that is more likely to occur than any other as guaranteed by the integration of modern failure physics modeling and advanced simulation tools in the design process.

The consequence of more advanced reliability modeling tools is a new phenomenon of device failures resulting from a combination of several competing failure mechanism. Hence, a new approach is required for reliability modeling and prediction. This paper reviews the existing modeling and prediction methods and presents an approach for accurate system reliability modeling in the competing mechanisms era. In addition, a new simulation tool that based on this new approach is presented.

## 1.1. Reliability prediction from historical perspective

In order to understand the current trends in reliability modeling and prediction, we have to look at it from historical point of view. Reliability modeling and prediction is a relatively new discipline. Only since World War II has reliability become a subject of study. This came about because of the relatively complex electronic equipment

<sup>0026-2714/\$ -</sup> see front matter @ 2006 Elsevier Ltd. All rights reserved. doi:10.1016/j.microrel.2005.12.004

used during the war and the rather high failure rates observed.

Since then, we can indicate two different approaches for reliability modeling corresponding to different time periods. Until the 1980s, the exponential, or the constant failure rate (CFR) model [1] had been the only model used for describing the useful life of electronic components. It was common to six reliability prediction procedures, which were reviewed by Bowles [2] and was the foundation of the military handbook for reliability prediction of electronic equipments, known as MIL-HDBK-217 [3] series. It became the de facto industry standard for reliability prediction. Although the CFR model was used without physical justification, it is not difficult to reconstruct the rationale for the use of the CFR model which mathematically describes the failure distribution of systems in which the failures are due to completely random or chance events. Indeed, throughout that period, electronic equipment complexity has begun to increase significantly. Similarly, the earlier devices were fragile and had several intrinsic failure mechanisms, which combined together to result in a constant failure rate.

During the 1980s and early 1990s, with the introduction of integrated circuits (ICs), more and more evidence was gathered suggesting that the CFR model was no longer applicable. Phenomena, such as infant mortality and device wearout dominated the field failures and they could not be described using the CFR model. In 1991, two research groups, IIT Research Institute/Honeywell SSED and the Westinghouse/University of Maryland teams both suggested that the CFR model should not be used [4], based on their research to provide guidelines to update the MIL-HDBK-217. They suggested that the exponential distribution was unacceptable and should not be blindly applied to every type of component and system.

The end of the CFR as a sole model for reliability modeling was officially set with the publication of the "Perry Memo" [5]. Responding to increasing criticism of CFR, in 1994, Secretary of Defense William Perry issued a memorandum that effectively eliminated the use of most defense standards, including the MIL-HDBK-217 series. Many defense standards were cancelled at that time and, in their place, the DOD encouraged the use of industry standards, such as ISO 9000 series for quality assurance.

Since then, the Physics-of-Failure approach has dominated reliability modeling. In this approach, the root cause of individual failure mechanism is studied and corrected to achieve some determined lifetime. Since wearout mechanisms became better understood, the goal of reliability engineers has been to design dominant mechanisms for the useful life of the components by applying strict rules for every design feature. The theoretical result of this approach, of course, is that the expected wearout failures have become unlikely to occur during the normal service life of microelectronic devices. Nonetheless, failures do occur in the field and reliability prediction had to accommodate this new theoretical approach to the virtual elimination of any one failure mechanisms limiting the useful life of an electronic device.

## 1.2. Reliability modeling and prediction today

Reliability device simulators have become an integral part of the design process. These simulators successfully model the most significant physical failure mechanisms in modern electronic devices, such as time dependent dielectric breakdown (TDDB), negative bias temperature instability (NBTI), electromigration (EM) and hot carrier injection (HCI). These mechanisms are modeled throughout the circuit design process so that the system will operate for a minimum expected useful life.

Modern chips are composed of tens or hundreds of millions of transistors. Hence, chip level reliability prediction methods are mostly statistical. Today, chip level reliability prediction tools, model the failure probability of the chips at the end-of-life, when the known wearout mechanisms are expected to dominate. However, modern prediction tools do not predict the random, post-burn-in, failure rate that would be seen in the field.

Chip and packaged system reliability is still measured by a Failure unIT (FIT). The FIT is a rate, defined as the number of expected device failures per billion part hours. A FIT is assigned for each component multiplied by the number of devices in a system for an approximation of the expected system reliability. The semiconductor industry provides an expected FIT for every product that is sold based on operation within the specified conditions of voltage, frequency, heat dissipation, etc. Hence, a system reliability model is a prediction of the expected mean time between failures (MTBF) for an entire system as the sum of the FIT rates for every component.

A FIT is defined in terms of an acceleration factor,  $A_{\rm F}$ , as

$$FIT = \frac{\# failures}{\# tested * hours * A_F} \times 10^9,$$

(1)

where #failures and #tested are the number of actual failures that occurred as a fraction of the total number of units subjected to an accelerated test. The acceleration factor,  $A_{\rm F}$ , must be supplied by the manufacturers since only they know the failure mechanisms that are being accelerated in the high temperature operating life (HTOL) and it is generally based on a company proprietary variant of the MIL-HDBK-217 approach for accelerated life testing. The true task of reliability modeling, therefore, is to choose an appropriate value for  $A_{\rm F}$  based on the physics of the dominant device failure mechanisms that would occur in the field.

The HTOL qualification test is usually performed as the final qualification step of a semiconductor manufacturing process. The test consists of stressing some number of parts, usually about 100, for an extended time, usually 1000 h, at an accelerated voltage and temperature. Two features shed doubt on the accuracy of this procedure.

One feature is the lack of sufficient statistical data and the second is that companies generally present zero failures results of their qualification tests and hence stress their parts under relatively low stress levels to guarantee zero failures during qualification testing.

Unfortunately, with zero failures, no statistical data are acquired. Another feature is their calculation of the acceleration factor  $A_{\rm F}$ . If the qualification test results in zero failures, which allows the assumption (with only 60% confidence!) that no more than 1/2 a failure occurred during the accelerated test. This would result, based on the example parameters, in a reported FIT = 5000/AF, which can be almost any value from less than 1 FIT to more than 500 FIT, depending on the conditions and model used for the voltage and temperature acceleration.

The accepted approach for measuring FIT would, in theory, be reasonably correct if there was only a single dominant failure mechanism that was excited equally by either voltage or temperature. For example, electromigration is known to follow Black's equation (described later) and is accelerated by increased current stress in a conductor or by increasing the device temperature. If, however, multiple failure mechanisms are responsible for device failures, each failure mechanism should be modeled as an individual "element" in the system and the component survival is modeled as the survival probability of all the "elements" as a function of time.

If multiple failure mechanisms, instead of a single mechanism, are assumed to be time-independent and independent of each other, FIT (constant failure rate approximation) should be a reasonable approximation for realistic field failures. Under the assumption of multiple failure mechanisms, each will be accelerated differently depending on the physics that is responsible for each mechanism. If, however, an HTOL test is performed at an arbitrary voltage and temperature for acceleration based only on a single failure mechanism, then only that mechanism will be accelerated. In that instance, which is generally true for most devices, the reported FIT (especially one based on zero failures) will be meaningless with respect to other failure mechanisms.

## 1.3. Competing mechanism theory

#### 1.3.1. Multiple failure mechanism model

Whereas the failure rate qualification has not improved over the years, the semiconductor industry understanding of reliability physics of semiconductor devices has advanced enormously. Every known failure mechanism is so well understood and the processes are so tightly controlled that electronic components are designed to perform with reasonable life and with *no single dominant failure mechanism*. Standard HTOL tests generally reveal multiple failure mechanisms during testing, which suggests also that no single failure mechanism dominates the FIT rate in the field. Therefore, in order to make a more accurate model for FIT, a preferable approximation is that all failures are *equally likely* and the resulting overall failure distribution resembles *constant failure rate process* that is consistent with the mil-handbook, FIT rate approach.

The acceleration of a single failure mechanism is a highly non-linear function of temperature and/or voltage. The temperature acceleration factor  $(AF_{\rm T})$  and voltage acceleration factor  $(AF_{\rm V})$  can be calculated separately and are the subject of most studies of reliability physics. The total acceleration factor of the different stress combinations are the product of the acceleration factors of temperature and voltage:

$$AF = \frac{\lambda(T_2, V_2)}{\lambda(T_1, V_1)} = AF_{\rm T} \cdot AF_{\rm V}$$

=  $\exp\left(\frac{E_{\rm a}}{k}\left(\frac{1}{T_1} - \frac{1}{T_2}\right)\right) \exp(\gamma_1(V_2 - V_1)).$  (2)

This acceleration factor model is widely used as the industry standard for device qualification. However, it only approximates a single dielectric breakdown type of failure mechanism and does not correctly predict the acceleration of other mechanisms.

To be even approximately accurate, electronic devices should be considered to have several failure modes degrading simultaneously. Each mechanism 'competes' with the others to cause an eventual failure. When more than one mechanism exists in a system, then the relative acceleration of each one must be defined and averaged under the applied condition. Every potential failure mechanism should be identified and its unique AF should then be calculated for each mechanism at given temperature and voltage so the FIT rate can be approximated for each mechanism separately. Then, the final FIT is the sum of the failure rates per mechanism, as described by

$$FIT_{total} = FIT_1 + FIT_2 + \dots + FIT_i, \tag{3}$$

where each mechanism leads to an expected failure unit per mechanism,  $FIT_i$ . Unfortunately, individual failure mechanisms are not uniformly accelerated by a standard HTOL test, and the manufacturer is forced to model a single acceleration factor that cannot be combined with the known physics of failure models.

### 1.3.2. Acceleration factor

The qualification of device reliability, as reported by a FIT rate, must be based on an acceleration factor, which represents the failure model for the tested device. If we assume that there is no failure analysis (FA) of the devices after the HTOL test, or that the manufacturer does not report FA results to the customer, then a model should be made for the acceleration factor, AF, based on a combination of competing mechanisms. This will be explained by way of example. Suppose there are two identifiable, constant rate competing failure modes (assume an exponential distribution). One failure mode is accelerated only by temperature. We denote its failure rate as  $\lambda_1(T)$ . The other failure mode is only accelerated by voltage, and the corresponding failure rate is denoted as  $\lambda_2(V)$ . By perform-

ing the acceleration tests for temperature and voltage separately, we can get the failure rates of both failure modes at their corresponding stress conditions. Then we can calculate the acceleration factor of the mechanisms. If for the first failure mode we have  $\lambda_1(T_1)$ ,  $\lambda_1(T_2)$ , and for the second failure mode, we have  $\lambda_2(V_1)$ ,  $\lambda_2(V_2)$ , then the temperature acceleration factor is

$$AF_{\rm T} = \frac{\lambda_1(T_2)}{\lambda_1(T_1)}, \quad T_1 < T_2$$

(4)

and the voltage acceleration factor is

$$AF_{\rm V} = \frac{\lambda_2(V_2)}{\lambda_2(V_1)}, \quad V_1 < V_2.$$

(5)

The system acceleration factor between the stress conditions of  $(T_1, V_1)$  and  $(T_2, V_2)$  is

$$AF = \frac{\lambda_1(T_2, V_2) + \lambda_2(T_2, V_2)}{\lambda_1(T_1, V_1) + \lambda_2(T_1, V_1)} = \frac{\lambda_1(T_2) + \lambda_2(V_2)}{\lambda_1(T_1) + \lambda_2(V_1)}.$$

(6)

The above equation can be transformed to the following two expressions:

$$AF = \frac{\lambda_{1}(T_{2}) + \lambda_{2}(V_{2})}{\frac{\lambda_{1}(T_{2})}{AF_{T}} + \frac{\lambda_{2}(V_{2})}{AF_{V}}}$$

(7)

or

$$AF = \frac{\lambda_1(T_1)AF_{\rm T} + \lambda_2(V_1)AF_{\rm V}}{\lambda_1(T_1) + \lambda_2(V_1)}.$$

(8)

These two equations can be simplified based on different assumptions.

When  $\lambda_1(T_1) = \lambda_2(V_1)$  (i.e. equal probability under normal operating conditions):

$$AF = \frac{AF_{\rm T} + AF_{\rm V}}{2}.\tag{9}$$

Therefore, unless the temperature and voltage is carefully chosen so that  $AF_{\rm T}$  and  $AF_{\rm V}$  are very close, within a factor of about 2, then one acceleration factor will overwhelm the failures at the accelerated conditions. Similarly, when  $\lambda_1(T_2) = \lambda_2(V_2)$  (i.e. equal probability during accelerated test condition) then AF will take this form:

$$AF = \frac{2}{\frac{1}{AF_{\rm T}} + \frac{1}{AF_{\rm V}}}\tag{10}$$

and the acceleration factor applied to normal operating conditions will be dominated by the individual factor with the greatest acceleration. In either situation, the accelerated test does not accurately reflect the correct proportion of acceleration factors based on the understood physics of failure mechanisms.

This discussion can be generalized to incorporate situations with more than two failure modes. Suppose a device has *n* independent failure mechanisms, and  $\lambda_{\text{LT}_{\text{FM}i}}$  represents the *i*th failure mode at accelerated condition,  $\lambda_{\text{use}_{\text{FM}i}}$ represents the *i*th failure mode at normal condition, then  $A_{\text{F}}$  can be expressed. If the device is designed, such that the failure modes have equal frequency of occurrence during normal operating *conditions*:

$$AF = \frac{\lambda_{\text{use}_{\text{FM1}}} \cdot AF_1 + \lambda_{\text{use}_{\text{FM2}}} \cdot AF_2 + \dots + \lambda_{\text{use}_{\text{FMn}}} \cdot AF_n}{\lambda_{\text{use}_{\text{FM1}}} + \lambda_{\text{use}_{\text{FM2}}} + \dots + \lambda_{\text{use}_{\text{FMn}}}}$$

$$= \frac{\sum_{i=1}^n AF_i}{n}.$$

(11)

If the device is designed, such that the failure modes have equal frequency of occurrence during the *test conditions*:

$$AF = \frac{\lambda_{\text{LT}_{\text{FM1}}} + \lambda_{\text{LT}_{\text{FM2}}} + \dots + \lambda_{\text{LT}_{\text{FMn}}}}{\lambda_{\text{LT}_{\text{FM1}}} \cdot AF_1^{-1} + \lambda_{\text{LT}_{\text{FM2}}} \cdot AF_2^{-1} + \dots + \lambda_{\text{LT}_{\text{FMn}}} \cdot AF_n^{-1}}$$

$$= \frac{n}{\sum_{i=1}^n \frac{1}{AF_i}}.$$

(12)

From these relations, it is clear that only if the acceleration factors for each mode are almost equal, i.e.,  $AF_1 \approx AF_2$ , the total acceleration factor will be  $AF = AF_1 = AF_2$ , and certainly not the product of the two (as is currently the model used by industry). If, however, the acceleration of one failure mode is much greater than the second, the standard FIT calculation (Eq. (2)) could be incorrect by many orders of magnitude.

Due to the exponential nature of the acceleration factor as a function of V or T, if only a single parameter is changed, then it is not likely for more than one mechanism to be accelerated significantly compared to the others for any given V and T. In the next section, at least four mechanisms should be considered. Also, the various voltage and temperature dependencies must be considered in order to make a reasonable reliability model for electron devices. The assumption of equal failure probability under normal operating conditions is the most conservative and probably the most accurate. In fact, the exact proportions will not alter the result significantly since the proportional factor is only linearly related to the final acceleration factor, as compared to the exponential and power-law factors of the related physics models.

#### 2. MOS failure mechanisms models

The major wearout mechanisms of semiconductor-based micro-electronic devices are electromigration (EM), gate oxide breakdown also known as time dependent dielectric breakdown (TDDB), hot carrier injection (HCI) and negative bias temperature instability (NBTI). These mechanisms are briefly reviewed below.

#### 2.1. Electromigration

Electrons passing through a conductor transfer some of their momentum to its atoms. At sufficiently high electron current densities (greater than  $10^5 \text{ A/cm}^2$  [6]), atoms may shift towards the anode side. The material depletion at the cathode side causes circuit damage due to decreased

electrical conductance and eventual formation of open circuit conditions. This is caused by voids and micro-cracks, which may increase the conductor resistance as the crosssectional area is reduced. Increased resistance alone may result in device failure, yet, the resulting increase in local current density and temperature may lead to thermal runaway and catastrophic failure [7], such as an open circuit failure. Alternatively, short circuit conditions may develop due to excess material buildup at the anode. Hillocks form where there is excess material, breaking the oxide layer, allowing the conductor to come in contact with other device features. Other types of damage include whiskers, thinning, localized heating, and cracking of the passivation and inter-level dielectrics [8].

This diffusive process, known as electromigration, is still a major reliability concern despite vast scientific research as well as electrical and materials engineering efforts. Electromigration can occur in any metal when high current densities are present. In particular, the areas of greatest concern are the thin-film metallic interconnects between device features, contacts and vias [8].

## 2.1.1. EM physics

At high current densities, the force exerted by electrons scattering off the positively charged metal ions becomes stronger than the electrostatic pull force toward the cathode. Thus, the diffusion of the ions is biased in the direction of the electron flow, leading to electromigration. Its effects are expected to be characteristic of the material, such that the activation energy for electromigration is dependent on the material type, the size and orientation of the grains, stress, temperature and even the length of the conductor. Even low concentration doping may have great impact on the EM features. As an example, the EM activation energy of bulk Al is 1.4 eV, while adding small amounts (0.3-5%) of Cu reduces this activation energy by about 0.5-0.8 eV [8].

Grain size and pattern also have substantial impact on the effective EM activation energy of the metal. For instance, the activation energy ranges between 1 and 2 eV for thin films with large grain sizes. For very fine grained samples, the activation energy may be as low as 0.4– 0.6 eV. Thus, mass transport-induced damage is more severe at grain boundaries and is greatest where three or more grains meet. When small dimension conductors are used, columnar growth of the metal lowers the grain boundary density and increases the electromigration lifetime.

Stress gradients also affect electromigration since they can induce atomic motion within the metal. Atoms migrate from regions of compressive stress to regions of tensile stress. When a conductor is shorter than a critical length,  $L_c$ , known as the 'Blech Length', the stress-induced flow of atoms counters the EM driving force and EM is eliminated [9].

Temperature gradients, caused by high current Joule heating also affect electromigration. While these gradients

may only span a temperature change of some tens of degrees, the temperature change over a few microns results in large gradients [9]. Since EM is a thermally activated process, the temperature gradients produce flux divergences such as those found at contacts or other device features.

Increasingly, low resistivity Cu interconnects have been made use in ICs since Cu has a lower atomic diffusivity than Al. However, the surface self-diffusion in copper appears to be faster than grain-boundary self-diffusion. Thus, Cu does not provide the desired solution and the reliability of Cu interconnects may be improved by suppressing the interface and surface diffusion [10].

## 2.1.2. Lifetime prediction

Modeling electromigration median time to failure (MTTF) from the first principles of the failure mechanism is difficult. While there are many competing models attempting to predict time-to-failure from first principles, there is no universally accepted model.

Currently, the favored method to predict time to failure is an approximate statistical one given by the *Black's* equation, which describes the MTTF by

$$MTTF = A(j_e)^{-n} \exp(E_a/kT), \qquad (13)$$

where  $j_e$  is the current density and  $E_a$  is the EM activation energy. Failure times are described by the lognormal distribution [11]. The symbol A is a constant, which depends on a number of factors, including grain size, line structure and geometry, test conditions, current density, thermal history, etc. Black determined the value of n to equal 2. However, nis highly dependent on residual stress and current density [8] and its value is highly controversial.

A range of values for the EM activation energy,  $E_a$ , of aluminum (Al) and aluminum alloys is also reported. The typical value is  $E_a = 0.6 \pm 0.1$  eV. The activation energy can vary due to mechanical stresses caused by thermal expansion. Introduction of 0.5% Cu in Al interconnects may result in n = 2.63 and an activation energy of  $E_a = 0.95$  eV. For multi-level Damascene Cu interconnects, an activation energy of  $E_a = 0.94 \pm 0.11$  eV at a 95% confidence interval (CI) and a value of the current density exponent of  $n = 2.03 \pm 0.21$  (95% CI) were found [12].

#### 2.1.3. Lifetime distribution model

Traditionally, the EM lifetime has been modeled by the lognormal distribution. Most test data appear to fit the lognormal distribution, but these data are typically for the failure time of a single conductor [13]. Through the testing of over 75,000 Al(Cu) connectors, Gall et al. [13] showed that the electromigration failure mechanism did follow the lognormal distribution. This is valid for the TTF of the first link with the assumption that the first link failure will result in device failure. The limitation is that a lognormal distribution is not scalable. A device with different numbers of links fails with a different lognormal distribu-

tion. Thus, a measured failure distribution is valid only for the device on which it is measured. Gall et al. also showed that the Weibull (and thus the exponential) distribution is not a valid model for electromigration.

Even though the lognormal distribution is the best fit for predicting the failure of an individual device due to EM, the exponential model is still applicable for modeling EM failure in a system of many devices where the reliability is determined by the first failure of the system.

#### 2.1.4. Lifetime sensitivity

The sensitivity of the electromigration lifetime can be observed by plotting the lifetime as a function of the input parameters. For EM, the most significant input parameters corresponding to lifetime are the temperature (T) and current density  $(j_e)$ . The lifetime may be normalized using an acceleration factor.

Substituting *Black's* equation and assuming an exponential failure distribution into

$$A_{\rm f} = \lambda_{\rm rated} / \lambda \tag{14}$$

provides the acceleration factor for EM

$$A_{\rm f,EM} = (j_{\rm e}/j_{\rm e,rated})^{-n} \exp[(E_{\rm a,EM}/kT)(1/T - 1/T_{\rm rated})].$$

(15)

Obviously, T has a much greater impact on  $A_{\rm f}$  than  $j_{\rm e}$ .

As device features continue to shrink and interconnect current densities grow, EM will remain a concern. New technologies may reduce the EM impact of increasing densities but new performance requirements emerge that require increased interconnect reliability under conditions of decreased metallization inherent reliability [9]. Thus, EM will remain a design and wearout issue in future semiconductor designs.

## 2.2. Time dependent dielectric breakdown

Time dependent dielectric breakdown (TDDB), also known as oxide breakdown, is a source of significant reliability concern. When a sufficiently high electric field is applied across the dielectric gate of a transistor, continued degradation of the material results in the formation of conductive paths, which may short the anode and cathode [14]. This process will be accelerated as the thickness of the gate oxide decreases with continued device down-scaling.

The TDDB process takes place in two stages [15]. In the first stage, the oxide is damaged by the localized hole and bulk electron trapping within it and at its interfaces. The second stage is reached when the increasing density of traps within the oxide form a percolation (conduction) path through the oxide. This short circuit between the substrate and gate electrode results in oxide failure. This process has been successfully modeled using Monte Carlo simulations.

The formation of a percolation path may result in one of two types of failure. Once a conduction path forms, current flows through the path causing a sudden energy burst, which may cause runaway thermal heating. The result may be a *soft breakdown* if the device continues to function. Local melting of the oxide will destroy the gate and is thus denoted as *hard breakdown*. It has been speculated that soft breakdown does not even significantly affect transistor operation, although it may still lead to the failure of short channel devices. While the change in both threshold voltage and leakage from soft breakdown is small and initially does not affect device operation, the effects are cumulative. Multiple soft breakdowns may result in an increase in leakage current to unacceptable levels [16].

#### 2.2.1. TDDB physics

Trap generation is the key factor determining oxide degradation and breakdown. Three general models are discussed in the literature for trap generation. These models are the "anode hole injection" (AHI) model, the "thermo-chemical" model, and the "anode hydrogen release" (AHR) model.

The AHI model  $(1/E \mod e)$  was proposed by Schuegraf and Hu [17] and studied by many researchers. In this model, electrons injected from the gate metal cathode into the oxide undergo impact ionization events, which generate holes in the process. Some of these holes tunnel back into the cathode and create electron traps in the oxide. The physics of the trap creation process is still speculative.

The thermo-chemical model (E model) is another widely cited dielectric breakdown model. McPherson and Mogul [18] reviewed the development of this model and proposed a physical explanation. This model proposes that defect generation is a field-driven process and the current flowing through the oxide plays a secondary role at most. The interaction of the applied electric field with the dipole moments associated with oxygen vacancies leads to a conduction sub-band formation and to severe Joule heating at the stage of oxide breakdown.

In the AHR model, the energy release of the incoming electrons at the anode may activate hydrogen release at the anode, besides creating holes. The released hydrogen diffuses through the oxide and can generate electron traps. There have been contradicting opinions on the exact field acceleration law of time-to-breakdown –  $t_{\rm BD}$ . According to the AHI model (1/*E* model) the field dependence of the  $t_{\rm BD}$  takes the form:

$$t_{\rm BD}(t) = \tau_0 \exp\left(\frac{G}{E_{\rm OX}}\right),$$

(16)

where  $E_{OX}$  is the electric field across the dielectric and  $\tau_0$  and G are constants.

According to the thermo-chemical model (E model) the field dependence of the  $t_{BD}$  is of the form:

$$t_{\rm BD}(t) = t_0 \exp(-\gamma E_{\rm OX}),\tag{17}$$

where  $t_0$  and  $\gamma$  are constants.

There is still no consensus on the correct acceleration law and the discussion of the E and 1/E models continues.

The debate about E vs. 1/E models is most applicable for thick oxides. For ultra-thin oxides evidence shows that gate voltage is the primary driver of the breakdown process [19]. Additionally, there is evidence that the temperature dependence of ultra-thin oxides is non-Arrhenius, but rather the temperature acceleration factor is larger at higher temperatures. To account for these observations, Wu et al. [19] have proposed a relationship in the form of

$$MTTF = T_{BD0}(V) \exp(a(V)/T + b(V)/T^2),$$

(18)

where  $T_{BD0}(V)$ , *a* and *b* are voltage dependent factors. The second order term,  $b/T^2$ , is included in order to account for any non-Arrhenius temperature effects.

#### 2.2.2. Lifetime distribution model

The time-to-breakdown  $(t_{BD})$  is a statistically distributed parameter. At high fields, a very wide distribution of breakdown times is found. It is commonly assumed to be distributed according to the Weibull statistics, which is typical for 'weakest link processes'. The cumulative distribution function can then be described as

$$F(t) = 1 - \exp\left[-\left(\frac{t}{\eta}\right)^{\beta}\right],\tag{19}$$

where  $\beta$  is the shape factor of the distribution, often called the Weibull slope, and  $\eta$  is a scale factor. Eq. (19), can be rearranged such that

$$\ln[-\ln(1 - F(t))] = \beta \ln(t) - \beta \ln(\eta), \qquad (20)$$

which implies that a plot of  $\ln[-\ln(1 - F)]$  as a function of the logarithm of t yields a straight line with a slope of  $\beta$ .

Lognormal distribution has also been used to analyze accelerated test data of dielectric breakdown. Although it may fit failure data over a limited sample set, it has been demonstrated that the Weibull distribution more accurately fits large numbers of TDDB failures [20]. An important disadvantage of lognormal distribution is that it does not predict the observed area dependence of  $t_{BD}$  for ultrathin gate oxides.

## 2.2.3. The breakdown event

The breakdown event itself is usually described using a "weakest link" model. Gate oxide failure is a weakest link type of problem because the whole chip fails if any one device fails, and a device fails if any small portion of the gate area of the device breaks down.

The first 'weakest link' model was formulated by Sune et al. [21] in the early 1990s and described oxide breakdown and defect generation via a Poisson process. In this model, a capacitor is divided into a large number of small cells. It is assumed that during oxide stressing, neutral electron traps are generated at random positions on the capacitor area. The number of traps in each cell is counted. Once the number of traps in a cell reaches a critical value, breakdown will occur. The disadvantage of Sune's model is its two-dimensional nature. A new three-dimensional model, based on the percolation concept has been suggested in Ref. [22] and has been thoroughly elaborated in Refs. [23,24]. The model assumes that electron traps are generated inside the oxide at random positions in space. Around these traps, a sphere is defined with a fixed radius r, which is the only parameter of the model. If the spheres of two neighboring traps overlap, conduction between these traps becomes possible by definition.

This mechanism of trap generation continues until a conducting path is created from one interface to the other, which defines the breakdown condition. The percolation model for oxide breakdown is able to quantitatively explain two important experimental observations: (i) as the oxide thickness decreases, the density of oxide traps needed to trigger breakdown decreases [23–25], and (ii) as the oxide thickness decreases, the Weibull slope of the breakdown distribution decreases and approaches unity, i.e. a larger spread of the  $t_{BD}$ -values is observed [23,24,26,27].

Oxide thickness will continue to be scaled in future devices because of the need to improve and optimize circuit performance. The effect of TDDB in the case of ultrathin oxides is still arguable. The contrasting viewpoints indicate the need for better understanding of TDDB as device features shrink.

#### 2.3. Hot carrier injection

Hot carriers in the semiconductor device are the cause of a distinct wearout mechanism, the hot carrier injection (HCI). Hot carriers are produced when the source–drain current flowing through the channel attains high energy beyond the lattice temperature. Some of these hot carriers gain sufficient energy to be injected into the gate oxide, resulting in charge trap and interface state generation. The latter may lead to shifts in the performance characteristics of the device, e.g., the threshold voltage, transconductance, or saturation current, and eventually to its degradation.

The rate of hot carrier injection is directly related to the channel length, oxide thickness and the operating voltage of the device. Since the latter are minimized for optimal performance, the scaling has not kept pace with the reduction in channel length. Current densities have been increased with a corresponding increase in device susceptibility to hot carrier effects.

## 2.3.1. HCI physics

Hot carriers are generated during the operation of semiconductor devices as it switch states. As carriers travel through the channel from source to drain, the lateral electric field near the drain junction causes carriers to become hot [28]. A small part of these hot carriers gain sufficient energy—higher than the Si–SiO<sub>2</sub> energy barrier of about 3.7 eV—to be injected into the gate oxide. In nMOS (negative-channel metal-oxide semiconductor) devices, hot electrons are generated while hot holes are produced in pMOS (positive-channel metal-oxide semiconductor) devices. Injection of either carrier results in three primary types of damage: trapping of electrons or holes in pre-existing traps, generation of new traps, and the generation of interface traps [29]. These traps may be classified by location [30] while their effects vary.

Interface traps are located at or near the  $Si-SiO_2$  interface and directly affect transconductance, leakage current and noise level. Oxide traps are located further away from the interface and affect the long term MOSFET stability, specifically the threshold voltage. Effects of defect generation include threshold voltage shifts, transconductance degradation and drain current reduction [28]. NBTI seems to have similar degradation patterns, except for pMOS, so both will be treated similarly here.

Hu et al. [31] proposed the 'lucky' electron model for hot carrier effects. This is a probabilistic model proposing that a carrier must first gain enough kinetic energy to become 'hot', and then the carrier momentum must become redirected perpendicularly so the carrier can enter the oxide. The current across the gate is denoted by  $i_{gate}$  and during normal operation its value is negligible. Degradation due to hot carriers is proportional to  $i_{gate}$ , making the latter a good monitor of the former. If the rate of change of the HCI-induces damage, designated by  $\Delta$ , is proportional to  $i_{gate}$ , then

$$d\Delta/dt \sim i_{\text{gate}} = A(\Delta)/W \cdot i_{\text{drain}} \cdot (i_{\text{sub}}/i_{\text{drain}})^m, \qquad (21)$$

where W is the width of the MOSFET. By letting  $B = A(\Delta)/W$ , and knowing that MTTF depends on the reciprocal of  $d\Delta/dt$ , the failure rate is found from

$$\lambda = B \cdot i_{\text{drain}} \cdot \left( i_{\text{sub}} / i_{\text{drain}} \right)^m. \tag{22}$$

This equation assumes static (dc) voltages and currents. To account for dynamic degradation  $\lambda$  has to be integrated over a full cycle time.

Temperature plays an interesting, though small role in hot carrier injection, since the activation energy is negative, implying that HCI diminishes with increasing temperature. At low temperatures, the substrate current increases because the drain current increases. According to Acovic et al. [32], the effects of oxide degradation are stronger at low temperatures because the electrons, having lower thermal energy, are more confined within the negatively charged degraded zone. Another possibility is that freezeout of impurities in the drain at low temperatures makes n-MOSFETs more sensitive to electrons trapped in the drain region, increasing degradation. Degradation decreases at high temperatures because the drain current and the mean free path decrease.

#### 2.3.2. Lifetime prediction

The lucky electron model does not fully predict hot carrier injection lifetime. Since there is no direct method of measuring device lifetime, the Arrhenius relationship remains a favored lifetime prediction tool. The following models are from JEP-122A [14]. It contains two models. The *N*-Channel model is for nMOS devices. In these devices the substrate current is an indicator of hot carriers. The MTTF equation is

$$MTTF = B(i_{sub}) - N \exp(E_a/kT), \qquad (23)$$

where *B* is a scale factor, which is a function of doping profiles, sidewall spacing, dimensions, etc.,  $i_{sub}$  is the substrate current, *N* ranges from 2 to 4, and  $E_a$  is the activation energy in the range of -0.1 eV to -0.2 eV.

In pMOS devices, hot holes do not show up as substrate current. However, the gate current can serve as an indicator of hot carriers. Thus the *P*-Channel model is

$$MTTF = B(i_{gate})^{-M} \exp(E_a/kT), \qquad (24)$$

where *B* and  $E_a$  are the same as before while  $i_{gate}$  is the peak gate current during stressing and *M* ranges from 2 to 4. However, the Arrhenius term is not necessarily appropriate for these mechanisms.

#### 2.3.3. Lifetime distribution model

There is little discussion in literature about a proper statistical lifetime distribution model for hot carrier injection. A logical hypothesis for the lifetime distribution would be the exponential one. This is a good assumption because as a device becomes more complex, with millions of gates, it may be considered as a system.

The failure probability of each individual gate is not most likely an exponential distribution. However, the cumulative effect of early failures and process variability, ensuring each gate has a different failure rate, widens the spread of the device failures. The end result is that intrinsic hot carrier injection becomes statistically more random as the failures occur at a constant rate.

#### 2.3.4. Lifetime sensitivity

As for EM, hot carrier injection lifetime is sensitive to changes in the input parameters. The acceleration factor for hot carrier injection is

$$A_{\rm F,HCD} = \exp(B(1/V_{\rm dd} - 1/V_{\rm dd,max})).$$

(25)

HCI continues to be a reliability concern as device feature sizes shrink. HCI is a function of internal electric fields in the device and as such is affected by channel length, oxide thickness and device operating voltage. Shorter channel lengths decrease reliability but the oxide thickness and the voltage may also be reduced to help alleviate the reduction in reliability. Another way of improving hot carrier reliability may be by shifting the position of the maximum drain so it is deeper in the channel [32]. This would result in hot carriers being generated further away from the gate and Si-SiO<sub>2</sub> interface, reducing the likelihood of injection into the gate. Another method is to reduce the substrate current by using a lightly doped drain (LDD) where part of the voltage drop is across a lightly doped drain extension not covered by the gate. Annealing the oxides in NH<sub>3</sub>, N<sub>2</sub>O or NO or growing them directly in N<sub>2</sub>O or NO improves

their resistance to interface state generation by the hot carriers.

### 2.4. Negative bias temperature instability

NBTI differs from hot carrier injection in that NBTI causes a shift in the device threshold voltage. The mechanism for NBTI damage are holes trapped within the interface between the  $SiO_2$  gate insulator and the Si substrate. NBTI damage is most prevalent in p-MOSFET devices where holes are thermally activated and gain sufficient energy to disassociate the interface/oxide defects near the lightly doped drain (LDD) regions. This happens at the LDD regions because of the higher hole concentrations near the gate edge.

NBTI mainly occurs in p-channel MOS devices stressed with negative gate voltages at elevated temperatures. It appears to be negligible for positive gate voltage and for either positive or negative gate voltages in n-MOSFETs. NBTI manifests itself as decrease in absolute drain current  $I_{\text{Dsat}}$  and transconductance  $g_m$  while the absolute "off" current  $I_{\text{off}}$  and threshold voltage  $V_{\text{th}}$  increase.

The typical stress conditions of NBTI are temperatures of 100–250 °C and oxide electric fields below 6 MV/cm. These stress conditions are typical during burn-in. The threshold voltage  $V_{\rm th}$  and flat-band voltage  $V_{\rm FB}$  of a MOS-FET are given by

$$V_{\rm th} = V_{\rm FB} - 2\phi_{\rm F} - \frac{|\mathcal{Q}_{\rm B}|}{C_{\rm ox}},\tag{26}$$

$$V_{\rm FB} = \phi_{\rm MS} - \frac{Q_{\rm f}}{C_{\rm ox}} - \frac{Q_{\rm it}(\phi_{\rm s})}{C_{\rm ox}}.$$

(27)

The fixed oxide charge  $Q_f$  and the interface-trapped charge density  $Q_{it}$  are the two factors determining the threshold voltage shift. Positive increases of these two parameters lead to a negative threshold voltage shift:

$$\Delta V_{\rm th} = -\frac{\Delta Q_{\rm it}(\phi_{\rm s})}{C_{\rm ox}} - \frac{\Delta Q_{\rm f}}{C_{\rm ox}}.$$

(28)

During the NBTI degradation, the threshold voltage shifts to more negative direction, affecting either the interface traps or the fixed oxide charges.

The simplest form of the on-state driving current  $I_{\text{Dsat}}$ and transconductance  $g_m$  of a MOSFET is given by

$$I_{\text{Dsat}} = \frac{W}{2L} \mu_{\text{eff}} C_{\text{ox}} (V_{\text{gs}} - V_{\text{th}})^2, \qquad (29)$$

$$g_m = \frac{W}{L} \mu_{\rm eff} C_{\rm ox} (V_{\rm gs} - V_{\rm th}). \tag{30}$$

These equations show that the parameters leading to  $I_{\text{Dsat}}$ and  $g_m$  degradation are the threshold voltage and the mobility  $\mu_{\text{eff}}$ . The mobility degradation is mostly induced by interface trap generation, leading to additional surface-related scattering.

#### 2.4.1. NBTI physics

Since first observed by Deal et al. [33] in 1967, NBTI has been intensively investigated and many models for its physical mechanisms have been proposed. The three most prominent models in the literature feature holes injection into the oxide, electron tunneling and electrochemical reactions.

The hole-trapping model is based on avalanche hole injection measurements of unstressed MOS capacitors and NBTI tests [34–36]. This model proposes that the negative midgap voltage shift (which is believed to be a monitor of the positive oxide charge with no contribution from interface states), is due to population of intrinsic hole traps. All the positive charge generated by preceding negative bias stresses can be removed by the positive bias stress. However, the exact mechanism for hole injection into the oxide is still unknown.

The thermally assisted electron tunneling model was established by Breed [37,38]. According to this model, the neutral or positive centers, which are the charge traps, are located near the oxide interface. Under negative bias stress, the centers are excited. The electrons tunnel from the excited states into empty states of the Si conduction band. This is a thermally assisted tunneling process.

Several authors proposed the electrochemical reaction model or the reaction-diffusion model, which has recently been accepted by many researchers [39–42]. This model explains the NBTI effect in terms of electrochemical reactions.

NBTI became evident with the advent of  $0.13 \,\mu\text{m}$  processes as devices required much thinner gate oxides and introduced nitrides in the SiO<sub>2</sub> to prevent boron penetration into the gate. Another source of concern is plasma-induced damage during interconnect deposition resulting in driving hydrogen atoms into the Si–SiO<sub>2</sub> interface.

#### 2.4.2. Lifetime prediction

Generally, a threshold voltage shift  $\Delta V_{\text{th}}$  caused by NBTI can be expressed as

$$\Delta V_{\rm th} = A f_1(t) f_2(V_{\rm g}) \exp\left(\frac{-E_{\rm a}}{kT}\right). \tag{31}$$

Here  $f_1$  and  $f_2$  are functions account for the time dependence and gate voltage dependence. Based on the physical mechanisms and experimental data, several models for the time dependence have been suggested.

## 2.4.2.1. Logarithmic time dependence

$$\Delta V_{\rm th} = A \log(t). \tag{32}$$

This model was established on the ideal of charge trapping, wherein carriers tunnel into existing traps [33]. According to this model, the NBTI is field accelerated, and there is little or no temperature activation. The saturation behavior is due to the finite trap density. There is significant deviation at long time when using this model. However, it is frequently observed in recent high-k gate dielectrics experiments.

2.4.2.2. Exponential time dependence

$$\Delta V_{\rm th} = A \exp\left(\frac{t}{\tau}\right) \tag{33}$$

or

$$\Delta V_{\rm th} = A \exp\left(\frac{t}{\tau_1}\right) + B \exp\left(\frac{t}{\tau_2}\right). \tag{34}$$

A single exponential time dependence model was established at first based on the first order reaction, which was limited by the hole concentration [39]. Different from the logarithmic time dependence, this model suggested the temperature activation from the reactions. Later, a two-exponential model was further suggested [43,44].

## 2.4.2.3. Power law time dependence.

$$\Delta V_{\rm th} = At^n. \tag{35}$$

The power law model was based on the reaction diffusion mechanism. According to this model, the hydrogen profile determines the time dependency [40,41]. The temperature dependence arises from the reaction and diffusion processes and the saturation behavior comes from the diffusion barrier or the available Si–H bonds. Compared with the other two models, this model has the most observed features and is widely accepted.

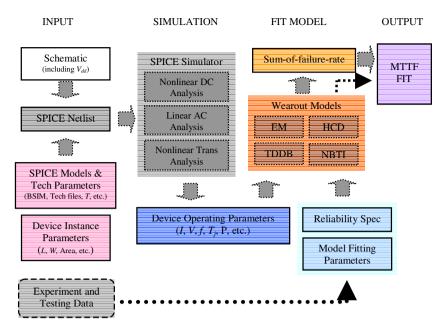

#### 3. Review of existing reliability simulation tools

IC reliability simulation is not a new concept and a number of reliability models and simulation methodologies such as BERT [45] and ARET [46] have been developed during the past decade. Most state-of-the-art reliability simulation methods try to emulate the degradation process of aged devices in a repetitive scheme. They are based on the physical failure mechanisms and contain the major wearout models for EM, HCI, NBTI and TDDB. A set of parameters for each of these failure mechanisms are identified and the algorithms of extracting these parameters for a given technology are developed by accelerated tests on test structures. A circuit simulator, such as SPICE, is employed to calculate the electrical parameters of fresh and degraded devices to predict their degradation or failure from these parameters.

This reliability simulation method can help designers understand how the devices degrade over time, identify the reliability bottlenecks within the circuits and make design tradeoffs between performance and reliability in the product design stage. It can also help manufacturers build their circuits such that no known wearout mechanism will dominate over the life of an operating device and assure adequate reliability for the product. In what follows, two commercial state-of-the-art reliability simulation methods are reviewed, then a set of failure equivalent circuits for the most important intrinsic silicon wearout mechanisms including HCI, TDDB and NBTI are reviewed. Finally, in the next section, a new failure rate-based SPICE reliability simulation methodology is introduced to investigate product reliability in different ways.

## 3.1. Degradation-based reliability simulation tools

Hot carrier reliability simulation models and methods have been implemented and widely used in the semiconductor industry for many years. To some extent, the accuracy of hot carrier reliability simulation represents the robustness and efficiency of the entire reliability simulator, therefore, for the purpose of simplicity, HCI simulation is employed as the vehicle to deliver the basic concepts and flows realized in some commercial degradation-based reliability simulation methods.

#### 3.1.1. Hot carrier reliability simulation in Virtuoso UltraSim

Virtuoso UltraSim is the Cadence FastSPICE circuit simulator capable of predicting and validating timing, power and reliability of mixed-signal, complex digital and System-on-Chip (SoC) designs in advanced technology of 0.13  $\mu$ m and below. It has a set of specialized reliability models (AgeMos) for HCD and NBTI simulation [47]. In the simulation, an Age parameter is calculated for each nMOS device with the following formula:

$$Age(\tau) = \int_{t=0}^{t=\tau} \left(\frac{I_{sub}}{I_{ds}}\right)^m \frac{I_{ds}}{WH} dt, \qquad (36)$$

where W refers to the width of the transistor; m and H are technology dependent parameters and determined from experiments;  $I_{sub}$  is the substrate current;  $I_{ds}$  is the drain current;  $\tau$  is the time for stress. For pMOS devices, the gate current  $I_{gate}$  is used instead of  $I_{sub}$  to determine the Age parameter. The degree of MOS device degradation has been experimentally found to be a function of this Age parameter for wide ranges of channel length and stress conditions and the relationship has a plausible theoretical basis [48].

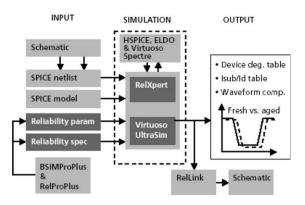

The simulation starts with device parameter extraction and modeling. From the SPICE model parameters of fresh devices, some other device parameters are added to accurately model  $I_{sub}$ . Saturation current  $I_{dsat}$ , threshold voltage,  $V_{\rm th}$ , or the maximum transconductance,  $g_{\rm max}$ , can be used as a degradation monitoring parameter.  $I_{dsat}$  is a good degradation monitor for digital circuits, while  $V_{\rm th}$  is suitable for analog applications. Normally, the stress time resulting in 10% decrease of one of these degradation monitoring parameters is arbitrarily set as the device lifetime. The final step is AgeMos extraction. Based on the Age parameter calculated after the fresh simulation, the Age-Mos applies the degradation models, which can be input to most SPICE-like simulators, for the aged circuit simulation. Reliability simulation with Virtuoso UltraSim is an iterative process, in which several iterations are often needed in order to get accurate modeling. The simulation can calculate and output the degradation results to predict the lifetime of each MOS instance [49]. The overall simulation flow is depicted in Fig. 1.

Fig. 1. Hot carrier reliability simulation flowchart in Virtuoso UltraSim [45].

The fundamental models and methodology of reliability simulation was first proposed and implemented in BERT (Berkeley Reliability Tools), introduced by Chenming Hu in 1992 [48]. This approach to reliability equivalent circuits was commercially realized in Virtuoso UltraSim and similarly in ELDO, the simulator developed by Mentor Graphics. The main advantages of the BERT simulation methodologies are accuracy and SPICE modeling technology compatibility. However, it imposes a burden on designers to correctly extract the device fresh and degraded parameters and leads to non-physical trends, which prevents its popularity in reliability design process. These tools are very important for the IC designers, but once a circuit is produced, no flexibility remains to alter the reliability if a new application or set of operating parameters is applied.

#### 3.1.2. Hot carrier reliability simulation in Eldo

Eldo and UltraSim both deliver all the capability and accuracy of SPICE-level simulation for complex analog circuits and SoC designs. However there are some subtle differences. In Eldo, the substrate current  $I_{sub}$  is not selected as the primary reliability parameter as in UltraSim. In general, the drain current  $I_d$ , threshold voltage  $V_t$  or transconductance  $g_m$  is often used as a degradation monitoring parameter, and the stress time resulting in 10% decrease of one of these monitoring parameters is arbitrarily set to the device lifetime. Hot carrier reliability simulation in Eldo adopts  $I_d$  as the degradation monitoring parameter and characterizes it with a compact  $\Delta I_d$  model, which directly models the difference of drain currents between fresh and aged devices.

There exist two competing mechanisms, which lead to the obvious hot carrier induced drain current variations between fresh and degraded devices: the deviation of  $I_d$ from its linear dependence on  $V_{ds}$  due to velocity saturation effects and the decreasing of  $\Delta I_d/I_d$  due to the reduction of charged interface states [51]. In Eldo, the  $\Delta I_d$  is modeled with Eq. (41) to (40), which unify the subthreshold, linear and saturation regions with a simple relation for both forward and reverse operation modes [50]:

$$\frac{\Delta I_{\rm d}}{I_{\rm d}} = \left(\frac{B_6(1 - e^{-B_1 V_{\rm gs}}) + B_2}{1 + B_5(V_{\rm gs} - B_3 V_{\rm th})}\right) \left(\frac{N_{\rm it} L_{\rm it}}{L_{\rm eff}}\right) \\ \times \left(\frac{1}{1 + \alpha(V_{\rm ds} - V_{\rm low}) + \beta V_{\rm ds}}\right), \tag{37}$$

$$V_{\rm low} = A_3 V_{\rm dsat},\tag{38}$$

$$\alpha = \frac{A_1}{1 + A_4 (V_{\rm gs} - V_{\rm th})^{A_2}},\tag{39}$$

$$\beta = A_5 V_{\rm gs} + A_6, \tag{40}$$

where  $N_{it}$  is the interface trap density,  $L_{it}$  is the extension of the damage within the channel,  $L_{eff}$  is the effective channel length,  $V_{gs}$  is the gate-to-source voltage,  $V_t$  is the threshold voltage,  $V_{ds}$  is the drain-to-source voltage,  $V_{dsat}$  is the drain saturation voltage,  $A_1$  to  $A_6$  and  $B_1$  to  $B_6$  are model fitting parameters.

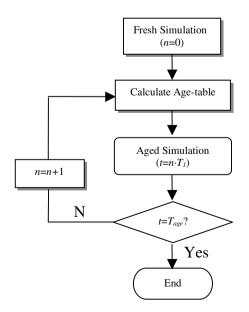

The same Age parameter defined by Eq. (36) is incorporated to model the "age" of each transistor. The HCI aging process is simulated in an iterative way as depicted schematically in Fig. 2.

The period,  $T_{age}$ , at which the circuit performance is to be tested is divided into smaller time intervals,  $T_1$ . The *Age* table is calculated at the end of each time interval and a new simulation with Eldo is carried forward. This process is repeated until  $T_{age}$  is reached. This iterative scheme can account for the gradual change of bias conditions as a result of device wearout.

The  $\Delta I_d$  modeling approach provides the possibility to have a relatively simpler parameter extraction process. It is suitable to model bi-directional stress and asymmetrical drain current behavior. However, because this approach also adopts both *Age* parameter and small-step iterative algorithm in the degradation simulation process, it inherits the same limitations of the BERT-like tools as discussed before.

Fig. 2. HCI reliability simulation in Eldo [50]. A large number of SPICE simulation iterations have to be carried out to obtain accuracy.

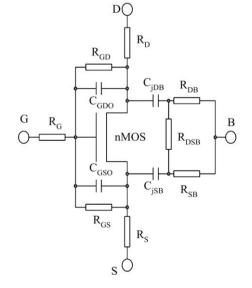

#### 3.2. Failure mechanism equivalent circuits

In order to account for the effect of the failure mechanisms on circuit functionality and reliability, the devicelevel lifetime models have to be extended to circuit-level applications. The bridge connecting the gap between device wearout degree and circuit performance drift is no doubt the circuit models. The underlying concept of the circuit models is modeling degradation of device parameters with some additional lumped circuit elements (resistors, transistors or dependent current sources, etc.) to capture the behavior of a damaged MOSFET in circuit operation environment. The values of these additional lumped elements are determined by device wearout parameters (such as  $\Delta N_{\rm it}$ which are time dependent and by device terminal voltage and current waveforms, therefore, at any time t, values of these lumped elements can be predicted accurately and their magnitudes reflect the device wearout degree. The larger the magnitude of these values, the more severe is the damage to circuit functionality. As a result, circuit designers can quickly analyze circuit reliability behavior at any given time with these circuit models.

## 3.2.1. HCI

Several HCI circuit models have been developed in the past years and some of them have been built into commercial reliability simulation tools. In this section, some of these circuit models are briefly reviewed, followed by the introduction of the HCI circuit model and its implementation.

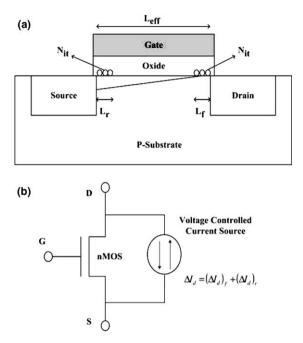

BERT has been the most successful circuit reliability simulation tool. BERT directly models n-MOSFET hot carrier damage in drain current degradation. The drain current degradation,  $\Delta I_d$ , results from the drain mobility degradation, which again results from HCI-induced interface traps  $\Delta N_{it}$ .  $\Delta N_{it}$  is modeled in terms of the famous *Age* parameter introduced in the previous section. In BERT,  $\Delta I_d$  is implemented as an asymmetrical voltage controlled current source in parallel with the original n-MOS-FET. The p-MOSFET HCI effect is modeled with the concept of channel shortening and drain resistance increase [45]. The BERT  $\Delta I_d$  model is shown in Fig. 3. Here one can see asymmetry in the forward and reverse I-V characteristics, allowing the simulation of devices undergoing bi-directional stresses (such as devices in a transmission gate).

The detailed  $\Delta I_d$  model equations and parameters are defined in [52]. The main contribution of BERT  $\Delta I_d$  model is the ability to characterize bi-directional hot carrier stress effects, however it requires extraction of six process parameters from device testing, which is a non-trivial work.

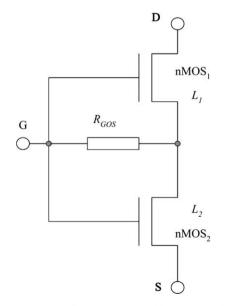

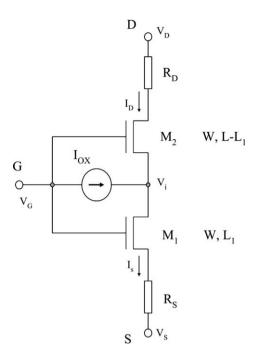

Experiments have proven that HCI-induced interface traps in n-MOSFET are localized above the channel near the drain junction. More specifically, these interface traps are localized within 100 nm from the drain [53]. Based on this observation, Leblebici et al. at UIUC [54,55] developed a two-transistor HCI circuit model, which consisted of an HCI damaged parasitic transistor with fixed channel length

Fig. 3. BERT n-MOSFET HCI circuit model. (a) Bidirectional interface trap generation near both drain and source.  $L_{\rm f}$  and  $L_{\rm r}$  represent forward and reverse hot carrier damaged regions. (b) HCI drain current  $\Delta I_{\rm d}$  circuit model [51].

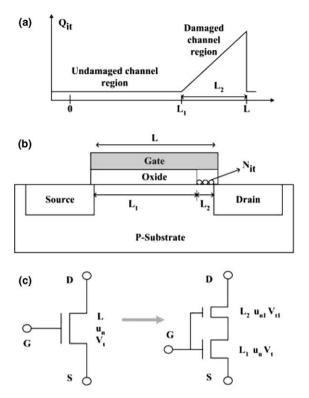

$L_2$  ( $L_2 \approx 0.1 \,\mu$ m) in series connection with the original transistor whose channel length was shrunk to  $L - L_2$ . The primary assumption for this model is that all generated interface traps are occupied with electrons, which equals to considering only negative fixed charge. The model is illustrated in Fig. 4.

From Fig. 4a, the interface trapped charge  $Q_{it}$  due to HCI can be readily derived as

when

$$(0 \le x \le L_1)$$

:

$Q_{it}(x) = 0$

(41)

or when  $(L_1 \leq x < L)$ :

$$Q_{\rm it}(x) = \frac{Q_M}{L_2}(x - L_1),$$

(42)

where  $Q_M$  denotes the largest interface charge,  $L_1 = L - L_2$ , and  $L_2$  represents the length of the damaged channel region. This two-transistor model characterizes the amount of hot carrier damage with only two parameters  $Q_M$  and  $L_2$ , therefore, the model parameter extraction work is greatly reduced. The drawbacks of this model are: that the triangular charge density distribution is over simplified, and that an accurate  $Q_M$  value is difficult to extrapolate.

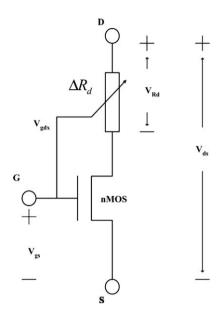

The simplest HCI circuit model has been the hot carrier induced series resistance enhancement model (HISREM), also named  $\Delta R_d$  model, which is proposed by Hwang et al. at Oregon State University [58]. Based on the fact that the increase of HCI-induced series drain resistance is due to the injection of hot carriers close to the drain edge, a series resistance  $\Delta R_d$  added to the drain of the n-MOSFET can

Fig. 4. UIUC n-MOSFET HCI two-transistor series model. (a) Triangular oxide charge distribution profile used in model derivation. (b) Crosssectional view of n-MOSFET with hot carrier damage,  $L_2$  is the damaged channel region. (c) Two-transistor series circuit model. The parasitic transistor has different channel mobility and threshold voltage with the channel length  $L_2$  set to 0.1 µm [54,56,57].

reflect the process of hot carrier induced interface trap generation and therefore accounts for the channel mobility reduction and threshold voltage drifts. HISREM consists of a voltage dependent drain resistor  $\Delta R_d$  connected in series with the original n-MOSFET.  $\Delta R_d$  is a function of the applied voltages and the hot carrier induced interface trapped charge  $\Delta N_{it}$ .

The behavior of the damaged n-MOSFET is emulated by the original undamaged device operated with a reduced drain-to-source voltage, which is controlled by this additional drain resistor  $\Delta R_d$ . Because  $\Delta N_{it}$  is a time dependent parameter,  $\Delta R_d$  model is able to predict drain current degradation at any given time. HISREM is also capable of modeling self-limiting effects of hot carrier damage because the increase in series drain resistance of an n-MOSFET suppresses hot carrier stress. The most advantageous feature of the HISREM model is that only one parameter,  $\Delta N_{it}$ , needs to be extrapolated from device testing work. Consequently, HISREM can be easily used by circuit designers to perform an expeditious reliability analysis.

The HCI circuit model is based on the above  $\Delta R_d$  model with some improvements. The major improvement is that  $\Delta R_d$  value is considered to be determined by both interface trapped charge  $\Delta N_{it}$  and oxide trapped charge  $\Delta N_{ox}$ . The contribution of  $\Delta N_{ox}$  to device wearout is often neglected, but recent experimental work recognizes that they can

Fig. 5. HCI circuit model. In the model:  $V_{\text{gd}x} = V_{\text{gs}} - V_{\text{t}} - V_{\text{ds}}$  and  $V_{R_{\text{d}}} = I_{\text{ds}} \Delta R_{\text{d}}$ .  $V_{\text{t}}$  is threshold voltage and  $I_{\text{ds}}$  is the current from node D to S.

account for some of the observed enhanced degradation effects in n-MOSFETs which could not be explained solely by  $\Delta N_{\rm it}$  generation.

The HCI circuit model is illustrated in Fig. 5. The derivation of  $\Delta R_d$  is carried out assuming that (1) all interface traps are acceptor-like and occupied by electrons, and (2) the channel mobility degradation,  $\mu$ , is caused by both  $\Delta N_{\rm it}$  and  $\Delta N_{\rm ox}$ . The assumption (1) means the net charge in interface traps is a fixed negative charge for n-MOSFET in strong inversion operation. Assumption (2) leads to:

$$\mu = \frac{\mu_0}{(1 + \alpha \cdot \Delta N)},\tag{43}$$

where  $\Delta N = \Delta N_{it} + \Delta N_{ox}$  (in unit cm<sup>-2</sup>),  $\mu_0$  is the original channel mobility,  $\alpha$  is a process dependent constant and  $\alpha \approx 2.4 \times 10^{-12}$  cm<sup>2</sup> [58].

The drain current drain flowing through an undamaged nMOS (when  $\Delta N = 0$  at t = 0) is defined as  $I_{ds0}$ :

$$I_{\rm ds0} = \mu_0 C_{\rm ox} \frac{W}{L} \left( V_{\rm gs} - V_{\rm t} - \frac{V_{\rm ds}}{2} \right) V_{\rm ds}.$$

(44)

When  $\Delta N$  is small, the relation between fresh and degraded drain-to-source current is

$$I_{\rm ds} = \frac{I_{\rm ds0}}{1 + \alpha \cdot \Delta N}.\tag{45}$$

This leads to an expression of  $\Delta R_d$  which is determined by  $\Delta N$  and the terminal voltages and currents

$$\Delta R_{\rm d} = \frac{V_{R_{\rm d}}}{I_{R_{\rm d}}} = \frac{1 + \alpha \cdot \Delta N}{I_{\rm ds0}} V_{R_{\rm d}},\tag{46}$$

where  $I_{ds0}$  is given by Eq. (43) and  $V_{R_d}$  is calculated using [59]:

$$V_{R_{\rm d}} = -V_{\rm gdx} + \sqrt{V_{\rm gdx}^2 + 2V_{\rm ds}\,\Delta N \left[\frac{\alpha \left(V_{\rm gdx} + \frac{V_{\rm ds}}{2}\right)}{1 + \alpha \cdot \Delta N} + \frac{q}{C_{\rm ox}}\right]},\tag{47}$$

where  $V_{\text{gd}x} = V_{\text{gs}} - V_{\text{t}} - V_{\text{ds}}$  for the linear region and  $V_{\text{gd}x} = 0$  for the saturation region.

In quasi-static operation,  $\Delta N$  is a time-dependent parameter, therefore,  $\Delta R_d$  is also time-dependent. At any given time *t*, if  $\Delta N$  is known,  $\Delta R_d$  will be uniquely determined. The models for  $\Delta N$  and  $\Delta N_{\text{ox}}$  have been well documented in literature [53,54].  $\Delta N_{\text{it}}$  can be calculated using

$$\Delta N_{\rm it} = C_1 \left[ \frac{I_{\rm ds}}{W} \exp\left( -\frac{\Phi_{\rm it,e}}{q\lambda_{\rm e}E_m} \right) t \right]^n,\tag{48}$$

where W is the channel width,  $\Phi_{it,e}$  is the critical energy for electrons to create an interface trap,  $\lambda_e$  is the hot-electron mean free path and  $C_1$  is a process constant.

The models and model parameters for  $\Delta N_{\rm ox}$  are given in [55] (on pp. 59–66). For convenience, they are recapitulated as

$$\Delta N_{\rm ox} = N_1 [1 - \exp(-\sigma_1 I_{\rm ei} t)] - N_2 [1 - \exp(-\sigma_2 I_{\rm ei} t)].$$

(49)

A set of typical model fitting parameters, for Eq. (49), have been given in [55] (p. 65). The above new  $\Delta R_d$  model inherits all the merits of HISREM model and it is physically more comprehensive in characterizing hot carrier damages. The drawback of this improved  $\Delta R_d$  model is the inclusion of one more parameter  $\Delta N_{ox}$ , which complicates parameter extraction work.

## 3.2.2. NBTI

Simulating the impact of NBTI at the circuit level using SPICE is very important [60]. Most of the work on NBTI SPICE simulation is performed such that the degraded circuit behavior is simulated using the transistor parameter  $V_t$ , which is shifted by a fixed value [61]. This kind of simulation method cannot physically relate circuit performance degradation to NBTI wearout under dynamic operation conditions since it does not include the NBTI stress time as a parameter. The most effective way to develop such a relation is by developing a NBTI circuit model. However, to the best of our knowledge, no such electrical model exists in literature. Stretched exponential time dependence describes the threshold voltage degradation as

$$\Delta V_{t}(t) = \Delta V_{\max} \left[ 1 - \exp\left(-\frac{t}{\tau}\right)^{\beta} \right].$$

(50)

Thus, a new NBTI circuit model is proposed, which is an electrical model relating the time dependent NBTI physical degradation parameter  $\Delta V_t$  to lumped electrical model elements, thereby enabling effective and quick NBTI circuit reliability simulation.

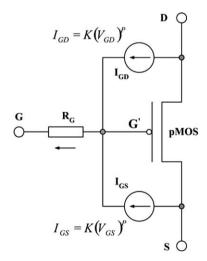

The most severe NBTI effect is p-MOSFET threshold voltage increase— $\Delta V_t$ , which is equivalent to a decrease in the p-MOSFET absolute gate-to-source voltage. This is equivalent to adding a voltage source at the gate. However, we chose to split the p-MOSFET gate connection and add a gate resistance  $R_{\rm G}$  between the original gate biasing point G and the p-MOSFET gate terminal G'. This allows inclusion of a gate leakage current flowing mechanism (voltage controlled current sources between gate and drain and between gate and source), so that the NBTI model can be included with the TDDB model without a conflict developing by having a voltage source and current source at the same node. In fact, there should be no difference between using a voltage source or a current source to represent  $\Delta V_{\rm t}$ , whereby the gate leakage current flows through the gate resistance  $R_G$  and increases the p-MOSFET effective gate voltage at point G'. This gate current would depend on the gate voltage because of R. The current may be somewhat un-physical so a substrate bias source may be substituted instead, but many possibilities have yet to be explored in this area.

Since the p-MOSFET source is held fixed at its highest potential, the inclusion of  $R_G$  and gate leakage current leads to a decrease of the p-MOSFET absolute gate-tosource voltage, thereby imitating the NBTI threshold voltage degradation. Based on this concept, the NBTI circuit model is constructed and shown in Fig. 6. The advantage of this configuration will become clear when compared to the model for TDDB, presented next.

In this model,  $R_G$  is a voltage dependent resistance because gate leakage currents are voltage dependent.  $R_G$ is also a time dependent resistance because voltage drop across  $R_G$  at any specific time t is equal to threshold voltage shift  $\Delta V_t$  which is time dependent. According to [62], the gate leakage current due to oxide breakdown can be

Fig. 6. NBTI circuit model. NBTI-induced p-MOSFET threshold voltage increase is modeled as absolute gate-to-source voltage decrease. Gate tunneling current flowing through the gate resistance  $R_G$  leads to the increase of voltage at point G'. This corresponds to the decrease of p-MOSFET absolute gate-to-source voltage and therefore mimics the threshold voltage degradation effect. Gate tunneling current is modeled with two voltage controlled current sources which follow the form of a power law relation as:  $I = KV^p$ .

modeled as a gate-to-diffusion leakage current, with a power law dependence of the formula  $I = KV^p$  (where K and p are fitting parameters). The same power law voltage dependency, shown in Fig. 6, is adopted in modeling gate leakage currents. As a result, for the gate-to-drain leakage current,  $I_{GD} = K(V_{GD})^p$ , and for the gate-to-source leakage current,  $I_{GS} = K(V_{GS})^p$ . The default value of p is set to 5, and the default value of K is  $3 \times 10^{-6}$  [62].

In Fig. 6, the voltage drop across  $R_{\rm G}$  is

$$V_{R_{\rm G}}(t) = V_{\rm G'} - V_{\rm G} = \Delta V_{\rm G}(t) = (I_{\rm GD} + I_{\rm GS})R_{\rm G}.$$

(51)

Threshold voltage degradation  $\Delta V_t$  due to NBTI is already given by Eq. (50). Therefore, from the relation  $\Delta V_G(t) = \Delta V_t(t)$ , we obtain an analytical solution for  $R_G$ :

$$R_{\rm G} = \frac{\Delta V_{\rm max}}{KV_{\rm GD}^{\rho} + KV_{\rm GS}^{\rho}} \left[ 1 - e^{-\left(\frac{j}{\tau}\right)^{\beta}} \right].$$

(52)

The typical values and extraction methods for the model parameters  $\Delta V_{\text{max}}$ , *K*, *p*,  $\tau$  and  $\beta$  have been given and discussed during the process of deriving Eq. (52).

One of the most important points shown in Fig. 6 is that this new model is much better than a simple model which only inserts a voltage source between G and G' representing threshold voltage shift in that it inherently incorporates both NBTI and possible oxide breakdown effects.

For nMOS positive bias temperature instability (PBTI) circuit model, a similar structure to that for pMOS NBTI shown in Fig. 6 can be constructed, except that all current flowing directions are reversed and the model fitting parameters of the threshold voltage model  $\Delta V_t$  (Eq. (50)) are determined from nMOS PBTI stress testing. For the two current sources  $I_{GD}$  and  $I_{GS}$  in nMOS PBTI circuit model, a better gate leakage model, proposed by Lee et al. [63] is adopted:

$$I_{\rm GS} = \frac{1}{2} A L \exp(\alpha V_{\rm GS} - \beta t_{\rm ox}^{-\gamma})$$

(53)

and

$$I_{\rm GD} = \frac{1}{2} A L \exp(\alpha V_{\rm GD} - \beta t_{\rm ox}^{-\gamma}), \qquad (54)$$

where  $I_{\rm GS}$  and  $I_{\rm GD}$  are in  $\mu$ A, *L* is effective channel length in nanometer,  $t_{\rm ox}$  is oxide thickness in nanometer, A = 127.04,  $\alpha = 5.61$ ,  $\beta = 10.6$  and  $\gamma = 2.5$ . These typical values for n-MOSFETs were obtained by fitting industrial data and found to be good for technologies across many generations up to 0.13  $\mu$ m. These new leakage models are able to maintain good stability in SPICE simulation [63].

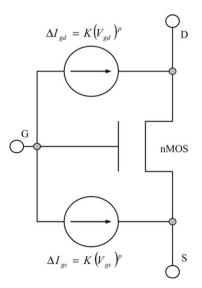

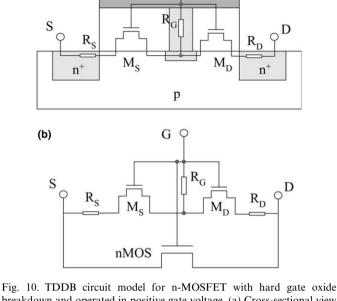

3.2.3. TDDB

It is onerous work to develop an effective circuit model for gate oxide breakdown because device post-breakdown behavior is extremely complicated, and has been perplexing the reliability physics community for decades. Device I-Vcharacteristics after gate oxide breakdown relies on many parameters including, breakdown location, transistor type, voltage polarity, device operation mode (accumulation or inversion), oxide area and even poly-gate doping type. Interestingly, literature searches reveal that TDDB failure modeling is a very active area and more than a dozen circuit models have been developed by various research institutes and industrial labs. All this work attempts to develop quantitative methodologies for predicting the response of circuits to gate oxide breakdown events [64]. In this section, some of the most successful TDDB failure circuit models are reviewed. The first equivalent circuit, developed by Rodriguez et al., models oxide soft-breakdown as a progressive wearout phenomenon, whereas the others model oxide breakdown as a catastrophic singular event.

Starting from the observation that a CMOS inverter's transfer curve under gate oxide stresses can be fitted by a combination of a threshold voltage shift (caused by charge trapping prior to breakdown) and a gate-to-drain leakage current model, which follows the form of a power-law relation as  $I = KV_{gd}^{p}$ . Rodriguez et al. at IBM [65,66,62] developed a simple TDDB circuit model, which consists of a voltage-dependent current source bridging either gate-to-drain or gate-to-source, depending on the breakdown location, allowing the oxide breakdown leakage current in a transistor to be simulated in a circuit. This power-law leakage current model is illustrated in Fig. 7.