#### Emerging Power-Gating Techniques for Low Power Digital Circuits

#### Michael B. Henry

Dissertation submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

> Doctor of Philosophy in Computer Engineering

Leyla Nazhandali, Chair Wu-chun Feng Mary Jane Irwin Cameron D. Patterson Joseph G. Tront

November 3rd, 2011 Blacksburg, Virginia

Keywords: Digital Electronics, Low Power, Power-Gating, NEMS, Sense-amplifier Pass Transistor Logic

Copyright 2011, Michael B. Henry

# Emerging Power-Gating Techniques for Low Power Digital Circuits Michael B. Henry ABSTRACT

As transistor sizes scale down and levels of integration increase, leakage power has become a critical problem in modern low-power microprocessors. This is especially true for ultra-low-voltage (ULV) circuits, where high levels of leakage force designers to chose relatively high threshold voltages, which limits performance. In this thesis, an industry-standard technique known as power-gating is explored, whereby transistors are used to disconnect the power from idle portions of a chip. Present power-gating implementations suffer from limitations including non-zero off-state leakage, which can aggregate to a large amount of wasted energy during long idle periods, and high energy overhead, which limits its use to long-term system-wide sleep modes. As this thesis will show however, by vastly increasing the effectiveness of power-gating through the use of emerging technologies, and by implementing aggressive hardware-oriented power-gating policies, leakage in microprocessors can be eliminated to a large extent. This allows the threshold voltage to be lowered, leading to ULV microprocessors with both low switching energy and high performance.

The first emerging technology investigated is the Nanoelectromechnical-Systems (NEMS) switch, which is a CMOS-compatible mechanical relay with near-infinite off-resistance and low on-resistance. When used for power-gating, this switch completely eliminates off-state leakage, yet is compact enough to be contained on die. This has tremendous benefits for applications with long sleep times. For example, a NEMS-power-gated architecture performing an FFT per hour consumes 30 times less power than a transistor-power-gated architecture. Additionally, the low on-resistance can lower power-gating area overhead by 36-83%.

The second technology targets the high energy overhead associated with powering a circuit on and off. This thesis demonstrates that a new logic style specifically designed for ULV operation, Sense Amplifier Pass Transistor Logic (SAPTL), requires power-gates that are 8-10 times smaller, and consumes up to 15 times less boot-up energy, compared to static-CMOS. These abilities enable effective power-gating of an SAPTL circuit, even for very short idle periods. Microprocessor simulations demonstrate that a fine-grained power-gating policy, along with this drastically lower overhead, can result in up to a 44% drop in energy.

Encompassing these investigations is an energy estimation framework built around a cycle-accurate microprocessor simulator, which allows a wide range of circuit and power-gating parameters to be optimized. This framework implements two hardware-based power-gating schedulers that are completely invisible to the OS, and have extremely low hardware overhead, allowing for a large number of power-gated regions. All together, this thesis represents the most complete and forward-looking study on power-gating in the ULV region. The results demonstrate that aggressive power-gating allows designers to leverage the very low switching energy of ULV operation, while achieving performance levels that can greatly expand the capabilities of energy-constrained systems.

# Contents

| 1 | Introduction |                                                                 |    |

|---|--------------|-----------------------------------------------------------------|----|

|   | 1.1          | Organization and Key Findings                                   | 4  |

| 2 | Bac          | kground                                                         | 7  |

|   | 2.1          | Ultra-Low-Voltage Operation                                     | 7  |

|   | 2.2          | Power-Gating                                                    | 10 |

| 3 | Eff          | ective Long-Term Power-Gating with NEMS Switches                | 13 |

|   | 3.1          | Introduction                                                    | 13 |

|   | 3.2          | CMOS-Compatible NEMS Switches                                   | 16 |

|   | 3.3          | Theoretical Analysis of Transistor- and NEMS-based Power-Gating | 19 |

|   |              | 3.3.1 Transistor-Based Power-Gating                             | 20 |

|   |              | 3.3.2 NEMS-Based Power-Gating                                   | 21 |

|   | 3.4          | Implementation                                                  | 22 |

|   |              | 3.4.1 NEMS Power-Gating System Overview                         | 22 |

|   |              | 3.4.2 NEMS Switch Physical Parameters                           | 25 |

|   |              | 3.4.3 FFT Architectures                                         | 26 |

|   | 3.5          | Methodology                                                     | 27 |

|   |              | 3.5.1 NEMS Switch Simulation                                    | 28 |

|   |              | 3.5.2 NEMS Area Analysis                                        | 29 |

|   |              | 3.5.3 NEMS Energy Analysis                                      | 29 |

|   |     | 3.5.4 F                       | FT Architectural Exploration                          | 30 |  |

|---|-----|-------------------------------|-------------------------------------------------------|----|--|

|   |     | 3.5.5 T                       | Cechnology Scaling Exploration                        | 30 |  |

|   | 3.6 | Results .                     |                                                       | 31 |  |

|   |     | 3.6.1 N                       | VEMS Area Analysis                                    | 31 |  |

|   |     | 3.6.2 N                       | VEMS Energy Analysis                                  | 32 |  |

|   |     | 3.6.3 A                       | Architectural Exploration Results                     | 33 |  |

|   |     | 3.6.4 T                       | Pechnology Scaling Exploration Results                | 36 |  |

|   | 3.7 | Conclusi                      | on                                                    | 39 |  |

| 4 | Fir | ne-Graine                     | ed Power-Gating: Transistors vs. NEMS                 | 41 |  |

|   | 4.1 | Introduc                      | tion                                                  | 41 |  |

|   | 4.2 |                               | al Unit Energy Model in the of Power-Gating           | 44 |  |

|   | 4.3 | Function                      | al Unit Power-Gating Policies                         | 47 |  |

|   | 4.4 | 4 NEMS Simulation Environment |                                                       |    |  |

|   |     | 4.4.1 S                       | ystem Overview                                        | 52 |  |

|   | 4.5 | Function                      | al Unit Simulation Environment                        | 54 |  |

|   | 4.6 | Results .                     |                                                       | 55 |  |

|   |     | 4.6.1 N                       | VEMS Energy Analysis                                  | 55 |  |

|   |     | 4.6.2 Id                      | deal Policy                                           | 56 |  |

|   |     | 4.6.3 I                       | Flag Policy                                           | 58 |  |

|   |     | 4.6.4 N                       | VEMS Endurance Results                                | 59 |  |

|   | 4.7 | Conclusi                      | on                                                    | 61 |  |

| 5 |     |                               | Grained Power-Gating with ifier Pass-Transistor Logic | 63 |  |

|   | 5.1 | Introduc                      | tion                                                  | 63 |  |

|   | 5.2 | Sense-Ar                      | mplifier Pass-Transistor Logic:                       | 65 |  |

|   | 5.3 | Low Pow                       | ver-Gating Overhead with SAPTL                        | 69 |  |

|   |     | 521 L                         | solation Colls                                        | 60 |  |

|              |                             | 5.3.2 Current Spikes                        | 0          |  |  |

|--------------|-----------------------------|---------------------------------------------|------------|--|--|

|              |                             | 5.3.3 Reduced Power-Network Capacitance     | 1          |  |  |

|              | 5.4                         | Experimental Methodology                    | <b>'</b> 4 |  |  |

|              | 5.5                         | Results                                     | 7          |  |  |

|              | 5.6                         | Conclusion                                  | 31         |  |  |

| 6            | Con                         | clusion 8                                   | 4          |  |  |

|              | 6.1                         | Recommendations for Future Work             | 86         |  |  |

| $\mathbf{A}$ | A SAPTL Synthesis Framework |                                             |            |  |  |

|              | A.1                         | Overview                                    | 39         |  |  |

|              | A.2                         | FPGA Synthesis and BDD Reduction            | 00         |  |  |

|              | A.3                         | Delay Estimation                            | )1         |  |  |

|              |                             | A.3.1 Worst Case Delay                      | )4         |  |  |

|              | A.4                         | Results                                     | )5         |  |  |

|              | A.5                         | Potential Improvements                      | 7          |  |  |

|              |                             | A.5.1 Delay-Aware Critical Path Mapping     | 7          |  |  |

|              |                             | A.5.2 BDD Remapping to Mitigate Sneak-Paths | 8          |  |  |

|              |                             | A.5.3 Small Node Conversion to CMOS         | 9          |  |  |

|              | A.6                         | Conclusion                                  | 00         |  |  |

# List of Figures

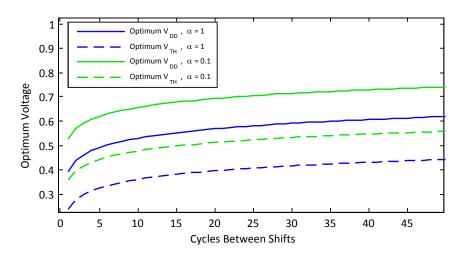

| 2.1  | Optimum Supply and Threshold Voltage of a 32-bit barrell shifter        | 9  |

|------|-------------------------------------------------------------------------|----|

| 2.2  | The limitations of power-gating                                         | 10 |

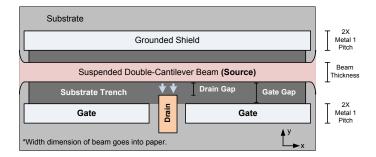

| 3.1  | NEMS switch layout                                                      | 17 |

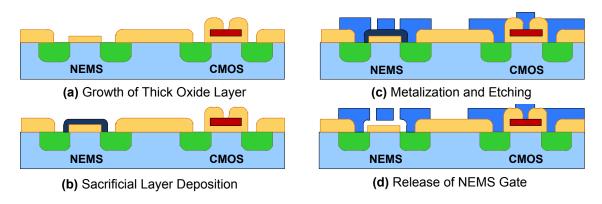

| 3.2  | Hybrid CMOS-NEMS production flow                                        | 18 |

| 3.3  | System diagram of a NEMS power-gating scheme.                           | 23 |

| 3.4  | Schematic and simulation of a charge pump                               | 24 |

| 3.5  | Total energy of 4 FFT architectures                                     | 27 |

| 3.6  | Power-gating area overhead                                              | 31 |

| 3.7  | Average power consumption of transistor-power-gated architectures       | 34 |

| 3.8  | Average power consumption of NEMS-power-gated architectures             | 35 |

| 3.9  | Energy per cycle of NEMS- and transistor-power-gated architectures      | 37 |

| 3.10 | Energy components of transistor- and NEMS-power-gated FFT architectures | 38 |

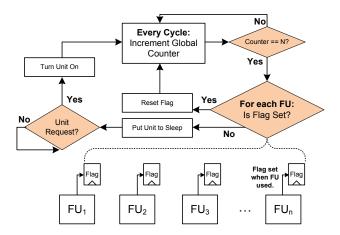

| 4.1  | Hardware flowchart for the Flag Policy                                  | 48 |

| 4.2  | Flag Policy pseudocode                                                  | 48 |

| 4.3  | System diagram of NEMS functional unit power-gating scheme              | 52 |

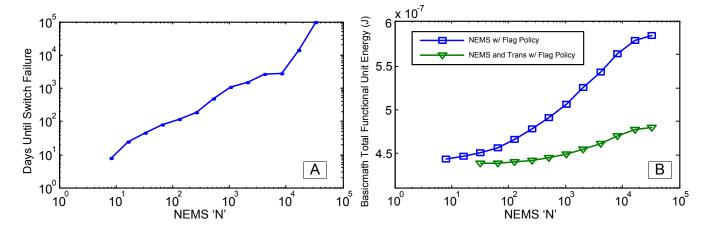

| 4.4  | Effect of Flag Policy aggressiveness on NEMS lifetime                   | 60 |

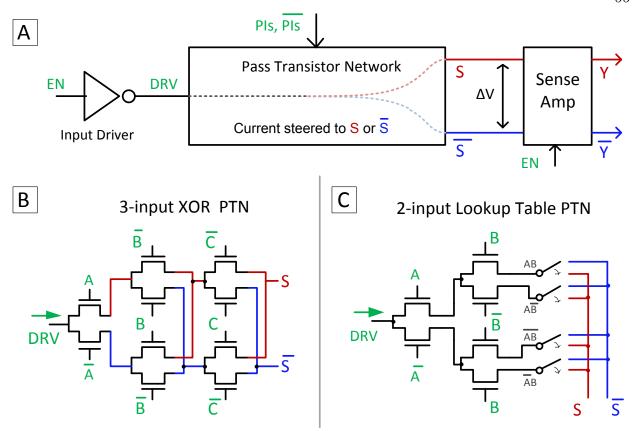

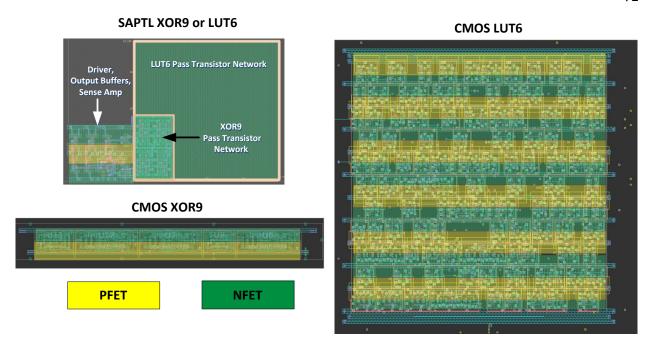

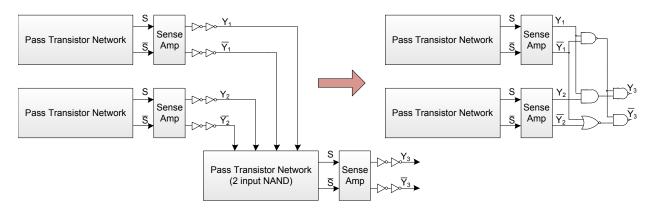

| 5.1  | Overview of SAPTL                                                       | 66 |

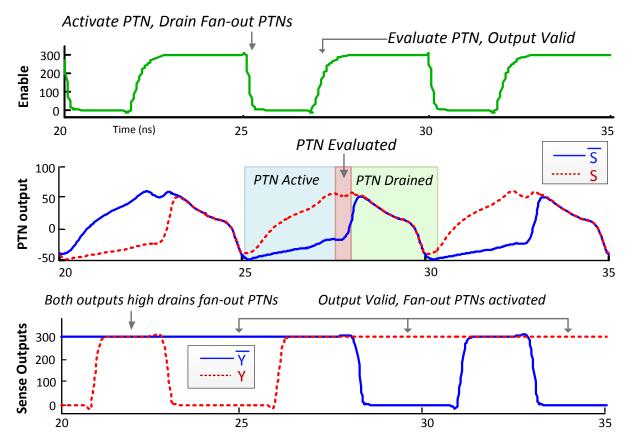

| 5.2  | SAPTL simulation waveforms                                              | 67 |

| 5.3  | Power-gating isolation overview                                         | 69 |

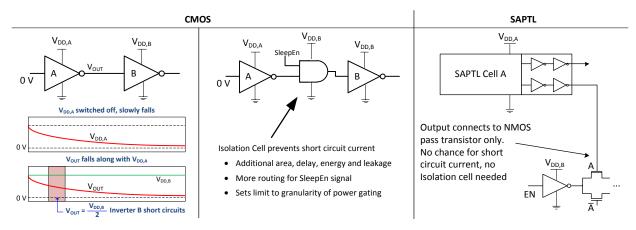

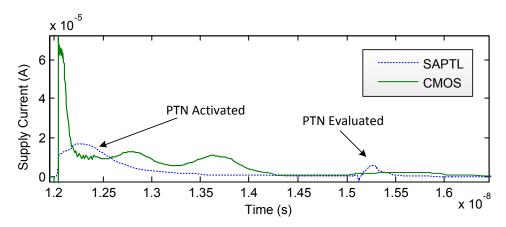

| 5.4  | Current spikes of CMOS and SAPTL                                        | 70 |

| 5.5 | PFET area of CMOS and SAPTL                                                       | 72 |

|-----|-----------------------------------------------------------------------------------|----|

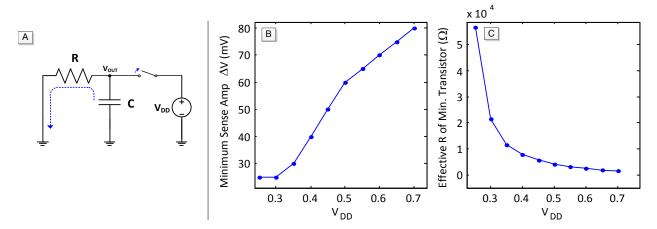

| A.1 | Minimum $\Delta V$ of Sense-amp; Effective Resistance of minimum sized transistor | 91 |

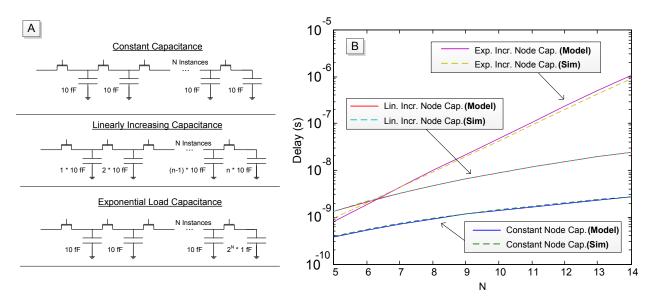

| A.2 | Simulation vs. model of RC ladder delay                                           | 93 |

| A.3 | Pseucode used to determine worst-case delay of an SAPTL cell                      | 94 |

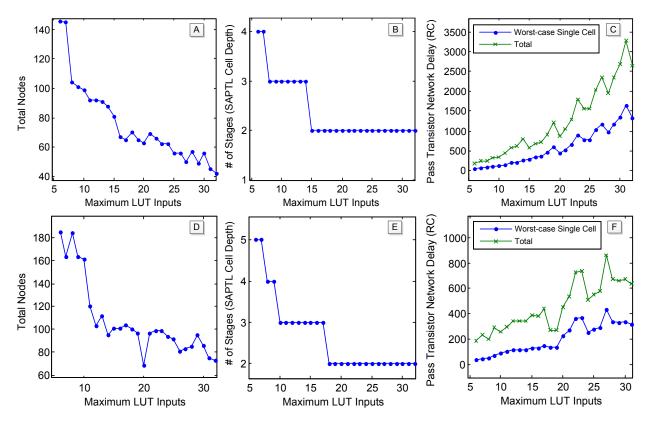

| A.4 | Results of SAPTL synthesis                                                        | 96 |

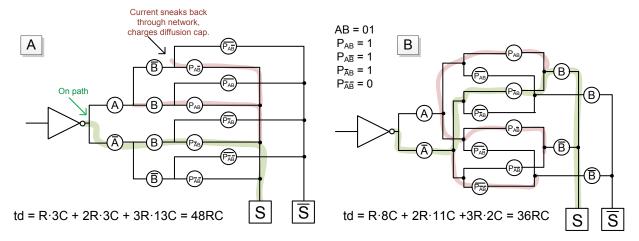

| A.5 | Reording of BDD to reduce delay                                                   | 98 |

| A 6 | Collapsing small SAPTL cells into CMOS                                            | 90 |

# List of Tables

| 3.1 | Physical characteristics of the switches used in this study                                                               | 25 |

|-----|---------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Time and energy required to active NEMS switch bank                                                                       | 33 |

| 4.1 | Physical characteristics of the switches used in this study                                                               | 53 |

| 4.2 | Results of charge pump and NEMS switch simulations                                                                        | 55 |

| 4.3 | Comparison of ideal power-gating policies to no power-gating with respect to percent drop in total functional unit energy | 56 |

| 4.4 | Comparison of ideal power-gating policies to no power-gating with respect to percent drop in total functional unit energy | 57 |

| 4.5 | Comparison of Flag Policy to no power-gating with respect to percent drop in total functional unit energy                 | 58 |

| 4.6 | Effect of limiting NEMS switch rate by setting $N$ to 2048                                                                | 59 |

| 5.1 | Small-Circuit Comparison of CMOS to SAPTL                                                                                 | 77 |

| 5.2 | Large-circuit Comparison of CMOS to SAPTL                                                                                 | 78 |

| 5.3 | Comparing the Immediate Policy to both the Flag Policy and no power-gating for CMOS functional units                      | 80 |

| 5.4 | Comparing the Immediate Policy to both the Flag Policy and no power-gating for SAPTL functional units                     | 81 |

# Chapter 1

### Introduction

One of the biggest challenges related to low-power design is mitigating and controlling the leakage power of a circuit. What was once considered a minor nuisance a decade ago has now become one of the top design priorities in modern microprocessors. The assault of leakage power has seemingly come from all sides. Technology scaling has allowed for more functionality per area, higher speeds, and lower switching energy, but has also increased leakage power exponentially. Likewise, supply voltage scaling has yielded a dramatic reduction in switching energy, but has typically been accompanied by a reduction in threshold voltage in order to maintain performance, which also increases leakage power. Finally, as the demand for more capability and performance continues to grow, the number of functional blocks and the amount of memory has increased dramatically, and more transistors means more leakage power.

High levels of leakage power have now impacted all levels of digital design, and has stopped supply voltage scaling in its tracks, which used to be the most popular method for keeping power consumption under control. The last few decades has seen a steady drop in the power consumption of integrated circuits, due to the reduction of supply voltage, which at one time used to be as high as 5 V. To prevent any lost performance, this was accompanied by a drop in threshold voltage, which also increases the severity of leakage. With the recent

dominance of leakage power, however, it became untenable to continue to reduce the threshold voltage, which meant the supply voltage for performance-constrained applications has remained around 1 V for the last decade.

This has not stopped researchers and designers from continuing to reduce the supply voltage for applications that are more energy-constrained than performance-constrained. Recent advances in circuit design have allowed researchers to operate chips with supply voltages well below the range normally used by integrated circuits. In the so-called *Ultra-Low-Voltage* (ULV) region, switching energy is dramatically reduced, which is advantageous for emerging applications with very tight energy budgets. Without the accompanying reduction in threshold voltage, however, performance is seriously impacted, so current ULV prototypes are only suited for non-performance-constrained applications. This clearly demonstrates how leakage power is intertwined with switching energy and performance: by mitigating leakage power, designers can push supply voltages into the ULV region, while at the same time lowering the threshold voltage. This would lead to a large drop in switching energy, while keeping performance levels constant, thus greatly expanding the capabilities of energy-constrained integrated circuits.

One of the most obvious places to mitigate leakage power is during standby periods, when no processing is occurring. To accommodate the growing popularity of mobile, wireless, and sensor processing, all of which have substantial idle times, the microprocessor industry has widely adopted power-gating and software-controlled sleep modes. With this technique, transistors are used to disconnect the power from unused portions of a microprocessor, which substantially reduces leakage power. This approach is attractive because it mitigates leakage without requiring any modification to the logic or operation of the power-gated circuit. That being said, there are still many design challenges related to power-gating, as well as inefficiencies that limit its effectiveness.

In this thesis, emerging technologies are examined that target the inefficiencies of powergating. Special attention is paid to the ULV region, where large reductions in leakage can also lead to a large drop in switching energy. The first inefficiency stems from the unavoidable aspects of using transistors as power-gates. When a circuit is turned off, the transistor power-gates themselves leak, meaning leakage is reduced, but not eliminated. Also, a voltage drop is created across the power-gate, which lowers the effective supply voltage of the power-gated circuit, thus slowing it down. Making a transistor power-gate wider decreases the voltage drop, but increases the off-state leakage, meaning a trade-off exists. This trade-off can make it exceedingly difficult for designers to size the power-gates, since different operating conditions may have different optimal sizings. In this thesis, an emerging CMOS-Compatible technology, the Nanoelectromechanical-Systems (NEMS) Switch, is investigated as an alternate power-gating structure. Due to an air-gap, NEMS switches have a nearly infinite off-resistance, which essentially eliminates off-state leakage. They also have a very low on-resistance, which greatly mitigates the performance drop of power-gating. NEMS-based power-gating is examined in a wide variety of scenarios, including long-term power-gating, where the switch-rate is low, and fine-grained power-gating of the functional units of a microprocessor, where a unit may be frequently power-gated for short periods of time.

The second inefficiency of power-gating results from the energy overhead associated with powering a functional block on and off. When power-gating is implemented, there are varying levels of granularity at which an unused functional unit can be powered off. In a coarse-grained approach, software-controlled sleep modes are implemented which shut down the entire processor during the long idle periods. More fine-grained approaches shut down idle functional units of a microprocessor, even while active processing is occurring, generally using either software or hardware control. The limit to the granularity of power-gating is the energy overhead: if it takes a lot of energy to turn a unit off and on, then it may not be possible to target short idle periods, since the leakage energy saved would be outweighed by the power-gating energy overhead.

The energy overhead of static-CMOS is generally high due to the high power-network capacitance and large current spikes. In this thesis, an alternative form of logic is investigated: Sense-Amplifier-Pass-Transistor-Logic (SAPTL). This style of logic, originally designed for

ultra-low-voltage operation in highly variant environments, also has significantly lower power-gating overhead. This opens the door to a new paradigm: *Ultra-Fine-Grained* power-gating. With this approach, functional units are shut down almost immediately after use, which, when paired with a power-gating system with very low overhead, leads to large drops in energy consumption.

As part of these investigations, a detailed analytical energy estimation framework is presented that can quickly optimize the various parameters of a power-gated system, including supply voltage, threshold voltage, transistor power-gate width, NEMS switch selection, etc. Integrated with this energy framework is a cycle-accurate simulator with the capability of power-gating individual functional units. The cycle-accurate simulator implements two power-gating policies that can be implemented completely in hardware with very little overhead. Thus, not only does this thesis present the most complete and methodical investigation into power-gating in the ULV region, covering nearly every aspect of its implementation, but it also looks forward into how emerging technologies and logic styles can greatly improve its efficiency.

#### 1.1 Organization and Key Findings

After a brief background on ULV operation and power-gating in Chapter 2, Chapter 3 analyzes long term power-gating using NEMS switches as power-gating structures. This is done for an FFT application using a comprehensive simulation framework and NEMS energy model. The key findings of this chapter are as follows:

• The infinite off-resistance of NEMS switches leads to large reductions in average power consumption for architectures with long sleep periods. As an example, a NEMS-power-gated architecture performing an FFT every hour consumes 30 times less power than a transistor-power-gated architecture.

- The area overhead of a power-gating implementation using state-of-the-art NEMS prototypes is estimated to be 36-83% lower, compared to transistor power-gates. Further improvements to the contact resistance of the switches would yield a much larger reduction.

- By eliminating off-state leakage, architecture selection becomes more straightforward.

With the zero off-state leakage of NEMS switches, no matter how long the idle periods are, the optimum architecture is generally the one that is the most efficient in terms of switching energy.

Chapter 4 analyzes fine-grained functional unit power-gating, where individual functional units of a microprocessor, such as the integer ALU, floating point unit, etc., are shut off when not in use through the use of a hardware-based power-gating policy. Both an ideal oracle policy and a simple hardware-based policy are simulated, and both NEMS and transistors are compared as power-gating structures. This chapter also presents the power-gating energy estimation framework and the microprocessor simulation environment, which are also used in Chapter 5. The key findings of this chapter are as follows:

- Functional unit power-gating pushes the optimum supply voltage and threshold voltage lower by 100-250 mV, which positively benefits all benchmarks, regardless of their functional unit usage behavior. Even a highly active floating point FFT benchmark that rarely shut any units off sees a 20.7% drop in total functional unit energy.

- With an ideal oracle-based scheduler, NEMS-based functional unit power-gating yields a 29.5% average reduction in total functional unit energy with respect to no functional unit power-gating, while an ideal transistor-based system yields a 23.5% reduction. While the difference is not overwhelming, it must be taken into account that NEMS switches are truly advantageous for long idle periods. These results, however, demonstrate that the high activation energy and delay of NEMS switches do not hinder their use when targeting shorter idle periods.

• With the more realistic hardware-based Flag Policy, NEMS power-gating yields a 28.9% drop in energy, while transistor power-gating yields a 23.0% drop in energy. As is evident, the Flag Policy achieves results that are very close to the ideal policy.

In Chapter 5, Ultra-Fine-Grained power-gating is examined, which targets very short idle periods of microprocessor functional units. A recently developed style of logic, SAPTL, is examined and the power-gating energy overhead is compared to CMOS through the simulation of hand-crafted small circuits and synthesis of larger circuits. The effect of the lower power-gating energy overhead of SAPTL on the effectiveness of functional unit power-gating of a microprocessor is then determined using the simulation framework from Chapter 4. The key findings of this chapter are as follows:

- Compared to CMOS, SAPTL requires power-gating structures that are 8-10 times smaller than CMOS. When booting up from a sleep mode, SAPTL circuits consume up to 40 times less energy.

- When integrated into the microprocessor simulations, this lower overhead, along with an extremely simple scheduler that simply shuts a functional unit off immediately after its use, leads to as high as a 44% drop in total functional unit energy.

The 44% drop in total functional unit energy that was achieved in Chapter 5 is remarkable considering the fact that this was achieved without any delay penalty, without any change to the logical structure, and in such a way that is completely invisible to the operating system or program that is running. This was accomplished solely by eliminating leakage and reducing  $V_{DD}$  and  $V_{TH}$ .

Chapter 6 offers conclusions as well as recommendations for future work on ULV power-gating. Appendix A presents a novel synthesis approach for SAPTL circuits, which is used in Chapter 5.

## Chapter 2

# Background

#### 2.1 Ultra-Low-Voltage Operation

Supply voltage scaling has long been a popular method for energy and power reduction due to the fact that reducing the supply voltage decreases switching power consumption quadratically, while only increasing circuit delay linearly. Traditionally, voltage scaling has been limited to around 700-800 mV, mainly due to issues with SRAM reliability and performance loss [9]. In recent years, the application space has opened up for devices such as wireless and ubiquitous sensors, biomedical implants, etc. with relaxed performance constraints and extremely tight energy budgets. This has motivated the scaling down of energy per operation and has led researchers to examine the limits to how low supply voltage scaling can go.

Traditional CMOS operation has been described as having an on-network of transistors operating in saturation and an off-network in weak-inversion (or cut-off). In reality, the line between on and off can be blurred: as long as the gain of the transistors is greater than one, and the on-network has a stronger drive-strength than the off-network, then complementary logic is possible [34]. This opens up the possibility of CMOS devices operating with a supply voltage that is at or less than the threshold voltage of the transistors, in the so-called *Ultra*-

Low Voltage (ULV) region. The basic principles of ULV operation are the same as nominal voltage operation (nominal voltage being the typical supply voltage the foundry recommends; currently around 1.0 V). The only difference is that rather than the on-network in saturation and the off-network in weak-inversion, both networks are in weak-inversion. Owing to the still-existing gate bias, however, the on-network has a higher drive strength, which makes complementary logic possible.

Theoretical operation of CMOS operation at ULV voltages has been known for decades [33], but in recent years, the fast-paced growth in energy constrained applications and devices has driven researchers to overcome major obstacles and build functional prototypes. These accomplishments include accurate circuit models, low voltage SRAM that can operate down to 180 mV [34], design standards for robust cells that can overcome the high potential for functional failure [19], and methodologies that can mitigate the severe process variation that ULV circuits experience [14]. Recent prototypes exemplify this surge in research and demonstrate the huge energy savings that are possible. The Phoenix processor [13] is a 1 mm<sup>2</sup> ultra-low-voltage processor that consumes 226 nW when active and 35 pW in a carefully designed sleep mode. In [19], a 300 mV ULV version of the popular Texas Instruments MSP-430 is presented that consumes 12.2 uW when active and 1 uW in a sleep mode. In was demonstrated in [17] that ULV operation can be used for energy efficient high-performance applications through parallelization by fabricating an MPEG processor that achieves 411 billion operations per watt(GOPS/W) at 300 mV, compared to only 43 GOPS/W at nominal voltage [17].

A major challenge of ULV operation is selecting an appropriate supply voltage and threshold voltage that balances performance, switching energy, and leakage power. Even if a set clock frequency is decided upon, the supply and threshold voltage can be jointly raised and lowered, which maintains a constant performance, but optimizes for either leakage energy or switching energy. This optimum point is dependent on the activity factor of the circuit. Given a constant delay, if the activity factor of a circuit is high, then a low supply  $(V_{DD})$  and threshold voltage  $(V_{TH})$  is optimal, whereas if the activity factor is low, a high  $V_{DD}$  and

**Figure 2.1:** Optimum Supply and Threshold Voltage of a 32-bit barrell shifter with a clock frequency of 100 MHz.

$V_{TH}$  is optimal. Figure 2.1 demonstrates this, which plots the optimum  $V_{DD}$  and  $V_{TH}$  for a 32-bit barrel shifter (130 nm technology, 100 MHz clock frequency), with respect to the number of idle clock cycles between shift operations. Two activity factors are shown, which correspond to the percentage of gates that switch during each shift operation. This graph clearly shows what was previously stated: high activity factors favor a low  $V_{DD}$  and  $V_{TH}$ , while low activity factors favor a high  $V_{DD}$  and  $V_{TH}$ .

It is conceivable to construct a circuit that can dynamically tune  $V_{DD}$  and  $V_{TH}$  to track the optimum voltages as the activity factor changes; circuits have been demonstrated that switch the power network between two  $V_{DD}$ s [26], and body biasing can be used to dynamically alter  $V_{TH}$  [18]. Actual implementation of a system such as this is exceedingly challenging, however. This is because 1) multiple power rails and body bias regions introduces significant additional area; 2) body biasing has greatly lost effectiveness in newer technologies due to higher doping concentrations [27]; and 3) tracking the activity factor in an energy efficient manner is a non-trivial task. A simpler approach, one that this thesis investigates thoroughly, is to use power-gating to shut off a circuit when not in use. By eliminating leakage during idle cycles, the activity factor is effectively increased, pushing the optimum  $V_{DD}$  and  $V_{TH}$  lower. The limiting factor to this approach is the effectiveness of power-gating. The present industry standard techniques used for power-gating are too energy inefficient to allow for

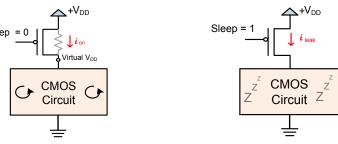

# When active, voltage drop across power-gates lowers virtual V<sub>DD</sub>

# When powered off, there is still leakage current through power-gates

Figure 2.2: The limitations of power-gating: performance drop and non-zero off-state leakage.

rapid power-gating, and the off-state leakage is non-zero. This motivates the focus of this thesis, which details how emerging technologies can be used to vastly improve the efficiency of power-gating. This would allow for a single optimum  $V_{DD}$  and  $V_{TH}$  across a wide range of operating conditions, which would greatly increase the energy efficiency of ULV circuits.

#### 2.2 Power-Gating

Transistor-based power-gating is implemented by placing sleep transistors in-line between the circuit and the power network (headers) or the ground network (footers). Footers are generally more area-efficient as the high n-type mobility means less of them are needed. That being said, most commercial designs implement headers due to easier design and analysis, especially when multiple power domains or an external switchable voltage regulator is used [35]. There are two major limitations of headers (and footers), which are outlined in Figure 2.2. First, the headers themselves leak which means leakage is reduced, but not eliminated. Second, when the headers are on, the current flowing though them creates a voltage drop on the power network that lowers the performance of the power-gated circuit [32]. This performance drop is especially severe with ULV processors, where delay is exponentially dependent on supply voltage; in this region, a small variation in voltage leads to a very large drop in performance.

The controlling factor of the trade-off between delay increase and off-state leakage reduction

is the width of the headers. A common industry practice is to size the headers such that the worst-case supply voltage drop is less than 10%, but this results in a large area overhead, and generally the sleep-mode leakage reduction is only around 90% [27]. During long idle periods, this remaining leakage can lead to significant amounts of wasted energy. The ultra-low power Phoenix processor took the opposite route and used a small amount of footers with non-minimal channel lengths [13]. This resulted in picowatt-range off-state power, but the large supply voltage drop limited the clock frequency to 106 kHz. This trade-off, and the desire to achieve a large reduction in off-state leakage without impacting performance motivates one of the examinations in this thesis, where an emerging technology, the CMOS-Compatible NEMS switch, is used as a power-gating structure.

#### Granularity of Power-Gating:

An important aspect of power-gating is the granularity at which it is performed. Temporal granularity determines how short the targeted idle periods can be, whereas regional granularity determines how many separable power-gating regions there are. It is usually the case that these two are intertwined. The most coarse-grained approach is to use an external switchable regulator. Switching off the voltage regulator would effectively eliminate on-chip leakage (though the regulator itself would still leak), but it is very coarse grained in both regards. First, the capacitance of the switched power network would be extremely large and would take a significant amount of time and energy to recharge upon boot-up [35], meaning only extremely long idle periods could be targeted. Second, each power-gated region would require separate power supply pins. In a pin-constrained chip, this places limits on the number of potential regions.

Modern low-power microprocessors tend to take a more fine-grained approach. It is now nearly universal that power-gating structures are moved on chip to avoid having to recharge the large external power network and decoupling capacitance present on-chip. There is also a great deal of active research into having separate power-gated regions of the chips that are individual targeted. One example is functional unit power-gating, where portions of a

microprocessor, such as the integer and floating point ALU, memory, I/O, are individually shut off when not in use. Many studies have been performed on functional unit power-gating, and they tend to focus on selecting appropriate sizes for headers, modeling the break-even cycle count of a functional unit [15], or crafting policies that increase the time a unit spends powered off [20, 29].

The goal of this thesis is to effectively eliminate leakage in such a way that a single low  $V_{DD}$  and  $V_{TH}$  becomes optimal. As such, granularity is a very important aspect that will be extensively analyzed. NEMS-based power-gating, which is presented in the next two chapters, allow for leakage elimination that is equivalent or better than what is achievable with an external switchable regulator. It is also CMOS-compatible and can be implemented on-chip, which means that the high external capacitances can be avoided, and much smaller power-gated regions can be targeted. Chapter 5 also focuses on granularity and introduces a new paradigm: Ultra-Fine-Grained power-gating. By greatly reducing the overhead of turning functional units on and off, very brief idle periods can be targeted and the level of leakage elimination can be greatly increased. Finally, a major focus of Chapter 4 and 5 is simple, hardware-only power-gating schedulers. By keeping the schedulers simple and in hardware, more regions can be power-gated, and their on/off state can be completely invisible to the OS.

## Chapter 3

# Effective Long-Term Power-Gating with NEMS Switches

#### 3.1 Introduction

A major limitation of CMOS power-gates is the fact that they do not completely eliminate off-state leakage when a circuit is powered off. For the rapidly emerging class of devices with long idle periods, such as environmental sensor networks, biomedical implants, wireless security systems, etc., the residual off-state leakage can accumulate to a large amount of wasted energy. The transistor power-gates can be made narrower or longer in order to reduce the residual leakage, however this increases the effective resistance of the power-gates, which slows down the circuit. This leads to a counterproductive trade-off between the amount of off-state leakage and the performance penalty. The only remaining method to combat the off-state leakage, while maintaining performance, is to raise both the threshold and supply voltage of the chip, which moves it away from the ULV region and deprives it of the low-energy benefits.

The over-arching parameter that determines the trade-off between leakage reduction and

delay-penalty is the on/off ratio of the transistor; a high on-current minimizes the voltage drop across the power-gating structure, while a low off-current minimizes residual off-state leakage. It is possible to use non-minimal lengths and adjust the sizing of a transistor to maximize the on/off ratio, but there is an upper limit and it is still too low for effective power-gating of energy constrained devices with long idle periods. Additionally, technology scaling has caused a large drop in the on/off ratio meaning power-gating is less effective at newer technology nodes. This motivates the search for a new power-gating structure with a significantly higher on/off ratio that can be seamlessly integrated onto a CMOS die, and has a reasonable area and energy overhead.

One leading contender is the CMOS-Compatible Nanoelectromechanical Systems (NEMS) switch, which is a nano-scale mechanical relay that has a near-infinite off resistance, low on-resistance, and a nanosecond-range mechanical switching delay [11]. Researchers of these devices envision entire circuits comprised of NEMS-based complementary logic, which would be entirely free of leakage power, but issues with switching speed and device lifetime have hampered these efforts [25]. However, a more feasible intermediate step would be a hybrid system with on-die NEMS switches acting as power-gates for CMOS circuitry. With the periodic systems described previously, the actuation rate for power-gates would be low enough that the billion-cycle lifetime of the NEMS devices is acceptable. Additionally, the sub-100 ns mechanical delay of a NEMS switch is tolerable for power-gating, since the wake-up times of most systems are in the microsecond range [27]. Thus, the zero off-leakage, low on-resistance, and on-die integration make NEMS switches very attractive for power-gating. This chapter presents an investigation that models and simulates all important aspects of CMOS-NEMS integration for power-gating and provides results that should motivate both industry and academia to pursue further research and eventual fabrication and commercialization of CMOS-NEMS systems.

Included in this chapter is a comprehensive study of NEMS-based power-gating in the context of coarse-grained power-gating of an FFT architecture. First, a background is provided on both the operation and integration of NEMS switches. Next, a simple energy model is

presented that provides insight into the behavior of a NEMS-power-gated circuit. The rest of this chapter presents the simulation framework that is used to compare the effectiveness of NEMS power-gates to transistor power-gates across a variety of metrics, including area overhead, activation energy, performance loss, and sleep-mode leakage. We do this for a range of FFT architectures and technologies and show that the many advantages of NEMS switches warrant further investigation into their use as power-gates. More specifically, the contributions of this chapter are as follows:

- We provide a system level simulation framework for NEMS-based power-gating that captures the major sources of energy, performance, and area overhead.

- Using an FFT processor benchmark, we compare the effectiveness of NEMS-based power-gating to transistor-based power-gating in the presence of aggressive voltage scaling and across a range of operating conditions and system-level parameters, such as core complexity and technology node.

- We parameterize the NEMS switch geometry and contact resistance and determine their effect on the energy and area overhead of power-gating.

#### Our findings are as follows:

- The infinite off-resistance of NEMS switches leads to large reductions in average power consumption for architectures with long sleep periods. As an example, a NEMS-power-gated architecture performing an FFT every hour consumes 30 times less power than a transistor-power-gated architecture.

- With transistor power-gates, the optimum FFT architecture, in terms of complexity, depends heavily on how often the FFT is performed. For example, architectures that favor low leakage power over switching energy efficiency are optimal at very low throughputs. With NEMS power-gates, due to the zero off-state leakage, the optimal architecture is always the one with the lowest switching energy consumption, which results in an architecture that is flexible for changing throughputs.

- The activation energy of the NEMS power-gate switch array in a 130 nm technology is in the nanojoule range, the activation time is under 40  $\mu s$ , and the on-power is effectively zero. The source of this energy and delay overhead is primarily from the charge-pump boot-up. These overhead values fall dramatically with lower technologies.

- The area overhead of a power-gating implementation using current NEMS prototypes is 36-83% lower, compared to transistor power-gates. Further improvements to the contact resistance of the switches would yield a much larger reduction.

#### 3.2 CMOS-Compatible NEMS Switches

Nano-Electro-Mechanical System (NEMS) switches are nano-scale relays with a suspended cantilever beam (representing the source) that bends under electrostatic force from the gate to form an ohmic contact with the drain. The off-resistance is nearly infinite due to the air gap between the source and drain, while the on-resistance is low due to the ohmic contact. The overriding motivation of NEMS researchers has been to develop entire circuits comprised solely of NEMS switches, and in fact complementary and complex logic built solely with these switches has been demonstrated [7]. Two major drawbacks have stifled progress on this front: first, the switching speed ranges from 10-100 ns, which is too slow for logic [6]; second, the reported lifetime has ranged from 10e8 to 10e12 on-off cycles [21,25] which does not guarantee a long enough lifetime for logic implementation. Since the switching is much less frequent with power-gating, the implications of these drawbacks are not as severe.

#### Principles of Operation:

Figure 3.1 gives a compact layout of a laterally actuated electrostatic NEMS switch and is based on previously fabricated devices [6,7,25]. The device operates by electrostatic force between the gate and a cantilever beam suspended across a trench in the substrate. When the voltage of the gate reaches the activation voltage of the switch, the electrostatic force overcomes the elastic force of the beam, which then collapses towards the drain. This forms

Figure 3.1: Layout of a compact double-cantilever NEMS switch supsended over a trench.

an ohmic contact that permits current to flow from the source to the drain. A wide range of contact resistances have been reported, ranging from 83  $\Omega$  with gold contacts [11], to several thousand  $\Omega$  with contact materials such as platinum [25] or aluminum oxide [16]. The primary reason for this wide range is that most prototypes are designed for NEMS-based digital logic, where the high mechanical delay completely dominates the electrical delay (and a high resistance is beneficial by limiting the current draw).

#### **Fabrication:**

NEMS switches are considered CMOS compatible for three reasons. First, the structural and contact materials can be built using CMOS materials such as polysilicon, platinum, and tungsten. Second, the switches can be patterned using photolithography and released (i.e. suspended over an air gap) using techniques that already exist in CMOS flows. Finally, the entire switch fabrication flow does not use temperatures or process steps that will harm the CMOS circuitry. Fabrication of NEMS switches broadly involves three steps. First, a sacrificial layer, represented by the dark gray rectangle in Figure 3.1, is patterned. Next, the NEMS structure, consisting of the beam, source, and gates, are patterned using polysilicon or metal, with the beam being patterned on top of the sacrificial layer. At this point, a low-resistivity metal coating can be applied to reduce the contact resistance. Finally, the sacrificial layer is removed leaving an air-gap above which the beam is suspended. Detailed fabrication steps of NEMS switches using standalone MEMS/NEMS processes can be found in [6, 7, 23, 25]. Additionally, Figure 3.2 presents a CMOS-NEMS hybrid manufacturing flow, originally proposed in [8], that requires the addition of only three process steps to the

**Figure 3.2:** Hybrid CMOS-NEMS production flow. Only three additional masks would need to be added to the CMOS process.

standard CMOS process flow.

It is also conceivable to manufacture the NEMS switches on a separate die and use 3DIC integration techniques to bond it to the logic die. This would be advantageous in two situations: first, if designers wish to exploit a state-of-the-art process which may not yet have NEMS integrated into the flow, they can manufacture the NEMS switches on an older, more mature process; second, a 2D array of switches can be mass produced on a state-of-the-art technology with the through-silicon-vias in predetermined spots. Designers could then connect to this array through 3D integration and use as many switches as they need. This could greatly drive down the costs because a single NEMS array design could be reused for thousands of different applications. This would be similar to the gate-array or sea-of-gates approaches.

#### **Tunable Parameters:**

Adjusting the beam length, thickness, and width (width dimension goes into the substrate trench), as well as the drain gap and the gate gap allows for both the switching speed and activation voltage to be tuned [6]. A longer, narrower beam generally results in a slower switch with a lower activation voltage, which translates to lower energy per actuation, while a shorter, wider beam produces a faster switch with a higher activation voltage. A narrower gate gap also produces a lower activation voltage, but the gap is limited by the lithography

of the technology. This implies that, much like transistors, the scaling down of feature sizes can have a direct positive impact on the activation voltage and energy per actuation.

# 3.3 Theoretical Analysis of Transistor- and NEMS-based Power-Gating

In order to provide insight into the behavior of transistor- and NEMS- power-gated systems, we derive some basic equations for the energy and power in the presence of voltage scaling. We first pay attention to the fact that voltage scaling and power-gating are not two independent knobs for power reduction. For example, if a design at nominal voltage is four times faster than the required throughput, it should spend 75% of the time power-gated. If we use voltage scaling to reduce its speed by half, it should spend 50% of the time power-gated. Therefore, depending on the efficiency of power-gating and the gain from voltage scaling, any of these solutions might be superior. The purpose of this section, therefore, is not to derive an analytical solution for optimizing power (which would be prohibitively difficult), but rather to describe the relationship between switch characteristics, power, supply voltage and target throughput. It should be noted that this is a simple model suitable for long idle periods. Chapter 5 presents a much more detailed model suitable for more fine-grained power-gating that accounts for power-gating overhead.

Let us define target throughput,  $R_T$ , as the desired number of tasks performed per second (for example, FFTs per second). Also, let us define energy, E, as energy per task. Average power consumption, P, can be determined by  $R_T \cdot E$ . For any given design, switching energy,  $E_S$ , leakage power,  $P_L$ , and maximum throughput,  $R_M$ , are all dependent on supply voltage and can be considered functions of V. Using these definitions, the average power consumption P of a non-switched, i.e. not power-gated, circuit with respect to  $R_T$  and supply voltage V, is defined as:

$$P(V, R_T) = R_T \cdot E_A(V) + P_L(V) \tag{3.1}$$

It should be noted that with non-switched circuits, as  $R_T$  approaches 0, the average power consumption approaches  $P_L$ , meaning the least complex design would consume the least amount of power.

#### 3.3.1 Transistor-Based Power-Gating

When transistor power-gates (headers) are used, they affect both the critical delay and leakage power of a circuit. To examine this, we use the terminology from [32], which identifies two effects that headers have on a circuit:  $K_D$  is the delay penalty, and is the factor by which a circuit slows down due to the voltage drop across the header.  $K_L$  is the leakage reduction, and is the factor by which the leakage is reduced when the power switch is off.  $K_D$  and  $K_L$  are dependent on the relative header width,  $W_H$ , which is defined as the width of the header divided by the sum of the widths of the NFETs of the circuit. The duty cycle, D, of the circuit is the the ratio between the time the switch has to be on and the total cycle time. Equation (3.2) provides the equation for duty cycle with respect to V,  $R_T$ , and  $W_H$ .

$$D(V, R_T, W_H) = \frac{R_T}{R_M(V)/K_D(W_H)}$$

(3.2)

By modifying (3.1), we can get (3.3) that provides the average power equation for transistor switched circuit:

$$P(V, R_T, W_H) = R_T \cdot E_S(V) + \frac{(1 - D)P_L(V)}{K_L(W_H)} + D \cdot P_L(V)$$

(3.3)

As the target throughput, i.e.  $R_T$  and D, approaches zero, the power consumption does not go to zero, but instead consumes  $P_L/K_L(W_H)$  watts.

In [13], it was shown that it is possible to target very low-throughput architectures by using a very small header. However, if the header is too small, a large voltage drop will result and the effective supply voltage of the circuit may be below the minimum operational voltage of the circuit, rendering the circuit inoperable. Once this header size limit is reached,  $K_L(W_H)$  reaches its maximum value and no matter how low the throughput goes, the power consumption will always be at  $P_L(V)/K_L(W_H)$ .

#### 3.3.2 NEMS-Based Power-Gating

NEMS power-gates affect the power and energy consumption in three ways. First, the sleep-mode power becomes zero due to the effectively infinite off-resistance of the NEMS switch. Second, a certain amount of activation energy,  $E_{ACT}$  is needed to actuate the NEMS switches. Finally, the NEMS switches consume power when on, represented as  $P_{SW}^{-1}$ . With these changes, Equation (3.1) can be rewritten for NEMS-gated circuits as follows, where  $K_D(\Omega)$  is the delay penalty due to the finite contact resistance of the switch array:

$$P(V, R_T) = R_T(E_A(V) + E_{ACT}) + \frac{R_T}{R_M(V)/K_D(\Omega)} [P_L(V) + P_{SW}]$$

(3.4)

Rearranging (3.4) gives (3.5):

$$P(V, R_T) = R_T \cdot \left[ E_A(V) + E_{ACT} + \frac{P_L(V) + P_{SW}}{R_M(V)/K_D(\Omega)} \right]$$

(3.5)

Let  $E_{MIN}$  be the minimum energy of a circuit, across all supply voltages, as shown in (3.6) and  $V_{opt}$  be the voltage where  $E_{MIN}$  is achieved:

$$E_{MIN} = \min_{\forall V} \left[ E_A(V) + E_{ACT} + \frac{P_L(V) + P_{SW}}{R_M(V)/K_D(\Omega)} \right]$$

(3.6)

As long as  $R_M(V_{opt})$  is equal or more than  $R_T$ , which holds for lower-throughput applications, (3.5) becomes:

$$P(R_T) = R_T \cdot E_{MIN} \qquad : R_T < R_M(V_{opt}) \tag{3.7}$$

<sup>&</sup>lt;sup>1</sup>It will later be shown that this on-power is negligible for electrostatic switches. Other classes of switches, such as thermal switches, do have significant on-power though, so it is included for completeness.

Comparing (3.7) and (3.3) shows several important distinctions between the behavior of a transistor switched circuit versus a NEMS switched one:

- In NEMS-gated circuits, the average power consumption approaches 0 as  $R_T$  approaches 0.

- The supply voltage that minimizes energy of NEMS-gated circuits is no longer dependent on the target throughput, and can be determined separately.

- The most suitable architecture, regardless of the target throughput, is the one that has the least  $E_{MIN}$ . Since the architecture is running at its maximum throughput, this tends to be the architecture with the lowest switching energy. This contrasts to transistor power-gated applications, where the most suitable architecture highly depends on the target throughput.

#### 3.4 Implementation

Since NEMS switches have an actuation voltage that is much higher than the typical voltage of a CMOS circuit, a system is needed that is able to generate the high voltages and distribute them to the switches. This section details that system, as well as the various FFT architectures that are implemented for the architectural exploration.

#### 3.4.1 NEMS Power-Gating System Overview

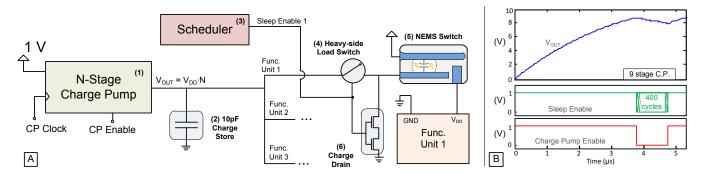

Figure 3.3.A gives a system-level overview of the NEMS-based power-gating scheme. For clarity, each of the major components are labeled with numbers. The charge pump (1) takes a voltage of 1 V (which is generally available on ultra-low-voltage chips for I/O) and produces the activation voltage necessary to actuate the switches. The charge pump simulated in this study is a bootstrap charge pump [24], which can be compactly implemented on-die with

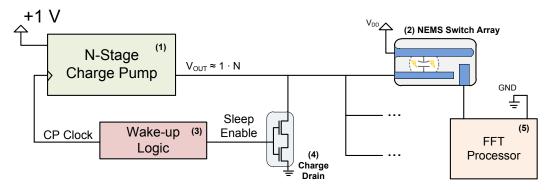

Figure 3.3: System diagram of a NEMS power-gating scheme.

MOSFET capacitors [35] and (ideally) produces an output voltage  $V_{OUT} = V_{DD} * N$ , where N is the number of stages in the pump. The load of the charge pump is the combined capacitance of the NEMS switch array (2). When the wake-up logic (3) decides to switch on the FFT processor (5), it activates the charge pump clock. The charge pump charges the gate of the NEMS switches to the activation voltage of the switches, which actuates them and connects the FFT processor to  $V_{DD}$ . Once the wake-up logic determines the FFT processor is no longer needed, it opens up a charge drain (4), which drains the charge from the NEMS switches, breaking the FFT processor's connection to  $V_{DD}$ .

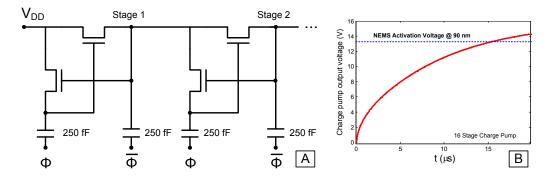

Figure 3.4.A presents a schematic representation of the simulated boot-strap charge pump. Two MOSFETs per stage are used as diodes to prevent the charge from flowing back to the  $V_{DD}$  source, while a clock signal  $\phi$  effectively acts as the pumping mechanism. The clock is connected to 250 fF capacitors, which were simulated using MOSFET gates. Figure 3.4.B presents SPICE simulation results of the output voltage of a 16-stage charge pump with respect to time ( $V_{DD} = 1$ ). The non-idealities and charge pump losses are clear from this graph since the 16 stage pump only charges to around 15 V. Also shown for comparison is the turn-on voltage of a NEMS switch with a 90 nm drain gap (see Table 3.1).

The leakage current of NEMS switches has been shown to be in the femto-amp range [6]. Likewise, the speed of the charge drain is not critical, so it can be stacked and sized such that leakage through it is also in this range. This implies the NEMS switches can hold their charge for a very long time, so once the charge pump charges the NEMS switches, it can

**Figure 3.4:** A. Schematic of the simulated bootstrap charge pump. B. Simulated output voltage with respect to time for a 16 stage charge pump;  $\phi = 20 \text{MHz}$ .

be shut-off for the duration of the processing. Therefore, effectively, the NEMS switches require no power consumption to keep them on; only a fixed amount of energy is needed to charge them to the actuation voltage. The experiments in this paper measured the activation energy and activation time through charge pump simulations and the impact on the overall energy consumed by processing the FFT was determined.

An important consideration with any power-gating system is what has to be left on while the unit is asleep. As far as wake-up periphery, this is highly application-dependent and can be as simple as a picowatt-range timer [13]. A requirement for any NEMS-based power-gating system, however, is that the charge pump is able to function while the NEMS switches are off. This necessitates putting the charge pump on a power network that is not switched with NEMS switches and the leakage will be non-zero leakage when idle. Due to a relative lack of leakage paths, the charge pump exhibits low leakage when idle, and additionally, it can be power-gated using conventional transistors and activated using the wake-up periphery. As part of the experimental methodology, the leakage of a power-gated charge pump will be measured.

| Target     | Beam                      | Beam       | Drain    | Activation | Switching  |

|------------|---------------------------|------------|----------|------------|------------|

| CMOS Tech. | Length $(\mu \mathbf{m})$ | Width (nm) | Gap (nm) | Voltage    | Speed (ns) |

| 130 nm     | 11                        | 100        | 130      | 19.5       | 98         |

| 90 nm      | 10                        | 100        | 90       | 13.1       | 81         |

| 65 nm      | 10                        | 100        | 70       | 9.0        | 81         |

| 45 nm      | 10                        | 100        | 50       | 5.9        | 81         |

| 32 nm      | 10                        | 100        | 30       | 3.2        | 81         |

**Table 3.1:** Physical characteristics of the switches used in this study.

#### 3.4.2 NEMS Switch Physical Parameters

In [6], an analysis is provided of the effect of switch dimensions on activation voltage and switching times. This is done through both simulation and fabrication of switches with a wide variety of dimensions. The mechanical delay of the NEMS switches fall in the nanosecond range, so the boot-up time of the FFT processor is dominated by the charge pump. A lower activation voltage means less work for the charge pump, so the switches with the lowest activation voltages were chosen from the set in [6], which also happen to be the slowest switches. Architectures with transistor channel lengths ranging from 130 nm to 32 nm were tested in this study. In a CMOS process, this channel length is usually the smallest dimension that is achievable by the photolithography, which means there can be no structures on the NEMS switch that are smaller than the channel length. The drain gap is the critical dimension of the NEMS switches (i.e. it is desirable to minimize this dimension), so it will be matched to the channel length of their corresponding CMOS technology. An overview of the physical characteristics of the chosen NEMS switches is given in Table 3.1, listed by their corresponding CMOS technology. It should be noted that there was no data for the 130 nm and 90 nm switch, so the parameters for those switches were extrapolated using analytical equations from [6].

The contact resistance can be considered a tunable parameter of the NEMS switch. Lower contact resistance means less NEMS switches are needed in the power-gating array, which

has a direct impact on the area overhead. To quantify this, a range of contact resistances was examined and the resulting area overhead was determined and compared to the area overhead of transistor-based power-gating.

#### 3.4.3 FFT Architectures

One of the topics studied is the effect of transistor-based and NEMS-based power-gating on architecture choice. To that end, four FFT architectures that vary in complexity and speed were simulated. They each perform a 1024-point radix-2 FFT with 32-bit complex numbers. The low- and medium-complexity implementations use a single real valued 16-bit ALU with a multiplier and an adder, a register bank, and a very simple microprogram to implement the FFT. The low-complexity design uses a 16-bit add/shift multiplier that takes 16 clock cycles, while the medium-complexity design uses a high speed Booth multiplier that takes a single clock cycle. The high-complexity implementation takes advantage of the repetitive nature of the signal flow of an FFT, and contains 9 adders and 3 Booth multipliers. Finally, a parallel architecture with 16 high-complexity cores is investigated. All of the designs are optimally pipelined with respect to energy per FFT at maximum frequency [28]. The designs require a memory bank to hold the 1024 input points, and the same memory bank also holds intermediate values and the final result. A ROM bank is also required to store the constant coefficients (sometimes called twiddle factors) used in the FFT. Data retention is an important concept with power-gating, because a powered down memory bank loses its data. As is the case with a lot of signal processing applications, the raw data does not need to be kept after it is processed. Therefore, data retention is not necessary. More general purpose architectures, on the other hand, may require a data retention plan.

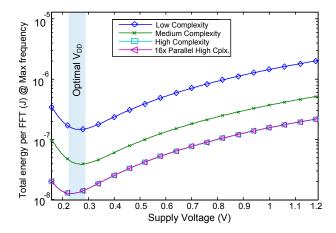

Figure 3.5 presents the total energy per FFT of the four different designs with respect to supply voltage (the designs are running at their respective maximum clock rate) for the 130 nm technology node, using the methodology in Section 3.5. As the complexity of the designs increase, the energy per FFT decreases, mainly due to the fact that the smaller designs

Figure 3.5: Total energy of the 4 FFT architectures (at their respective max. frequencies) with respect to  $V_{DD}$ .

must save intermediate operands in registers and have a lower activity factor. However, the parallel design is not more energy efficient than its scalar counterpart, because parallelization in general does not decrease the energy per task [28].

#### 3.5 Methodology

This chapter presents results of experiments that compare NEMS- and transistor-based power-gating across a wide variety of metrics. An area analysis was carried out which compared area overhead required for power-gating. The energy and time required to actuate the NEMS switches were also determined. An architectural exploration was carried out, where FFT architectures of various complexities were examined with respect to switching energy efficiency and sleep-mode power consumption. Finally, through a technology scaling exploration, it was determined how effective the proposed power-gating structures are as feature sizes decrease. The specific methodologies for each exploration follow:

#### 3.5.1 NEMS Switch Simulation

The simulation of NEMS switches, and their older micron-scale MEMS counterpart, has received a lot of attention in the literature and is important for understanding how various parameters, including material and geometry selection, affect the switching speed, turn-on voltage, and reliability. Considering NEMS switches are actually mechanical devices, doing a mechanical co-simulation with an electronic simulator such as SPICE would be difficult and time-consuming. For these reason, we chose instead to treat NEMS switches as a simple switch in our simulator. The simulated switch has an infinite off-resistance, a specific turn-on gate voltage, a turn-on delay once that gate voltage is reached, and a finite contact resistance once on. Additionally, plate capacitors are used to model the gate-beam capacitance as well as the various parasitic capacitances that are evident in Figure 3.1. This simple switch definition allows us to abstract the many switch parameters into what is important for digital logic designers, and is also flexible enough to handle a wide range of switch types.

As for switch material selection, the switch from [6] was simulated because it contained the most comprehensive data on the effect of switch geometry versus speed and turn-on voltage. Both the structural and contact material of this switch was strained Ruthenium. Other structural materials have been reported, including polysilicon switches that demonstrate high reliability [25], but comprehensive data in the literature is lacking. The contact resistance is an important parameter for power-gating, but is not well researched due to its relative unimportance with NEMS-based digital logic. Additionally, the structural portion of any switch can be coated with metal to improve the contact resistance, e.g. the polysilicon switch from [25] uses a platinum coating. Since contact resistance is such a highly controllable parameter, we abstracted the material and contact design into a simple range of potential contact resistances based on previously reported values.

### 3.5.2 NEMS Area Analysis

With NEMS-based power-gating, the two major determinants of area overhead are the contact resistance of the NEMS switch, and the magnitude of the performance drop that is acceptable. For the area overhead experiments, contact resistances ranging from 50 to 6000  $\Omega$  were considered. Two performance drops were considered as well: 10% (corresponding to  $K_D = 1.11$ , as shown in Equation 3.3) and 90% ( $K_D = 10$ ). SPICE simulations were carried out to determine, for a given contact resistance, how many NEMS switches are needed to limit the delay increase to these two values. Then, using the switch dimensions in Table 3.1 and the layout in Figure 3.1.B, the total area overhead was determined. This was done for the 130 nm technology and the High Complexity FFT architecture with a supply voltage of 0.5 V.

As a point of comparison, the area overhead of transistor-based power-gating was also determined. The number of transistor headers (Regular  $V_{TH}$ , channel width = 1.5  $\mu$ m, channel length = 130 nm) necessary to limit the delay increase to  $K_D = 10$  and  $K_D = 1.11$  was measured in SPICE, and this was multiplied by the area of the header (determined by a standard cell layout in Virtuoso).

## 3.5.3 NEMS Energy Analysis

The primary sources of NEMS actuation energy are the charging of the gate capacitance of the NEMS switches, and energy loss resulting from the non-ideal nature of the charge pump. To quantify this energy, as well as the additional actuation delay caused by the charge pump charging up the output load, SPICE simulations of the system in Figure 3.3 were carried out for the switches listed in Table 3.1. The gate capacitance was calculated using a parallel plate model and, as an example, was found to be 1.60 fF for the 130 nm switch. For each activation voltage, the number of charge pump stages needed, the time required for the output to reach the activation voltage, and the energy consumption of the

charge pump and NEMS switches were measured. The output capacitive load of the charge pump, which is the combined gate capacitance of the NEMS switches in the power-gating switch array, impacts the boot-up time and activation energy. To quantify the effect of the number of switches in the array on activation time and energy, two loads were tested in the simulations. The first load is the combined gate capacitance of 17 switches, which is the number of 800  $\Omega$  NEMS switches required to achieve  $K_D = 10$  (90% drop in performance) with the 130 nm High Complexity FFT architecture at 0.5 V. The second load is the gate capacitance of 170 switches, which results in a  $K_D = 1.11$  (10% performance drop).

#### 3.5.4 FFT Architectural Exploration

An industry-level 130 nm Regular  $V_{TH}$  standard cell library was used to synthesize the four FFT architectures. For memory, custom SRAM bit-cells that can operate down to 450 mV [5] were integrated into CACTI [22]. For the transistor-gated circuits, an exhaustive search was used to find the optimal supply voltage and header size in order to minimize power consumption for each target throughput, which ranged from one FFT per  $\mu s$  to one FFT per day. Supply voltages ranging from 1.2 V to 150 mV were tested. To determine the optimal header size, the methodology from [32] was used, whereby  $K_L$  and  $K_D$  are determined for various relative widths, ranging from one down to the minimum functional size. This process was repeated for each of the four FFT architectures. For the NEMS-gated circuits, the same procedure was applied, with the exceptions that the exhaustive search was only done for  $V_{DD}$ , the activation energy was added in, off-state leakage was assumed to be zero, and a 10% performance drop due to the contact resistance was assumed.

## 3.5.5 Technology Scaling Exploration

The technology scaling exploration examined technology nodes with channel lengths of 90 nm, 65 nm, and 32 nm. For brevity, only the high complexity architecture was examined for

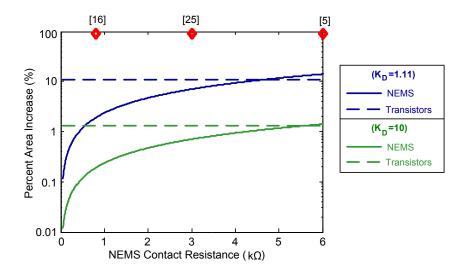

**Figure 3.6:** Percent area increase with respect to the NEMS contact resistance for two target performance drops. Shown for comparison is the area increase with a transistor-based power-gating implementation.

this exploration. The power and timing were determined using scaling based on predictive technology model [37] SPICE simulations. The power and timing of the memory banks were gathered from [22]. The use of custom low-voltage bitcells and the transistor-gating and NEMS-gating methodology is identical to the architectural exploration.

## 3.6 Results

## 3.6.1 NEMS Area Analysis

Figure 3.6 gives the power-gating area overhead with respect to the contact resistance of the NEMS switches for the 130 nm High Complexity FFT architecture with a supply voltage of 0.5 V. The baseline area, of which percent increase is given, is  $40,100 \ \mu m^2$ . Both a 10%  $(K_D = 1.11)$  and 90%  $(K_D = 10)$  target drop in performance is considered, and the area overhead of a transistor power-gating implementation is shown for comparison. At the top of the graph, the contact resistance of three NEMS prototypes is marked on the x-axis.

The contact resistance of the NEMS switch directly determines how many switches are needed to achieve the target performance drop. It can be seen that as the contact resistance falls, the area overhead reduces dramatically to the point of being negligible. It would take a contact resistance of above 5  $k\Omega$  for the area overhead to equal or exceed the overhead of transistor power-gates, and early NEMS prototypes [16,25] have already achieved lower resistances. In summary, transistor power-gates led to an area overhead of up to 10%, depending on the target performance drop, while current NEMS prototypes would only led to an area increase of a few percentage points, which is expected to improve as NEMS technology improves.

#### 3.6.2 NEMS Energy Analysis

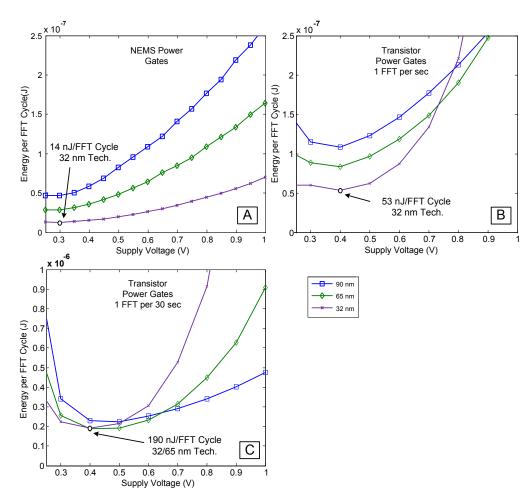

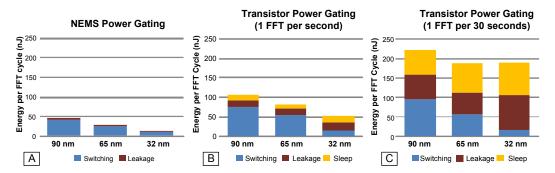

As was noted earlier, the sources of NEMS actuation energy are the charging of the gate capacitance of the NEMS switches, and energy loss resulting from the non-ideal nature of the charge pump. Table 4.2 gives the actuation time  $(T_{BOOT})$  and actuation energy  $(E_{BOOT})$ for the various NEMS switches (130 nm High Complexity FFT processor with 0.5 V supply and 800  $\Omega$  contact resistance). Considering the 130 nm FFT architecture consumes 3.92  $\mu J$ , it can be seen that even with a 19.5 V activation voltage, the energy overhead of the charge pump is negligible. Additionally, a performance drop of 10% requires ten times as many switches as 90%, but leads to only a small increase in activation time and energy, suggesting most of the delay and energy consumption comes from the non-ideal efficiency of the charge pump. It is clear that for applications with a similar processing time and energy consumption of this FFT application, the primary design focus of the NEMS switch should be reducing switch area and contact resistance, with the activation voltage and switching time being the secondary focus. Considering the charge pump cannot be power-gated with NEMS switches, its own leakage power is an important consideration. The off-state leakage power of the largest charge pump was found to be 50.2 pW when power-gated off with transistors. The source of leakage was mostly in the peripheral control structures and is relatively independent of the number of stages.

**Table 3.2:** Time and energy required to active NEMS switch bank.

|            |                | Target Performance Drop |                     |                       |                              |  |  |

|------------|----------------|-------------------------|---------------------|-----------------------|------------------------------|--|--|

| CMOS       | NEMS Actuation | 90                      | 0%                  | 10%                   |                              |  |  |

| Technology | Voltage (V)    | $T_{BOOT}$ $E_{BOOT}$   |                     | $\rm T_{BOOT}$        | $\mathbf{E}_{\mathbf{BOOT}}$ |  |  |

| 130 nm     | 19.5           | $38.1 \ \mu s$          | $2.97~\mathrm{nJ}$  | $40.6~\mu \mathrm{s}$ | 3.16 nJ                      |  |  |

| 90 nm      | 13.1           | $15.6 \ \mu s$          | $0.945~\mathrm{nJ}$ | $17.0~\mu\mathrm{s}$  | 1.03 nJ                      |  |  |

| 65 nm      | 9.0            | $5.17 \ \mu s$          | $225~\mathrm{pJ}$   | $5.97~\mu \mathrm{s}$ | 260 pJ                       |  |  |

| 45 nm      | 5.9            | $0.966 \ \mu s$         | $28.0~\mathrm{pJ}$  | $1.22~\mu\mathrm{s}$  | 35.5 pJ                      |  |  |

| 32 nm      | 3.2            | 92.3 ns                 | $2.46~\mathrm{pJ}$  | $147~\mathrm{ns}$     | 3.93 pJ                      |  |  |

#### 3.6.3 Architectural Exploration Results

#### Transistor-Based Power-Gating

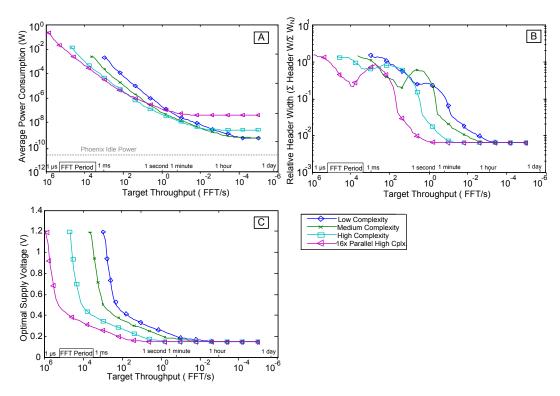

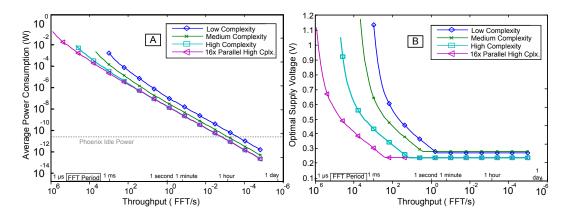

Figure 3.7 presents the results of the architectural exploration for transistor-based power-gating. For a given target throughput (horizontal axis), the best combination of supply voltage (chart C) and relative header width (chart B) that yields the minimum average power consumption (chart A) is shown. As the target throughput reduces, due to the relaxed performance requirements, the header width can be reduced, which reduces the sleep-mode power but also increases the performance drop. As was mentioned in Section 3, if the header is too small, then the voltage drop across the header would render the circuit inoperable. Figure 3.7.B shows the fundamental limit to the relative size of the header. For the 130 nm technology, the optimal relative header width approaches  $5*10^{-2}$  with an optimal supply voltage of around 200 mV.

It can be seen that with target throughputs higher than an FFT every second, the parallel architecture is the most power efficient. The reason is that the parallel architecture is much faster than the others, so the supply voltage can be set lower, thereby reducing power [28].

**Figure 3.7:** A: Average power consumption of transistor-power-gated FFT architectures w.r.t. target throughput. B: Optimal relative header width w.r.t. target throughput. C: Optimal supply voltage w.r.t. target throughput.

At lower throughputs, where the header size starts to reach the above mentioned limit, the average power consumption approaches  $P_L/K_L$ . In this region the least complex architectures become the most power efficient. This implies that even in the presence of transistor switches, the target throughput is an important consideration when selecting an architecture.